PTEA415050

www.ti.com

SLTS291B - JULY 2008 - REVISED NOVEMBER 2010

# 15-A, 48-V INPUT, 5-V OUTPUT, ISOLATED, 1/8th BRICK DC/DC CONVERTER

Check for Samples: PTEA415050

## **FEATURES**

- 15-A Output Current Rating

- Input Voltage Range: 36 V to 75 V

- 91% Efficiency

- 1500 V<sub>DC</sub> Isolation

- On/Off Control

- Overcurrent Protection

- Differential Remote Sense

- Adjustable Output Voltage

- Output Overvoltage Protection

- Over-Temperature Shutdown

- · Undervoltage Lockout

- Standard 1/8-Brick Footprint

- UL Safety Agency Approval

### **DESCRIPTION**

The PTEA415050 power module is a 5-V, single-output, isolated DC/DC converter, housed in an industry standard one-eighth brick package. This module is rated up to 75 W with a maximum load current of 15 A.

The PTEA415050 operates from a standard 48-V telecom central office (CO) supply and occupies less than 2.0 in<sup>2</sup> of PCB area. The modules offer OEMs a compact and flexible high-output power source in an industry standard footprint. They are suitable for distributed power applications in both telecom and computing environments, and may be used for intermediate bus converter architectures.

Features include a remote On/Off control with optional logic polarity, an undervoltage lockout (UVLO), a differential remote sense, and an industry standard output voltage adjustment using an external resistor. Protection features include output overcurrent protection (OCP), overvoltage protection (OVP), and thermal shutdown (OTP).

The module is fully integrated for stand-alone operation, and requires no additional components.

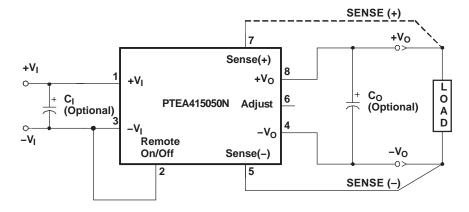

#### STANDARD APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## PTEA415050

SLTS291B - JULY 2008 - REVISED NOVEMBER 2010

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **ORDERING INFORMATION**

For the most current package and ordering information, see the Package Option Addendum at the end of this datasheet, or see the TI website at www.ti.com.

## **Table 1. PART NUMBERING SCHEME**

|      | Input<br>Voltage | Output<br>Current | Output Voltage | Enable       | Electrical Options        |   | Pin Style                 |

|------|------------------|-------------------|----------------|--------------|---------------------------|---|---------------------------|

| PTEA | 4                | 15                | 050            | N            | 2                         | Α | D                         |

|      | 4 = 48 V         | 15 = 15A          | 050 = 5 V      | N = Negative | 2 = V <sub>O</sub> Adjust |   | D = Through-hole, Pb-free |

|      |                  |                   |                | P = Positive |                           |   |                           |

### **ABSOLUTE MAXIMUM RATING**

|                     |                             |                                                            |                              | UNIT |  |  |  |

|---------------------|-----------------------------|------------------------------------------------------------|------------------------------|------|--|--|--|

| T <sub>A</sub>      | Operating Temperature Range | Over V <sub>I</sub> Range                                  | -40°C to 85°C <sup>(1)</sup> |      |  |  |  |

| $V_{I,\;MAX}$       | Maximum Input Voltage       | Continuous voltage                                         | 75 V                         |      |  |  |  |

|                     | waxiinum input voitage      | Peak voltage for 100 ms duration                           | 100 V                        |      |  |  |  |

| P <sub>O, MAX</sub> | Maximum Output Power        | Maximum Output Power                                       |                              |      |  |  |  |

| $T_S$               | Storage Temperature         | -40°C to 125°C                                             |                              |      |  |  |  |

|                     | Mechanical Shock            | Per Mil-STD-883, Method 2002.3 1 ms, 1/2 Sine, mounted     | 250 G                        |      |  |  |  |

|                     | Mechanical Vibrarion        | Per Mil-STD-883, Method 2007.2 20-<br>2000 Hz, PCB mounted | AD Suffix                    | 15 G |  |  |  |

|                     | Weight                      | 18 grams                                                   |                              |      |  |  |  |

|                     | Flammability                |                                                            |                              |      |  |  |  |

(1) See SOA curves or consult factory for appropriate derating.

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

SLTS291B - JULY 2008-REVISED NOVEMBER 2010

## **ELECTRICAL CHARACTERISTICS PTEA415050**

(Unless otherwise stated,  $T_A$  =25°C,  $V_I$  = 48 V,  $V_O$  = 5 V,  $C_O$  = 0  $\mu F$ , and  $I_O$  =  $I_O$ max)

|                             | PARAMETER                      | TES                                         | MIN                                | TYP  | MAX               | UNIT                |                 |

|-----------------------------|--------------------------------|---------------------------------------------|------------------------------------|------|-------------------|---------------------|-----------------|

| lo                          | Output Current                 | Over V <sub>I</sub> range                   | 0                                  |      | 15                | Α                   |                 |

| VI                          | Input Voltage Range            | Over I <sub>O</sub> Range                   | 35                                 | 48   | 75                | ٧                   |                 |

| V <sub>O</sub> tol          | Cat Daint Valtana Talayana     |                                             |                                    |      | ±1 <sup>(1)</sup> |                     | %V <sub>O</sub> |

| Set Point Voltage Tolerance |                                |                                             |                                    | 4.95 | 5                 | 5.05                | ٧               |

| Reg <sub>temp</sub>         | Temperature Variation          | -40°C >T <sub>A</sub> > 85°C                |                                    | ±91  |                   | %V <sub>O</sub>     |                 |

| Reg <sub>line</sub>         | Line Regulation                | Over V <sub>I</sub> range                   |                                    |      | ±1                |                     | mV              |

| Reg <sub>load</sub>         | Load Regulation                | Over I <sub>O</sub> range                   |                                    |      | ±1                |                     | mV              |

| $\Delta V_{o}$ tot          | Total Output Voltage Variation | Includes set-point, line,                   | load, -40°C >T <sub>A</sub> > 85°C |      | ±1.5              | ±3                  | %V <sub>O</sub> |

| $\Delta V_{ADJ}$            | Output Adjust Range            | P <sub>O</sub> ≤ 75 W                       |                                    | -20  |                   | 10                  | %V <sub>O</sub> |

| η                           | Efficiency                     | $I_O = I_O max$                             |                                    |      | 91%               |                     |                 |

| $V_{R}$                     | V <sub>O</sub> Ripple (pk-pk)  | 20 MHz bandwidth                            |                                    |      | 40                |                     | $mV_{pp}$       |

| t <sub>tr</sub>             | Transient Response             | 0.1 A/µs slew rate, 50%                     | % to 75% I <sub>O</sub> max        |      | 100               |                     | μs              |

| $\Delta V_{tr}$             | Transient nesponse             | V <sub>O</sub> over/undershoot              |                                    | 200  |                   | mV                  |                 |

| I <sub>TRIP</sub>           | Overcurrent Threshold          | Shutdown, followed by                       | auto-recovery                      |      | 19                |                     | Α               |

| OVP                         | Output Overvoltage Protection  | Output shutdown and la                      |                                    | 120  |                   | %V <sub>O</sub>     |                 |

| OTP                         | Over Temperature Protection    | Temperature Measurer = 10°C nominal.        |                                    | 115  |                   | ° C                 |                 |

| $f_s$                       | Switching Frequency            | Over V <sub>I</sub> range                   |                                    | 290  |                   | kHz                 |                 |

| INVIO                       |                                | V <sub>OFF</sub>                            | $V_I$ decreasing, $I_O = 5$ A      |      | 29.4              |                     | ٧               |

| UVLO                        | Undervoltage Lockout           | V <sub>HYS</sub>                            |                                    | 3.3  |                   | ∨<br>∟              |                 |

| On/Off In                   | put: Negative Enable           |                                             |                                    |      |                   |                     | İ               |

| $V_{IH}$                    | Input High Voltage             | Peteranged to V                             |                                    |      |                   | Open <sup>(2)</sup> | V               |

| $V_{IL}$                    | Input Low Voltage              | Referenced to -V <sub>I</sub>               |                                    | -0.2 |                   | 0.8                 | <b>∨</b><br>∟   |

| $I_{\rm IL}$                | Input Low Current              |                                             |                                    | -0.2 |                   | mA                  |                 |

| On/Off In                   | put: Positive Enable           |                                             |                                    |      |                   |                     | İ               |

| $V_{IH}$                    | Input High Voltage             | Referenced to -V <sub>I</sub>               |                                    | 4.5  |                   | Open <sup>(2)</sup> | V               |

| $V_{IL}$                    | Input Low Voltage              | Referenced to -v <sub>1</sub>               |                                    | -0.2 |                   | 0.8                 | <b>V</b>        |

| $I_{\parallel L}$           | Input Low Current              |                                             |                                    |      | -0.2              |                     | mA              |

| I <sub>ISB</sub>            | Standby Input Current          | Output disabled (pin 2                      | status set to Off)                 |      | 0.5               |                     | mA              |

| C <sub>I</sub>              | External Input Capacitance     | Between +V <sub>I</sub> and -V <sub>I</sub> | 0                                  | 100  |                   | μF                  |                 |

| (                           | External Output Conscitones    | Between +V <sub>O</sub> and -V <sub>O</sub> |                                    |      |                   | 1000                | μF              |

| Co                          | External Output Capacitance    | Equivalent Series Resis                     | 10                                 |      |                   | mΩ                  |                 |

|                             | Isolation Voltage              | Input-to-output and inpu                    |                                    | 1500 | -                 | Vdc                 |                 |

|                             | Isolation Capacitance          | Input-to-output                             |                                    |      | 1200              |                     | pF              |

|                             | Isolation Resistance           | Isolation Resistance Input-to-output        |                                    |      |                   |                     |                 |

If Sense(–) is not used, pin 5 must be connected to pin 4 for optimum output voltage accuracy.

The Remote On/Off input has an internal pull-up and may be controlled with an open collector (or open drain) interface. An open circuit correlates to a logic high. Consult the application notes for interface considerations.

SLTS291B - JULY 2008 - REVISED NOVEMBER 2010

www.ti.com

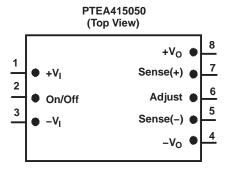

#### PIN DESCRIPTIONS

$+V_1$ : The positive input for the module with respect to  $-V_1$ . When powering the module from a -48-V telecom central office supply, this input is connected to the primary system ground.

-V<sub>i</sub>: The negative input supply for the module, and the 0 VDC reference for the Remote On/Off input. When powering the module from a +48-V supply, this input is connected to the 48-V return.

**Remote On/Off:** This input controls the On/Off status of the output voltage. It is either driven low  $(-V_1 \text{ potential})$ , or left open-circuit. For units identified with the NEN option, applying a logic low to this pin will enable the output. And for units identified with the PEN option, the output will be disabled.

$V_O$  Adjust: Allows the output voltage to be trimmed by up or down between +10% and -20% of its nominal value. The adjustment method uses a single external resistor. Connecting the resistor between  $V_O$  Adjust and  $-V_O$  adjusts the output voltage lower, and placing it between  $V_O$  Adjust and  $+V_O$  adjusts the output higher. The calculations for the resistance value follows industry standard formulas. For further information consult the application note on output voltage adustment.

$+V_0$ : The positive power output with respect to  $-V_0$ , which is DC isolated from the input supply pins. If a negative output voltage is desired,  $+V_0$  should be connected to the secondary circuit common and the output taken from  $-V_0$ .

$-V_0$ : The negative power output with respect to  $+V_0$ , which is DC isolated from the input supply pins. This output is normally connected to the secondary circuit common when a positive output voltage is desired.

**Sense(+):** Provides the converter with an output sense capability to regulate the set-point voltage directly at the load. When used with Sense(-), the regulation circuitry will compensate for voltage drop between the converter and the load. The pin may be left open circuit, but connecting it to  $+V_O$  will improve load regulation. If a series inductor is used for filtering between the module output and load, this pin must be connected directly to the module output to ensure good control design stability.

**Sense(-):** Provides the converter with an output sense capability when used in conjunction with Sense(+) input. For optimum output voltage accuracy this pin should always be connected to  $-V_0$ .

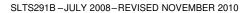

#### TYPICAL CHARACTERISTICS

# PTEA415050, $V_0 = 5 V$ (1) (2)

NSTRUMENTS

- (1) All data listed in Figure 1, Figure 2, and Figure 3 have been developed from actual products tested at 25°C. This data is considered typical data for the dc-dc converter.

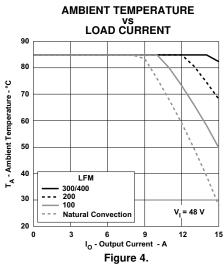

- (2) The temperature derating curves represent operating conditions at which internal components are at or below manufacturer's maximum rated operating temperature. Derating limits apply to modules soldered directly to a 100–mm × 100–mm, double-sided PCB with 2 oz. copper. For surface mount packages, multiple vias (plated through holes) are required to add thermal paths around the power pins. Please refer to the mechanical specification for more information. Applies to Figure 4.

Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

TEXAS INSTRUMENTS

SLTS291B-JULY 2008-REVISED NOVEMBER 2010

www.ti.com

#### **APPLICATION INFORMATION**

## Operating Features and System Considerations for the PTEA415050 DC/DC Converter

#### **Overcurrent Protection**

To protect against load faults, these converters incorporate output overcurrent protection. Applying a load to the output that exceeds the converter's overcurrent threshold (see applicable specification) will cause the output voltage to momentarily fold back, and then shut down. Following shutdown the module will periodically attempt to automatically recover by initiating a soft-start power-up. This is often described as a *hiccup* mode of operation, whereby the module continues in the cycle of successive shutdown and power up until the load fault is removed. Once the fault is removed, the converter automatically recovers and returns to normal operation.

## **Output Overvoltage Protection**

Each converter incorporates protection circuitry that continually senses for an output overvoltage (OV) condition. The OV threshold is set approximately 20% higher than the nominal output voltage. If the converter output voltage exceeds this threshold, the converter is immediately shut down and remains in a latched-off state. To resume normal operation the converter must be actively reset. This can only be done by momentarily removing the input power to the converter. For fail-safe operation and redundancy, the OV protection uses circuitry that is independent of the converter's internal feedback loop.

### **Overtemperature Protection**

Overtemperature protection is provided by an internal temperature sensor, which closely monitors the temperature of the converter's printed circuit board (PCB). If the sensor exceeds a temperature of approximately 115°C, the converter will shut down. The converter will then automatically restart when the sensed temperature drops back to approximately 105°C. When operated outside its recommended thermal derating envelope (see data sheet SOA curves), the converter will typically cycle on and off at intervals from a few seconds to one or two minutes. This is to ensure that the internal components are not permanently damaged from excessive thermal stress.

## **Undervoltage Lockout**

The Undervoltage lockout (UVLO) is designed to prevent the operation of the converter until the input voltage is at the minimum input voltage. This prevents high start-up current during normal power-up of the converter, and minimizes the current drain from the input source during low input voltage conditions. The UVLO circuitry also overrides the operation of the *Remote On/Off* control.

### **Primary-Secondary Isolation**

These converters incorporate electrical isolation between the input terminals (primary) and the output terminals (secondary). All converters are production tested to a withstand voltage of 1500 VDC. This specification complies with UL60950 and EN60950 requirements. This allows the converter to be configured for either a positive or negative input voltage source. The data sheet *Pin Descriptions* section provides guidance as to the correct reference that must be used for the external control signals.

### **Input Current Limiting**

The converter is not internally fused. For safety and overall system protection, the maximum input current to the converter must be limited. Active or passive current limiting can be used. Passive current limiting can be a fast acting fuse. A 125-V fuse, rated no more than 10 A, is recommended. Active current limiting can be implemented with a current limited *Hot-Swap* controller.

#### **Thermal Considerations**

Airflow may be necessary to ensure that the module can supply the desired load current in environments with elevated ambient temperatures. The required airflow rate may be determined from the Safe Operating Area (SOA) thermal derating chart (see typical characteristics).

Product Folder Links: PTEA415050

SLTS291B - JULY 2008 - REVISED NOVEMBER 2010

#### **Differential Remote Sense**

The remote sense pins allows the converter to precisely regulate the DC output voltage at a remote location. This might be a power plane on an inner layer of the host PCB. Connecting Sense(+) directly to  $+V_O$ , and Sense(-) to  $-V_O$  will improve output voltage accuracy. In the event that the sense pins are left open-circuit, an internal  $10-\Omega$  resistor between each sense pin and its corresponding output prevents an excessive rise in the output voltage. For practical reasons, the amount of IR voltage compensation should be limited to 0.5~V maximum.

The remote sense feature is designed to compensate for limited amounts of *IR* voltage drop. It is **not** intended to compensate for the forward drop of a non-linear or frequency dependent components that may be placed in series with the converter output. Examples of such components include OR-ing diodes, filter inductors, ferrite beads, and fuses. Enclosing these components with the remote sense connections effectively places them inside the regulation control loop, which can affect the stability of the regulator.

Product Folder Links: PTEA415050

TEXAS INSTRUMENTS

SLTS291B-JULY 2008-REVISED NOVEMBER 2010

www.ti.com

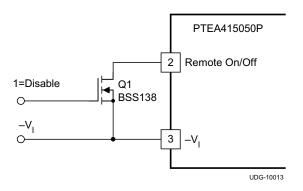

# Using the Remote On/Off Function on the PTEA415050 DC/DC Converter

For applications requiring output voltage On/Off control, the PTEA415050 DC/DC converter incorporate a *Remote On/Off* control (pin 2). This feature can be used to switch the module off without removing the applied input source voltage. When placed in the *Off* state, the standby current drawn from the input source is typically reduced to 3 mA.

## **Negative Output Enable (NEN)**

Models using the negative enable option, the *Remote On/Off* (pin 2) control must be driven to a logic low voltage for the converter to produce an output. This is accomplished by either permanently connecting pin 2 to  $-V_1$  (pin 3), or driving it low with an external control signal. Table 2 shows the input requirements of pin 2 for those modules with the *NEN* option.

Table 2. On/Off Control Requirements for Negative Enable

|                  | PARAMETER                | MIN  | TYP | MAX   | UNITS |

|------------------|--------------------------|------|-----|-------|-------|

| $V_{IH}$         | Disable                  | 2.4  |     | 20    | V     |

| $V_{IL}$         | Enable                   | -0.2 |     | 8.0   |       |

| V <sub>o/c</sub> | Open-Circuit             |      | 9   | 15    |       |

| I                | Pin 2 at -V <sub>I</sub> |      |     | -0.75 | mA    |

## Positive Output Enable (PEN)

For those models with the positive enable (PEN) option, leaving pin 2 open circuit, (or driving it to an equivalent logic high voltage), will enable the converter output. This allows the module to produce an output voltage whenever a valid input source voltage is applied to  $+V_I$  with respect to  $-V_I$ . If a logic-low signal is then applied to pin 2 the converter output is disabled. Table 3 gives the input requirements of pin 2 for modules with the *PEN* option.

Table 3. On/Off Control Requirements for Positive Enable

|                  | PARAMETER                | MIN  | TYP | MAX  | UNITS |

|------------------|--------------------------|------|-----|------|-------|

| $V_{IH}$         | Enable                   | 4.5  |     | 20   | V     |

| V <sub>IL</sub>  | Disable                  | -0.2 |     | 0.8  |       |

| V <sub>o/c</sub> | Open-Circuit             |      | 5   | 7    |       |

| I <sub>I</sub>   | Pin 2 at –V <sub>I</sub> |      |     | -0.5 | mA    |

### Notes:

- 1. The Remote On/Off control uses  $-V_1$  (pin 3) as its ground reference. All voltages are with respect to  $-V_1$ .

- 2. An open-collector device (preferably a discrete transistor) is recommended. A pull-up resistor is not required. If one is added the pull-up voltage should not exceed 20 V.

**Caution:** Do not use a pull-resistor to  $+V_l$  (pin 1). The remote On/Off control has a maximum input voltage of 20 V. Exceeding this voltage will overstress, and possibly damage, the converter.

- 3. The *Remote On/Off* pin may be controlled with devices that have a totem-pole output. This is provided the output high level voltage (V<sub>OH</sub>) meets the module's minimum V<sub>IH</sub> specified in Table 2. If a TTL gate is used, a pull-up resistor may be required to the logic supply voltage.

- 4. The converter incorporates an *undervoltage lockout* (UVLO). The UVLO keeps the converter off until the input voltage is close to the minimum specified operating voltage. This is regardless of the state of the *Remote On/Off* control. Consult the product specification for the UVLO input voltage thresholds.

Product Folder Links: PTEA415050

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

SLTS291B - JULY 2008 - REVISED NOVEMBER 2010

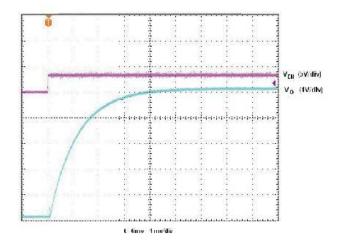

Turn-On: With a valid input source voltage applied, the converter produces a regulated output voltage within 10 ms of the output being enabled. Figure 6 shows the output response of the PTEA following the removal of the logic-low signal from the Remote On/Off (pin 2); see Figure 5. This corresponds to the rise in V<sub>EN</sub> in Figure 6. Although the rise-time of the output voltage is short (<5 ms), the indicated delay time will vary depending upon the input voltage and the module's internal timing. The waveforms were measured with 48 VDC input voltage. and a 15-A resistive load.

Figure 5. Recommended Remote On/Off Control

Figure 6. Power Up

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Links: PTEA415050

SLTS291B-JULY 2008-REVISED NOVEMBER 2010

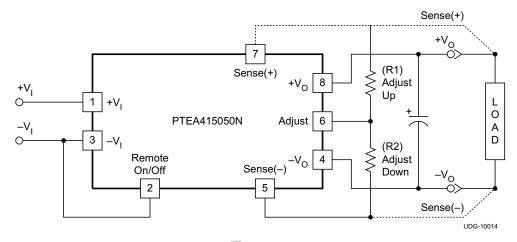

# Adjusting the Output Voltage of the PTEA415050 Isolated DC/DC Converter

The output voltage adjustment of the PTEA415050 isolated DC/DC converter follows the standard adopted by popular 1/8-brick DC/DC converters. Adjustment is accomplished with a single external resistor that can adjust the output voltage from -20% to +10% of the nominal set-point voltage. The placement of the resistor determines the direction of adjustment, up or down, and the value of the magnitude of adjustment. To ensure good  $V_O$  set-point accuracy, a 1% maximum tolerance resistor is recommended.

**Adjust Up:** To increase the output voltage add a resistor, R1, between  $V_O$  Adjust (pin 6) and Sense(+) (pin 7).

**Adjust Down:** Add a resistor, (R2), between  $V_O$  Adjust (pin 6) and Sense(-) (pin 5).

Refer to Figure 7 for the placement of the required resistor, R1 or (R2).

The values of R1 [adjust up], and (R2) [adjust down], can be calculated using the following formulas.

$$R1 = \frac{5.11 \text{ V}_{\text{O}} (100 + \Delta\%)}{1.225 \Delta\%} - \frac{511}{\Delta\%} - 10.22 \text{ (k}\Omega)$$

(1)

$$(R2) = 5.11 \frac{100}{\Delta\%} - 10.22 \quad (k\Omega)$$

(2)

Where:

$\Delta$ % = Amount of adjustment in %

V<sub>O</sub> = Original set-point voltage

#### Notes:

- 1. Use a 1% resistor for either the R1 or (R2). Place the resistor as close to the converter as possible.

- 2. If V<sub>O</sub> is increased, the maximum load current must be derated according to the following equation.

$$I_{O}(max) = \frac{V_{O} \times I_{O}(rated)}{V_{A}}$$

where

- V<sub>O</sub> is the original set-point voltage

- V<sub>A</sub> is the adjusted output voltage (measured between pin 8 and pin 4)

(3)

In any instance, the load current must not exceed the converter's maximum rated output current of 15 A.

3. The overvoltage threshold is fixed, and is set approximately 20% above the nominal output voltage. Adjusting the output voltage higher reduces the voltage margin between the adjusted output voltage and the overvoltage (OV) protection threshold. This could make the module sensitive to OV fault detection, as a result of random noise and load transients.

Figure 7.

Submit Documentation Feedback

SLTS291B -JULY 2008-REVISED NOVEMBER 2010

# **Table 4. Adjustment Resistor Values**

| V <sub>O</sub> (nom)<br>% Adjust (V) | Adjusted Output<br>Voltage (V) | Trim-Up R <sub>ADJ</sub><br>R1 (kΩ) | Trim-Down R <sub>ADJ</sub><br>R2 (kΩ) |

|--------------------------------------|--------------------------------|-------------------------------------|---------------------------------------|

| +10                                  | 5.50                           | 169                                 | Open                                  |

| + 9                                  | 5.45                           | 187                                 | Open                                  |

| + 8                                  | 5.40                           | 205                                 | Open                                  |

| + 7                                  | 5.35                           | 237                                 | Open                                  |

| + 6                                  | 5.30                           | 274                                 | Open                                  |

| + 5                                  | 5.25                           | 324                                 | Open                                  |

| + 4                                  | 5.20                           | 402                                 | Open                                  |

| + 3                                  | 5.15                           | 536                                 | Open                                  |

| + 2                                  | 5.10                           | 806                                 | Open                                  |

| + 1                                  | 5.05                           | 1580                                | Open                                  |

| 0                                    | 5.00                           | Open                                | Open                                  |

| -1                                   | 4.95                           | Open                                | 499                                   |

| -2                                   | 4.90                           | Open                                | 243                                   |

| -3                                   | 4.85                           | Open                                | 158                                   |

| -4                                   | 4.80                           | Open                                | 118                                   |

| -5                                   | 4.75                           | Open                                | 90.9                                  |

| -6                                   | 4.70                           | Open                                | 75.0                                  |

| <b>-</b> 7                           | 4.65                           | Open                                | 63.4                                  |

| -8                                   | 4.60                           | Open                                | 53.6                                  |

| -9                                   | 4.55                           | Open                                | 46.4                                  |

| -10                                  | 4.50                           | Open                                | 41.2                                  |

| -11                                  | 4.45                           | Open                                | 36.5                                  |

| -12                                  | 4.40                           | Open                                | 32.4                                  |

| -13                                  | 4.35                           | Open                                | 28.7                                  |

| -14                                  | 4.30                           | Open                                | 26.1                                  |

| -15                                  | 4.25                           | Open                                | 23.7                                  |

| -16                                  | 4.20                           | Open                                | 21.5                                  |

| -17                                  | 4.15                           | Open                                | 19.6                                  |

| -18                                  | 4.10                           | Open                                | 18.2                                  |

| -19                                  | 4.05                           | Open                                | 16.5                                  |

| -20                                  | 4.00                           | Open                                | 15.4                                  |

Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

# PACKAGE OPTION ADDENDUM

19-Dec-2019

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type            | Package | Pins | Package | Eco Plan                      | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|-------------------------|---------|------|---------|-------------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |                         | Drawing |      | Qty     | (2)                           | (6)              | (3)                |              | (4/5)          |         |

| PTEA415050N2AD   | NRND   | Through-<br>Hole Module | EAW     | 8    | 15      | RoHS (In Work)<br>& non-Green | SN               | N / A for Pkg Type | -40 to 85    |                |         |

| PTEA415050P2AD   | NRND   | Through-<br>Hole Module | EAW     | 8    | 15      | RoHS (In Work)<br>& non-Green | SN               | N / A for Pkg Type | -40 to 85    |                |         |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

19-Dec-2019

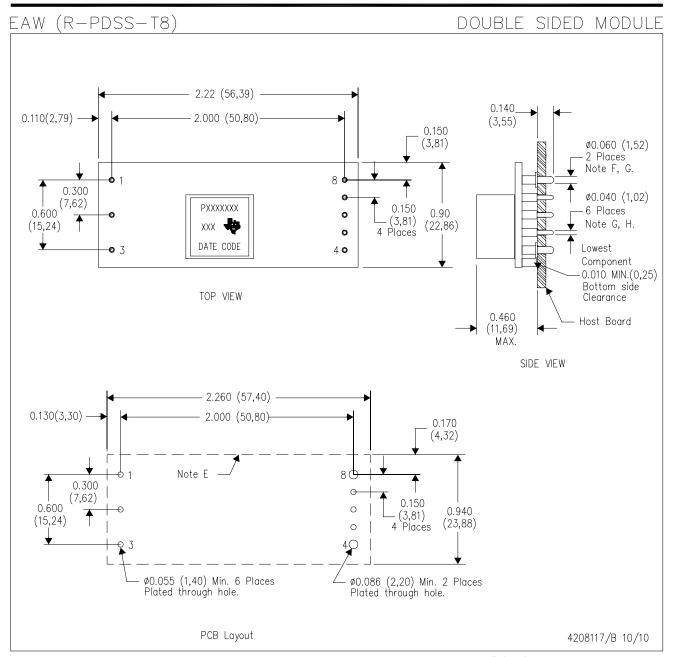

NOTES:

- A. All linear dimensions are in inches (mm).

- B. This drawing is subject to change without notice.

- C. 2 place decimals are  $\pm 0.020$  ( $\pm 0.51$ mm).

- D. 3 place decimals are  $\pm 0.010$  ( $\pm 0.25$ mm).

- E. Recommended keep out area for user components.

- F. Pins are 0.040" (1,02) diameter with 0.070" (1,78) diameter standoff shoulder.

- G. All pins: Material Copper Alloy Finish — Tin (100%) over Nickel plate

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated