# Octal High-Side Driver NCV7755

The NCV7755 is an automotive grade integrated driver with eight high–side switches. The device provides drive capability up to 700 mA per channel and is protected for overload and overtemperature conditions. All the channels have integrated output clamps for switching inductive loads, multiple start pulses for bulbs, and can be mapped to two internal PWM generators for LED loads. The output control and diagnostic reporting is via SPI. Additionally, INx pins can be mapped to any of the outputs for direct control.

A dedicated limp-home mode enables operational control of two high-side drivers via logic input pins.

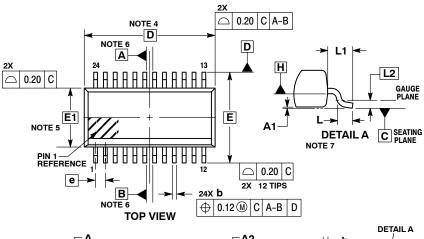

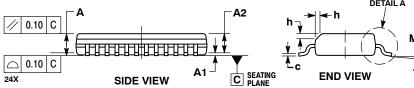

The NCV7755 is available in a SSOP-24 exposed pad package for optimal thermal performance.

#### **Features**

- 8 High-Side Channels

- For Relays (Flyback Clamps)

- Bulbs (Multiple Pulse in-rush Scheme)

- LEDs (Internal PWM Generator)

- 2.3 A Peak Current (Max)

- $R_{DS(on)}$  0.9  $\Omega$  (Typ), 1.8  $\Omega$  (Max)

- Paralleling of Two Output Pair is Allowed

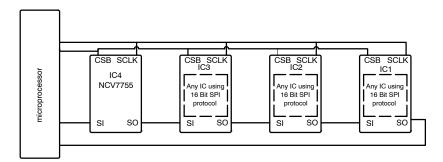

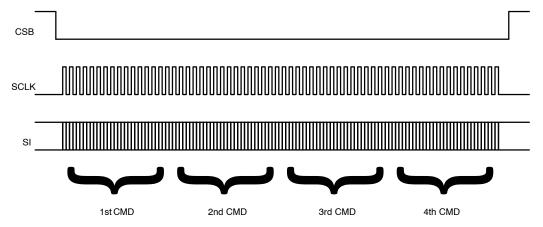

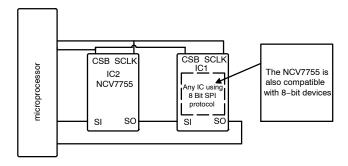

- SPI Control (16 Bit)

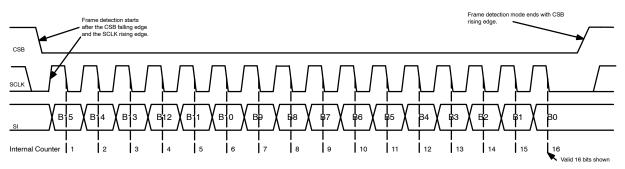

- Frame Error Detection (16 Bits + 8\*n Bits)

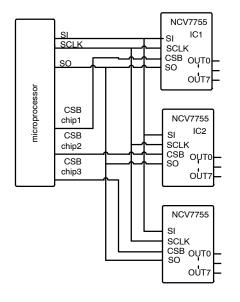

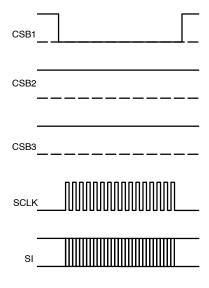

- Daisy Chain Capable

- Two Input Pins with Mapping for PWM Operation

- Low Quiescent Current in Sleep Mode

- Limp Home Mode with Auto-retry

- Supports Cranking Voltage of 3 V Minimum on VS

- 3.3 V & 5 V Compatible Digital Input Supply Range

- Fault Reporting

- Openload (OFF or ON)

- Overload

- Overtemperature

- Power Supply Fail (VS, VDD Undervoltage)

- Output Short to GND and Battery

- Reverse Polarity Protection

- Loss of Ground Protection

- Power-on Reset (VDD)

- SSOP-24 with an Exposed Pad

- NCV Prefix for Automotive

- Site and Change Control

- ◆ AEC-Q100 Qualified

#### **MARKING DIAGRAM**

NCV7755 = Specific Device Code

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device       | Package   | Shipping   |

|--------------|-----------|------------|

| NCV7755DQR2G | SSOP24-EP | 2500       |

|              | (Pb-Free) | Units/Rail |

# **Applications**

- Automotive Body Control Unit

- Automotive Engine Control Unit

- Relay Drive

- Bulb Drive

- LED Drive

1

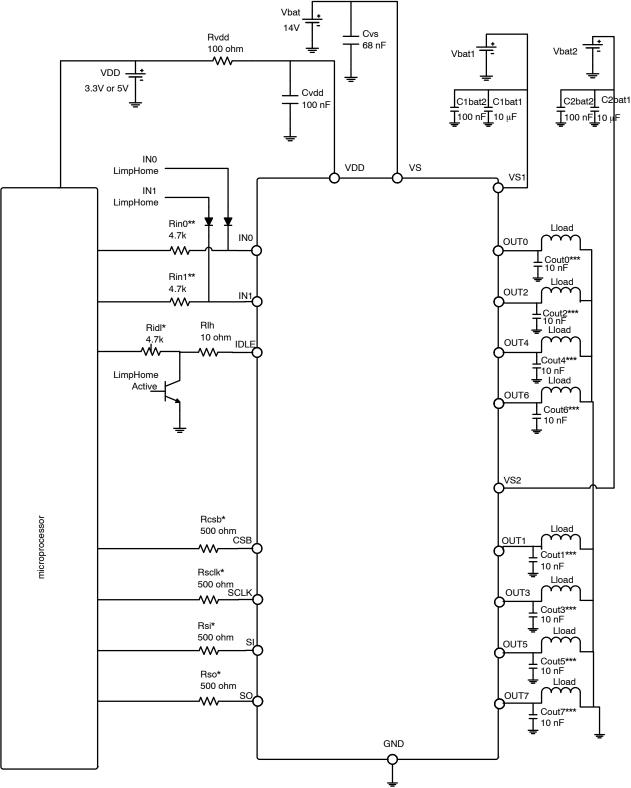

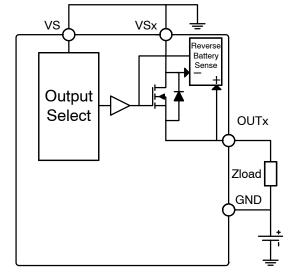

- \* Required for Reverse Polarity protection.

- \*\* Required for Reverse Polarity and Loss of Ground protection.

- \*\*\* Required for EMC.

Figure 1. Application Diagram

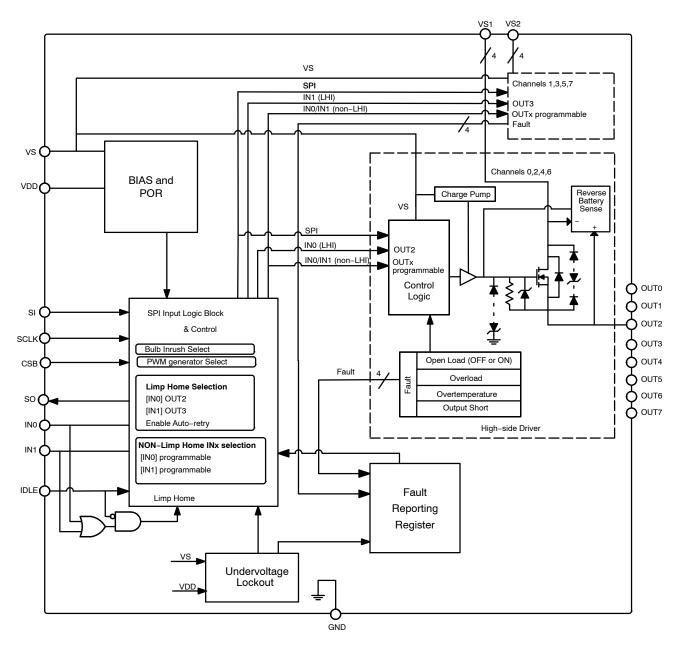

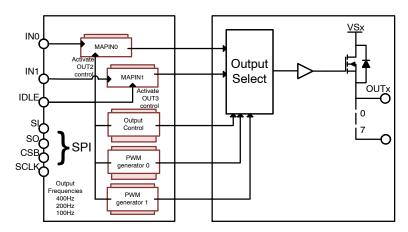

Figure 2. Block Diagram

# **PACKAGE PIN DESCRIPTION**

| SSOP-24<br>EPAD | Symbol      | Description                                                                                                                                                                                                     |

|-----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | CSB         | SPI Chip Select "Bar" (120 kΩ pull–up resistor to VDD)                                                                                                                                                          |

| 2               | SCLK        | SPI Clock (120 kΩ pull–down resistor)                                                                                                                                                                           |

| 3               | SI          | SPI Serial Data Input (120 kΩ pull-down resistor)                                                                                                                                                               |

| 4               | SO          | SPI Serial Data Output. Tri-state when CSB is high                                                                                                                                                              |

| 5               | GND         | Ground                                                                                                                                                                                                          |

| 6               | OUT0        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 7               | NC          | No connection. Internally not bonded                                                                                                                                                                            |

| 8               | OUT2        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 9               | VS1         | Power supply input for High-side drivers channels 0, 2, 4, and 6                                                                                                                                                |

| 10              | OUT4        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 11              | OUT6        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 12              | NC          | No connection. Internally not bonded                                                                                                                                                                            |

| 13              | NC          | No connection. Internally not bonded                                                                                                                                                                            |

| 14              | OUT7        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 15              | OUT5        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 16              | VS2         | Power supply input for High-side drivers channels 1, 3, 5, and 7                                                                                                                                                |

| 17              | OUT3        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 18              | NC          | No connection. Internally not bonded                                                                                                                                                                            |

| 19              | OUT1        | High-side driver output. Requires an external pull-down component for operation                                                                                                                                 |

| 20              | VS          | Power supply input for output power switches gate control                                                                                                                                                       |

| 21              | IDLE        | High activates low Iq Idle mode (120 k $\Omega$ pull-down resistor)  Low with IN0 = IN1 = low puts device in sleep mode. Low puts all SPI registers in reset  Low with INx = high puts device in limp home mode |

| 22              | IN1*        | Input pin 1. Controls channel 3 (default) and in Limp Home Mode (with IDLE = low). Outputs can be mapped to this pin. (120 k $\Omega$ pull-down resistor)                                                       |

| 23              | INO*        | Input pin 0. Controls channel 2 (default) and in Limp Home Mode (with IDLE = low). Outputs can be mapped to this pin. (120 k $\Omega$ pull-down resistor)                                                       |

| 24              | VDD         | Digital power supply input for SPI and support interface to VS                                                                                                                                                  |

| EPAD            | Exposed Pad | Connect to GND for best thermal performance or leave unconnected.  Internally, the EPAD is isolated from the GND signal                                                                                         |

\*Ground if not used for best EMI performance. Alternatively keep open and internal pull–down will hold the input low through a 120 k $\Omega$  pull down resistor.

# **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                       | Symbol                                   | Min                            | Max                        | Unit           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------|----------------------------|----------------|

| Battery supply input voltage (VS) DC Positive Transient input supply voltage (Note 1)                                                                                                                                                        | VsMax<br>VsacMax                         | -0.3<br>-                      | 36<br>42                   | V              |

| Battery supply input voltage (VS1, VS2) DC input supply voltage with short circuit Positive Transient input supply voltage (Note 1)                                                                                                          | VsdcscMax<br>VsxacMax                    | 0 -                            | 36<br>42                   | V              |

| Logic Supply Input Voltage (VDD)<br>DC                                                                                                                                                                                                       | VddMax                                   | -0.3                           | 5.5                        | V              |

| Output Voltage (OUTx)                                                                                                                                                                                                                        | VoutMax                                  | -25                            | VSx+0.3                    | V              |

| Output Current (OUTx) Specified is the maximum overload detection threshold.                                                                                                                                                                 | loutMax                                  | -                              | 2.3                        | А              |

| Digital I/O pin voltage<br>(IDLE, IN0, IN1, CSB, SCLK, SI,)<br>(SO)                                                                                                                                                                          | VioMax<br>ViosoMax                       | -0.3<br>-0.3                   | 5.5<br>VDD+0.3V            | V              |

| Digital I/O input current (IDLE, INO, IN1, CSB, SCLK, SI, SO)                                                                                                                                                                                | lioMax                                   | -10.0                          | 2.0                        | mA             |

| Clamping Energy  Maximum (single pulse)  (Tj = 25°C, lout = 440 mA)  (Tj = 150°C, lout = 400 mA)  Repetitive (multiple pulse)                                                                                                                | VclpDc25Max<br>VclpDc150Max<br>VclpAcMax | -<br>-<br>-                    | 50<br>25<br>Note 2         | mJ<br>mJ<br>mJ |

| Operating Junction Temperature Range                                                                                                                                                                                                         | Tj                                       | -40                            | 150                        | °C             |

| Storage Temperature Range                                                                                                                                                                                                                    | Tstr                                     | -65                            | 150                        | °C             |

| ESD Capability (AEC-Q100-002, AEC-Q100-011) Human body model (100 pF, 1.5 k $\Omega$ ) (VSx, OUTx pins) Human body model (100 pF, 1.5 k $\Omega$ ) (all other pins) Charged Device Model (corner pins) Charged Device Model (all other pins) | Vesd4k<br>Vesd2k<br>Vesd750<br>Vesd500   | -4000<br>-2000<br>-750<br>-500 | 4000<br>2000<br>750<br>500 | V<br>V<br>V    |

| AECQ10x-12<br>Short Circuit Reliability Characterization                                                                                                                                                                                     | AECQ10x                                  | Grade A                        | -                          |                |

- 1. Ton = 400 ms; ton/toff = 10%, 100 pulse limit. 2. 2 M pulses (triangular), VS = 15 V, 63  $\Omega$ , 390 mH,  $T_A$  = 25°C.

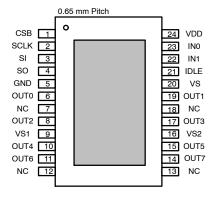

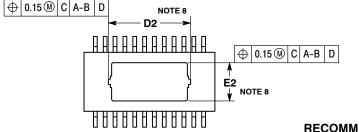

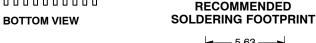

Figure 3. Pin-out

#### **PACKAGE**

| Moisture Sensitivity Level                                                                                                        | MSL                                 | 2            |              |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|--------------|

| Lead Temperature Soldering: SMD style only, Reflow (Note 3) Lead – Free Part 60 – 150 sec above 217°C, 40 sec max at peak         | Treflow                             | 265 peak     | °C           |

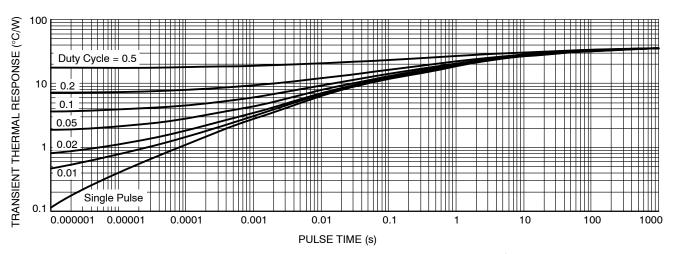

| Package Thermal Resistance and Characterization Parameter SSOP-24 EPAD Junction-to-Ambient (Note 4) Junction-to-pin (exposed pad) | R <sub>θJA</sub><br>Ψ <sub>JB</sub> | 35.1<br>24.3 | °C/W<br>°C/W |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

3. For additional information, see or download **onsemi**'s Soldering and Mounting Techniques Reference Manual, SOLDERRM/D and

#### RECOMMENDED OPERATING CONDITIONS

|                                                                 |         | Va   | lue  |      |

|-----------------------------------------------------------------|---------|------|------|------|

| Rating                                                          | Symbol  | Min  | Max  | Unit |

| Digital Supply Input Voltage (VDD)                              | VDDRec  | 3.00 | 5.5  | V    |

| Battery Supply Input Voltage (VS, VS1, VS2)                     | VSRec   | 7.0* | 18** | V    |

| DC Output Current (OUTx), (T <sub>A</sub> = 85°C, all channels) | IoutRec |      | 330  | mA   |

| Junction Temperature                                            | $T_J$   | -40  | 150  | °C   |

<sup>\*</sup>Extended operation down to 3 V with possible parameter shift. \*\*Extended operation up to 28 V with possible parameter shift.

# **ELECTRICAL CHARACTERISTICS** $(-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, 3.0 \text{ V} < \text{VDD} < 5.5 \text{ V}, 7 \text{ V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \text{ V}, 7 \text{ V} < 100^{\circ}\text{C}$ IDLE = high unless otherwise specified)

| Characteristic                        | Conditions                                                                                        | Symbol                             | Min    | Тур         | Max               | Unit                     |

|---------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------|--------|-------------|-------------------|--------------------------|

| VS CURRENTS                           |                                                                                                   |                                    |        |             |                   |                          |

| Operating Current (VS)<br>Active Mode | Set to Active Mode via SPI<br>HWCR.ACT (bit 7) = 1                                                |                                    |        |             |                   |                          |

|                                       | IDLE = CSB = VDD<br>SCLK=0V<br>No Open Circuit Diag Current                                       |                                    |        |             |                   |                          |

| Channels Off Channels On              | 7 V < VS < 18 V, INO = IN1 = 0<br>VS < VDD-1 V, INO = IN1 = 0<br>7 V < VS < 18 V, INO = IN1 = VDD | VSactOFF1<br>VSactOFF2<br>VSactON1 | -<br>- | -<br>-<br>- | 7.7<br>5.0<br>8.7 | mA<br>mA<br>mA           |

|                                       | VS < VDD-1 V, IN0 = IN1 = VDD                                                                     | VSactON2                           | _      | 2.3         | 5.0               | mA                       |

| Operating Current (VS)<br>Idle Mode   | IDLE = CSB = VDD<br>IN0 = IN1 = SCLK = 0 V<br>All Channels Off                                    |                                    |        |             |                   |                          |

|                                       | 7 V < VS < 18 V<br>VS < VDD-1 V                                                                   | VSidl1<br>VSidl2                   | -<br>- | -<br>-      | 2.2<br>0.3        | mA<br>mA                 |

| Operating Current (VS)<br>Sleep Mode  | CSB = VDD<br>IDLE = IN0 = IN1 = 0 V                                                               |                                    |        |             |                   |                          |

|                                       | $T_{J} = 85^{\circ}C$ $T_{J} = 150^{\circ}C$                                                      | VSslp85<br>VSslp150                | -      | 0.1<br>0.1  | 3<br>20           | μ <b>Α</b><br>μ <b>Α</b> |

Application Note AND8083/D.

<sup>4.</sup> Per JEDEC JESD51-7 at natural convection on FR4 2s2p board (76.2 mm x 114.3 mm x 1.5 mm) with 2 inner copper layers.

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} \\ (-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \ 3.0 \ \text{V} < \text{VDD} < 5.5 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \\ \text{IDLE} = \text{high unless otherwise specified})$

| Characteristic                                         | Conditions                                                                                       | Symbol                    | Min    | Тур    | Max        | Unit                     |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|--------|--------|------------|--------------------------|

| VDD CURRENTS                                           |                                                                                                  |                           |        |        |            |                          |

| Operating Current (VDD)<br>Active Mode                 | Set to Active Mode via SPI<br>HWCR.ACT (bit 7) = 1                                               |                           |        |        |            |                          |

|                                                        | IDLE = CSB = VDD<br>SCLK = 0 V                                                                   |                           |        |        |            |                          |

|                                                        | No Open Circuit DIAG current                                                                     |                           |        |        |            |                          |

| Channels Off                                           | 7 V < VS < 18 V, IN0 = IN1 = 0<br>VS < VDD-1 V, IN0 = IN1 = 0<br>7 V < VS <18 V, IN0 = IN1 = VDD | VDDactOFF1<br>VDDactOFF2  | -<br>- | -<br>- | 0.3<br>2.7 | mA<br>mA                 |

| Channels On                                            | VS < VDD-1 V, IN0 = IN1 = VDD                                                                    | VDDactON1<br>VDDactON2    | _      | _      | 0.3<br>3.5 | mA<br>mA                 |

| Operating Current (VDD) Idle Mode                      | IDLE = CSB = VDD,<br>IN0 = IN1 = SCLK = 0 V<br>All Channels Off<br>7 V < VS < 18 V               | VDDidl1                   | -      | _      | 0.3        | mA                       |

|                                                        | VS < VDD-1 V                                                                                     | VDDidl2                   | -      | -      | 2.2        | mA                       |

| Operating Current (VDD)<br>Sleep Mode                  | $CSB = VDD$ $IDLE = IN0 = IN1 = 0 V$ $T_{J} = 85^{\circ}C$ $T_{J} = 150^{\circ}C$                | VDDslp85<br>VDDslp150     | _<br>_ | 0.1    | 2.5<br>10  | μ <b>Α</b><br>μ <b>Α</b> |

| TOTAL CURRENTS                                         | 1) = 130 0                                                                                       | VDDsip130                 |        | _      | 10         | μΑ                       |

| Total Sleep Current                                    | CSB=VDD                                                                                          |                           |        |        |            |                          |

| (VS + VDD)                                             | IDLE=IN0=IN1=0V<br>Tj=85°C<br>Tj=150°C                                                           | Slp85<br>Slp150           | -<br>- | -<br>- | 5<br>30    | μ <b>Α</b><br>μ <b>Α</b> |

| Total Idle Mode<br>Current Consumption<br>(VS + VDD)   | IDLE=CSB=VDD<br>IN0=IN1=SCLK=0V<br>All Channels Off                                              | VSVDDidl                  | -      | -      | 2.5        | mA                       |

| Total Active Mode<br>Current Consumption<br>(VS + VDD) | Set to Active Mode via SPI<br>HWCR.ACT (bit 7) = 1                                               |                           |        |        |            |                          |

|                                                        | IDLE = CSB = VDD, SCLK = 0 V                                                                     |                           |        |        |            |                          |

| Channels Off<br>Channels On                            | All outputs off<br>All outputs on                                                                | VSVDDactOFF<br>VSVDDactON | -<br>- | -<br>- | 8<br>9     | mA<br>mA                 |

| VS OPERATING RANGE                                     | •                                                                                                | •                         |        |        |            |                          |

| VS<br>Undervoltage Shutdown                            | VS falling OUTx = ON RL = $50 \Omega$                                                            | VSUVLO                    | 1.5    | 2.7    | 3.0        | V                        |

| VS<br>Undervoltage Shutdown<br>Hysteresis              |                                                                                                  | VSUVLOhys                 | -      | 1      | -          | V                        |

| VS<br>Minimum Operating Voltage                        | VS rising OUTx = ON RL = $50 \Omega$                                                             | VSmin                     | _      | -      | 4.0        | V                        |

| VDD OPERATING RANGE                                    |                                                                                                  |                           |        |        |            |                          |

| VDD<br>Lower Operating Voltage                         |                                                                                                  | VDDLOP                    | 3.0    | _      | 4.5        | V                        |

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} \\ (-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \ 3.0 \ \text{V} < \text{VDD} < 5.5 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \\ \text{IDLE} = \text{high unless otherwise specified})$

| Characteristic                                                                                     | Conditions                                                                                               | Symbol                   | Min          | Тур          | Max           | Unit                     |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------|--------------|--------------|---------------|--------------------------|

| VDD OPERATING RANGE                                                                                |                                                                                                          |                          |              |              |               |                          |

| VDD<br>Undervoltage Shutdown                                                                       | VDD falling<br>SI = SCLK = CSB = 0 V                                                                     | VDDUVLO                  | 1.0          | 2.7          | 3.0           | V                        |

| THERMAL REPEORMANCE                                                                                | SO from low to high impedance                                                                            |                          |              |              |               |                          |

| THERMAL PERFORMANCE                                                                                | T                                                                                                        |                          | 1            |              |               |                          |

| Thermal Shutdown                                                                                   | Note 11                                                                                                  | TSD                      | 150          | 175          | 200           | °C                       |

| Thermal Hysteresis                                                                                 | Note 11                                                                                                  | TSDhys                   | 10           | 25           | -             | °C                       |

| OUTPUT DRIVER                                                                                      |                                                                                                          |                          | _            |              |               |                          |

| Output Transistor RDSon                                                                            | IOUT = 220 mA<br>$T_J = 25$ °C<br>$T_J = 150$ °C                                                         | Rdson25<br>Rdson150      | -<br>-       | 0.9<br>1.6   | _<br>1.8      | Ω<br>Ω                   |

| Reverse Polarity ON Resistance                                                                     | VSx = -16 V<br>IOUT = 220 mA<br>Tj = 25°C<br>Tj = 150°C                                                  | Revpol25<br>Revpol150    | _<br>_       | 0.9<br>1.6   | <u>-</u><br>- | Ω<br>Ω                   |

| Overload Detection Current<br>1 <sup>st</sup> threshold (OVL0)<br>2 <sup>nd</sup> threshold (OVL1) |                                                                                                          | ILovI0<br>ILovI1         | 1.30<br>0.70 | 1.80<br>1.05 | 2.30<br>1.30  | A<br>A                   |

| Overload Shutdown<br>Delay Time                                                                    | Active Mode including Bulb Inrush Mode Individual channel operation BIM.OUTn = HWCR.PAR = 0 <sub>B</sub> | tOVLO                    | 4            | 7            | 11            | μs                       |

| Output Leakage                                                                                     | VS = VDD = 0 V<br>VOUT = 0 V<br>VDS = 28 V<br>Tj = 85°C<br>Tj = 150°C                                    | Leak85<br>Leak150        | -<br>-       | 0.01<br>0.1  | 0.5<br>5.0    | μ <b>Α</b><br>μ <b>Α</b> |

| Output Current<br>During Loss of Ground                                                            | RL = 50 Ω<br>VS = VS1 = VS2                                                                              | LOG                      | -2.0         | -            | _             | mA                       |

| Dropout Voltage                                                                                    | RL = 50 Ω<br>VS = VS1 = VS2 = 4 V                                                                        | Drop                     | -            | -            | 1             | V                        |

| Output Drain/Source Clamp                                                                          | IL = 20 mA<br>VS = VS1 = VS2 = 36 V                                                                      | clampDS                  | 42           | 46           | 54            | V                        |

| Output Source/GND Clamp                                                                            | IL = 20 mA<br>VS = VS1 = VS2 = 7 V                                                                       | clampSG                  | -25          | -            | -16           | V                        |

| MODE DELAY TIMES                                                                                   |                                                                                                          |                          |              |              |               |                          |

| Sleep to Idle Delay                                                                                | IDLE pin going high (50%)<br>To TER+INST register = 8680 <sub>H</sub>                                    | Slp2idl                  | -            | 200          | 400           | μs                       |

| Sleep to Limp Home Delay                                                                           | INx going high To VDS = 10%VS                                                                            | Slp2lh                   | -            | 300          | 600           | μs                       |

| Idle to Sleep Delay                                                                                | IDLE pin going low (50%) To Standard Diagnostics clearing = 0000 <sub>H</sub>                            | ldl2slp                  | -            | 100          | 200           | μs                       |

| Idle to Active Delay                                                                               | INx going high to MODE = 10 <sub>B</sub> From CSB going high To MODE = 10 <sub>B</sub>                   | Idl2actINx<br>Idl2actCSB | -<br>-       | 100<br>100   | 200<br>200    | μs<br>μs                 |

| Limp Home to Sleep Delay                                                                           | INx going low<br>To Standard Diagnostics<br>clearing = 0000 <sub>H</sub>                                 | Lh2slp                   | -            | 200          | 400           | μs                       |

| Limp Home to Active Delay                                                                          | IDLE going high To MODE=10 <sub>B</sub>                                                                  | Lh2act                   | -            | 50           | 100           | μs                       |

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} \\ (-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \ 3.0 \ \text{V} < \text{VDD} < 5.5 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \\ \text{IDLE} = \text{high unless otherwise specified})$

| Characteristic                    | Conditions                                           | Symbol                     | Min | Тур  | Max    | Unit |

|-----------------------------------|------------------------------------------------------|----------------------------|-----|------|--------|------|

| MODE DELAY TIMES                  |                                                      |                            |     |      |        |      |

|                                   | INx going low to MODE = 11 <sub>B</sub>              | Act2idIINx                 |     | 100  | 200    | μs   |

| Active to Idle Delay              | From CSB going high                                  |                            | -   |      |        |      |

|                                   | To MODE = 11 <sub>B</sub>                            | Act2idICSB                 |     | 100  | 200    | μs   |

|                                   | IDLE going low To TER + INST                         |                            |     |      |        |      |

|                                   | register=                                            |                            |     |      |        |      |

| Active to Limp Home Delay         | 8683 <sub>H</sub> (IN0 = VDD, IN1 = VDD)or           | Act2lh                     | _   | 50   | 100    | μs   |

|                                   | 8682 <sub>H</sub> (IN0 = GND, IN1 = VDD)or           |                            |     |      |        |      |

|                                   | 8681 <sub>H</sub> (IN0 = VDD, IN1 = GND)             |                            |     |      |        |      |

|                                   | IDLE going low                                       |                            |     |      |        |      |

| Active to Sleep Delay             | To Standard Diagnostics clearing = 0000 <sub>H</sub> | Act2slp                    | -   | 50   | 100    | μS   |

|                                   | Rload = 10K to GND                                   |                            |     |      |        |      |

| OUTPUT TIMING SPECIFICATION       | 1                                                    | 1                          |     |      |        |      |

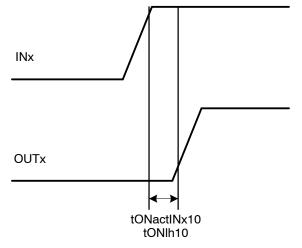

| Turn On Delay                     | VS = VS1 = VS2 = 13.5 V, RL = 50 Ω                   |                            |     |      |        |      |

|                                   | IN A ARRANGUET                                       | 1001 1101 10               |     | l .  |        |      |

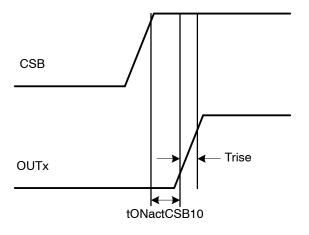

| Active Mode                       | INx to 10% VOUT CSB rising edge to 10% VOUT          | tONactINx10<br>tONactCSB10 | 1 1 | 4    | 8<br>8 | μS   |

|                                   | CSB fishing edge to 10% VCC1                         | IONACIOSETO                |     | 4    | 0      | μs   |

| Limp Home Mode                    | INx to 10% VOUT                                      | tONIh10                    | 1   | 4    | 8      | μs   |

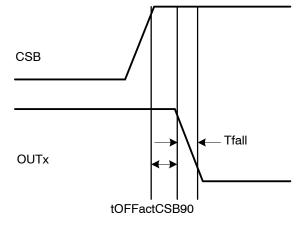

| Turn Off Delay                    | $VS = VS1 = VS2 = 13.5 \text{ V}, RL = 50 \Omega$    |                            |     |      |        |      |

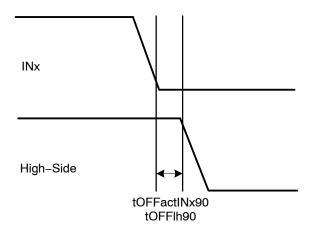

| Active Mode                       | INx to 90% VOUT                                      | tOFFactINx90               | 1   | 6    | 12     | μS   |

|                                   | CSB rising edge to 90% VOUT                          | tOFFactCSB90               | 1   | 6    | 12     | μs   |

| Limp Home Mode                    | INx to 90% VOUT                                      | tOFFlh90                   | 1   | 6    | 12     | μS   |

| Turn On / Turn Off Matching       |                                                      |                            |     |      |        |      |

| Active Mode                       | VS = VS1 = VS2 = 13.5 V,<br>RL = 50 Ω                | tMatchACT                  | -10 | 0    | 10     | μS   |

| Limp Home Mode                    | HL = 50 \$2                                          | tMatchLH                   | -10 | 0    | 10     | μs   |

| Rise Time Active Mode             | VS = VS1 = VS2 = 13.5 V, RL = 50 Ω                   | tRiseAct                   | 2.4 | 5.25 | 7.7    | μS   |

| Limp Home Mode                    | 30% to 70% VS                                        | tRiselh                    | 2.4 | 5.25 | 7.7    | μS   |

| Fall Time                         |                                                      |                            |     |      |        | P*-  |

| Active Mode                       | VS = VS1 = VS2 = 13.5 V, RL = 50 Ω                   | tFallAct                   | 2.8 | 5.25 | 7.7    | μS   |

| Limp Home Mode                    | 70% to 30% VS                                        | tFallIh                    | 2.8 | 5.25 | 7.7    | μs   |

| LIMP HOME TIMING                  | •                                                    | -                          | •   | •    |        |      |

| Limp Home Auto-Retry Times        |                                                      |                            |     |      |        |      |

| Limp Home Mode 0                  |                                                      | tRSTIh0                    | 7   | 10   | 13     | ms   |

| Limp Home Mode 1                  |                                                      | tRSTlh1                    | 14  | 20   | 26     | ms   |

| Limp Home Mode 2                  |                                                      | tRSTIh2                    | 28  | 40   | 52     | ms   |

| Limp Home Mode 3                  |                                                      | tRSTIh3                    | 56  | 80   | 104    | ms   |

| BULB INRUSH TIMING                | 1                                                    |                            | 1   | 1    |        |      |

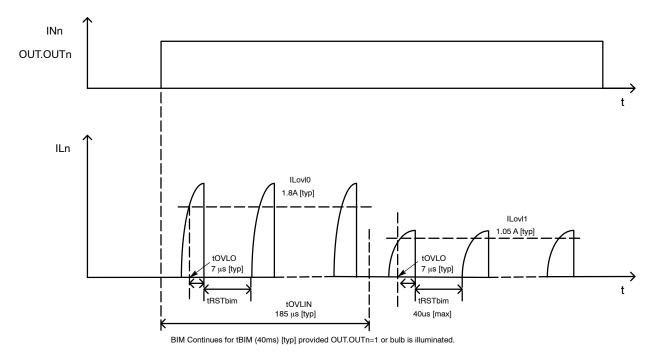

| Restart Time Bulb Inrush Mode     |                                                      | tRSTbim                    | _   | _    | 40     | μS   |

| Overload Current Switch Threshold |                                                      |                            |     |      |        | r    |

| Delay Time                        |                                                      | tOVLIN                     | 110 | 185  | 260    | μs   |

| Reset Time                        |                                                      |                            |     |      |        |      |

| Bulb Inrush Mode                  |                                                      | tBIM                       | -   | 40   | _      | ms   |

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} (-40 ^{\circ}\text{C} < \text{T}_{\text{J}} < 150 ^{\circ}\text{C}, \ 3.0 \ \text{V} < \text{VDD} < 5.5 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS1} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS3} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS3} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS3} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS3} = \text{VS2} < 18 \ \text{V}, \ 7 \ \text{V} < \text{VS} = \text{VS3} =$ IDLE = high unless otherwise specified)

| Characteristic                                                   | Conditions                       | Symbol    | Min | Тур | Max | Unit |

|------------------------------------------------------------------|----------------------------------|-----------|-----|-----|-----|------|

| PWM GENERATOR                                                    |                                  |           |     |     |     |      |

| Internal Frequency                                               | HWCR_PWM.ADJ = 1000 <sub>B</sub> | fINT      | 80  | 102 | 125 | kHz  |

| Internal Frequency Variation between Generator 0 and Generator 1 |                                  | fVAR      | -15 | -   | 15  | %    |

| Internal Frequency Synchronization Time (Note 5)                 | HWCR_PWM.ADJ = 1000 <sub>B</sub> | tSYNC     | -   | 5   | 10  | μs   |

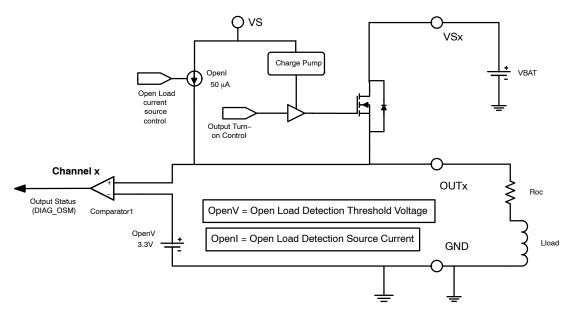

| OPEN LOAD OUTPUT STATUS MON                                      | IITOR                            |           |     |     |     |      |

| Output Status Monitor<br>Comparator Settling Time                |                                  | OpenT     | -   | -   | 20  | μs   |

| Output Status Monitor<br>Threshold Voltage                       |                                  | OpenV     | 3.0 | 3.3 | 3.6 | V    |

| Output Status Monitor Diagnostic Source Current                  |                                  | OpenI     | 25  | 50  | 100 | μΑ   |

| Open Load equivalent resistance                                  |                                  | OpenR     | 30  | -   | 300 | kΩ   |

| OPEN LOAD AT ON                                                  |                                  |           |     |     |     |      |

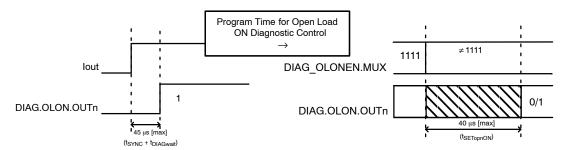

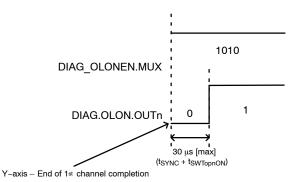

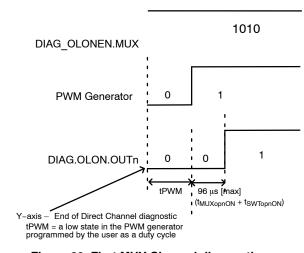

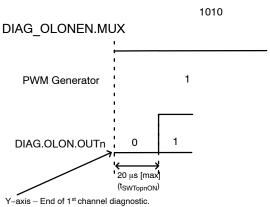

| Open Load ON<br>Wait for Diagnostic<br>(Note 6)                  |                                  | tDIAGwait | 6   | 15  | 35  | μs   |

| Open Load ON<br>Waiting Time<br>before mux activation (Note 7)   |                                  | tMUXopnON | 40  | 58  | 76  | μs   |

| Open Load ON<br>Settling Time (Note 8)                           |                                  | tSETopnON | -   | 20  | 40  | μs   |

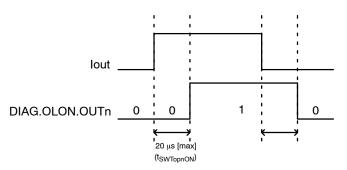

| Open Load ON<br>Channel Switching Time(Note 9)                   |                                  | tSWTopnON | _   | 10  | 20  | μs   |

| Open Load ON<br>Threshold Current                                |                                  | lopnON    | 1   | 6   | 10  | mA   |

- 5. Basis in timing requirements for

- i) Reset Overload Current Thresholds.

- ii) Auto-retry timing reset in limp home mode.

iii) Open Load at ON multiplex operation (but not direct channel diagnostic).

Time required to wait before programming for Open Load ON Diagnostic Control.

- Delay from PWM generator going high to fault recognized in DIAG\_OLON.OUT.

Delay from Open Load ON Diagnostic Control (with system fault) bit set to fault recognized in DIAG\_OLON.OUT.

Delay time between Open Load at ON event and to fault recognized in DIAG\_OLON.OUT.

#### **DIGITAL INTERFACE CHARACTERISTICS**

| Characteristic                                           | Conditions                         | Symbol                 | Min | Тур | Max | Unit |

|----------------------------------------------------------|------------------------------------|------------------------|-----|-----|-----|------|

| INPUT CHARACTERISTICS                                    |                                    |                        |     |     |     |      |

| Digital Input Threshold (IDLE, IN0, IN1, CSB, SCLK, SI)  |                                    | VthIn                  | 0.8 | 1.4 | 2.0 | V    |

| Digital Input Hysteresis (IDLE, IN0, IN1, CSB, SCLK, SI) |                                    | Vhysln                 | 50  | 175 | 300 | mV   |

| Input Pull-down Resistance<br>(IDLE, IN0, IN1, SI, SCLK) | IDLE = IN0 = IN1 = SI = SCLK = VDD | Rpdx                   | 50  | 120 | 190 | kΩ   |

| Input Pull-up Resistance (CSB)                           | CSB = 0 V                          | RpdCSBx                | 50  | 120 | 190 | kΩ   |

| CSB Leakage to VDD                                       | CSB = 5 V, VDD = 0 V               | IlkgCSBV <sub>DD</sub> | -   | -   | 100 | μΑ   |

# **DIGITAL INTERFACE CHARACTERISTICS (continued)**

| Characteristic                       | Conditions                                         | Symbol       | Min         | Тур | Max | Unit |  |

|--------------------------------------|----------------------------------------------------|--------------|-------------|-----|-----|------|--|

| OUTPUT CHARACTERISTICS               |                                                    |              |             |     |     |      |  |

| SO – Output High                     | I(out) = 1.5 mA                                    | VsoH         | VDD-<br>0.4 | -   | VDD | V    |  |

| SO – Output Low                      | I(out) = −2.0 mA                                   | VsoL         | -           | -   | 0.4 | V    |  |

| SO Tri-state Leakage                 | CSB = VDD, 0 V < SO < VDD                          | IlkzSOtstate | -1          | -   | 1   | μΑ   |  |

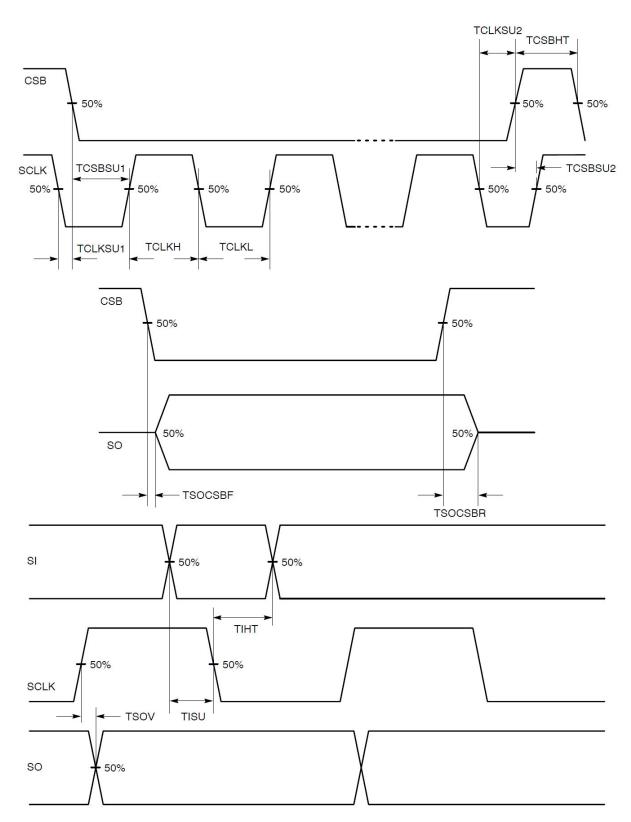

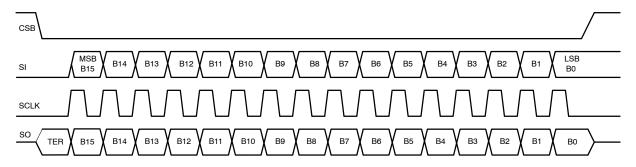

| SPI TIMING (VDD = 4.5 V and VS       | 5 > 7 V)                                           |              |             |     |     |      |  |

| SCLK Frequency                       |                                                    | Fclk         | _           | -   | 5   | MHz  |  |

| SCLK Clock Period                    |                                                    | TpClk        | 200         | -   | -   | ns   |  |

| SCLK High Time                       |                                                    | TCLKH        | 85          | -   | -   | ns   |  |

| SCLK Low Time                        |                                                    | TCLKL        | 85          | -   | -   | ns   |  |

| SCLK Setup Time<br>To CSB going low  | Falling SCLK to falling CSB                        | TCLKSU1      | 85          | -   | -   | ns   |  |

| SCLK Setup Time<br>To CSB going high | Falling SCLK to rising CSB                         | TCLKSU2      | 85          | -   | -   | ns   |  |

| SI Setup Time                        |                                                    | TISU         | 50          | -   | -   | ns   |  |

| SI Hold Time                         |                                                    | TIHT         | 50          | -   | -   | ns   |  |

| CSB Setup Time                       |                                                    | TCSBSU1      | 100         | -   | -   | ns   |  |

| CSB Setup Time                       |                                                    | TCSBSU2      | 100         | -   | -   | ns   |  |

| CSB High Time                        | (Note 10)                                          | TCSBHT       | 5.0         | -   | -   | μs   |  |

| SO enable<br>after CSB falling edge  |                                                    | TSOCSBF      | -           | -   | 200 | ns   |  |

| SO disable<br>After CSB rising edge  |                                                    | TSOCSBR      | -           | -   | 200 | ns   |  |

| SO Rise Time                         | Cload = 40 pF (Note 11)                            | TSOrise      | -           | 10  | 25  | ns   |  |

| SO Fall Time                         | Cload = 40 pF (Note 11)                            | TSOfall      | -           | 10  | 25  | ns   |  |

| SO Valid Time                        | Cload 40 pF (Note 11)<br>SCLK rising 80% to SO 50% | TSOV         | -           | 50  | 100 | ns   |  |

<sup>10.</sup> This is the minimum time the user must wait between SPI commands.

11. Not production tested.

Figure 4. Serial Turn On

Figure 5. Serial Turn Off

Figure 6. INx Control Turn On

Figure 7. INx Control Turn Off

Figure 8. Serial Peripheral Interface Detailed Timing

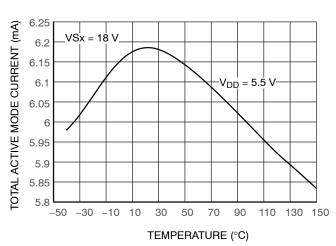

#### **TYPICAL PERFORMANCE GRAPHS**

1.850 TOTAL IDLE CURRENT (mA) 1.800 1.750 VSx = 18 V VDD = 5.5 V 1.700 1.650 1.600 1.550 1.500 -50 0 50 100 150 TEMPERATURE (°C)

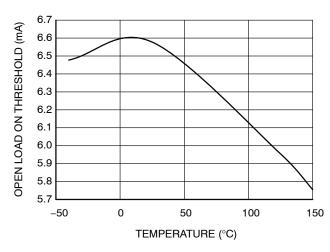

Figure 9. Open Load On Threshold vs. Temperature

Figure 10. Total Idle Current vs. Temperature

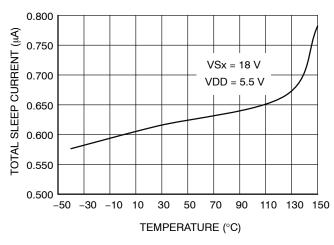

Figure 11. Total Sleep Current vs. Temperature

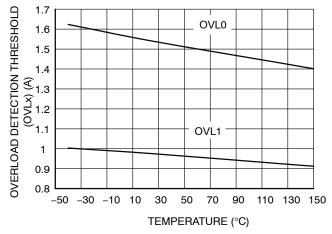

Figure 12. Overload Threshold vs. Temperature

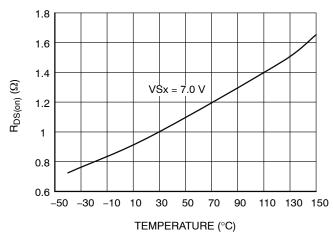

Figure 13. R<sub>DS(on)</sub> vs. Temperature

Figure 14. Total Active Mode Current vs. Temperature

#### **DETAILED OPERATING DESCRIPTION**

#### **General Overview**

The NCV7755 is comprised of eight DMOS high-side power drivers. There are two connection pins (VS1, VS2) for the drain of each output driver with 4 common drivers per pin. Communication to the device is through a 16-bit SPI port for output control, programming, and fault reporting. The device also features a limp home mode with an IDLE control pin for limp home entry and two input control pins (IN0 & IN1) for output engagement.

Output loads can be varied from inductive loads, bulb loads, or LED loads. Special features for each load type include output clamps, in-rush design considerations, and two on-chip PWM generators.

The NCV7755 allows independent mapping of the INx pins to the outputs and independent mapping of the two PWM generators to the outputs.

The device is capable of running down to VS = 3 V for automotive cranking events.

#### **Power Supply**

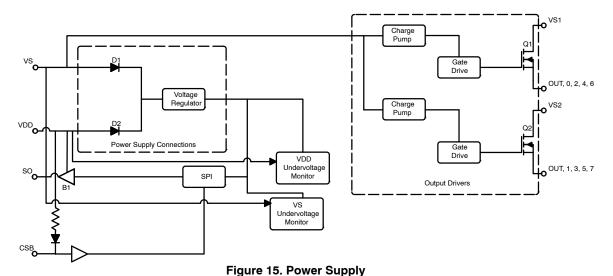

There are four power supply input requirements. The descriptions of their internal connections are listed below.

- VS Analog Supply Input Battery input for all internal analog circuitry. The maximum current drain is 8.7 mA over temperature

- VS1 Output Driver Drain connection for OUT0, OUT2, OUT4, OUT6. The maximum current is internally limited by the maximum overload detection threshold of 2.3 A (each channel)

- VS2 Output Driver Drain connection for OUT1, OUT3, OUT5, OUT7. The maximum current is

- internally limited by the maximum overload detection threshold of 2.3 A (each channel)

- VDD Digital Supply Input Internal logic supply input. Runs from 3.3 V input or 5 V input. The maximum current drain is 3.5 mA over temperature

It's important to note the maximum combined current drain of both VS and VDD is specified at 9 mA with the channels on.

Sleep mode current for VS is 3  $\mu$ A at 85°C and the maximum combination of VS+VDD is 5  $\mu$ A at 85°C.

The exposed pad connection should be connected to ground with as large a pc board metal connection as possible for best thermal performance and EMC considerations. However this is not a ground connection for IC ground currents.

Load Dump – During a peak transient event such as automotive load dump the outputs maintain their operation up to the maximum rating for Positive Transient input supply voltage of 42 V as programmed via SPI or the input control pins INO and IN1.

Cranking Conditions – Automotive cranking conditions can cause the battery (aka VS) to dip to low levels. In order to maintain circuit operation down to the lowest possible levels the battery connection is OR'd with the logic supply voltage (VDD). Diodes D1 and D2 provide the OR'd condition into the voltage regulator. The reduction or removal of current into D1 from VS will cause the current into D2 from VDD to increase to keep the voltage regulator alive. Additional current can also come from SO.

#### Power-Up/Power-Down Control

VDD and VS each has their own Power–On reset monitors which serve to hold off proper operation until sufficient voltage is present to control the output device. The device powers up with sufficient voltage on either or both VDD or VS, and INx or IDLE pin are high. The Standard Diagnostic Register initially reports both VS Undervoltage (Monitor) and VDD Lower Operating Range (Monitor).

SPI communication is present with sufficient voltage on VDD. An undervoltage on VDD resets all the registers to their default values and no SPI communication is available, although memory of Overload / Overtemperature conditions is maintained in ERR of the Standard Diagnostics Register and can be retrieved when VDD is present. If VS is present with VDD undervoltage, Limp Home mode control is possible.

Sufficient voltage on VS allows for output turn-on. During cranking conditions as VS dips, the diode OR'd circuit described in the previous section allows for the IC to maintain current into the logic solely from VDD. All channels which are on keep their state during cranking unless commanded to turn off. Channel turn-on may not be possible during cranking.

VDD Low Operation Voltage – VDD is monitored and its status is reported in the Diagnostic Register as bit 13 (LOPVDD). The default value is set to a "1" during power up and is continuously monitored for the electrical parameter VDD Lower Operating Voltage (between 3.0 V and 4.5 V). Because of this threshold, operation for VDD with a 3.3 V supply will continuously report a "1" in this register. The LOPVDD bit can only be reset by reading the Standard Diagnostic Register.

# **DIAGNOSTIC REGISTER (Default listing after Power-up or Reset)**

| Field  | State | Description                               |

|--------|-------|-------------------------------------------|

| UVRVS  | 1     | There was an undervoltage condition on VS |

| LOPVDD | 1     | VDD was previously below 4.5 V            |

| MODE   | 11    | Idle Mode (2 bits)                        |

| TER    | 1     | Previous transmission failed              |

| OLON   | 0     | No open load ON detected                  |

| OLOFF  | 0     | No open load OFF detected                 |

| ERR    | 0     | No Failure detected                       |

#### INST REGISTER (This is the 1st Register Read back after a Logic Reset)

| Field | State   | Description                   |  |

|-------|---------|-------------------------------|--|

| INST  | TER = 1 | Previous transmission failed. |  |

|       | INx = 0 | Input pins are set low        |  |

# **DEFAULT LISTING AFTER LOGIC RESET**

| Field       | Description                                                  |

|-------------|--------------------------------------------------------------|

| OUT         | Output is off                                                |

| BIM         | Output latches off with overload                             |

| MAPIN0      | IN0 is mapped to OUT2                                        |

| MAPIN1      | IN1 is mapped to OUT3                                        |

| INST        | Previous transmission failed. Input pins are set low         |

| DIAG_IOL    | Diagnostic current is not enabled                            |

| DIAG_OSM    | Voutx is less than the Output Monitor Threshold              |

| DIAG_OLON   | Normal operation                                             |

| DIAG_OLONEN | Open Load ON not active                                      |

| HWCR        | Normal operation, no reset command, no parallel combinations |

| HWCR_OCL    | Normal operation, no latch clear                             |

| HWCR_PWM    | PWM generator 1 not active. PWM generator 0 not active       |

| PWM_CR0     | Generator 0 Base Frequency Internal clock divided by 1024    |

| PWM_CR1     | Generator 1 Base Frequency Internal clock divided by 1024    |

| PWM_OUT     | The selected output is not driven by a PWM generator         |

| PWM_MAP     | The selected output is connected to PWM Generator 0          |

Table 1. DEVICE CAPABILITY AS A FUNCTION OF VS AND VDD

|                                           | VDD < VDDUVLO (Note 15)                                                    | VDD = VDDLOP (Note 16)                                                     | VDD > VDDLOP (Note 17)                                                     |

|-------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| VS < 3.0 V (Note 12)                      | Channels –<br>Cannot be controlled                                         | Channels –<br>Cannot be controlled                                         | Channels –<br>Cannot be controlled                                         |

|                                           | SPI registers – Reset                                                      | SPI registers - Available                                                  | SPI registers - Available                                                  |

|                                           | SPI communication –<br>Not available                                       | SPI communication – Possible (fsclk = 1 MHz)                               | SPI communication – Possible (fsclk = 5 MHz)                               |

|                                           | Limp Home Mode –<br>Not available                                          | Limp Home Mode –<br>Available (channels are off)                           | Limp Home Mode –<br>Available (channels are off)                           |

| <b>3.0 V &lt; VS &lt; VSmin</b> (Note 13) | Channels –<br>Cannot be controlled by SPI                                  | Channels – Can be controlled by SPI (Rdson deviations possible).           | Channels – Can be controlled by SPI (Rdson deviations possible).           |

|                                           | SPI registers - Reset                                                      | SPI registers - Available                                                  | SPI registers - Available                                                  |

|                                           | SPI communication –<br>Not available                                       | SPI communication – Possible (fsclk = 1 MHz)                               | SPI communication – Possible (fsclk = 5 MHz)                               |

|                                           | Limp Home Mode – Available (Rdson deviations possible)                     |                                                                            | Limp Home Mode – Available (Rdson deviations possible)                     |

| VS > VSmin (Note 14)                      | Channels –<br>Cannot be controlled by SPI                                  | Channels – Can be controlled by SPI (Rdson deviations possible).           | Channels – Can be controlled by SPI (Rdson deviations possible).           |

|                                           | SPI registers – Reset                                                      | SPI registers - Available                                                  | SPI registers - Available                                                  |

|                                           | SPI communication –<br>Not available                                       | SPI communication – Possible (fsclk = 5 MHz)                               | SPI communication – Possible (fsclk = 5 MHz)                               |

|                                           | Limp Home Mode – Available<br>(Rdson deviations possible<br>with VS < 7 V) | Limp Home Mode – Available<br>(Rdson deviations possible<br>with VS < 7 V) | Limp Home Mode – Available<br>(Rdson deviations possible<br>with VS < 7 V) |

<sup>12. (</sup>Undervoltage Shutdown max specification VUVLO = 3 V)

13. VSmin = (Minimum Operating Voltage)

14. VSmin = (Minimum Operating Voltage)

15. VDDUVLO = VDD Undervoltage Shutdown

16. VDDLOP = VDD Lower Operating Voltage

17. VDDLOP = VDD Lower Operating Voltage

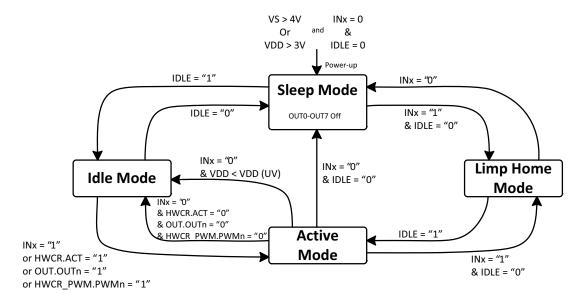

# **Modes of Operation**

There are 4 modes of operation. Each is presented in the state diagram below.

1. Sleep Mode

- 2. Idle Mode

- 3. Active Mode

- 4. Limp Home Mode

Figure 16. Modes of Operation

# TABLE 2. DEVICE FUNCTION VERSUS VS AND VDD VOLTAGES

| Operation Mode | Function          |                                                | lervoltage<br>DDUVLO | VS<br>Undervoltage<br>VDD > VDDUVLO | VS no<br>Undervoltage<br>VDD <vdduvlo< th=""><th>VS no<br/>Undervoltage<br/>VDD &gt; VDDUVLO</th></vdduvlo<> | VS no<br>Undervoltage<br>VDD > VDDUVLO |  |  |

|----------------|-------------------|------------------------------------------------|----------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|

| Sleep          | Channels          |                                                |                      |                                     | Channels not available                                                                                       |                                        |  |  |

|                | SPI Communication |                                                |                      |                                     | no SPI communication<br>SPI Register Reset                                                                   |                                        |  |  |

|                | SPI Registers     | _                                              |                      |                                     | or rriegister rieset                                                                                         |                                        |  |  |

| idle           | Channels          | ailable<br>cation                              | set                  | х                                   | 0                                                                                                            | х                                      |  |  |

|                | SPI Communication | not av<br>nmuni                                | er<br>Re             | 0                                   | х                                                                                                            | ⊗                                      |  |  |

|                | SPI Registers     | Channels not available<br>oo SPI communication | SPI Register Reset   | 0                                   | reset                                                                                                        | <b>Ø</b>                               |  |  |

| Active         | Channels          | Cha<br>no S                                    | SP                   | х                                   | (INx pins only)                                                                                              | <b>②</b>                               |  |  |

|                | SPI Communication |                                                |                      | 0                                   | х                                                                                                            | 0                                      |  |  |

|                | SPI Registers     |                                                |                      | 0                                   | reset                                                                                                        | 0                                      |  |  |

| Limp Home      | Channels          |                                                |                      | х                                   | (INx pins only)                                                                                              | (INx pins only)                        |  |  |

|                | SPI Communication |                                                |                      | 🧭 (read only)                       | х                                                                                                            | (read only)                            |  |  |

|                | SPI Registers     |                                                |                      | (read only)                         | reset                                                                                                        | (read only)                            |  |  |

#### Power-up

The power-up condition for the NCV7755 is an OR'd condition between the VS battery input and the VDD logic input. Either of the supplies exceeding their minimum operative voltage (4.0 V max for VS) or (3.0 V for VDD) will initiate the internal power-on sequence. In addition to these low voltage attributes, the device will maintain its state with battery voltages down to VS = 3 V such as during cranking. For SPI communication, the digital power supply must also be maintained at > 3 V.

#### Sleep Mode

The NCV7755 enters sleep mode when pins IDLE and IN0 and IN1 are all low. All outputs are off and all SPI registers are reset. Operating current is at a minimum (3  $\mu$ A max at 85°C).

#### **Idle Mode**

The device enters Idle Mode when the IDLE pin is brought high with INO and IN1 low. All channels are off and Open Load Diagnostic Current is off. The internal regulator powers on and SPI registers and communication become active with a proper logic supply voltage (VDD). Overload / Overtemperature bits are not cleared when entering Idle mode from active mode for safety reasons.

#### **Active Mode**

The normal operational mode for the device is Active Mode. The high-side drivers can be activated, loads can be driven, device output status can be retrieved, and device attributes can be programmed. The device enters active mode with any of the following commands.

- IDLE is high and IN0 or IN1 is set to a one

- IDLE is high and the Hardware Configuration Register (HWCR.ACT) is set to a 1<sub>B</sub> via a SPI command

- IDLE is high and the Power Output Control Register (OUT.OUTn) is set to a 1<sub>B</sub> for one or more of the outputs via a SPI command

- IDLE is high and a PWM Configuration Register (HWCR.PWM.PWMn) is set active via a SPI command

Any transition into Active Mode institutes a communication link between INO, IN1 and OUT2, OUT3.

#### **DIGITAL MODE CHART**

| MODE      | IDLE | INO   | IN1    |

|-----------|------|-------|--------|

| Sleep     | 0    | 0     | 0      |

| IDLE      | 1    | 0     | 0      |

| Active*   | 1    | 1 and | l/or 1 |

| Limp Home | 0    | 1 and | d/or 1 |

\*Additionally, Active Mode can be entered via SPI control.

| Hardware Configuration Register - HWCR.ACT = 1 |

|------------------------------------------------|

| Power Output Control Register – OUT.OUT = 1    |

| PWM Configuration Register – HWCR_PWM.PWMn = 1 |

#### **Limp Home Mode**

Only Channel 2 and 3 are controlled (via IN0 and IN1) during Limp Home Mode. Limp Home mode requires only VS and VSx for driver turn—on. VDD is not required. The device enters Limp Home Mode when the IDLE pin is low and IN0 and/or IN1 are high. When IN0 is high, channel 2 turns on. When IN1 is high, channel 3 turns on. These two input control pins and corresponding channels are also active after a power up condition.

SPI communication is active (with VDD>VDDUVLO) in read—only mode only and reports Overload and Overtemperature faults, and will also continue to monitor for Output Status Monitor conditions (on all channels), but Open Load Diagnostic Current is inactive (on all channels).

When entering Limp Home Mode, the Undervoltage Monitor (UVRVS) and Lower Operating Range Monitor (LOPVDD) bits are set to  $1_{\rm B}$  while the Open Load ON (OLON) State and Open Load OFF (OLOFF) State are set to  $0_{\rm B}$ . The Transmission Error bit (TER) is set to "1" for the first SPI command which is sent back with the INST register returned with the first SPI command, and will act normally afterwards.

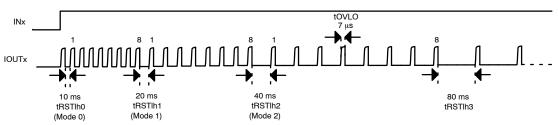

The NCV7755 incorporates an auto-retry function for highly capacitive loads in Limp Home Mode. In normal operation (Active Mode), the device can compensate for capacitive loads (in case of Overload, Short Circuit or Overtemperature) with the external microprocessor drive control time, but when in Limp Home Mode this is not possible. Attempted tries to turn on an output with a constant input high control when exposed to Overload (Ilovl0), Short Circuit or Overtemperature will occur with the following characteristics.

- 10 ms (8 retries)

- 20 ms (8 retries)

- 40 ms (8 retries)

- 80 ms (continuously)

It is important to note the 8 counts do not include the initial turn—on attempt of the device.

A reset to the initial 8 retries at 10 ms can be realized with a low on the input of 2 times the Internal Frequency Synchronization Time (typically  $2 \times 5 \mu s$ ).

\*IlovI0 - This is the higher current threshold used in Active Mode.

Figure 17.

# **Output Control**

The 8 outputs can be controlled via 4 ways which are listed below.

- 1. Output Control via SPI. Commands to turn a device on are input through the SPI interface.

- Output Control via IN0 and/or IN1. To activate this, a SPI command must be sent to map the control to either IN0 (MAPIN0) or IN1 (MAPIN1). By default, mapping of IN0 and IN1

- are set to OUT2 (IN0) and OUT3 (IN1) after power-up.

- 3. Limp Home Mode A low on IDLE will allow control of OUT2 (IN0) and OUT3 (IN1).

- 4. PWM Control A SPI command can connect any of the outputs to either of 2 PWM generators whose properties for frequency and duty cycle are programmable.

Figure 18. Output Control

#### **OUTPUTS**

The 8 outputs of the NCV7755 are designed to work with multiple types of loads and with the capability of paralleling two paired channels.

#### **Resistive Loads**

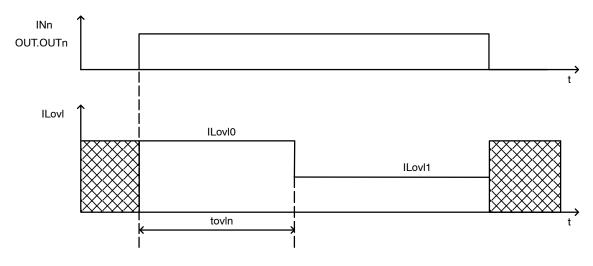

Resistive loads are primarily concerned with output current, switching delays, and slew rates. The NCV7755 has two overload thresholds. The  $1^{st}$  overload threshold is 1.3~A (min) and has an overload current switch threshold delay time (tOVLIN) of  $110~\mu s$  (min) triggered by OUT.OUTn. Once this delay time has been exceeded, the overload threshold reduces to 0.7~A (min). Turn–on delay time is 8~u s (max) and turn–off delay time is  $12~\mu s$  (max). Rise and fall times are both  $2.8~\mu s$  (min).

A turn off time longer than 2 x Internal Frequency Synchronization Time will reset the overload threshold back to the 1st level.

#### Relays

Relay loads are supported using an internal inductive clamp on the output driver to protect the driver. The negative transients seen when turning off an inductive load are internally limited on the output drivers with a clamp voltage minimum of -25 V. Paired output drivers are permissible with the use of the paired channel synchronization handling of overload and overtemperature conditions.

#### **Bulbs**

The NCV7755 is designed to drive 2 W lamps or 5 W lamps (using two channels in parallel) with its Bulb Inrush feature. Incandescent bulb in-rush characteristics are exhibited as a high current event due to the bulb filament initial low resistance. As the bulb heats up the resistance increases. Initial high currents could trigger an overload condition latching off the output. Setting a bit in the Bulb Inrush Mode register (BIM) allows the device to latch off (and report ERRn during that time [tRSTbim]) and automatically restart after the Bulb Inrush Mode Restart Time of 40 µs (max). Overtemperature conditions can also trigger a latch off event and auto-restart. The auto-restart helps to increase the bulb resistance putting the overload threshold out of range. Bulb Inrush Mode continues until the bulb is illuminated (not in overload) or the Bulb Inrush Mode reset time is reached (typically 40 ms). Dual Overload Detection Current thresholds continue to be valid in Bulb Inrush Mode.

Figure 19. Bulb In-rush Mode

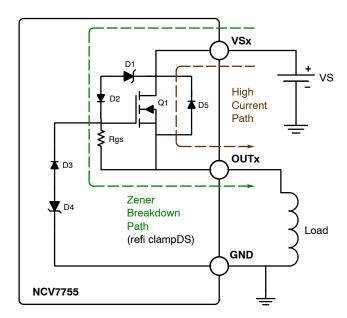

#### **Output Clamping**

Internal protection is provided for the output drivers for the maximum drain to source voltage and the absolute maximum voltage from the output to negative voltages which occurs on OUTx when inductive loads are turned off.

D1

High

Current

Path

D4

Breakdown

Path

(refi clampSG)

NCV7755

Figure 20. Output Clamp (Normal Operation)

Protection for Q1 drain to source is provided by D1, D2, and Rgs.

Protection for negative clamp voltages is provided by Rgs, D3, and D4.

Figure 21. Output Clamp (at High Voltage)

#### **Outputs in Parallel**

The NCV7755 was designed for operation with the capability to parallel some of the outputs for increased current handling for an individual load. This is not recommended for most other integrated circuits due to the asynchronous turn-off of paralleled outputs causing undo stress to the last channel on. The channels in the list below are allowed to run in parallel by programming the Hardware

Configuration Register (HWCR.PAR) which can deactivate both channels synchronously during an overload or overtemperature event.

Please note during Limp Home Mode only Channel 2 and Channel 3 are active. Because a parallel combination of channels 2 and 3 is not allowed, there is no provision for parallel outputs during Limp Home Mode.

| Parallel Co    |                         |   |

|----------------|-------------------------|---|

| Channel Number | HWCR.PAR<br>Bit address |   |

| 0              | 2                       | 0 |

| 1              | 3                       | 1 |

| 4              | 6                       | 2 |

| 5              | 7                       | 3 |

#### **Fault Detection**

Overload

Two overload current thresholds (ILovl0 & ILovl1) triggered by a turn-on command support the designer in driving highly capacitive loads. A higher initial current threshold (ILovl0) ignores potential in-rush events caused by high capacitance. The 2<sup>nd</sup> level supports maintenance of

lower IC temperature levels during any shorted events while still providing proper operation.

This multi-level threshold strategy is implemented whenever the driver is active on. When operating in Bulb-Inrush mode (BIM), the auto-restart feature will also be active.

Overload detection conditions are latched off and require a SPI command to reactivate the effected output.

Figure 22.

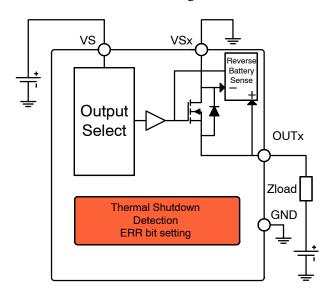

Thermal Shutdown – Individual thermal sensors are provided for each channel. A breach of the thermal shutdown threshold will latch the channel off and set the diagnostic bit ERRn for the channel. Clearing the error bit is done by setting the corresponding HWCR\_OCL.OUTn bit to "1". HWCR\_OCL.OUTn is cleared after the error bit is cleared and the channel will accept commands to turn on.

During Bulb Inrush Mode, the output is "latched" off when the thermal threshold is breached, and will auto-restart once the thermal sensor no longer detects a fault

#### **FAULT REPORTING**

#### ERRn, Overload & Overtemperature

Short to Ground – Overload conditions or Overtemperature conditions latch off the affected channel and the diagnostic bit ERRn is set. Reactivation must be via the SPI commands in normal operation using HWCR\_OCL.OUTn. The logic inputs will not reset the latch. Limp Home Mode however utilizes an output restart time.

After a breach of the ILovl0 or Ilovl1 level the channel is latched off and an error diagnostic bit is set (ERRn). Clearing the error bit is done by setting the corresponding HWCR\_OCL.OUTn bit to "1". HWCR\_OCL.OUTn is

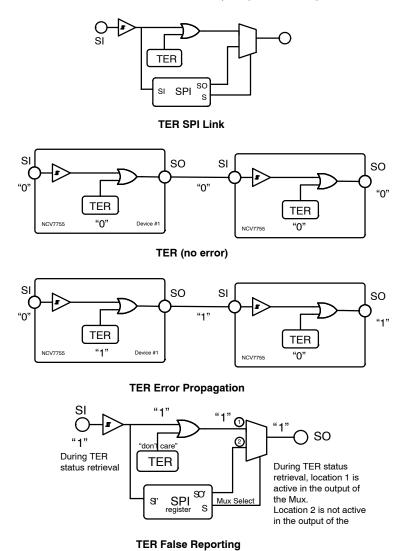

cleared after the error bit is cleared and the channel will accept commands to turn on.