# ANALOG Low Voltage Microphone Preamplifier with Variable Compression and Noise Cating **Variable Compression and Noise Gating**

SSM2167 **Data Sheet**

## **FEATURES**

Complete microphone conditioner in a 10-lead package Single 3 V operation Low shutdown current  $< 2 \mu A$ Adjustable noise gate threshold Adjustable compression ratio Automatic limiting feature prevents ADC overload Low noise and distortion: 0.2% THD + N 20 kHz bandwidth

# **APPLICATIONS**

Desktop, portable, or palmtop computers Telephone conferencing **Communication headsets Two-way communications** Surveillance systems Karaoke and DJ mixers

### **GENERAL DESCRIPTION**

The SSM2167 is a complete and flexible solution for conditioning microphone inputs in personal electronics and computer audio systems. It is also excellent for improving vocal clarity in communications and public address systems. A low noise voltage controlled amplifier (VCA) provides a gain that is dynamically adjusted by a control loop to maintain a set compression characteristic. The compression ratio is set by a single resistor and can be varied from 1:1 to over 10:1 relative to the fixed rotation point. Signals above the rotation point are limited to prevent overload and to eliminate popping. A downward expander (noise gate) prevents amplification of background noise or hum. This results in optimized signal levels prior to digitization, thereby eliminating the need for additional gain or attenuation in the digital domain. The flexibility of setting the compression ratio and the time constant of the level detector, coupled with two values of rotation point, make the SSM2167 easy to integrate in a wide variety of microphone conditioning applications.

The device is available in a 10-lead MSOP package, and is guaranteed for operation over the extended industrial temperature range of -40°C to +85°C.

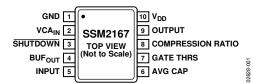

#### PIN CONFIGURATION

Figure 1. 10-Lead MSOP (RM Suffix)

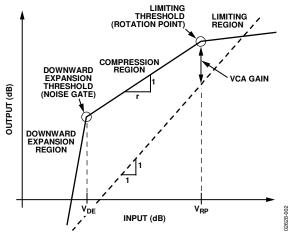

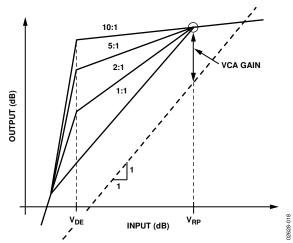

Figure 2. General Input/Output Characteristics

# **TABLE OF CONTENTS**

| Features                                                                          |

|-----------------------------------------------------------------------------------|

| Applications1                                                                     |

| General Description                                                               |

| Pin Configuration1                                                                |

| Revision History                                                                  |

| Specifications                                                                    |

| Absolute Maximum Ratings                                                          |

| Thermal Resistance                                                                |

| ESD Caution4                                                                      |

| Typical Performance Characteristics                                               |

| Applications Information                                                          |

| REVISION HISTORY                                                                  |

| 9/11—Rev. F to Rev. G                                                             |

| Changes to Ordering Guide                                                         |

| 2/11—Rev. E to Rev. F                                                             |

| Added Storage Temperature Range Parameter to Table 2                              |

| 6/09—Rev. D to Rev. E                                                             |

| Change to Signal Path Section                                                     |

| 2/09—Rev. C to Rev. D                                                             |

| Changes to Figure 4, Figure 5, Figure 6, and Figure 7 5 Changes to Ordering Guide |

| 11/07—Rev. B to Rev. C                                                            |

| Updated Format                                                                    |

| Theory of Operation8                                       |

|------------------------------------------------------------|

| Signal Path8                                               |

| Level Detector9                                            |

| Control Circuitry9                                         |

| Setting the Compression Ratio9                             |

| Setting the Noise Gate Threshold (Downward Expansion) . 10 |

| Rotation Point (Limiting)10                                |

| Shutdown Feature                                           |

| PCB Layout Considerations                                  |

| Outline Dimensions                                         |

| Ordering Guide11                                           |

|                                                            |

|                                                            |

| Updated Outline Dimensions                                 |

| Changes to Ordering Guide                                  |

| 9/03—Rev. A to Rev. B                                      |

| Deleted SSM2167-2 Model                                    |

| Changes to Ordering Guide                                  |

| Updated Outline Dimensions                                 |

| 3/02—Rev. 0 to Rev. A                                      |

| Edits to Specifications2                                   |

| Edits to Figure 2 and Figure 36                            |

| 7/01—Revision 0: Initial Version                           |

# **SPECIFICATIONS**

$V_{\text{S}} = 3.0 \text{ V}, f = 1 \text{ kHz}, R_{\text{L}} = 100 \text{ k}\Omega, R_{\text{COMP}} = 0 \text{ }\Omega, T_{\text{A}} = 25 ^{\circ}\text{C}, V_{\text{IN}} = 100 \text{ mV rms}, R_{\text{GATE}} = 2 \text{ k}\Omega, unless \text{ otherwise noted}.$

Table 1.

| Parameter                         | Symbol           | Test Conditions/Comments                 | Min | Тур  | Max | Unit   |

|-----------------------------------|------------------|------------------------------------------|-----|------|-----|--------|

| AUDIO SIGNAL PATH                 |                  |                                          |     |      |     |        |

| Voltage Noise Density             | e <sub>n</sub>   | 10:1 compression                         |     | 20   |     | nV/√Hz |

| Noise                             |                  | 20 kHz bandwidth, V <sub>IN</sub> = GND  |     | -70  |     | dBV    |

| Total Harmonic Distortion + Noise | THD + N          | $V_{IN} = 100 \text{ mV rms}$            |     | 0.2  |     | %      |

| Input Impedance                   | Z <sub>IN</sub>  |                                          |     | 100  |     | kΩ     |

| Output Impedance                  | Z <sub>OUT</sub> |                                          |     | 145  |     | Ω      |

| Load Drive                        |                  | Minimum resistive load                   |     | 5    |     | kΩ     |

|                                   |                  | Maximum capacitive load                  |     | 2    |     | nF     |

| Input Voltage Range               |                  | 0.4% THD + N                             |     | 600  |     | mV rms |

| Output Voltage Range              |                  | 0.4% THD + N                             |     | 700  |     | mV rms |

| Gain Bandwidth Product            |                  | 1:1 compression, VCA G = 18 dB           |     | 1    |     | MHz    |

| CONTROL SECTION                   |                  |                                          |     |      |     |        |

| VCA Dynamic Gain Range            |                  |                                          |     | 40   |     | dB     |

| VCA Fixed Gain                    |                  |                                          |     | 18   |     | dB     |

| Compression Ratio, Minimum        |                  |                                          |     | 1:1  |     |        |

| Compression Ratio, Maximum        |                  | See Table 4 for R <sub>COMP</sub>        |     | 10:1 |     |        |

| Rotation Point                    |                  |                                          |     | 63   |     | mV rms |

| Noise Gate Range                  |                  | Maximum threshold                        |     | -40  |     | dBV    |

| POWER SUPPLY                      |                  |                                          |     |      |     |        |

| Supply Voltage                    | V <sub>SY</sub>  |                                          | 2.5 |      | 5.5 | V      |

| Supply Current                    | Isy              |                                          |     | 2.3  | 5   | mA     |

| DC Output Voltage                 |                  |                                          |     | 1.4  |     | V      |

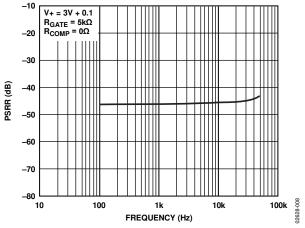

| Power Supply Rejection Ratio      | PSRR             | $V_{SY} = 2.5 \text{ V to } 6 \text{ V}$ |     | 45   |     | dB     |

| SHUTDOWN                          |                  |                                          |     |      |     |        |

| Supply Current                    | Isy              | Pin 3 = GND                              |     | 2    | 8   | μΑ     |

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| Supply Voltage                       | 6 V             |

| Input Voltage                        | 6 V             |

| Operating Temperature Range          | -40°C to +85°C  |

| Storage Temperature Range            | −65°C to +150°C |

| Junction Temperature                 | 150°C           |

| Lead Temperature (Soldering, 10 sec) | 300°C           |

| 883 (Human Body) Model               | 500 V           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# THERMAL RESISTANCE

$\theta_{JA}$  is specified for worst-case conditions, that is,  $\theta_{JA}$  is specified for a device soldered in a 4-layer circuit board for surface-mount packages.

Table 3.

| Package Type      | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|-------------------|-----------------|-----------------|------|

| 10-Lead MSOP (RM) | 180             | 35              | °C/W |

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

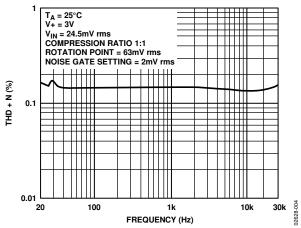

# TYPICAL PERFORMANCE CHARACTERISTICS

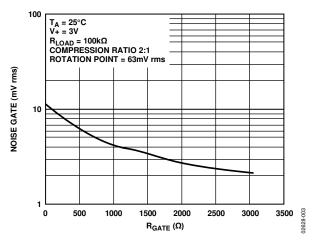

Figure 3. Noise Gate vs. RGATE

Figure 4. THD + N vs. Frequency

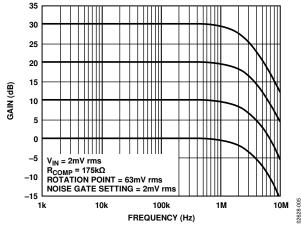

Figure 5. GBW Curves vs. VCA Gain

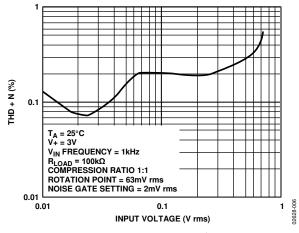

Figure 6. THD + N vs. Input Voltage

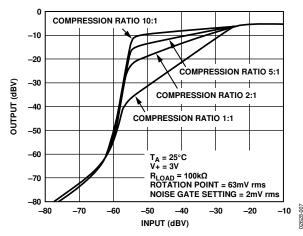

Figure 7. Output vs. Input Characteristics

Figure 8. PSRR vs. Frequency

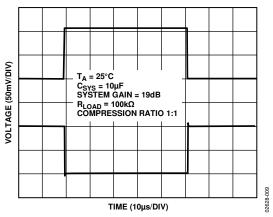

Figure 9. Small Signal Transient Response

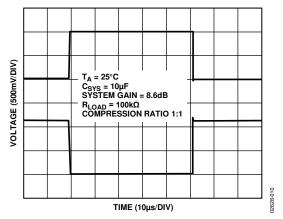

Figure 10. Large Signal Transient Response

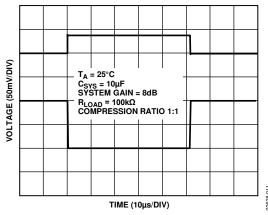

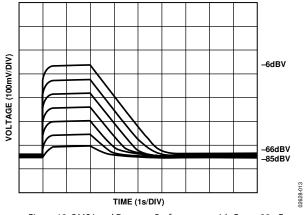

Figure 11. Small Signal Transient Response

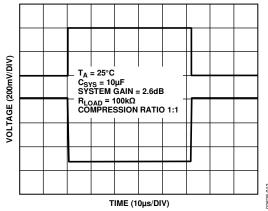

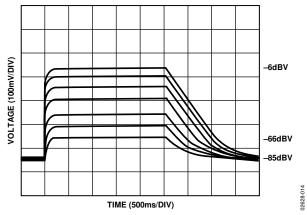

Figure 12. Large Signal Transient Response

Figure 13. RMS Level Detector Performance with  $C_{AVG} = 22 \mu F$

Figure 14. RMS Level Detector Performance with  $C_{AVG} = 2.2 \mu F$

# APPLICATIONS INFORMATION

The SSM2167 is a complete microphone signal conditioning system on a single integrated circuit. Designed primarily for voice-band applications, this integrated circuit provides amplification, limiting, variable compression, and noise gate. User adjustable compression ratio, noise gate threshold, and two different fixed gains optimize circuit operation for a variety of applications. The SSM2167 also features a low power shutdown mode for battery-powered applications.

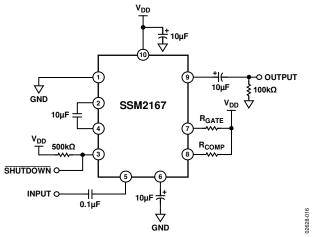

Figure 15. Typical Application Circuit

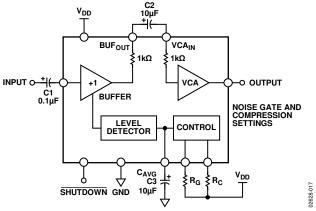

Figure 16. Functional Block Diagram

# THEORY OF OPERATION

The typical transfer characteristic for the SSM2167 is shown in Figure 2 where the output level in dB is plotted as a function of the input level in dB. The dotted line indicates the transfer characteristic for a unity-gain amplifier. For input signals in the range of  $V_{\text{DE}}$  (downward expansion) to  $V_{\text{RP}}$  (rotation point), an "r" dB change in the input level causes a 1 dB change in the output level. Here, r is defined as the compression ratio. The compression ratio may be varied from 1:1 (no compression) to 10:1 via a single resistor,  $R_{\text{COMP}}$ . Input signals above  $V_{\text{RP}}$  are compressed with a fixed compression ratio of approximately 10:1. This region of operation is the limiting region. Varying the compression ratio has no effect on the limiting region.

The breakpoint between the compression region and the limiting region is referred to as the limiting threshold or the rotation point. The term, rotation point, derives from the observation that the straight line in the compression region rotates about this point on the input/output characteristic as the compression ratio is changed.

The gain of the system with an input signal level of  $V_{RP}$  is the fixed gain, 18 dBV for the SSM2167, regardless of the compression ratio.

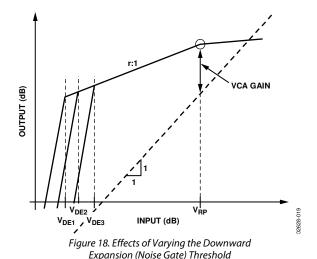

Input signals below  $V_{DE}$  are downward expanded; that is, a -1 dB change in the input signal level causes approximately a -3 dB change in the output level. As a result, the gain of the system is small for very small input signal levels, even though it may be quite large for small input signals above  $V_{DE}$ . The external resistor at Pin 7,  $R_{GATE}$ , is used to set the downward expansion threshold ( $V_{DE}$ ).

Finally, the SSM2167 provides an active low, CMOS-compatible digital power-down feature that reduces device supply current to typically less than  $2 \mu A$ .

### **SIGNAL PATH**

Figure 16 illustrates the block diagram of the SSM2167. The audio input signal is processed by the input buffer and then by the VCA. The input buffer presents an input impedance of approximately  $100~k\Omega$  to the source. A dc voltage of approximately 400~mV is present at INPUT (Pin 5) of the SSM2167, requiring the use of a blocking capacitor (C1) for ground-referenced sources. A  $0.1~\mu F$  capacitor is a good choice for most audio applications. The input buffer is a unity-gain stable amplifier that can drive the low impedance input of the VCA and an internal rms detector.

The VCA is a low distortion, variable gain amplifier whose gain is set by the side-chain control circuitry. An external blocking capacitor (C2) must be used between the buffer output and the VCA input. The 1 k $\Omega$  impedance between amplifiers determines the value of this capacitor, which is typically between 4.7  $\mu F$  and 10  $\mu F$ . An aluminum electrolytic capacitor is an economical choice. The VCA amplifies the input signal current flowing through C2 and converts this current to a voltage at the output pin (Pin 9) of the SSM2167. The net gain from input to output can be as high as 40 dB, depending on the gain set by the control circuitry.

The output impedance of the SSM2167 is typically less than 145  $\Omega$ , and the external load on Pin 9 should be >5 k $\Omega$ . The nominal output dc voltage of the device is approximately 1.4 V; therefore, a blocking capacitor for grounded loads must be used.

The bandwidth of the SSM2167 is quite wide at all gain settings. The upper 3 dB point is over 1 MHz at gains as high as 30 dB. The GBW plots are shown in Figure 5. The lower 3 dB cutoff frequency of the SSM2167 is set by the input impedance of the VCA (1  $k\Omega$ ) and C2. Whereas the noise of the input buffer is fixed, the input-referred noise of the VCA is a function of gain. The VCA input noise is designed to be at a minimum when the gain is at a maximum, thereby maximizing the usable dynamic range of the part.

### LEVEL DETECTOR

The SSM2167 incorporates a full-wave rectifier and a true rms level detector circuit whose averaging time constant is set by an external capacitor ( $C_{AVG}$ ) connected to the AVG CAP (Pin 6). For optimal low frequency operation of the level detector down to 10 Hz, the value of the capacitor should be 2.2  $\mu$ F. Some experimentation with larger values for  $C_{AVG}$  may be necessary to reduce the effects of excessive low frequency ambient background noise. The value of the averaging capacitor affects sound quality: too small a value for this capacitor may cause a pumping effect for some signals, whereas too large a value can result in slow response times to signal dynamics. Electrolytic capacitors are recommended here for lowest cost and should be in the range of 2  $\mu$ F to 22  $\mu$ F.

The rms detector filter time constant is approximately given by  $10 \times C_{\text{AVG}}$  milliseconds where  $C_{\text{AVG}}$  is in  $\mu\text{F}$ . This time constant controls both the steady state averaging in the rms detector as well as the release time for compression, that is, the time it takes for the system gain to increase due to a decrease in input signal. The attack time, the time it takes for the gain to be reduced because of a sudden increase in input level, is controlled mainly by internal circuitry that speeds up the attack for large level changes. In most cases, this limits overload time to less than 35 ms.

The performance of the rms level detector is illustrated in Figure 14 for a  $C_{\text{AVG}}$  of 2.2  $\mu\text{F}$  and Figure 13 for a  $C_{\text{AVG}}$  of 22  $\mu\text{F}$ . In Figure 13 and Figure 14, the input signal to the SSM2167 (not shown) is a series of tone bursts in six successive 10 dB steps. The tone bursts range from –66 dBV (0.5 mV rms) to –6 dBV (0.5 V rms). As illustrated in these figures, the attack time of the rms level detector is dependent only on  $C_{\text{AVG}}$ , but the release times are linear ramps whose decay times are dependent on both  $C_{\text{AVG}}$  and the input signal step size. The rate of release is approximately 240 dB/s for a  $C_{\text{AVG}}$  of 2.2  $\mu\text{F}$ , and 12 dB/s for a  $C_{\text{AVG}}$  of 22  $\mu\text{F}$ .

# **CONTROL CIRCUITRY**

The output of the rms level detector is a signal proportional to the log of the true rms value of the buffer output with an added dc offset. The control circuitry subtracts a dc voltage from this signal, scales it, and sends the result to the VCA to control the gain. The gain control of the VCA is logarithmic—a linear change in control signal causes a dB change in gain. It is this control law that allows linear processing of the log rms signal to provide the flat compression characteristic on the input/output characteristic shown in Figure 2.

Figure 17. Effect of Varying the Compression Ratio

#### SETTING THE COMPRESSION RATIO

Changing the scaling of the control signal fed to the VCA causes a change in the circuit compression ratio, r. This effect is shown in Figure 17. Connecting a resistor ( $R_{\text{COMP}}$ ) between Pin 8 and  $V_{\text{DD}}$  sets the compression ratio. Lowering  $R_{\text{COMP}}$  gives smaller compression ratios as indicated in Table 4. AGC performance is achieved with compression ratios between 2:1 and 10:1, and is dependent on the application. Shorting  $R_{\text{COMP}}$  disables the AGC function, setting the compression equal to 1:1. If using a compression resistor, using a value greater than 5 k $\Omega$  is recommended. If a value lower than 5 k $\Omega$  is used, the device may interpret this as a short, 0  $\Omega$ .

**Table 4. Setting Compression Ratio**

| Compression Ratio | Value of R <sub>COMP</sub> |

|-------------------|----------------------------|

| 1:1               | 0 Ω (short to V+)          |

| 2:1               | 15 kΩ                      |

| 3:1               | 35 kΩ                      |

| 5:1               | 75 kΩ                      |

| 10:1              | 175 kΩ                     |

# SETTING THE NOISE GATE THRESHOLD (DOWNWARD EXPANSION)

The noise gate threshold is a programmable point using an external resistor ( $R_{GATE}$ ) that is connected between Pin 7 (GATE THRS) and  $V_{DD}$ . The downward expansion threshold may be set between -40~dBV and -55~dBV, as shown in Table 5. The downward expansion threshold is inversely proportional to the value of this resistance: setting this resistance to 0  $\Omega$  sets the threshold at approximately 10 mV rms (-40~dBV), whereas a 5 k $\Omega$  resistance sets the threshold at approximately 1 mV rms (-55~dBV). This relationship is illustrated in Figure 18. It is not recommended to use more than 5 k $\Omega$  for the  $R_{GATE}$  resistor because the noise floor of the SSM2167 prevents the noise gate from being lowered further without causing problems.

**Table 5. Setting Noise Gate Threshold**

| Noise Gate (dBV) | Value of R <sub>GATE</sub> |

|------------------|----------------------------|

| -40              | 0 Ω (short to V+)          |

| -48              | 1 kΩ                       |

| -54              | 2 kΩ                       |

| <b>-</b> 55      | 5 kΩ                       |

# **ROTATION POINT (LIMITING)**

Input signals above a particular level, the rotation point, are attenuated (limited) by internal circuitry. This feature allows the SSM2167 to limit the maximum output, preventing clipping of the following stage, such as a codec or ADC. The rotation point for the SSM2167 is set internally to -24 dBV (63 mV rms).

# **SHUTDOWN FEATURE**

The supply current of the SSM2167 can be reduced to under  $10~\mu A~by$  applying an active low, 0~V~CMOS-compatible input to the SHUTDOWN pin (Pin 3) of the SSM2167. In this state, the input and output circuitry of the SSM2167 assumes a high impedance state; as such, the potentials at the input pin and the output pin are determined by the external circuitry connected to the SSM2167. The SSM2167 takes approximately 200 ms to settle from a shutdown to power-on command. For power-on to shutdown, the SSM2167 requires more time, typically less than 1~sec. Cycling the power supply to the SSM2167 can result in quicker settling times: the off-to-on settling time of the SSM2167 is less than 200~ms, whereas the on-to-off settling time is less than 1~ms. The SSM2167 shutdown current is related to both temperature and voltage.

# **PCB LAYOUT CONSIDERATIONS**

Because the SSM2167 is capable of wide bandwidth operation and can be configured for as much as 60 dB of gain, special care must be exercised in the layout of the PCB that contains the IC and its associated components. The following applications hints should be considered for the PCB.

The layout should minimize possible capacitive feedback from the output of the SSM2167 back to its input. Do not run input and output traces adjacent to each other.

A single-point (star) ground implementation is recommended in addition to maintaining short lead lengths and PCB runs. In applications where an analog ground and a digital ground are available, the SSM2167 and its surrounding circuitry should be connected to the analog ground of the system. As a result of these recommendations, wire-wrap board connections and grounding implementations are to be explicitly avoided.

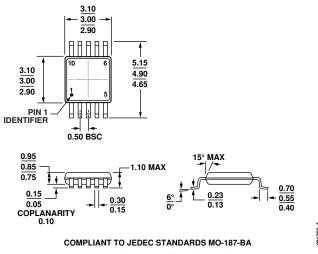

# **OUTLINE DIMENSIONS**

Figure 19. 10-Lead Mini Small Outline Package [MSOP] (RM-10) Dimensions shown in millimeters

# **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option | Branding |

|--------------------|-------------------|---------------------|----------------|----------|

| SSM2167-1RMZ-REEL  | -40°C to +85°C    | 10-Lead MSOP        | RM-10          | B11      |

| SSM2167-1RMZ-R7    | −40°C to +85°C    | 10-Lead MSOP        | RM-10          | B11      |

| SSM2167Z-EVAL      |                   | Evaluation Board    |                |          |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part, # denotes RoHS compliant product may be top or bottom marked.

**NOTES**