# TAXI™-compatible HOTLink<sup>®</sup> Transceiver

CY7C9689A

# Features

- Second-generation HOTLink<sup>®</sup> technology

- AMD<sup>™</sup> AM7968/7969 TAXIchip<sup>™</sup>-compatible

- 8-bit 4B/5B or 10-bit 5B/6B NRZI encoded data transport

- 10-bit or 12-bit NRZI pre-encoded (bypass) data transport

- Synchronous TTL parallel interface

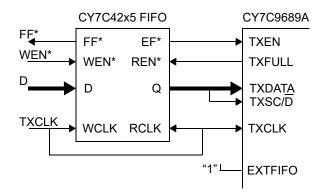

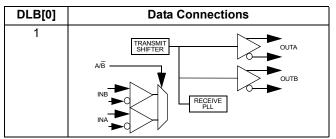

- Embedded/bypassable 256-character Transmit and Receive FIFOs

- 50- to 200-MBaud serial signaling rate

- Internal phase-locked loops (PLLs) with no external PLL components

- Dual differential PECL-compatible serial inputs and outputs

- Compatible with fiber-optic modules and copper cables

- Built-in self-test (BIST) for link testing

- Link Quality Indicator

- Single +5.0 V ±10%supply

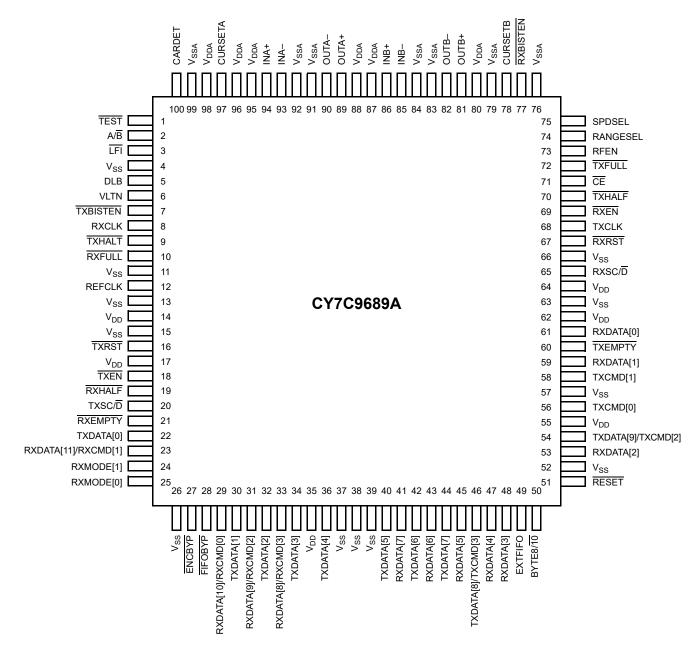

- 100-pin TQFP

- Pb-free package option available

# **Functional Description**

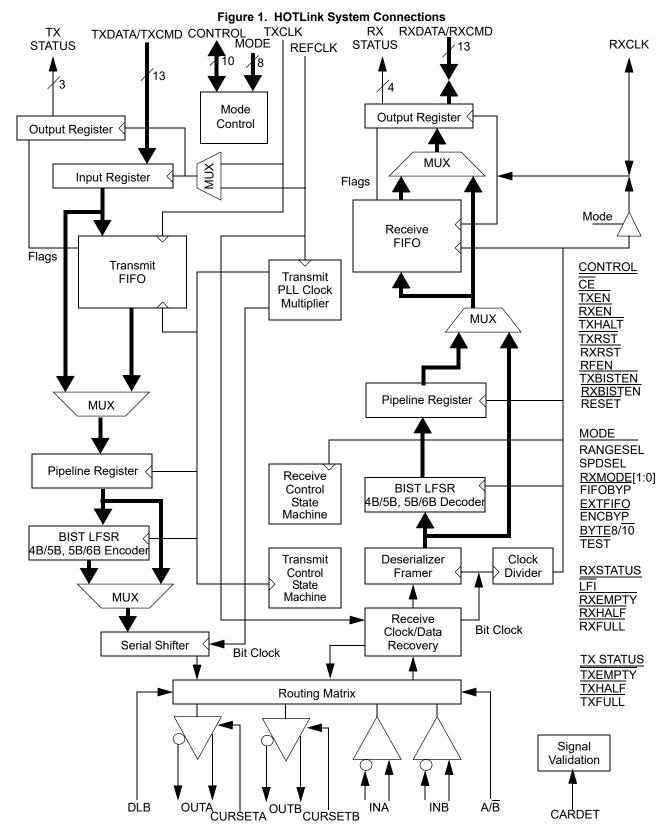

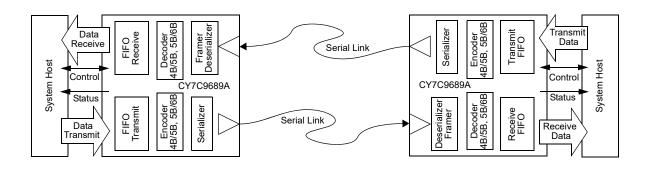

The CY7C9689A HOTLink Transceiver is a point-to-point communications building block allowing the transfer of data over high-speed serial links (optical fiber, balanced, and unbalanced copper transmission lines) at speeds ranging between 50 and 200 MBaud. The transmit section accepts parallel data of selectable widths and converts it to serial data, while the receiver section accepts serial data and converts it to parallel data of selectable widths. Figure 1 illustrates typical connections between two independent host systems and corresponding CY7C9689A parts. The CY7C9689A provides enhanced technology, increased functionality, a higher level of integration, higher data rates, and lower power dissipation over the AMD AM7968/7969 TAXIchip products.

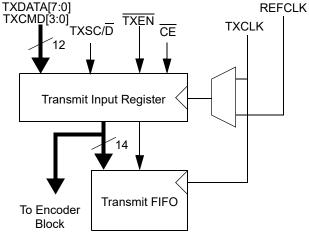

The transmit section of the CY7C9689A HOTLink can be configured to accept either 8- or 10-bit data characters on each clock cycle, and stores the parallel data into an internal synchronous Transmit FIFO. Data is read from the Transmit FIFO and is encoded using embedded 4B/5B or 5B/6B encoders to improve its serial transmission characteristics. These encoded characters are then serialized, converted to NRZI, and output from two PECL-compatible differential transmission line drivers at a bit-rate of either 10 or 20 times the input reference clock in 8-bit (or 10-bit bypass) mode, or 12 or 24 times the reference clock in 10-bit (or 12-bit bypass) mode.

The receive section of the CY7C9689A HOTLink accepts a serial bit-stream from one of two PECL compatible differential line receivers and, using a completely integrated PLL clock synchronizer, recovers the timing information necessary for data reconstruction. The recovered bit stream is converted from NRZI to NRZ, deserialized, framed into characters, 4B/5B or 5B/6B decoded, and checked for transmission errors. The recovered 8- or 10-bit decoded characters are then written to an internal Receive FIFO, and presented to the destination host system.

The integrated 4B/5B and 5B/6B encoder/decoder may be bypassed (disabled) for systems that present externally encoded or scrambled data at the parallel interface. With the encoder bypassed, the pre-encoded parallel data stream is converted to and from a serial NRZI stream. The embedded FIFOs may also be bypassed (disabled) to create a reference-locked serial transmission link. For those systems requiring even greater FIFO storage capability, external FIFOs may be directly coupled to the CY7C9689A through the parallel interface without the need for additional glue-logic.

The TTL parallel I/O interface may be configured as either a FIFO (configurable for depth expansion through external FIFOs) or as a pipeline register extender. The FIFO configurations are optimized for transport of time-independent (asynchronous) 8- or 10-bit character-oriented data across a link. A Built-In Self-Test (BIST) pattern generator and checker allows for testing of the high-speed serial data paths in both the transmit and receive sections, and across the interconnecting links.

HOTLink devices are ideal for a variety of applications where parallel interfaces can be replaced with high-speed, point-to-point serial links. Some applications include interconnecting workstations, backplanes, servers, mass storage, and video transmission equipment.

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised February 14, 2018

# TAXI HOTLink Transceiver Logic Block Diagram

# Contents

| Pin Configuration                        | 5  |

|------------------------------------------|----|

| Pin Descriptions                         | 6  |

| CY7C9689A HOTLink Operation              | 15 |

| Overview                                 | 15 |

| Transmit Data Path                       |    |

| Receive Data Interface                   | 15 |

| Oscillator Speed Selection               | 15 |

| CY7C9689A TAXI HOTLink Transceiver       |    |

| Block Diagram Description                | 16 |

| Transmit FIFO                            | 17 |

| Encoder Block                            | 17 |

| Transmit Shifter                         |    |

| Routing Matrix                           | 18 |

| Serial Line Drivers                      |    |

| Transmit PLL Clock Multiplier            |    |

| Transmit Control State Machine           | 19 |

| Serial Line Receivers                    | 19 |

| Signal Detect                            |    |

| Clock/Data Recovery                      |    |

| Clock Divider                            | 20 |

| Deserializer/Framer                      | 20 |

| Decoder Block                            | 20 |

| Receive Control State Machine            | 22 |

| Receive FIFO                             | 22 |

| Receive Input Register                   | 23 |

| Receive Output Register                  | 23 |

| Maximum Ratings                          | 24 |

| Operating Range                          | 24 |

| CY7C9689A DC Electrical Characteristics  | 24 |

| Capacitance                              |    |

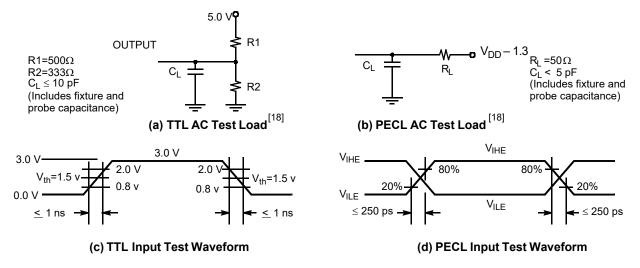

| AC Test Loads and Waveforms              | 25 |

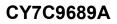

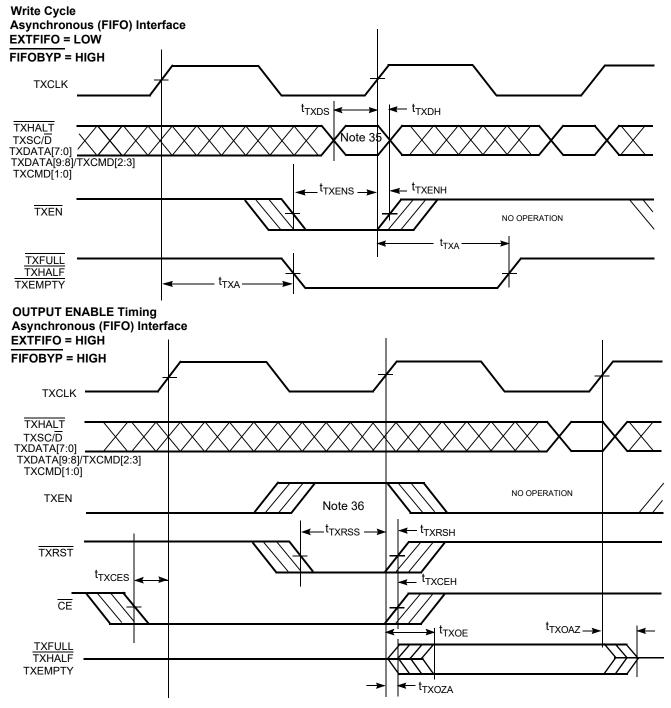

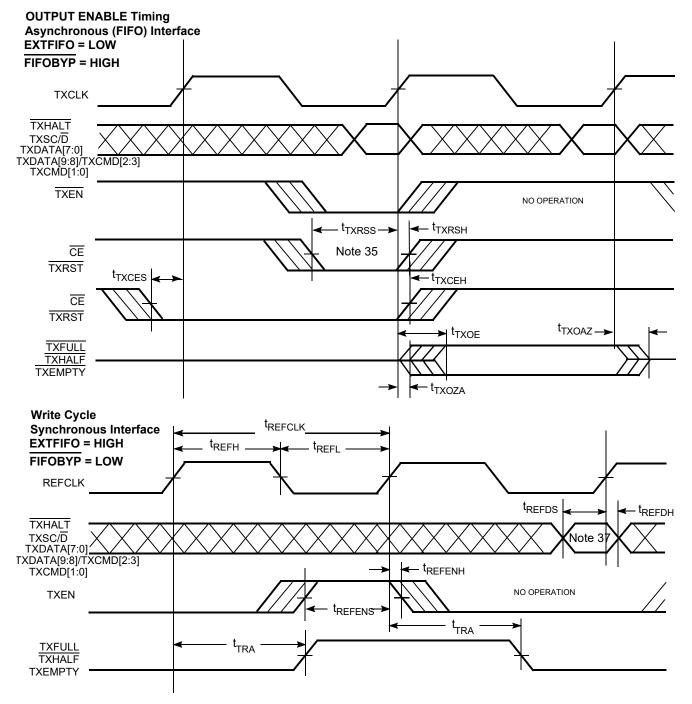

| CY7C9689A Transmitter TTL                |    |

| Switching Characteristics, FIFO Enabled  |    |

| CY7C9689A Receiver TTL                   |    |

| Switching Characteristics, FIFO Enabled  | 27 |

| CY7C9689A Transmitter TTL                |    |

| Switching Characteristics, FIFO Bypassed | 27 |

| CY7C9689A Receiver TTL                   |    |

| Switching Characteristics, FIFO Bypassed |    |

| CY7C9689A REFCLK Input                   |    |

| Switching Characteristics                | 29 |

| CY7C9689A Receiver                       |    |

| Switching Characteristics                | 29 |

| CY7C9689A Transmitter                    |    |

| Switching Characteristics                |    |

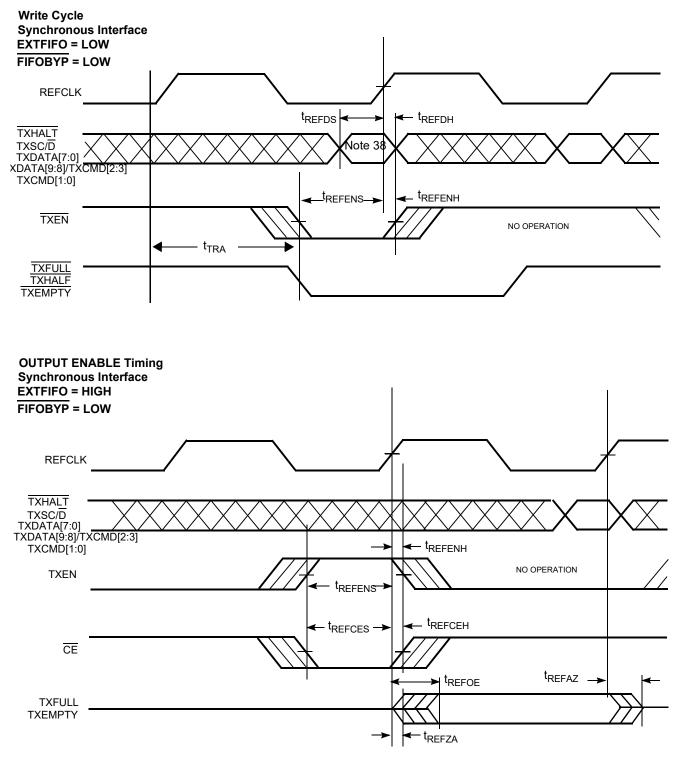

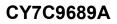

| CY7C9689A HOTLink Transmitter            |    |

| Switching Waveforms                      |    |

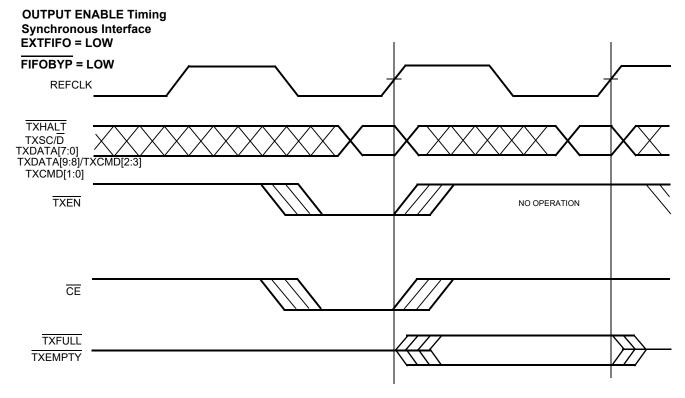

| CY7C9689A HOTLink Receiver               |    |

| Switching Waveforms                      | 35 |

|------------------------------------------|----|

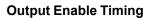

| Output Enable Timing                     | 36 |

| Functional Overview                      | 39 |

| CY7C9689A TAXI HOTLink Transmit-Path     |    |

| Operating Mode Descriptions              |    |

| Synchronous Encoded                      | 39 |

| Synchronous Pre-encoded                  |    |

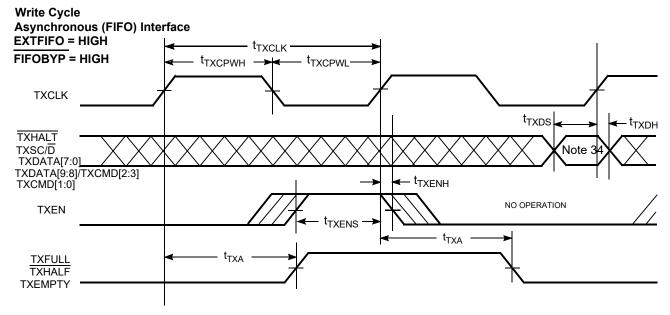

| Asynchronous Encoded                     | 40 |

| CY7C9689A TAXI HOTLink Receive-Path      |    |

| Operating Mode Descriptions              |    |

| Synchronous Decoded                      |    |

| Synchronous Undecoded                    |    |

| Asynchronous Decoded                     |    |

| Asynchronous Undecoded                   |    |

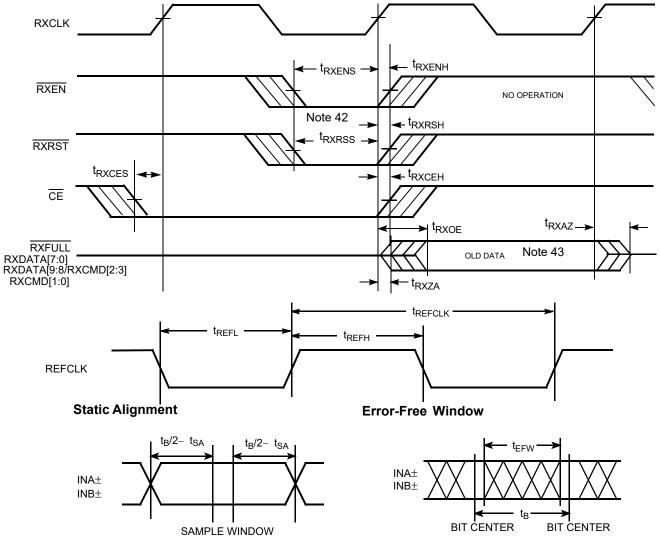

| BIST Operation and Reporting             |    |

| BIST Enable Inputs                       |    |

| BIST Transmit Path                       |    |

| BIST Receive Path                        |    |

| BIST Three-state Control                 |    |

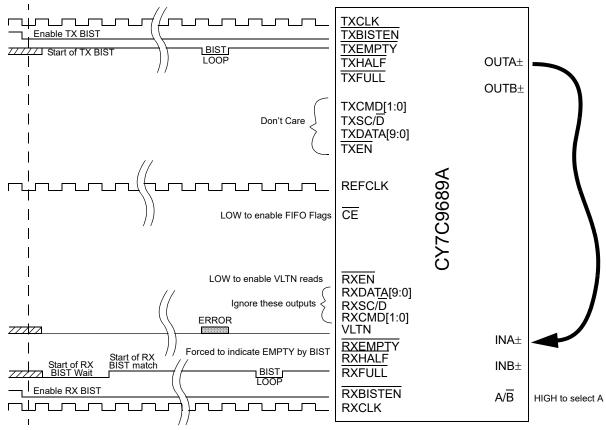

| Bus Interfacing                          | 43 |

| Shared Bus Interface Concept             |    |

| Device Selection                         |    |

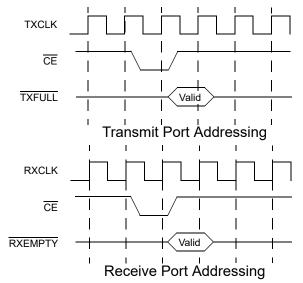

| Address Match and FIFO Flag Access       |    |

| Device Selection                         |    |

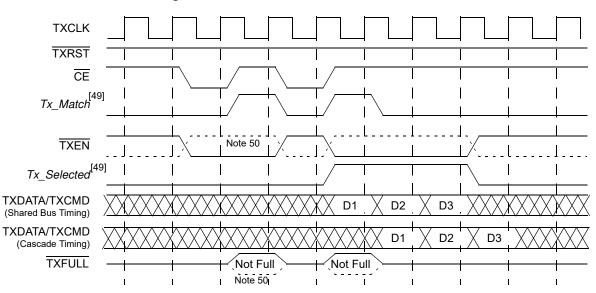

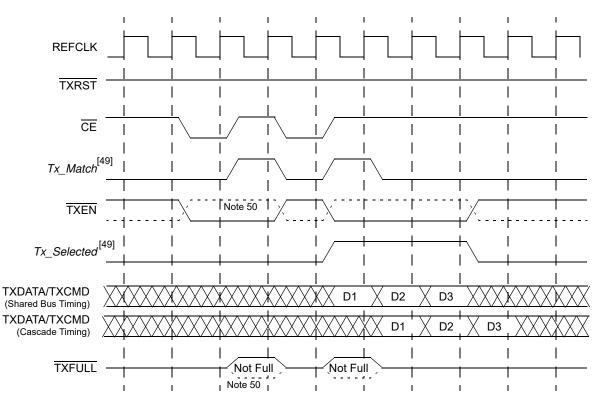

| Transmit Data Selection                  |    |

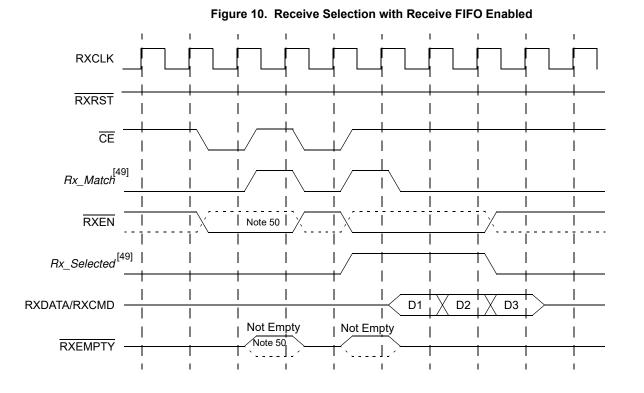

| Receive Data Selection                   |    |

| FIFO Reset Address Match                 |    |

| FIFO Reset Sequence                      |    |

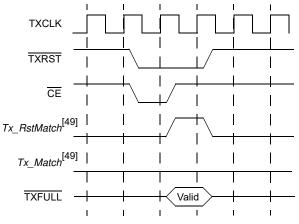

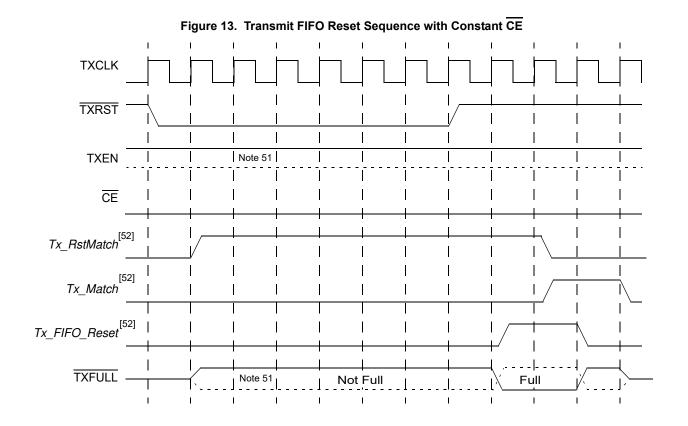

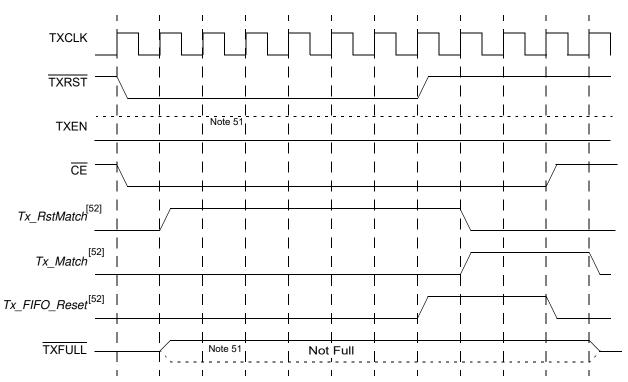

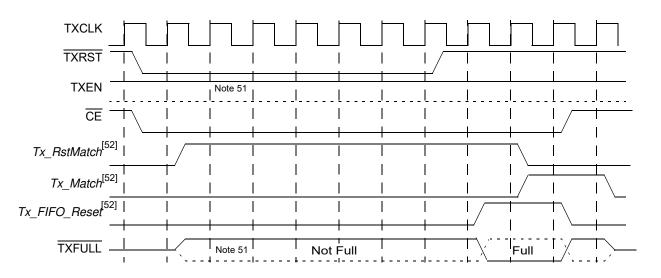

| Transmit FIFO Reset Sequence             |    |

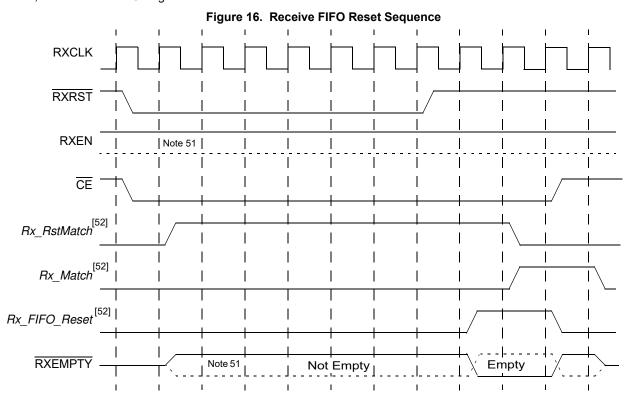

| Receive FIFO Reset Sequence              | 51 |

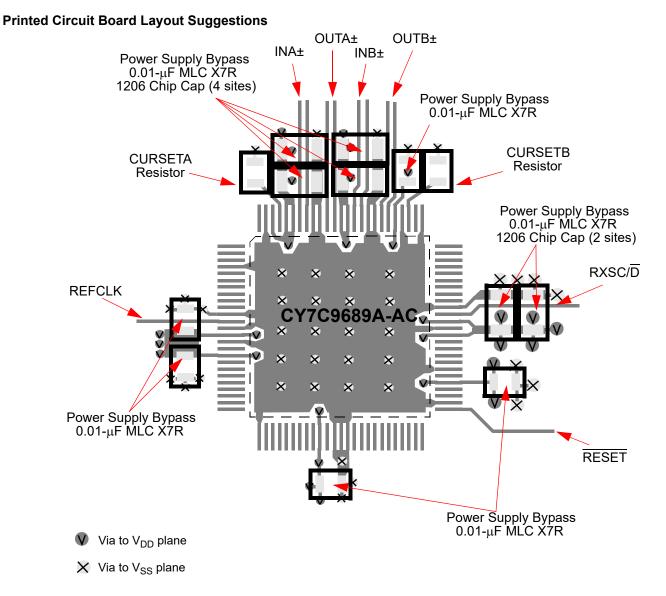

| Printed Circuit Board Layout Suggestions | 52 |

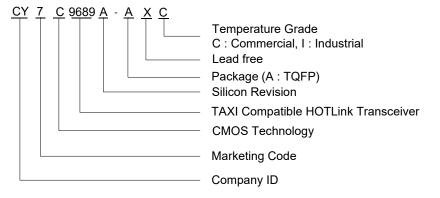

| Ordering Information                     | 53 |

| Ordering Code Definitions                |    |

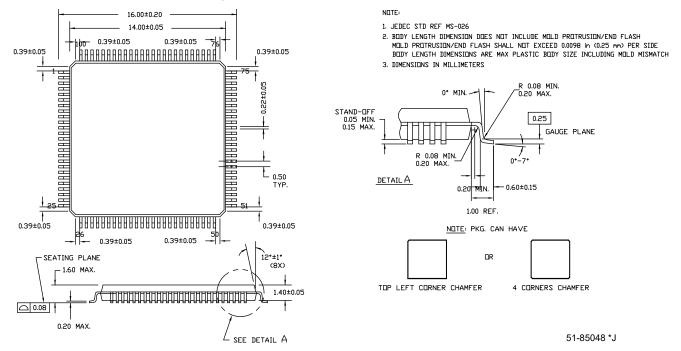

| Package Diagram                          |    |

| Acronyms                                 |    |

| Document Conventions                     |    |

| Units of Measure                         |    |

| Document History Page                    |    |

| Sales, Solutions, and Legal Information  | 57 |

| Worldwide Sales and Design Support       |    |

| Products                                 |    |

| PSoC® Solutions                          |    |

| Cypress Developer Community              |    |

| Technical Support                        | 57 |

# **Pin Configuration**

# **Pin Descriptions**

| Pin                                     | Name                       | I/O Characteristics                                            | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----------------------------------------|----------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Transı                                  | Transmit Path Signals      |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 68                                      | TXCLK                      | TTL clock input<br>Internal Pull-up                            | Transmit FIFO Clock.<br>Used to sample all Transmit FIFO and related interface signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 44, 42,<br>40, 36,<br>34, 32,<br>30, 22 | TXDATA[7:0]                | TTL input, sampled on<br>TXCLK↑ or REFCLK↑<br>Internal Pull-up | Parallel Transmit DATA Input.<br>When selected ( $\overline{CE} = LOW$ and $\underline{TXEN} = asserted$ ), information on these inputs is processed as DATA when $\underline{TXSC/D}$ is LOW and ignored otherwise. When the encoder is bypassed (ENCBYP is LOW), TXDATA[7:0] functions as the least significant eight bits of the 10- or 12-bit pre-encoded transmit character.<br>When the Transmit FIFO is enabled (FIFOBYP is HIGH), these inputs are sampled on the rising edge of TXCLK. When the Transmit FIFO is bypassed (FIFOBYP is LOW) these inputs are captured on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 54, 46                                  | TXDATA[9:8]/<br>TXCMD[2:3] | TTL input, sampled on<br>TXCLK↑ or REFCLK↑<br>Internal Pull-up | Parallel Transmit DATA or COMMAND Input.<br>When selected, BYTE8/10 is HIGH, and the encoder is enabled (ENCBYP is<br>HIGH), information on these inputs are processed as TXCMD[2:3] if TXSC/D is<br>HIGH and ignored otherwise.<br>When selected, BYTE8/10 is LOW, and the encoder is enabled (ENCBYP is<br>HIGH), information on these inputs are processed as TXDATA[9:8] if TXSC/D is<br>LOW and ignored otherwise.<br>When the encoder is bypassed (ENCBYP is LOW), TXDATA[9:8] functions as the<br>9th and 10th bits of the 10- or 12-bit <u>pre-encoded</u> transmit character.<br>When the Transmit FIFO is enabled (FIFOBYP is HIGH), these inputs <u>are sampled</u><br>on the rising edge of TXCLK. When the Transmit FIFO is bypassed (FIFOBYP is<br>LOW), these inputs are captured on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                            |  |  |

| 58, 56                                  | TXCMD[1:0]                 | TTL input, sampled on<br>TXCLK↑ or REFCLK↑<br>Internal Pull-up | Parallel Transmit COMMAND Input.<br>When selected and the encoder is enabled (ENCBYP is HIGH), information on<br>these inputs is processed as a COMMAND when TXSC/D is HIGH and ignored<br>otherwise.<br>When BYTE8/10 is HIGH and the encoder is bypassed (ENCBYP is LOW), the<br>TXCMD[1:0] inputs are ignored.<br>When BYTE8/10 is LOW and when the encoder is bypassed (ENCBYP is LOW),<br>the TXCMD[1:0] inputs function as the 11th and 12th (MSB) bits of the 12-bit<br>pre-encoded transmit character.<br>When the Transmit FIFO is enabled (FIFOBYP is HIGH), these inputs <u>are sampled</u><br>on the rising edge of TXCLK. When the Transmit FIFO is bypassed (FIFOBYP is<br>LOW), these inputs are sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 20                                      | TXSC/D                     | TTL input, sampled on<br>TXCLK↑ or REFCLK↑<br>Internal Pull-up | COMMAND or DATA input selector.<br>When selected, BYTE8/10 is HIGH, and the encoder is enabled (ENCBYP is HIGH)_this input selects if the DATA or COMMAND inputs are processed. If TXSC/D is HIGH, the value on TXCMD[3:0] is captured as one of sixteen possible COMMANDs, and the data on the TXDATA[7:0] bits are ignored. If TXSC/D is LOW, the information on TXDATA[7:0] is captured as one of 256 possible 8-bit DATA values, and the information on the TXCMD[3:0] bus is ignored.<br>When BYTE8/10 is LOW and the encoder is enabled (ENCBYP is HIGH) this input selects if the DATA or COMMAND inputs are processed. If TXSC/D is HIGH, the information on TXCMD[1:0] is captured as one of four possible COMMANDs, and the information on TXCMD[1:0] is captured as one of four possible COMMANDs, and the information on the TXCMD[3:0] bits are ignored. If TXSC/D is LOW, the information on TXDATA[9:0] bits are ignored. If TXSC/D is LOW, the information on TXDATA[9:0] is captured as one of 1024 possible 10-bit DATA values, and the information on the TXCMD[1:0] bus is ignored.<br>When the encoder is bypassed (ENCBYP is LOW) TXSC/D is ignored |  |  |

| Pin | Name     | I/O Characteristics                                               | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | TXEN     | TTL input, sampled on<br>TXCLK↑ or REFCLK↑<br>Internal Pull-up    | Transmit Enable.TXEN is sampled on the rising edge of the TXCLK or REFCLK input and enablesparallel data bus write operations (when selected). The device is selected whenTXEN is asserted during a clock cycle immediately following one in which CE issampled LOW.Depending on the level on EXTFIFO, the asserted state for TXEN can be activeHIGH or active LOW. If EXTFIFO is LOW, then TXEN is active LOW and data iscaptured on the same clock cycle where TXEN is sampled LOW.HIGH, then TXEN is active HIGH and data is captured on the clock cycle followingany clock edge when TXEN is sampled HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7   | TXBISTEN | TTL input,<br>asynchronous<br>Internal Pull-up                    | Transmitter BIST Enable.<br>When TXBISTEN is LOW, the transmitter generates a 511-character repeating sequence that can be used to validate link integrity. This 4B/5B BIST sequence is generated regardless of the state <u>of other config</u> uration inputs. The transmitter returns to normal operation when TXBISTEN is HIGH. All Transmit FIFO read operations are suspended when BIST is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16  | TXRST    | TTL input, sampled on<br>TXCLK↑<br>Internal Pull-up               | Reset Transmit FIFO.<br>When the Transmit FIFO is enabled (FIFOBYP is HIGH), TXEN is deasserted, CE is asserted (LOW), and TXRST is sampled LOW by TXCLK for seven cycles, the Transmit FIFO begins its internal reset process. The Transmit FIFO TXFULL flag is asserted and the host interface counter and address pointer are zeroed. This reset propagates to the serial transmit side, any remaining counters and pointers. The TXFULL flag is asserted until both sides of the Transmit FIFO have reset.<br>While TXRST remains asserted, the Transmit FIFO remains in reset and the TXFULL output remains asserted.<br>When the Transmit FIFO is bypassed (FIFOBYP is LOW), TXRST is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9   | TXHALT   | TTL input, sampled on<br>TXCLK↑<br>Internal Pull-up               | Transm <u>itter Halt</u> Control Input.<br>When TXHALT is asserted LOW, transmission of <u>data is</u> suspended and the<br>HOTLink TAXI transmits SYNC characters. When TXHALT is deasserted HIGH,<br>normal data processing proceeds.<br>If the Transmit FIFO is enabled (FIFOBYP is HIG <u>H), the in</u> terface is allowed to<br>continue loading data into the Transmit FIFO while TXHALT is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 72  | TXFULL   | Three-state TTL output,<br>changes following<br>TXCLK↑ or REFCLK↑ | Transmit FIFO Full Status Flag.<br>When the Transmit FIFO is enabled (FIFOBYP is HIGH) and its flags are driven<br>(CE is LOW), TXFULL is asserted when four or fewer characters can be written to<br>the HOTLink Transmit FIFO. If a Transmit FIFO reset has been initiated (TXRST<br>was sampled asserted for a minimum of seven TXCLK cycles), TXFULL is<br>asserted to enforce the full/unavailable status of the Transmit FIFO during reset.<br>When the Transmit FIFO is bypassed (FIF <u>OBYP</u> is LOW), the TXFULL output<br>changes after the rising edge of REFCLK. TXFULL is asserted when the trans-<br>mitter is BUSY (not accepting a new data or command characters) and deasserted<br>when new characters can be accepted.<br>When the Transmit FIFO is bypassed and RANGESEL is HIGH or SPDSEL is<br>LOW, TXFULL toggles at the character rate to provide a character rate reference<br>control-indication since REFCLK is operating at twice of the data rate.<br>The asserted state of this output (HIGH or LOW) is determined by the state of the<br>EXTFIFO input. When EXTFIFO is LOW, TXFULL is active LOW. When EXTFIFO<br>is HIGH, TXFULL is active HIGH. |

| Pin                                    | Name            | I/O Characteristics                                               | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|-----------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70                                     | TXHALF          | Three-state TTL output,<br>changes following<br>TXCLK↑            | Transmit FIFO Half-full Status Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 60                                     | TXEMPTY         | Three-state TTL output,<br>changes following<br>TXCLK↑ or REFCLK↑ | Transmit FIFO Empty Status Flag.<br><u>When the</u> Transmit FIFO is enabled (FIFOBYP is HIGH and CE is LOW),<br>TXEMPTY is asserted when the HOTLink Transmit FIFO has no data to forward<br>to the encoder. If a Transmit FIFO reset has been initiated (TXRST was sampled<br>asserted for a minimum of seven TXCLK cycles), TXEMPTY is deasserted and<br>remains deasserted until the Transmit <u>FIFO reset</u> operation is complete.<br>When the Transmit FIFO is bypassed (FIFOBY <u>P is LOW)</u> , TXEMPTY is asserted<br>to indicate that the transmitter can accept data. TXEMPTY is also used as a BIST<br>progress indicator when TXBISTEN is asserted.<br>When TXBISTEN is asserted LOW, TXEMPTY becomes the transmit BIST-loop<br><u>counter</u> indicator (regardless of the logic state of FIFOBYP). In this mode<br>TXEMPTY is asserted for one TXCLK or REFCLK period at the end of each trans-<br>mitted BIST sequence.<br><b>Note</b> : During BIST operations, when the Transmit FIFO is enabled (FIFOBYP is<br>HIGH), it is necessary to keep TXCLK operating, even though no <u>data is loa</u> ded<br>into the Transmit FIFO and TXEN is never asserted, to allow the TXEMPTY flag<br>to respond to the BIST state changes.<br>The asserted state of this output (HIGH or LOW) is determined by the state of the<br>EXTFIFO input. When EXTFIFO is LOW, TXEMPTY is active LOW. When<br>EXTFIFO is HIGH, TXEMPTY is active HIGH.<br>If CE is sampled asserted (LOW), TXEMPTY is driven to an active state. If CE is<br>sampled deasserted (HIGH), TXEMPTY is placed into a High-Z state. |

| Receiv                                 | ve Path Signals |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8                                      | RXCLK           | Bidirectional TTL clock<br>Internal Pull-up                       | Receive Clock.<br>When the Receive FIFO is enabled (FIFOBYP is HIGH), this clock is the Receive<br>interface <i>input</i> clock and is used to control <u>Receive</u> FIFO read and reset, opera-<br>tions. When the Receive FIFO is bypassed (FIFOBYP is LOW), this clock becomes<br>the recovered Receive PLL character clock <i>output</i> which runs continuously at the<br>character rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 41, 43,<br>45, 47,<br>48, 53,<br>59,61 | RXDATA[7:0]     | Three-state TTL output,<br>changes following<br>RXCLK↑            | Parallel Receive DATA Outputs.<br>When the decoder is enabled (ENCBYP is HIGH), the low-order eight bits of the decoded DATA character are presented on the RXDATA[7:0] outputs. COMMAND characters, when they are received, do not disturb these outputs. When the decoder is bypassed, the low order eight bits of the non-decoded character are presented on the RXDATA[7:0] outputs.<br>When the Receive FIFO is disabled (FIFOBYP is LOW), these outputs change on the rising edge of the RXCLK output. When the Receive FIFO is enabled (FIFOBYP is HIGH), these outputs change on the rising edge of RXCLK input.<br>RXEN is the three-state control for RXDATA[7:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin    | Name                         | I/O Characteristics                                                          | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|--------|------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -      |                              |                                                                              | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 31, 33 | RXDATA[9:8]/<br>RXCMD[2:3]   | Three-state TTL output,<br>changes following<br>RXCLK↑                       | Parallel Receive DATA or COMMAND Output.<br>When BYTE8/10 is HIGH and the decoder is enabled (ENCBYP is HIGH) these<br>outputs reflects the value for the most recently received RXCMD[2:3].<br>When BYTE8/10 is LOW and the decoder is enabled (ENCBYP is HIGH) these<br>outputs reflects the value for the most recently received RXDATA[9:8].<br>When the decoder is bypassed (ENCBYP is LOW), RXDATA[9:8] functions as the<br>9th and 10th bits of the 10- or 12-bit non-decoded receive character.<br>When the Receive FIFO is disabled (FIFOBYP is LOW), these outputs change on<br>the rising edge of the RXCLK output. When the Receive FIFO is enabled<br>(FIFOBYP is HIGH), these outputs change on the rising edge of the RXCLK input.<br>RXEN is a three-state control for RXDATA[9:8]/RXCMD[2:3].                                                                                                                                                                                                                                                |  |

| 23, 29 | RXDATA[11:10]<br>/RXCMD[1:0] | Three-state TTL output,<br>changes following<br>RXCLK↑                       | Parallel Receive COMMAND Outputs.<br>When the decoder is enabled (ENCBYP is HIGH) these outputs reflect the value<br>for the most recently received RXCMD[1:0].<br>When BYTE8/10 is HIGH and the decoder is bypassed (ENCBYP is LOW), these<br>outputs have no meaning and are driven LOW.<br>When BYTE8/10 is LOW and the decoder is bypassed (ENCBYP is LOW),<br>RXCMD[1:0] functions as the 11th and 12th (MSB) bits of the 12-bit non-decoded<br>receive character.<br>When the Receive FIFO is disabled (FIFOBYP is LOW), this output changes on<br>the rising edge of the RXCLK output. When the Receive FIFO is enabled<br>(FIFOBYP is HIGH), these outputs change on the rising edge of the RXCLK input.<br>RXEN is a three-state control for RXCMD[1:0].                                                                                                                                                                                                                                                                                             |  |

| 69     | RXEN                         | TTL input, sampled<br>on RXCLK↑<br>Internal Pull-up                          | Receive Enable Input.<br>RXEN is a three-state control for the parallel data bus read operations. RXEN is<br>sampled on the rising edge of the RXCLK input (or output) and enables parallel<br>data bus read operations (when selected). The device is selected when RXEN is<br>asserted during an RXCLK cycle immediately following one in which CE is sampled<br>LOW. The parallel data pins are driven to active levels after the rising edge of<br>RXCLK. When RXEN is de-asserted (ending the selection) the parallel data pins<br>are High-Z after the rising edge of RXCLK.<br>Depending on the level on EXTFIFO, this signal can be active HIGH or active LOW.<br>If EXTFIFO is LOW, then RXEN is active LOW. If EXTFIFO is HIGH, then RXEN<br>is active HIGH. Data is delivered on the clock cycle following any clock edge when<br>RXEN is active.                                                                                                                                                                                                  |  |

| 65     | RXSC/D                       | Three-state TTL output,<br>changes following<br>RXCLK↑                       | COMMAND or <u>D</u> ATA Output Indicator.<br>When BYTE8/10 is HIGH and the decoder is enabled (ENCBYP is HIGH), this<br>output indicates which group of outputs have been updated. If RXSC/D is HIGH,<br>RXCMD[3:0] contains a new <u>C</u> OMMAND. The DATA on the RXDATA[7:0] pins<br>remain unchanged. If RXSC/D is LOW, RXDATA[7:0] contains a new DATA<br>character. The <u>C</u> OMMAND output on RXCMD[3:0] remain unchanged.<br>When BYTE8/10 is LOW and the decoder is enabled (ENCBYP is HIGH), this<br>output indicates which group of outputs have been updated. If RXSC/D is HIGH,<br>RXCMD[1:0] contains a new <u>C</u> OMMAND and the DATA on the RXDATA[9:0]<br>remain unchanged. If RXSC/D is LOW, RXDATA[9:0] contains a new DATA<br>character and the COMMAND o <u>utput on RXCMD[1:0]</u> contains a new DATA<br>character and the COMMAND o <u>utput on RXCMD[1:0]</u> remain unchanged.<br>When the decoder is bypassed (ENCBYP is LOW) RXSC/D is not used and may<br>be left unconnected.<br>RXEN is a three-state control for RXSC/D. |  |

| 6      | VLTN                         | Three-state TTL output,<br>changes following<br>RXCLK↑<br>Internal Pull-down | Code Rule Violation Detected.<br>VLTN is asserted in response to detection of a 4B/5B or 5B/6B character that does<br>not meet the coding rules of these characters. When VLTN is asserted, the values<br>on the output DATA and COMMAND buses remain unchanged. VLTN remains<br>asserted for one RXCLK period.<br>VLTN is used to report character mismatches when RXBISTEN is driven LOW.<br>VLTN is driven LOW when the decoder is bypassed (ENCBYP is LOW).<br>RXEN is a three-state control for VLTN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Pin    | Name        | I/O Characteristics                                                 | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------|-------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 67     | RXRST       | TTL input, sampled on<br>RXCLK↑<br>Internal Pull-up                 | Receive FIFO Reset. Active LOW.<br>When the Receive FIFO is enabled (FIFOBYP is HIGH), RXEN is deasserted, CE is asserted (LOW), and RXRST is sampled while asserted (LOW) by RXCLK for seven cycles, the Receive FIFO begins its internal reset process.<br>Once the reset operation is started, the RXEMPTY flag is asserted and the interface counters and address pointer are zeroed. The reset operation proceeds to clear out the internal write pointers and counters. The RXEMPTY output remains asserted through the reset operation and remains asserted until new data is written to the Receive FIFO. While RXRST remains asserted, the Receive FIFO remains in reset and cannot accept received characters.<br>When the Receive FIFO is bypassed (FIFOBYP is LOW), RXRST is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 24, 25 | RXMODE[1:0] | Static control input<br>TTL levels<br>Normally wired HIGH or<br>LOW | Receiver Discard Policy Mode Select.<br>00b—allows all characters to be written into the Receive FIFO or output to the<br>Receive data bus<br>01b—discards all JK or LM sync characters except the "last" one of a string of sync<br>characters. Single sync characters in a data stream are included in the data written<br>into the Receive FIFO.<br>1Xb—discards all JK or LM sync characters. The data stream written into the<br>Receive FIFO does not include sync characters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 77     | RXBISTEN    | TTL input,<br>asynchronous<br>Internal Pull-up                      | Receiver BIST Enable. Active LOW.<br>When LOW, the receiver is configured to perform a character-for-character match<br>of the incoming data stream with a 511-character BIST sequence. The result of<br>character mismatches are indicated on the VLTN pin. Completion <u>of each</u><br>511-character BIST loop is accompanied by an assertion pulse on the RXFULL<br>flag.<br>The state of ENCBYP, FIFOBYP, and BYTE8/10 have no effect on BIST operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 73     | RFEN        | TTL input,<br>asynchronous<br>Internal Pull-up                      | Reframe Enable.<br>Used to control when the framer is allowed to adjust the character boundaries<br>based on detection of one or more framing characters in the data stream.<br>When framing is enabled (RFEN is HIGH) the receive framer realigns the serial<br>stream to the incoming 10-bit <u>JK</u> sync character (if BYTE8/10 is HIGH) or the 12-bit<br>LM sync character (if BYTE8/10 is LOW). Framing is disabled when RFEN is LOW.<br>The deassertion of RFEN freezes the character boundary relationship between<br>the serial stream and character clock. RFEN is an asynchronous input, sampled<br>by the internal Receive PLL character clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 10     | RXFULL      | Three-state TTL output,<br>changes following<br>RXCLK↑              | Receive FIFO Full Flag.<br>When the Receive FIFO is enabled (FIFOBYP is HIGH) and its flags are driven<br>(CE is LOW), RXFULL is asserted when space is available for four or fewer<br>characters to be written to the HOTLink Receive FIFO. If the RXCLK input is not<br>continuous or the FIFO is accessed at a rate slower than data is being received,<br>RXFULL may also indicate that some data has been lost because of FIFO overflow.<br>When the Receive FIFO is bypassed (FIFOBYP is LOW), RXFULL is deasserted<br>to indicate that valid data may be present. RXFULL is also used as a BIST progress<br>indicator, and pulses once every pass through the 511 character BIST loop.<br>When RXBISTEN is asserted (LOW), RXFULL becomes the receive BIST loop<br>progress indicator (regardless of the logic state of FIFOBYP). While RXBISTEN<br>is asserted, RXFULL is deasserted for the duration of the BIST pattern, pulsing<br>asserted for one RXCLK period on the last symbol of each BIST loop. If 14 of 28<br>consecutive symbols are received in error, RXFULL returns to the asserted state<br>until the start of a BIST pattern is again detected.<br>The asserted state of this output (HIGH or LOW) is determined by the state of the<br>EXTFIFO input. When EXTFIFO is LOW, RXFULL is active LOW. When EXTFIFO<br>is HIGH, RXFULL is active HIGH. |  |

| Pin    | Name       | I/O Characteristics                                    | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19     | RXHALF     | Three-state TTL output,                                | Receive FIFO Half-full Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19     |            | changes following<br>RXCLK↑                            | When the Receive FIFO is enabled (FIFOBYP is HIGH and CE is LOW) RXHALF<br>is asserted when the HOTLink Receive FIFO is half full (128 characters is half full).<br>If a Receive FIFO reset has been initiated (RXRST was sampled asserted for a<br>minimum of seven RXCLK cycles), RXHALF is deasserted to enforce the<br>empty/unavailable status of the Receive FIFO during reset. If FIFOBYP is LOW,<br><u>RXHALF</u> remains deasserted having no logical function.<br><u>RXHALF</u> is forced to the High-Z state only during a "full-chip" reset (i.e., while<br>RESET is LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21     | RXEMPTY    | Three-state TTL output,<br>changes following<br>RXCLK↑ | Receive FIFO Empty Flag.<br>When the Receive FIFO is enabled (FIFOBYP is HIGH) and its flags are driven<br>(CE is LOW), RXEMPTY is asserted when the HOTLink Receive FIFO has no data<br>to forward to the parallel interface. If a Receive FIFO reset has been initiated<br>(RXRST was sampled asserted for a minimum of seven RXCLK cycles),<br>RXEMPTY is asserted to enforce the empty/unavailable status of the Receive<br>FIFO during reset.<br>Any read operation occurring when RXEMPTY is asserted results in no change in<br>the FIFO status, and the data from the last valid read remains on the RXDATA bus.<br>When the Receive FIFO is bypassed but the decoder is enabled, RXEMPTY is<br>used as a valid data indicator. When deasserted it indicates that valid data is<br>present at the RXDATA or RXCMD outputs as indicated by RXSC/D. When<br>asserted it indicates that a SYNC character (JK or LM) is present on the RXCMD<br>output pins. When the Receive FIFO is bypassed (FIFOBYP is LOW), RXEMPTY<br>is deasserted whenever data is ready.<br>The asserted state of this output (HIGH or LOW) is determined by the state of the<br>EXTFIFO input. When EXTFIFO is LOW, RXEMPTY is active LOW. When<br>EXTFIFO is HIGH, RXEMPTY is active HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Contro | ol Signals |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 71     | CE         | TTL input sampled on<br>TXCLK↑, RXCLK↑, or<br>REFCLK↑  | Chip Enable Input. Active LOW.<br>When CE is asserted and sampled LOW by RXCLK, the Receive FIFO status flags<br>are driven to their active states. When this input is deasserted and sampled by<br>RXCLK, the Receive FIFO status flags are <u>placed</u> in a High-Z state.<br>When CE has been sampled LOW and RXEN changes from deasserted to<br>asserted and is sampled by RXCLK, the RXSC/D, RXDATA[7:0],<br>RXDATA[9:8]/RXCMD[2:3] and VLTN output <u>drivers</u> are enabled and go to their<br>driven levels. These pins remain driven <u>until RXEN</u> is sampled deasserted.<br>When the Transmit FIFO is enabled (FIFOBYP is HIGH), and CE is asserted and<br>sampled by TXCLK, the Transmit FIFO status flags are driven to their active states.<br>When this input is deasserted and sampled by TXCLK, the Transmit FIFO status<br>flags are placed in a High-Z state.<br>When the Transmit FIFO is bypassed (FIFOBYP is LOW), and CE is asserted and<br>sampled by REFCLK, the Transmit FIFO status flags are driven to their active<br>states. When this input is deasserted and sampled by REFCLK, the Transmit FIFO<br>status flags are placed in a High-Z state.<br>When the Transmit FIFO is enabled (FIFOBYP is LOW), and CE is asserted and<br>sampled by REFCLK, the Transmit FIFO status flags are driven to their active<br>states. When this input is deasserted and sampled by REFCLK, the Transmit FIFO<br>status flags are placed in a High-Z state.<br>When the Transmit FIFO is enabled (FIFOBYP is HIGH), CE has been sampled<br>LOW, and TXEN changes from deasserted to asserted and is sampled by TXCLK,<br>the TXSC/D, TXDATA[7:0], TXDATA[9:8]/RXCMD[2:3], and TXCMD[1:0] inputs<br>are sampled and passed to the <u>Transmit FIFO</u> . These inputs are sampled on all<br>consecutive TXCLK cycles until TXEN is sampled deasserted.<br>When the Transmit FIFO is bypassed (FIFOBYP is LOW), CE has been sampled<br>LOW, and TXEN changes from deasserted to asserted and is sampled by<br>REFCLK, the TXSC/D, TXDATA[7:0], TXDATA[9:8]/RXCMD[2:3], and<br>TXCMD[1:0] inputs are sampled and passed to the encoder or serializer as<br>directed by other control inputs. These inputs are sampled |

| Pin | Name     | I/O Characteristics                                                 | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-----|----------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|