# THC63LVD103D

## 160MHz 30bit COLOR LVDS TRANSMITTER

#### **General Description**

The THC63LVD103D transmitter is designed to support pixel data transmission between Host and Flat Panel Display from NTSC up to 1080p(60Hz).

The THC63LVD103D converts 35bits of CMOS/TTL data into four LVDS data streams. The transmitter can be programmed for rising edge or falling edge clock through a dedicated pin. At a transmit clock frequency of 160MHz, 30bits of RGB data and 5bits of timing and control data (HSYNC, VSYNC, DE, CONT1) are transmitted at an effective rate of 1120Mbps per LVDS channel.

#### Application

- •Medium and Small Size Panel

- · Tablet PC / Notebook PC

- · Security Camera / Industrial Camera

- Multi Function Printer

- Industrial Equipment

- ·Medical Equipment Monitor

#### **Features**

- ·Compatible with TIA/EIA-644 LVDS Standard

- •7:1 LVDS Transmitter

- Operating Temperature Range : 0 to +70°C

- ·No Special Start-up Sequence Required

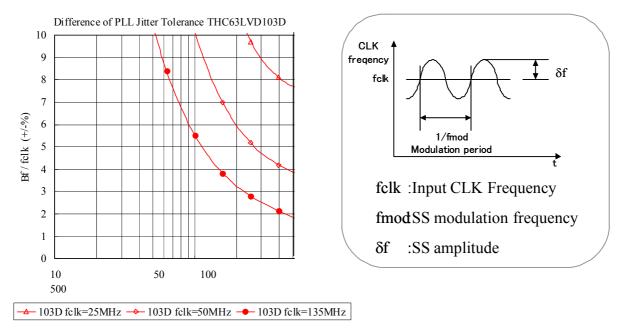

- Spread Spectrum Clocking Tolerant up to 100kHz Frequency Modulation and +/-2.5% Deviations.

- Wide Dot Clock Range: 8 to 160MHz Suited for TV Signal : NTSC(12.27MHz) - 1080p(148.5MHz) PC Signal : QVGA(8MHz) - WUXGA(154MHz)

- ·64pin TQFP Package

- ·1.2V to 3.3V LVCMOS/ inputs are supported.

- •LVDS swing is reducible as 200mV by RS-pin to reduce EMI and power consumption.

- $\cdot$  PLL requires no external components.

- ·Power Down Mode.

- ·Input clock triggering edge is selectable by R/F-pin

- •EU RoHS Compliant.

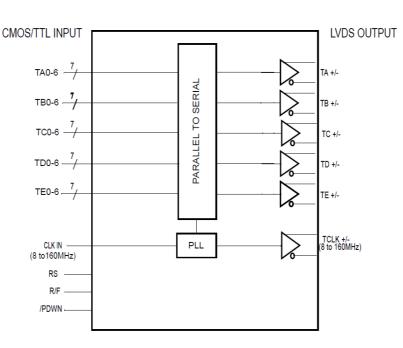

#### **Block Diagram**

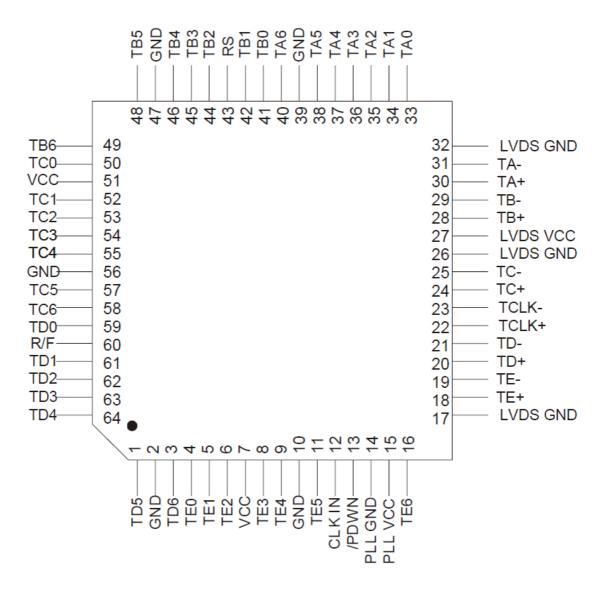

#### Pin Diagram

Figure 2. Pin Diagram

# Pin Description

| Pin Name       | Pin #                      | Direction | Туре   |                  | Descriptio     | n                  |  |

|----------------|----------------------------|-----------|--------|------------------|----------------|--------------------|--|

| TA+, TA-       | 30, 31                     |           |        |                  |                |                    |  |

| TB+, TB-       | 28, 29                     |           |        |                  |                |                    |  |

| TC+, TC-       | 24, 25                     |           |        | LVDS Data Out    |                | LVDS Data Out      |  |

| TD+, TD-       | 20, 21                     | Output    | LVDS   |                  |                |                    |  |

| TE+, TE-       | 18, 19                     |           |        |                  |                |                    |  |

| TCLK+,         | 22, 23                     |           |        | LVDS Clock C     | hut            |                    |  |

| TCLK-          |                            |           |        | LVDS CIOCK C     | Jut            |                    |  |

| $TA0 \sim TA6$ | 33, 34, 35, 36, 37, 38, 40 |           |        |                  |                |                    |  |

| $TB0 \sim TB6$ | 41, 42, 44, 45, 46, 48, 49 |           |        |                  |                |                    |  |

| $TC0 \sim TC6$ | 50, 52, 53, 54, 55, 57, 58 |           |        | Pixel Data Inpu  | ut             |                    |  |

| $TD0 \sim TD6$ | 59, 61, 62, 63, 64, 1, 3   |           |        |                  |                |                    |  |

| TE0 ~ TE6      | 4, 5, 6, 8, 9, 11, 16      |           |        |                  |                |                    |  |

| /PDWN          | 13                         |           |        | H : Normal Op    |                |                    |  |

|                |                            |           |        | L : Power Dow    |                |                    |  |

| RS             | 43                         |           |        | LVDS Swing N     |                | elect See Fig.8, 9 |  |

|                |                            | Input     | LVCMOS | RS               | LVDS           | Small Swing        |  |

|                |                            | mput      | /TTL   | KS               | Swing          | Input Support      |  |

|                |                            |           |        | VCC              | 350mV          | N/A                |  |

|                |                            |           |        | $0.6 \sim 1.4 V$ | 350mV          | RS=VREF            |  |

|                |                            |           |        | GND              | 200mV          | N/A                |  |

|                |                            |           |        | VREF : is Inp    | ut Reference V | Voltage            |  |

| R/F            | 60                         |           |        | Input Clock Tr   | iggering Edge  | Select             |  |

|                |                            |           |        | H : Rising Edg   | e              |                    |  |

|                |                            |           |        | L : Falling Edg  | je             |                    |  |

| CLKIN          | 12                         |           |        | Input Clock      |                |                    |  |

| VCC            | 51, 7                      |           |        | 11 2             |                | CMOS/TLL Inputs    |  |

|                |                            |           |        | and Digital Cir  |                |                    |  |

| GND            | 2, 10, 39, 47, 56          |           |        |                  |                | S/TTL Inputs and   |  |

|                |                            | Power     | -      | Digital Circuit  |                |                    |  |

| LVDS VCC       | 27                         | 100001    |        | Power Supply     |                |                    |  |

| LVDS GND       | 17, 26, 32                 |           |        | Ground Pins fo   |                |                    |  |

| PLL VCC        | 15                         |           |        | Power Supply     |                |                    |  |

| PLL GND        | 14                         |           |        | Ground Supply    | Pin for PLL C  | L'ircuitry.        |  |

Table 1. Pin Description

#### Absolute Maximum Ratings

| Parameter                        | Min  | Max       | Unit |

|----------------------------------|------|-----------|------|

| Supply Voltage (VCC)             | -0.3 | +4.0      | V    |

| LVCMOS/TTL Input Voltage         | -0.3 | VCC + 0.3 | V    |

| LVCMOS/TTL Output Voltage        | -0.3 | VCC + 0.3 | V    |

| LVDS Output Pin                  | -0.3 | VCC + 0.3 | V    |

| Output Current                   |      |           | mA   |

| Junction Temperature             | -    | +125      | °C   |

| Storage Temperature              | -55  | +150      | °C   |

| Reflow Peak Temperature          | -    | +260      | °C   |

| Reflow Peak Temperature Time     | -    | 10        | sec  |

| Maximum Power Dissipation @+25°C | -    | 1.8       | W    |

#### **Table 2. Absolute Maximum Ratings**

#### **Recommended Operating Conditions**

| Symbol | Parameter                     | Min | Тур | Max | Unit |

|--------|-------------------------------|-----|-----|-----|------|

| -      | All Supply Voltage            | 3.0 | 3.3 | 3.6 | V    |

| Та     | Operating Ambient Temperature | 0   | 25  | +70 | °C   |

| -      | Clock Frequency               | 8   | -   | 160 | MHz  |

#### Table 3. Recommended Operating Conditions

"Absolute Maximum Ratings" are those values beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics Table4, 5, 6, 7" specify conditions for device operation.

"Absolute Maximum Rating" value also includes behavior of overshooting and undershooting.

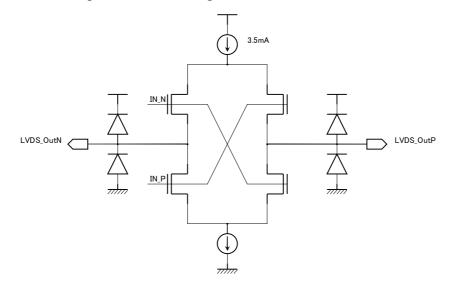

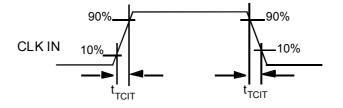

#### Equivalent LVDS Output Schematic Diagram

# Power Consumption

| Symbol            | Parameter                               | Conditions                        | Тур* | Max | Unit |

|-------------------|-----------------------------------------|-----------------------------------|------|-----|------|

| LVDS Transmitter  | RL=100Ω, CL=5pF, f=85MHz, RS=VCC        | 69                                | 75   | mA  |      |

|                   | Operating Current<br>Worst Case Pattern | RL=100Ω, CL=5pF, f=135MHz, RS=VCC | 87   | 93  | mA   |

| I <sub>TCCW</sub> | (Fig.5)                                 | RL=100Ω, CL=5pF, f=160MHz, RS=VCC | 97   | 104 | mA   |

|                   | LVDS Transmitter                        | RL=100Ω, CL=5pF, f=85MHz, RS=GND  | 55   | 61  | mA   |

|                   | Operating Current<br>Worst Case Pattern | RL=100Ω, CL=5pF, f=160MHz, RS=GND | 73   | 79  | mA   |

|                   | (Fig.5)                                 | RL=100Ω, CL=5pF, f=160MHz, RS=GND | 83   | 89  | mA   |

| I <sub>TCCS</sub> | LVDS Transmitter<br>Power Down Current  | /PDWN=L, All Inputs=L or H        | -    | 10  | μΑ   |

\*Typ values are at the conditions of VCC=3.3V and Ta = +25°C

#### Table 4. Power Consumption

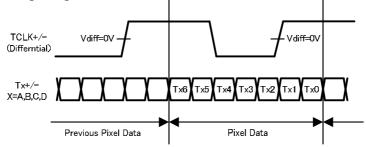

## Worst Case Pattern

x=A,B,C,D

#### Figure 4. Worst Case Pattern

## **Electrical Characteristics**

## LVCMOS/TTL DC Specifications

Over recommended operating supply and temperature range unless otherwise specified

| Symbol                        | Parameter                               | Conditions                           | Min                   | Тур*        | Max                           | Unit |

|-------------------------------|-----------------------------------------|--------------------------------------|-----------------------|-------------|-------------------------------|------|

| V <sub>IH</sub>               | High Level Input Voltage                | RS=VCC or GND                        | 2.0                   | -           | VCC                           | V    |

| V <sub>IL</sub>               | Low Level Input Voltage                 | RS=VCC or GND                        | GND                   | -           | 0.8                           | V    |

| V <sub>DDQ</sub> <sup>1</sup> | Small Swing Voltage                     |                                      | 1.2                   | -           | 2.8                           | V    |

| V <sub>REF</sub>              | Input Reference Voltage                 | Small Swing (RS=V <sub>DDQ</sub> /2) | -                     | $V_{DDQ}/2$ | -                             |      |

| ${\rm V_{SH}}^2$              | Small Swing High Level<br>Input Voltage | $V_{REF=}V_{DDQ}/2$                  | $V_{DDQ}/2$<br>+100mV | -           | -                             | V    |

| $V_{SL}^{2}$                  | Small Swing Low Level<br>Input Voltage  | $V_{REF} = V_{DDQ}/2$                | -                     | -           | V <sub>DDQ</sub> /2<br>-100mV | V    |

| I <sub>INC</sub>              | Input Current                           | $GND \le V_{IN} \le VCC$             | -                     | -           | ±10                           | μΑ   |

\*Typ values are at the conditions of VCC=3.3V and  $Ta = +25^{\circ}C$

Notes :  ${}^{1}V_{DDQ}$  voltage defines the max voltage of small swing inputs at RS=VREF. It is not an actual input voltage.

<sup>2</sup> Small swing signals are applied to TA0-6, TB0-6, TC0-6, TD0-6 and CLKIN.

Table 5. LV-CMOS/TTL DC Specifications

## **LVDS Transmitter DC Specifications**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol                          | Parameter                                         | Co                                         | nditions                | Min   | Тур* | Max   | Unit |

|---------------------------------|---------------------------------------------------|--------------------------------------------|-------------------------|-------|------|-------|------|

| VOD Differential Output Voltage |                                                   | RL=100Ω                                    | Normal swing<br>RS=VCC  | 250   | 350  | 450   | mV   |

| VOD                             | Differential Output Voltage                       | KL-10032                                   | Reduced swing<br>RS=GND | 100   | 200  | 300   | mV   |

| ΔVOD                            | Change in VOD between complementary output states |                                            |                         | -     | -    | 35    | mV   |

| VOC                             | Common Mode Voltage                               | RL=100Ω                                    |                         | 1.125 | 1.25 | 1.375 | V    |

| ΔVOC                            | Change in VOC between complementary output states |                                            |                         | -     | -    | 35    | mV   |

| I <sub>OS</sub>                 | Output Short Circuit Current                      | $V_{OUT}$ =GND, RL=100 $\Omega$            |                         | -     | -    | -24   | mA   |

| I <sub>OZ</sub>                 | Output TRI-STATE Current                          | /PDWN=GND,<br>V <sub>OUT</sub> =GND to VCC |                         | -     | -    | ±10   | μΑ   |

\*Typ values are at the conditions of VCC=3.3V and Ta = +25°C

### Table 6. LVDS Transmitter DC Specifications

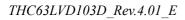

| Over recommended operating supply and temperature range unless otherwise specified |                                         |           |      |           |      |  |  |

|------------------------------------------------------------------------------------|-----------------------------------------|-----------|------|-----------|------|--|--|

| Symbol                                                                             | Parameter                               | Min       | Тур  | Max       | Unit |  |  |

| t <sub>TCIT</sub>                                                                  | CLK IN Transition Time                  | -         | -    | 5.0       | ns   |  |  |

| t <sub>TCP</sub>                                                                   | CLK IN Period                           | 6.25      | Т    | 125       | ns   |  |  |

| t <sub>TCH</sub>                                                                   | CLK IN High Time                        | 0.35T     | 0.5T | 0.65T     | ns   |  |  |

| t <sub>TCL</sub>                                                                   | CLK IN Low Time                         | 0.35T     | 0.5T | 0.65T     | ns   |  |  |

| t <sub>TCD</sub>                                                                   | CLK IN to TCLK+/- Delay                 | -         | 3T   | -         | ns   |  |  |

| t <sub>TS</sub>                                                                    | LVCMOS/TTL Data Setup to CLK IN         | 2.0       | -    | -         | ns   |  |  |

| t <sub>TH</sub>                                                                    | LVCMOS/TTL Data Hold from CLK IN        | 0.0       | -    | -         | ns   |  |  |

| t <sub>LVT</sub>                                                                   | LVDS Transition Time                    | -         | 0.6  | 1.5       | ns   |  |  |

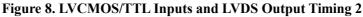

| t <sub>TOP1</sub>                                                                  | Output Data Position0 (T=6.25ns ~ 20ns) | -0.15     | 0.0  | +0.15     | ns   |  |  |

| t <sub>Top0</sub>                                                                  | Output Data Position1 (T=6.25ns ~ 20ns) | T/7-0.15  | T/7  | T/7+0.15  | ns   |  |  |

| t <sub>Top6</sub>                                                                  | Output Data Position2 (T=6.25ns ~ 20ns) | 2T/7-0.15 | 2T/7 | 2T/7+0.15 | ns   |  |  |

| t <sub>Top5</sub>                                                                  | Output Data Position3 (T=6.25ns ~ 20ns) | 3T/7-0.15 | 3T/7 | 3T/7+0.15 | ns   |  |  |

| t <sub>Top4</sub>                                                                  | Output Data Position4 (T=6.25ns ~ 20ns) | 4T/7-0.15 | 4T/7 | 4T/7+0.15 | ns   |  |  |

| t <sub>Top3</sub>                                                                  | Output Data Position5 (T=6.25ns ~ 20ns) | 5T/7-0.15 | 5T/7 | 5T/7+0.15 | ns   |  |  |

| t <sub>Top2</sub>                                                                  | Output Data Position6 (T=6.25ns ~ 20ns) | 6T/7-0.15 | 6T/7 | 6T/7+0.15 | ns   |  |  |

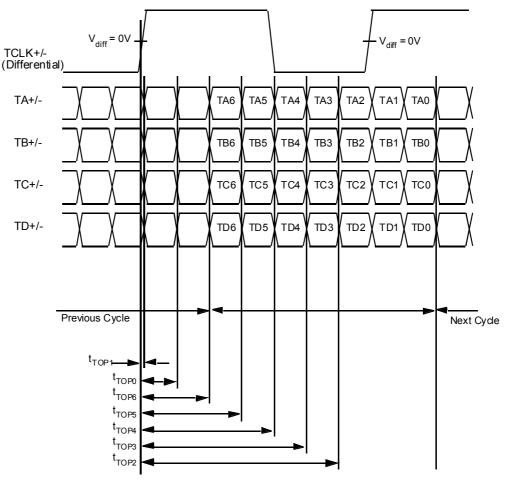

| t <sub>TPLL</sub>                                                                  | Phase Lock Loop Set                     | -         | -    | 10.0      | ms   |  |  |

# LVCMOS/TTL & LVDS Transmitter AC Specifications

\*Typ values are at the conditions of VCC=3.3V and Ta = +25°C

#### Table 7. LVCMOS/TTL & LVDS Transmitter AC Specifications

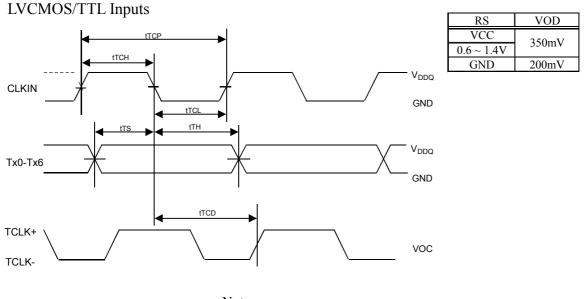

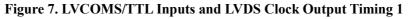

LVCMOS/TTL Input

Figure 5. CLKIN Transmission Time

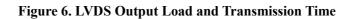

LVDS Output Load

## AC Timing Diagrams

Note : CLKIN : Solis line denotes the setting of R/F=GND Dashed line denotes the setting of R/F = VCC

# LVDS Output Data Position

Phase Lock Loop Set Time

#### Spread Spectrum Clocking Tolerant

Figure 11. Spread Spectrum Clocking Tolerant

The graph indicates the range that the IC works normally under SS clock input operation. The results are measured with a typical sample on condition of +25C° and 3.3V, therefore these

values are for reference and do not guarantee the performance of a product under other circumstance.

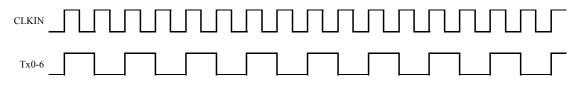

#### LVDS Data Timing Diagram

Figure 12. LVDS Data Timing Diagram

THC63LVD103D Pixel Data Mapping for JEIDA Format (6bit, 8bit and 10bit Application)

|            | 6bit  | 8bit  | 10bit |

|------------|-------|-------|-------|

| TA0        | R4    | R4    | R4    |

| TA1        | R5    | R5    | R5    |

| TA2        | R6    | R6    | R6    |

| TA3        | R7    | R7    | R7    |

| TA4        | R8    | R8    | R8    |

| TA5        | R9    | R9    | R9    |

| TA6        | G4    | G4    | G4    |

| TB0        | G5    | G5    | G5    |

| TB1        | G6    | G6    | G6    |

| TB2        | G7    | G7    | G7    |

| TB3        | G8    | G8    | G8    |

| TB4        | G9    | G9    | G9    |

| TB5        | B4    | B4    | B4    |

| TB6        | B5    | B5    | В5    |

| TC0        | B6    | B6    | B6    |

| TC1        | B7    | B7    | B7    |

| TC2        | B8    | B8    | B8    |

| TC3        | B9    | B9    | B9    |

| TC4        | Hsync | Hsync | Hsync |

| TC5        | Vsync | Vsync | Vsync |

| TC6        | DE    | DE    | DE    |

| TD0        | -     | R2    | R2    |

| TD1        | -     | R3    | R3    |

| TD2        | -     | G2    | G2    |

| TD3        | -     | G3    | G3    |

| TD4        | -     | B2    | B2    |

| TD5        | -     | B3    | B3    |

| TD6        | -     | N/A   | N/A   |

| TE0        | -     | -     | R0    |

| TE1        | -     | -     | R1    |

| TE2        | -     | -     | G0    |

| TE3        | -     | -     | G1    |

|            | -     | -     | B0    |

| TE4        | -     |       |       |

| TE4<br>TE5 | -     | _     | B1    |

Note : Use TA to TC channels and open TD channel for 6bit application. Use TA to TD channels and open TE channel for 8bit application.

Table 8. Data Mapping for JEIDA Format

|     | 6bit  | 8bit  | 10bit |

|-----|-------|-------|-------|

| TA0 | R0    | R0    | R0    |

| TA1 | R1    | R1    | R1    |

| TA2 | R2    | R2    | R2    |

| TA3 | R3    | R3    | R3    |

| TA4 | R4    | R4    | R4    |

| TA5 | R5    | R5    | R5    |

| TA6 | G0    | G0    | G0    |

| TB0 | Gl    | G1    | G1    |

| TB1 | G2    | G2    | G2    |

| TB2 | G3    | G3    | G3    |

| TB3 | G4    | G4    | G4    |

| TB4 | G5    | G5    | G5    |

| TB5 | B0    | B0    | B0    |

| TB6 | B1    | B1    | B1    |

| TC0 | B2    | B2    | B2    |

| TC1 | B3    | B3    | B3    |

| TC2 | B4    | B4    | B4    |

| TC3 | В5    | B5    | B5    |

| TC4 | Hsync | Hsync | Hsync |

| TC5 | Vsync | Vsync | Vsync |

| TC6 | DE    | DE    | DE    |

| TD0 | -     | R6    | R6    |

| TD1 | -     | R7    | R7    |

| TD2 | -     | G6    | G6    |

| TD3 | -     | G7    | G7    |

| TD4 | -     | B6    | B6    |

| TD5 | -     | B7    | B7    |

| TD6 | -     | N/A   | N/A   |

| TE0 | -     | -     | R8    |

| TE1 | -     | -     | R9    |

| TE2 | -     | -     | G8    |

| TE3 | -     | -     | G9    |

| TE4 | -     | -     | B8    |

| TE5 | -     | -     | B9    |

| TE6 | -     | -     | N/A   |

#### THC63LVD103D Pixel Data Mapping for VESA Format (6bit, 8bit and 10bit Application)

Note : Use TA to TC channels and open TD channel for 6bit application. Use TA to TD channels and open TE channel for 8bit application.

Table 9. Data Mapping for VESA Format

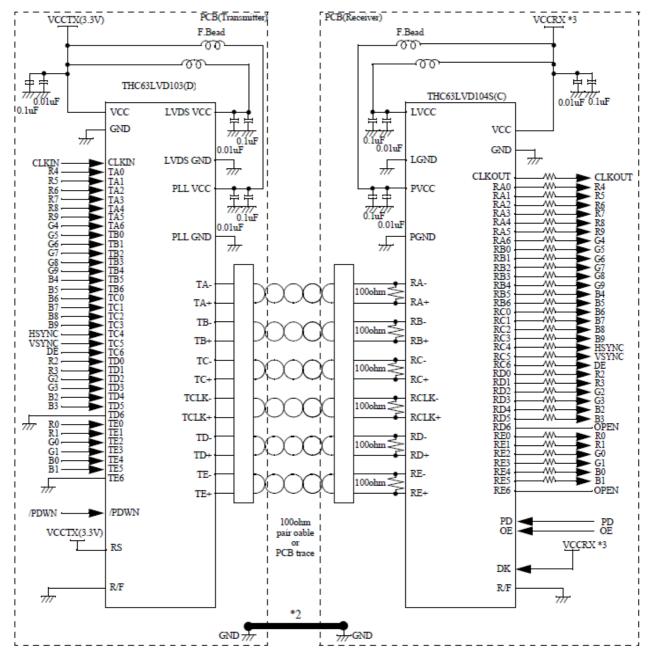

## Normal Connection with JEIDA Format

# Example

THC63LVD103D : Falling Edge / Normal Swing

Figure 13. Typical Connection Diagram

#### Notes

- Cable Connection and Disconnection Do not connect and disconnect the LVDS cable, when the power is supplied to the system.

- 2) GND Connection

Connect each GND of the PCB which THC63LVDM83D and LVDS-Rx on it. It is better for EMI reduction to place GND cable as close to LVDS cable as possible.

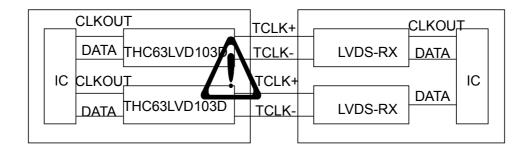

#### 3) Multi Drop Connection

Multi drop connection is not recommended.

Figure 14. Multi Drop Connection

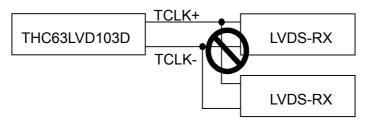

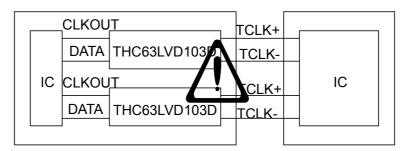

#### 4) Asynchronous use

Asynchronous using such as following systems is not recommended.

Figure 15. Asynchronous Use

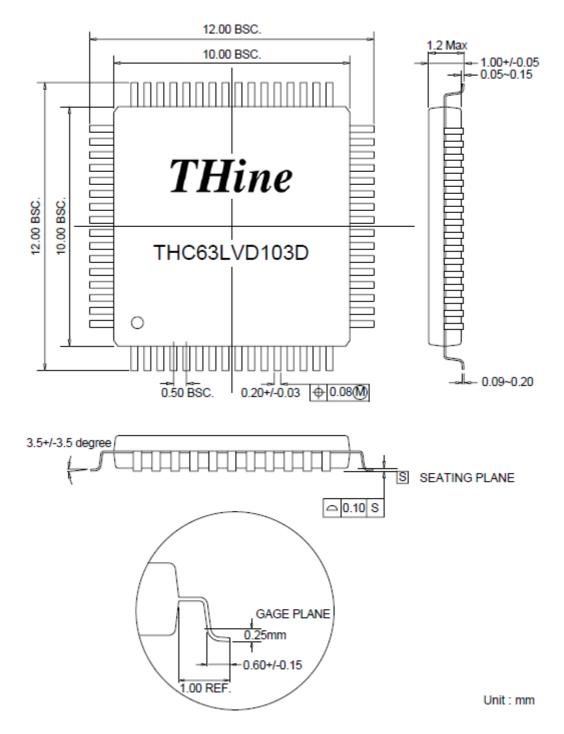

# Package

Figure 16. Package Diagram

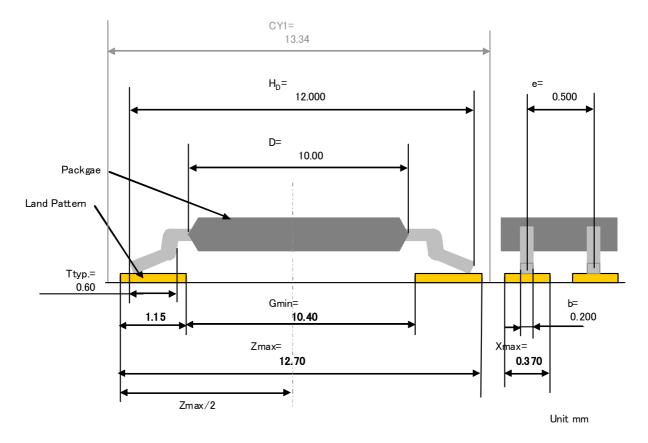

# Reference Land Pattern

Figure 17. Reference of Land Pattern

The recommendation mounting method of THine device is reflow soldering. The reference pattern is using the calculation result on condition of reflow soldering.

Notes

This land pattern design is a calculated value based on JEITA ET-7501.

Please take into consideration in an actual substrate design about enough the ease of mounting, the intensity of connection, the density of mounting, and the solder paste used, etc... The optimal land pattern size changes with these parameters. Please use the value shown by the land pattern as reference data.

# **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. We are not responsible for possible errors and omissions in this material. Please note if errors or omissions should be found in this material, we may not be able to correct them immediately.

- 3. This material contains our copyright, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without our prior permission is prohibited.

- 4. Note that if infringement of any third party's industrial ownership should occur by using this product, we will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

- 5. This product is presumed to be used for general electric equipment, not for the applications which require very high reliability (including medical equipment directly concerning people's life, aerospace equipment, or nuclear control equipment). Also, when using this product for the equipment concerned with the control and safety of the transportation means, the traffic signal equipment, or various Types of safety equipment, please do it after applying appropriate measures to the product.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Control Law.

THine Electronics, Inc. sales@thine.co.jp