# TEXAS INSTRUMENTS

Data sheet acquired from Harris Semiconductor SCHS177B

November 1997 - Revised May 2003

### Features

- Digital Design Avoids Analog Compensation Errors

- Easily Cascadable for Higher Order Loops

- Useful Frequency Range

- K-Clock.....DC to 55MHz (Typ)

- I/D-Clock ..... DC to 35MHz (Typ)

- Dynamically Variable Bandwidth

- Very Narrow Bandwidth Attainable

- Power-On Reset

- Output Capability

- Standard...... XORPD<sub>OUT</sub>, ECPD<sub>OUT</sub>

- Bus Driver ..... I/D<sub>OUT</sub>

- Fanout (Over Temperature Range)

- Standard Outputs ..... 10 LSTTL Loads

- Bus Driver Outputs ..... 15 LSTTL Loads

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- 'HC297 Types

- Operation Voltage ...... 2 to 6V

- High Noise Immunity  $N_{IL}$  = 30%,  $N_{IH}$  = 30% of  $V_{CC}$  at 5V

- CD74HCT297 Types

- Direct LSTTL Input Logic Compatibility  $V_{IL} = 0.8V$  (Max),  $V_{IH} = 2V$  (Min)

- CMOS Input Compatibility IJ  $\leq$  1µA at VOL, VOH

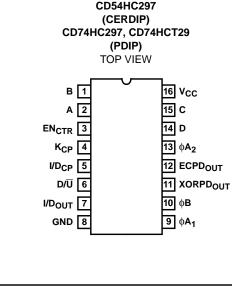

### Pinout

# CD54HC297, CD74HC297, CD74HCT297

## High-Speed CMOS Logic Digital Phase-Locked Loop

### Description

The 'HC297 and CD74HCT297 are high-speed silicon gate CMOS devices that are pin-compatible with low power Schottky TTL (LSTTL).

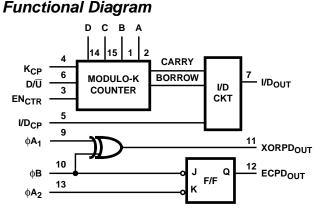

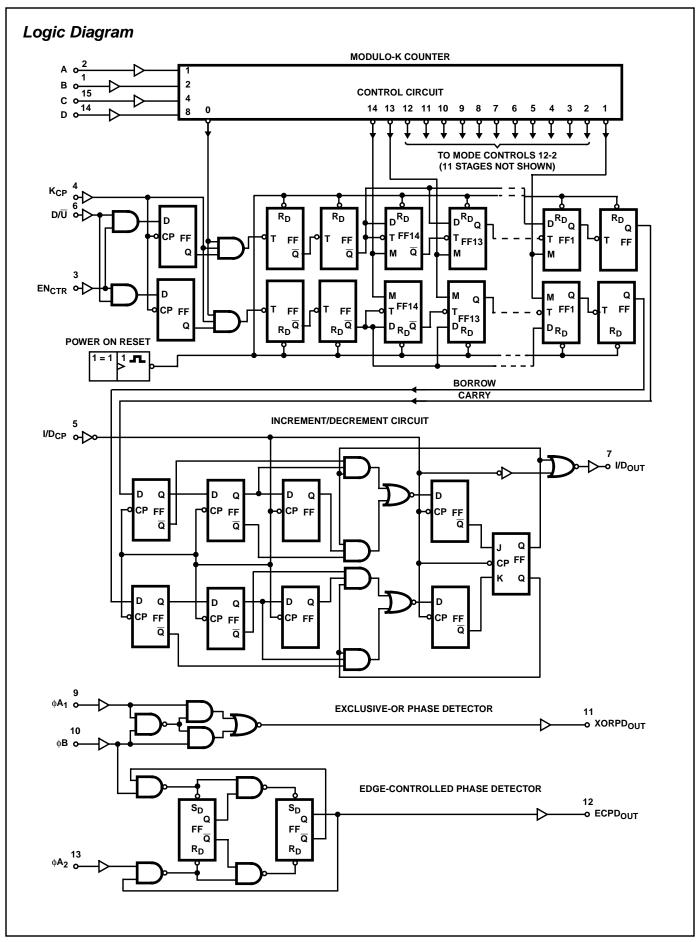

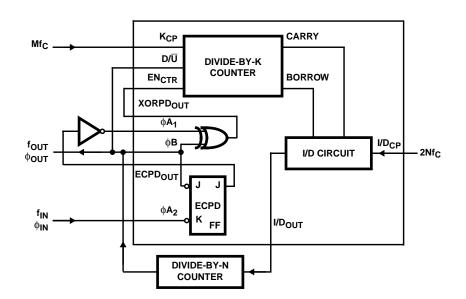

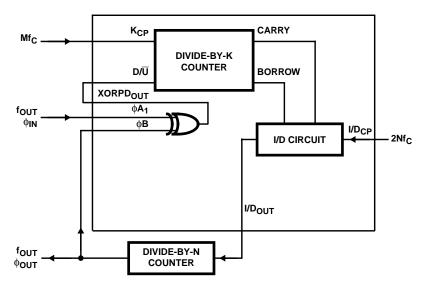

These devices are designed to provide a simple, cost-effective solution to high-accuracy, digital, phase-locked-loop applications. They contain all the necessary circuits, with the exception of the divide-by-N counter, to build first-order phase-locked-loops.

Both EXCLUSIVE-OR (XORPD) and edge-controlled phase detectors (ECPD) are provided for maximum flexibility. The input signals for the EXCLUSIVE-OR phase detector must have a 50% duty factor to obtain the maximum lock-range.

Proper partitioning of the loop function, with many of the building blocks external to the package, makes it easy for the designer to incorporate ripple cancellation (see Figure 2) or to cascade to higher order phase-locked-loops.

The length of the up/down K-counter is digitally programmable according to the K-counter function table. With A, B, C and D all LOW, the K-counter is disabled. With A HIGH and B, C and D LOW, the K-counter is only three stages long, which widens the bandwidth or capture range and shortens the lock time of the loop. When A, B, C and D are all programmed HIGH, the K-counter becomes seventeen stages long, which narrows the bandwidth or capture range and lengthens the lock time. Real-time control of loop bandwidth by manipulating the A to D inputs can maximize the overall performance of the digital phase-locked-loop.

The 'HC297 and CD74HCT297 can perform the classic first order phase-locked-loop function without using analog components. The accuracy of the digital phase-locked-loop (DPLL) is not affected by  $V_{CC}$  and temperature variations but depends solely on accuracies of the K-clock and loop propagation delays.

### **Ordering Information**

| PART NUMBER  | TEMP. RANGE ( <sup>o</sup> C) | PACKAGE      |

|--------------|-------------------------------|--------------|

| CD54HC297F3A | -55 to 125                    | 16 Ld CERDIP |

| CD74HC297E   | -55 to 125                    | 16 Ld PDIP   |

| CD74HCT297E  | -55 to 125                    | 16 Ld PDIP   |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright © 2003, Texas Instruments Incorporated

The phase detector generates an error signal waveform that, at zero phase error, is a 50% duty factor square wave. At the limits of linear operation, the phase detector output will be either HIGH or LOW all of the time depending on the direction of the phase error ( $\phi$ IN -  $\phi$ OUT). Within these limits the phase detector output varies linearly with the input phase error according to the gain K<sub>d</sub>, which is expressed in terms of phase detector output can be defined to vary between ±1 according to the relation:

phase detector output =  $\frac{\%$ HIGH - %LOW}{100}

The output of the phase detector will be  $K_d\varphi_e,$  where the phase error  $\varphi_e$  =  $\varphi IN$  -  $\varphi OUT.$

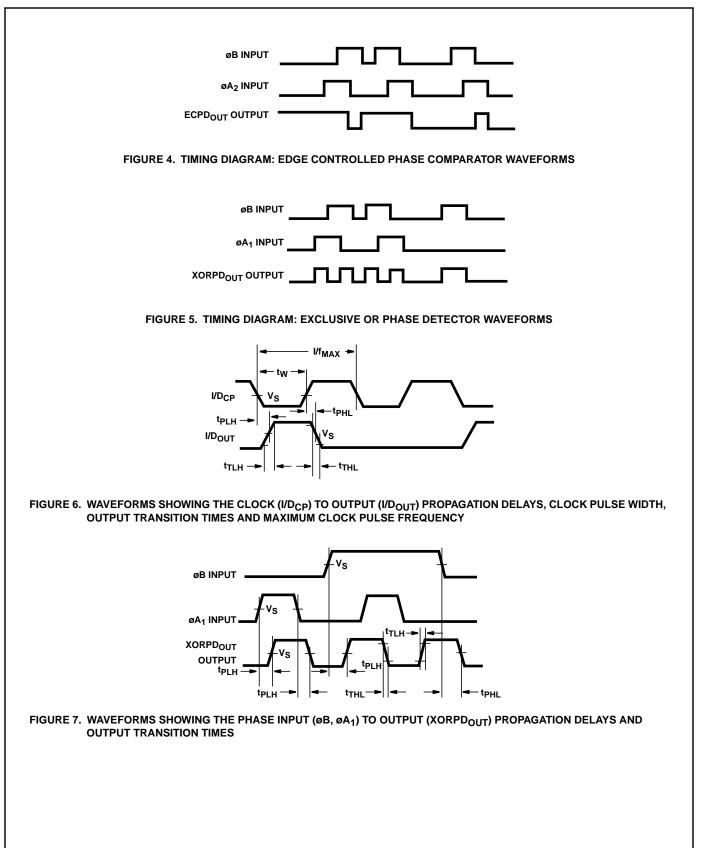

EXCLUSIVE-OR phase detectors (XORPD) and edge-controlled phase detectors (ECPD) are commonly used digital types. The ECPD is more complex than the XORPD logic function but can be described generally as a circuit that changes states on one of the transitions of its inputs. The gain (K<sub>d</sub>) for an XORPD is 4 because its output remains HIGH (XORPD<sub>OUT</sub> = 1) for a phase error of one quarter cycle.

Similarly, K<sub>d</sub> for the ECPD is 2 since its output remains HIGH for a phase error of one half cycle. The type of phase detector will determine the zero-phase-error point, i.e., the phase separation of the phase detector inputs for a  $\phi e$  defined to be zero. For the basic DPLL system of Figure 3,  $\phi e = 0$  when the phase detector output is a square wave.

The XORPD inputs are one quarter cycle out-of-phase for zero phase error. For the ECPD,  $\phi e = 0$  when the inputs are one half cycle out of phase.

The phase detector output controls the up/down input to the K-counter. The counter is clocked by input frequency  $Mf_c$  which is a multiple M of the loop center frequency  $f_c$ . When the K-counter recycles up, it generates a carry pulse. Recycling while counting down generates a borrow pulse. If the carry and the borrow outputs are conceptually combined into one output that is positive for a carry and negative for a borrow, and if the K-counter is considered as a frequency divider with the ratio  $Mf_c/K$ , the output of the K-counter will equal the input frequency multiplied by the division ratio. Thus the output from the K-counter is  $(K_d \phi_e Mf_c)/K$ .

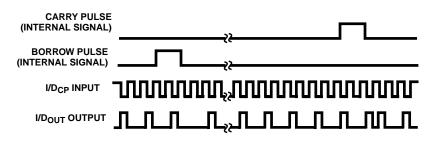

The carry and borrow pulses go to the increment/decrement (I/D) circuit which, in the absence of any carry or borrow pulses has an output that is one half of the input clock (I/D<sub>CP</sub>). The input clock is just a multiple, 2N, of the loop center frequency. In response to a carry of borrow pulse, the I/D circuit will either add or delete a pulse at I/D<sub>OUT</sub>. Thus the output of the I/D circuit will be Nf<sub>c</sub> + (K<sub>d</sub> $\phi$ eMf<sub>c</sub>)/2K.

The output of the N-counter (or the output of the phase-locked-loop) is thus:  $f_0 = f_c + (K_d \phi_e M f_c)/2KN$ .

If this result is compared to the equation for a first-order analog phase-locked-loop, the digital equivalent of the gain of the VCO is just  $Mf_c/2KN$  or  $f_c/K$  for M = 2N.

Thus, the simple first-order phase-locked-loop with an adjustable K-counter is the equivalent of an analog phase-lockedloop with a programmable VCO gain.

FUNCTION TABLE EXCLUSIVE-OR PHASE DETECTOR

| φ <b>Α</b> 1 | φΒ | XORPD OUT |

|--------------|----|-----------|

| L            | L  | L         |

| L            | Н  | Н         |

| Н            | L  | Н         |

| Н            | Н  | L         |

FUNCTION TABLE EDGE-CONTROLLED PHASE DETECTOR

| φ <b>Α</b> 2 | φΒ            | ECPD OUT  |

|--------------|---------------|-----------|

| H or L       | $\rightarrow$ | Н         |

| $\downarrow$ | H or L        | L         |

| H or L       | ↑             | No Change |

| ↑            | H or L        | No Change |

H = Steady-State High Level, L = Steady-State Low Level,  $\uparrow$  = LOW to HIGH  $\phi$  Transition,  $\downarrow$  = HIGH to LOW  $\phi$  Transition

#### K-COUNTER FUNCTION TABLE (DIGITAL CONTROL)

| D | с | в | А | MODULO<br>(K)   |

|---|---|---|---|-----------------|

| L | L | L | L | Inhibited       |

| L | L | L | Н | 2 <sup>3</sup>  |

| L | L | Н | L | 2 <sup>4</sup>  |

| L | L | Н | Н | 2 <sup>5</sup>  |

| L | Н | L | L | 2 <sup>6</sup>  |

| L | Н | L | Н | 2 <sup>7</sup>  |

| L | Н | Н | L | 2 <sup>8</sup>  |

| L | Н | Н | Н | 2 <sup>9</sup>  |

| н | L | L | L | 2 <sup>10</sup> |

| н | L | L | Н | 2 <sup>11</sup> |

| н | L | Н | L | 2 <sup>12</sup> |

| Н | L | Н | Н | 2 <sup>13</sup> |

| н | Н | L | L | 2 <sup>14</sup> |

| н | Н | L | Н | 2 <sup>15</sup> |

| н | Н | Н | L | 2 <sup>16</sup> |

| Н | Н | Н | Н | 2 <sup>17</sup> |

### **Absolute Maximum Ratings**

| DC Supply Voltage, V <sub>CC</sub> 0.5V to 7V<br>DC Input Diode Current, I <sub>IK</sub> |

|------------------------------------------------------------------------------------------|

| For $V_{l} < -0.5V$ or $V_{l} > V_{CC} + 0.5V$                                           |

| DC Output Diode Current, I <sub>OK</sub>                                                 |

| For $V_0 < -0.5V$ or $V_0 > V_{CC} + 0.5V$                                               |

| DC Drain Current, per Output, IO                                                         |

| For -0.5V < V <sub>O</sub> < V <sub>CC</sub> + 0.5V±25mA                                 |

| DC Output Source or Sink Current per Output Pin, IO                                      |

| For $V_0 > -0.5V$ or $V_0 < V_{CC} + 0.5V$ ±25mA                                         |

| DC V <sub>CC</sub> or Ground Current, I <sub>CC</sub> ±50mA                              |

|                                                                                          |

### **Operating Conditions**

| Temperature Range, T <sub>A</sub>                                                 |

|-----------------------------------------------------------------------------------|

| Supply Voltage Range, V <sub>CC</sub>                                             |

| HC Types                                                                          |

| HCT Types4.5V to 5.5V                                                             |

| DC Input or Output Voltage, V <sub>I</sub> , V <sub>O</sub> 0V to V <sub>CC</sub> |

| Input Rise and Fall Time                                                          |

| 2V                                                                                |

| 4.5V 500ns (Max)                                                                  |

| 6V                                                                                |

|                                                                                   |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | θ <sub>JA</sub> ( <sup>o</sup> C/W)     |

|------------------------------------------|-----------------------------------------|

| E (PDIP) Package                         | . 67                                    |

| Maximum Junction Temperature             | 150 <sup>0</sup> C                      |

| Maximum Storage Temperature Range        | 65 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 10s) | 300 <sup>0</sup> C                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1. The package thermal impedance is calculated in accordance with JESD 51-7.

### **DC Electrical Specifications**

|                                                            |                 | TEST<br>CONDITIONS                      |                     |                     | 25 <sup>0</sup> C |     |      | -40 <sup>0</sup> C TO 85 <sup>0</sup> C |                | -55°C TO 125°C |      |   |   |      |   |     |   |   |

|------------------------------------------------------------|-----------------|-----------------------------------------|---------------------|---------------------|-------------------|-----|------|-----------------------------------------|----------------|----------------|------|---|---|------|---|-----|---|---|

| PARAMETER                                                  | SYMBOL          | V <sub>I</sub> (V)                      | I <sub>O</sub> (mA) | v <sub>cc</sub> (v) | MIN               | ТҮР | MAX  | MIN                                     | MAX            | MIN            | MAX  |   |   |      |   |     |   |   |

| HC TYPES                                                   |                 |                                         |                     |                     |                   |     |      |                                         |                |                |      |   |   |      |   |     |   |   |

| High Level Input                                           | V <sub>IH</sub> | -                                       | -                   | 2                   | 1.5               | -   | -    | 1.5                                     | -              | 1.5            | -    | V |   |      |   |     |   |   |

| Voltage                                                    |                 |                                         |                     | 4.5                 | 3.15              | -   | -    | 3.15                                    | -              | 3.15           | -    | V |   |      |   |     |   |   |

|                                                            |                 |                                         |                     | 6                   | 4.2               | -   | -    | 4.2                                     | -              | 4.2            | -    | V |   |      |   |     |   |   |

| Low Level Input                                            | VIL             | -                                       | -                   | 2                   | -                 | -   | 0.5  | -                                       | 0.5            | -              | 0.5  | V |   |      |   |     |   |   |

| Voltage                                                    |                 |                                         |                     | 4.5                 | -                 | -   | 1.35 | -                                       | 1.35           | -              | 1.35 | V |   |      |   |     |   |   |

|                                                            |                 |                                         |                     | 6                   | -                 | -   | 1.8  | -                                       | 1.8            | -              | 1.8  | V |   |      |   |     |   |   |

| High Level Output V <sub>OH</sub><br>Voltage<br>CMOS Loads | V <sub>OH</sub> | H V <sub>IH</sub> or<br>V <sub>IL</sub> | -0.02               | 2                   | 1.9               | -   | -    | 1.9                                     | -              | 1.9            | -    | V |   |      |   |     |   |   |

|                                                            |                 |                                         | -0.02               | 4.5                 | 4.4               | -   | -    | 4.4                                     | -              | 4.4            | -    | V |   |      |   |     |   |   |

|                                                            |                 |                                         | -0.02               | 6                   | 5.9               | -   | -    | 5.9                                     | -              | 5.9            | -    | V |   |      |   |     |   |   |

| High Level Output<br>Voltage                               |                 |                                         |                     |                     |                   |     |      |                                         | -6<br>(Note 2) | 4.5            | 3.98 | - | - | 3.84 | - | 3.7 | - | V |

| TTL Loads                                                  |                 |                                         | -7.8<br>(Note 2)    | 6                   | 5.48              | -   | -    | 5.34                                    | -              | 5.2            | -    | V |   |      |   |     |   |   |

| Low Level Output                                           | V <sub>OL</sub> | V <sub>IH</sub> or                      | 0.02                | 2                   | -                 | -   | 0.1  | -                                       | 0.1            | -              | 0.1  | V |   |      |   |     |   |   |

| Voltage<br>CMOS Loads                                      |                 | $V_{IL}$                                | 0.02                | 4.5                 | -                 | -   | 0.1  | -                                       | 0.1            | -              | 0.1  | V |   |      |   |     |   |   |

|                                                            |                 |                                         | 0.02                | 6                   | -                 | -   | 0.1  | -                                       | 0.1            | -              | 0.1  | V |   |      |   |     |   |   |

| Low Level Output<br>Voltage                                |                 |                                         | 4<br>(Note 2)       | 4.5                 | -                 | -   | 0.26 | -                                       | 0.33           | -              | 0.4  | V |   |      |   |     |   |   |

| TTL Loads                                                  |                 |                                         | 5.2<br>(Note 2)     | 6                   | -                 | -   | 0.26 | -                                       | 0.33           | -              | 0.4  | V |   |      |   |     |   |   |

|                                                                      |                              | TEST<br>CONDITIONS                    |                     |                     | 25 <sup>0</sup> C |     |      | -40°C TO 85°C |      | -55°C TO 125°C |     |       |

|----------------------------------------------------------------------|------------------------------|---------------------------------------|---------------------|---------------------|-------------------|-----|------|---------------|------|----------------|-----|-------|

| PARAMETER                                                            | SYMBOL                       | V <sub>I</sub> (V)                    | I <sub>O</sub> (mA) | V <sub>CC</sub> (V) | MIN               | ТҮР | MAX  | MIN           | MAX  | MIN            | MAX | UNITS |

| Input Leakage<br>Current                                             | lı                           | V <sub>CC</sub> or<br>GND             | -                   | 6                   | -                 | -   | ±0.1 | -             | ±1   | -              | ±1  | μA    |

| Quiescent Device<br>Current                                          | Icc                          | V <sub>CC</sub> or<br>GND             | 0                   | 6                   | -                 | -   | 8    | -             | 80   | -              | 160 | μA    |

| HCT TYPES                                                            |                              |                                       |                     |                     |                   |     |      |               |      |                |     |       |

| High Level Input<br>Voltage                                          | VIH                          | -                                     | -                   | 4.5 to<br>5.5       | 2                 | -   | -    | 2             | -    | 2              | -   | V     |

| Low Level Input<br>Voltage                                           | V <sub>IL</sub>              | -                                     | -                   | 4.5 to<br>5.5       | -                 | -   | 0.8  | -             | 0.8  | -              | 0.8 | V     |

| High Level Output<br>Voltage<br>CMOS Loads                           | V <sub>OH</sub>              | V <sub>IH</sub> or<br>V <sub>IL</sub> | -0.02               | 4.5                 | 4.4               | -   | -    | 4.4           | -    | 4.4            | -   | V     |

| High Level Output<br>Voltage<br>TTL Loads                            |                              |                                       | -4                  | 4.5                 | 3.98              | -   | -    | 3.84          | -    | 3.7            | -   | V     |

| Low Level Output<br>Voltage<br>CMOS Loads                            | V <sub>OL</sub>              | V <sub>IH</sub> or<br>V <sub>IL</sub> | 0.02                | 4.5                 | -                 | -   | 0.1  | -             | 0.1  | -              | 0.1 | V     |

| Low Level Output<br>Voltage<br>TTL Loads                             |                              |                                       | 4                   | 4.5                 | -                 | -   | 0.26 | -             | 0.33 | -              | 0.4 | V     |

| Input Leakage<br>Current                                             | lı                           | V <sub>CC</sub> to<br>GND             | 0                   | 5.5                 | -                 | -   | ±0.1 | -             | ±1   | -              | ±1  | μA    |

| Quiescent Device<br>Current                                          | Icc                          | V <sub>CC</sub> or<br>GND             | 0                   | 5.5                 | -                 | -   | 8    | -             | 80   | -              | 160 | μA    |

| Additional Quiescent<br>Device Current Per<br>Input Pin: 1 Unit Load | ∆I <sub>CC</sub><br>(Note 2) | V <sub>CC</sub><br>-2.1               | -                   | 4.5 to<br>5.5       | -                 | 100 | 360  | -             | 450  | -              | 490 | μA    |

NOTE:

2. For dual-supply systems theoretical worst case (V<sub>I</sub> = 2.4V, V<sub>CC</sub> = 5.5V) specification is 1.8mA.

### **HCT Input Loading Table**

| INPUT                                         | UNIT LOADS |

|-----------------------------------------------|------------|

| EN <sub>CTR</sub> , D/Ū                       | 0.3        |

| Α, Β, C, D, K <sub>CP</sub> , φΑ <sub>2</sub> | 0.6        |

| I/D <sub>CP</sub> , φA <sub>1</sub> , φΒ      | 1.5        |

NOTE: Unit Load is  $\Delta I_{CC}$  limit specified in DC Electrical Specifications table, e.g., 360µA max at 25°C.

### **Prerequisite For Switching Function**

|                                                          | SYMBOL           |                     | 25  | <sup>o</sup> C | -40°C 1 | ГО 85 <sup>0</sup> С | -55°C T | O 125 <sup>0</sup> C | UNITS |

|----------------------------------------------------------|------------------|---------------------|-----|----------------|---------|----------------------|---------|----------------------|-------|

| PARAMETER                                                |                  | V <sub>CC</sub> (V) | MIN | MAX            | MIN     | MAX                  | MIN     | MAX                  |       |

| HC TYPES                                                 |                  |                     |     |                |         | •                    |         |                      |       |

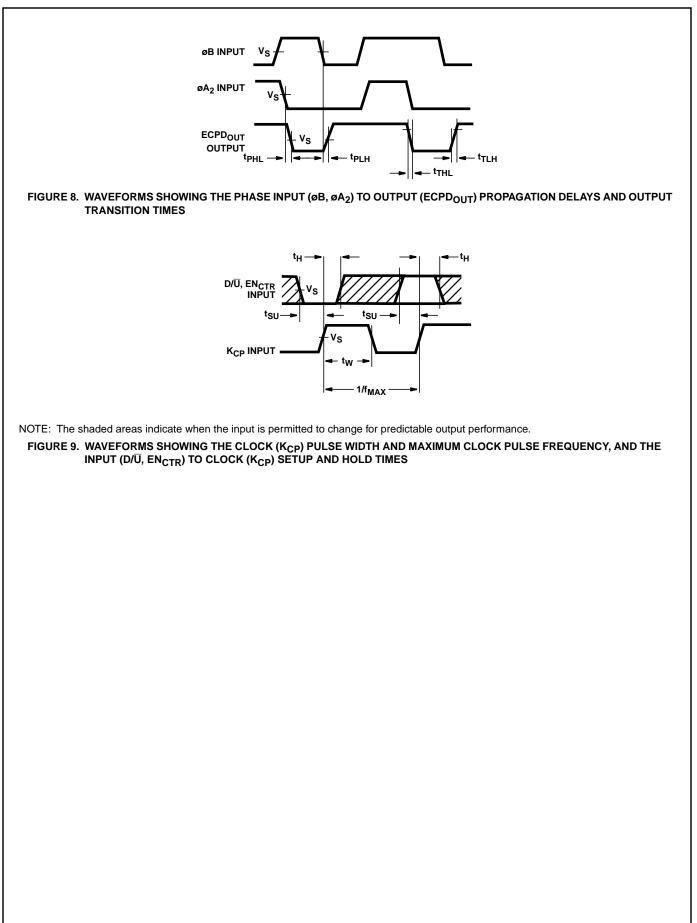

| Maximum Clock Frequency                                  | f <sub>MAX</sub> | 2                   | 6   | -              | 5       | -                    | 4       | -                    | MHz   |

| К <sub>СР</sub>                                          |                  | 4.5                 | 30  | -              | 24      | -                    | 20      | -                    | MHz   |

|                                                          |                  | 6                   | 35  | -              | 28      | -                    | 24      | -                    | MHz   |

| Maximum Clock Frequency                                  | f <sub>MAX</sub> | 2                   | 4   | -              | 3       | -                    | 2       | -                    | MHz   |

| I/D <sub>CP</sub>                                        |                  | 4.5                 | 20  | -              | 16      | -                    | 13      | -                    | MHz   |

|                                                          |                  | 6                   | 24  | -              | 19      | -                    | 15      | -                    | MHz   |

| Clock Pulse Width                                        | tw               | 2                   | 80  | -              | 100     | -                    | 120     | -                    | ns    |

| К <sub>СР</sub>                                          |                  | 4.5                 | 16  | -              | 20      | -                    | 24      | -                    | ns    |

|                                                          |                  | 6                   | 14  | -              | 17      | -                    | 20      | -                    | ns    |

| Clock Pulse Width                                        | t <sub>W</sub>   | 2                   | 125 | -              | 155     | -                    | 190     | -                    | ns    |

| I/D <sub>CP</sub>                                        |                  | 4.5                 | 25  | -              | 31      | -                    | 38      | -                    | ns    |

|                                                          |                  | 6                   | 21  | -              | 26      | -                    | 32      | -                    | ns    |

| Set-up Time<br>D/Ū, EN <sub>CTR</sub> to K <sub>CP</sub> | ts∪              | 2                   | 100 | -              | 125     | -                    | 150     | -                    | ns    |

|                                                          |                  | 4.5                 | 20  | -              | 25      | -                    | 30      | -                    | ns    |

|                                                          |                  | 6                   | 17  | -              | 21      | -                    | 26      | -                    | ns    |

| Hold Time                                                | t <sub>H</sub>   | 2                   | 0   | -              | 0       | -                    | 0       | -                    | ns    |

| $D/\overline{U}$ , EN <sub>CTR</sub> to K <sub>CP</sub>  |                  | 4.5                 | 0   | -              | 0       | -                    | 0       | -                    | ns    |

|                                                          |                  | 6                   | 0   | -              | 0       | -                    | 0       | -                    | ns    |

| HCT TYPES                                                | -                |                     |     |                |         |                      |         |                      | 1     |

| Maximum Clock Frequency<br>K <sub>CP</sub>               | f <sub>MAX</sub> | 4.5                 | 30  | -              | 24      | -                    | 20      | -                    | MHz   |

| Maximum Clock Frequency<br>I/D <sub>CP</sub>             | f <sub>MAX</sub> | 4.5                 | 20  | -              | 16      | -                    | 13      | -                    | MHz   |

| Clock Pulse Width<br>K <sub>CP</sub>                     | tw               | 4.5                 | 16  | -              | 20      | -                    | 24      | -                    | ns    |

| Clock Pulse Width<br>I/D <sub>CP</sub>                   | tw               | 4.5                 | 25  | -              | 31      | -                    | 38      | -                    | ns    |

| Set-up Time<br>D/Ū, EN <sub>CTR</sub> to K <sub>CP</sub> | t <sub>SU</sub>  | 4.5                 | 20  | -              | 25      | -                    | 30      | -                    | ns    |

| Hold Time<br>D/Ū, EN <sub>CTR</sub> to K <sub>CP</sub>   | t <sub>H</sub>   | 4.5                 | 0   | -              | 0       | -                    | 0       | -                    | ns    |

### Switching Specifications Input $t_r$ , $t_f = 6ns$

|                                                                                    |                                     | TEST                  |                     | 25  | °C      | -40°C TO 85°C | -55°C TO 125°C |       |

|------------------------------------------------------------------------------------|-------------------------------------|-----------------------|---------------------|-----|---------|---------------|----------------|-------|

| PARAMETER                                                                          | SYMBOL                              | CONDITIONS            | V <sub>CC</sub> (V) | ТҮР | MAX MAX |               | MAX            | UNITS |

| HC TYPES                                                                           |                                     |                       |                     |     |         |               |                |       |

| Propagation Delay, t <sub>PLH</sub> , t<br>I/D <sub>CP</sub> to I/D <sub>OUT</sub> | t <sub>PLH</sub> , t <sub>PHL</sub> | C <sub>L</sub> = 50pF | 2                   | -   | 175     | 220           | 265            | ns    |

|                                                                                    |                                     |                       | 4.5                 | -   | 35      | 44            | 53             | ns    |

|                                                                                    |                                     |                       | 6                   | -   | 30      | 34            | 43             | ns    |

|                                                                    |                                     | TEST                  | V <sub>CC</sub> (V) | 25 <sup>0</sup> C |     | -40°C TO 85°C | -55°C TO 125°C |       |

|--------------------------------------------------------------------|-------------------------------------|-----------------------|---------------------|-------------------|-----|---------------|----------------|-------|

| PARAMETER                                                          | SYMBOL                              | CONDITIONS            |                     | TYP               | MAX | МАХ           | MAX            | UNITS |

| Propagation Delay,<br>$\phi A_1, \phi B$ to XORPD <sub>OUT</sub>   | t <sub>PLH</sub> , t <sub>PHL</sub> | C <sub>L</sub> = 50pF | 2                   | -                 | 150 | 190           | 225            | ns    |

|                                                                    |                                     |                       | 4.5                 | -                 | 30  | 38            | 45             | ns    |

|                                                                    |                                     |                       | 6                   | -                 | 26  | 33            | 38             | ns    |

| Propagation Delay, $\phi B$ , $\phi A_2$ to ECPD <sub>OUT</sub>    | t <sub>PHL</sub> , t <sub>PHL</sub> | C <sub>L</sub> = 50pF | 2                   | -                 | 200 | 250           | 300            | ns    |

|                                                                    |                                     |                       | 4.5                 | -                 | 40  | 50            | 60             | ns    |

|                                                                    |                                     |                       | 6                   | -                 | 34  | 43            | 51             | ns    |

| Output Transition Time                                             | t <sub>TLH</sub>                    | C <sub>L</sub> = 50pF | 2                   | -                 | 75  | 95            | 110            | ns    |

| XORPD <sub>OUT</sub><br>ECPD <sub>OUT</sub>                        |                                     |                       | 4.5                 | -                 | 15  | 19            | 22             | ns    |

|                                                                    |                                     |                       | 6                   | -                 | 13  | 16            | 19             | ns    |

| Output Transition Time<br>I/D <sub>OUT</sub>                       | t <sub>TLH</sub>                    | C <sub>L</sub> = 50pF | 2                   | -                 | 60  | 75            | 90             | ns    |

|                                                                    |                                     |                       | 4.5                 | -                 | 12  | 15            | 18             | ns    |

|                                                                    |                                     |                       | 6                   | -                 | 10  | 13            | 15             | ns    |

| Input Capacitance                                                  | Cl                                  | -                     | -                   | -                 | 10  | 10            | 10             | pF    |

| HCT TYPES                                                          |                                     |                       |                     |                   |     |               |                |       |

| Propagation Delay,<br>I/D <sub>CP</sub> to I/D <sub>OUT</sub>      | <sup>t</sup> PLH <sup>, t</sup> PHL | C <sub>L</sub> = 50pF | 4.5                 | -                 | 35  | 44            | 53             | ns    |

| Propagation Delay,<br>φA <sub>1</sub> , φB to XORPD <sub>OUT</sub> | t <sub>PLH</sub> , t <sub>PHL</sub> | C <sub>L</sub> = 50pF | 4.5                 | -                 | 30  | 38            | 45             | ns    |

| Propagation Delay,<br>$\phi B$ , $\phi A_2$ to ECPD <sub>OUT</sub> | t <sub>PHL</sub> , t <sub>PHL</sub> | C <sub>L</sub> = 50pF | 4.5                 | -                 | 40  | 50            | 60             | ns    |

| Output Transition Time<br>XORPD <sub>OUT</sub>                     | t <sub>TLH</sub>                    | C <sub>L</sub> = 50pF | 4.5                 | -                 | 15  | 19            | 22             | ns    |

| Output Transition Time<br>ECPD <sub>OUT</sub>                      | t <sub>TLH</sub>                    | C <sub>L</sub> = 50pF | 4.5                 | -                 | 12  | 15            | 18             | ns    |

| Input Capacitance                                                  | Cl                                  | -                     | -                   | -                 | 10  | 10            | 10             | pF    |

### Switching Specifications Input t<sub>r</sub>, t<sub>f</sub> = 6ns (Continued)

FIGURE 1. DPLL USING BOTH PHASE DETECTORS IN A RIPPLE-CANCELLATION SCHEME

FIGURE 2. DPLL USING EXCLUSIVE-OR PHASE DETECTION

FIGURE 3. TIMING DIAGRAM: I/DOUT IN-LOCK CONDITION

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                    |              |                |         |

| 5962-8999001EA   | ACTIVE | CDIP         | J       | 16   | 1       | Non-RoHS     | SNPB          | N / A for Pkg Type | -55 to 125   | 5962-8999001EA | Samples |

|                  |        |              |         |      |         | & Green      |               |                    |              | CD54HC297F3A   | Samples |

| CD54HC297F3A     | ACTIVE | CDIP         | J       | 16   | 1       | Non-RoHS     | SNPB          | N / A for Pkg Type | -55 to 125   | 5962-8999001EA | Samples |

|                  |        |              |         |      |         | & Green      |               |                    |              | CD54HC297F3A   | Bampies |

| CD74HC297E       | ACTIVE | PDIP         | Ν       | 16   | 25      | RoHS & Green | NIPDAU        | N / A for Pkg Type | -55 to 125   | CD74HC297E     | Samples |

|                  |        |              |         |      |         |              |               |                    |              |                | Samples |

| CD74HCT297E      | ACTIVE | PDIP         | Ν       | 16   | 25      | RoHS & Green | NIPDAU        | N / A for Pkg Type | -55 to 125   | CD74HCT297E    | Samples |

|                  |        |              |         |      |         |              |               |                    |              |                | Bumpies |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

www.ti.com

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

OTHER QUALIFIED VERSIONS OF CD54HC297, CD74HC297 :

• Catalog : CD74HC297

• Military : CD54HC297

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Military QML certified for Military and Defense Applications

### TEXAS INSTRUMENTS

www.ti.com

9-Aug-2022

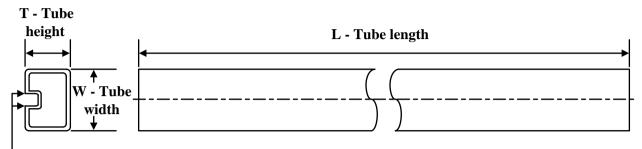

### TUBE

### - B - Alignment groove width

#### \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| CD74HC297E  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| CD74HC297E  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| CD74HCT297E | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| CD74HCT297E | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

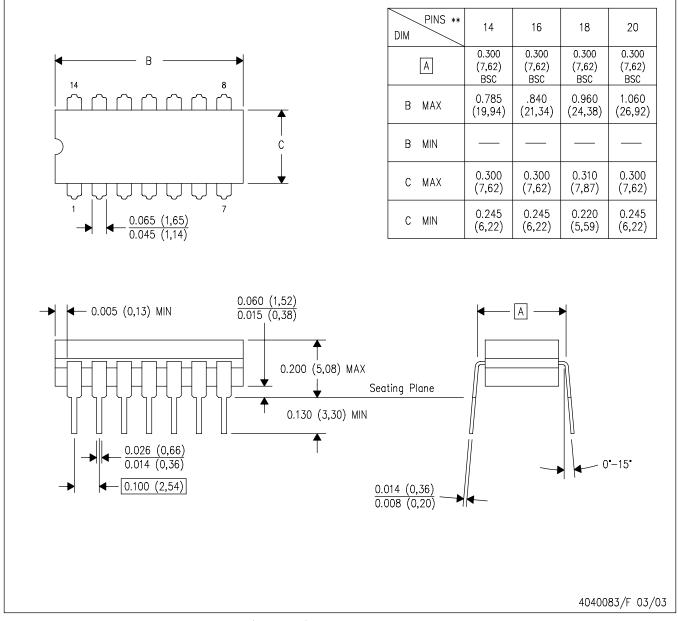

J (R-GDIP-T\*\*) 14 LEADS SHOWN

CERAMIC DUAL IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

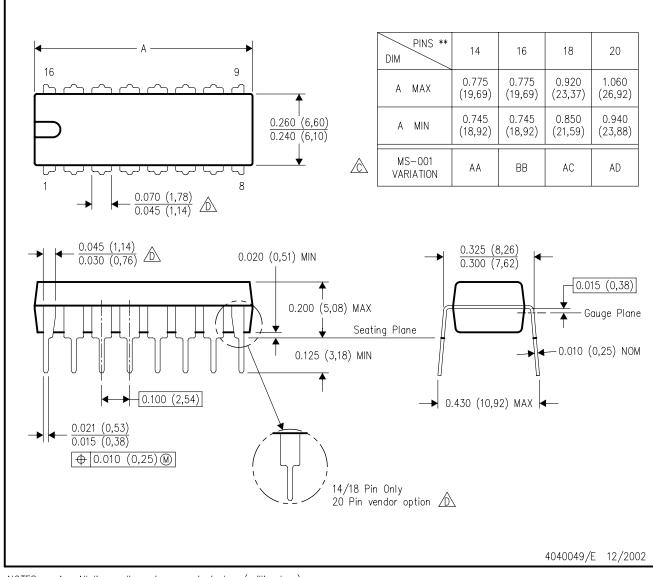

### N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\triangle$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated