### **General Description**

The AOZ2023 is a 3A ultra low dropout linear regulator designed for desktop motherboard, graphic card and notebook applications. This device needs dual supplies, a control voltage for the control circuitry and an input voltage for power conversion. The AOZ2023 delivers high-current and ultra low-drop output voltage for applications where  $V_{OUT}$  is very close to  $V_{IN}$ .

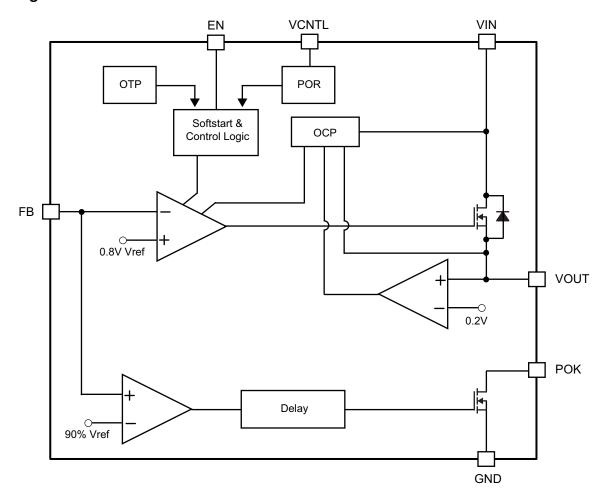

The AOZ2023 features comprehensive control and protection functions: a power on reset (POR) circuit for monitoring both control and power inputs for proper operation; an EN input for enabling or disabling the device, a power OK with time delay for indicating the output voltage status, a current limit function, and a thermal shutdown function.

The AOZ2023 is available in exposed pad SO-8 package.

#### **Features**

- Ultra low dropout linear regulator

- 1.3V~5.5V V<sub>IN</sub> supply voltage with external control voltage

- Dropout voltage (typical):

- 180mV @ 2A

- High accuracy output voltage ±1.5%

- Enable and Power Good

- V<sub>OUT</sub> pull low resistance when disabled

- Current limiting protection

- Thermal shutdown protection

- Output voltage adjustable

- Small footprint exposed pad SO-8 Package

### **Applications**

- Desktop, notebook PCs

- Workstations

- Graphic cards

- Low voltage logic supplies

- Gaming

- SMPS post regulators

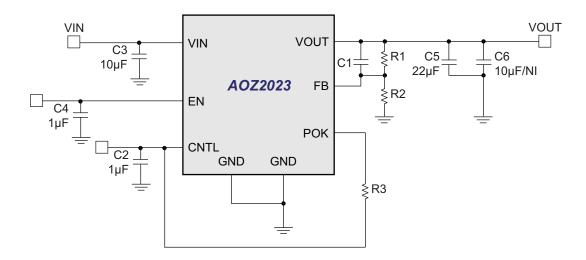

### **Typical Application**

# **Ordering Information**

| Part Number | Part Number Ambient Temperature Range |           | Environmental |  |  |

|-------------|---------------------------------------|-----------|---------------|--|--|

| AOZ2023PI   | -40 °C to +85 °C                      | EPAD SO-8 | Green Product |  |  |

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant. Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

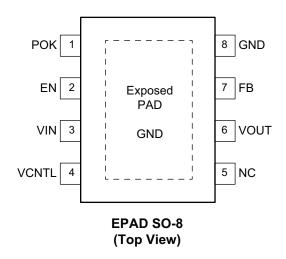

# **Pin Configuration**

# **Pin Description**

| Pin Number  | Pin Name                                                                                                                              | Pin Function                                                                                                                                                                                                                                                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | POK                                                                                                                                   | Power OK Indication. This pin is an open-drain output and is set high impedance once VOUT reaches 90% of its rating voltage.                                                                                                                                                                                                                |

| 2           | EN                                                                                                                                    | Enable Input. Pulling this pin below 0.8V turns the regulator off, reducing the quiescent current to a fraction of its operating value.                                                                                                                                                                                                     |

| 3           | VIN                                                                                                                                   | Input Voltage. This is the drain input to the power device that supply current to the output pin. Large bulk capacitors with low ESR should be placed physically close to this pin o prevent the input rail from dropping during large load transient. A 10µF ceramic capacitor is recommended at this pin.                                 |

| 4           | VCNTL                                                                                                                                 | Supply Input for Control Circuit. This pin provides bias voltage to the control circuitry and driver for the pass transistor. The driving capability of output current is proportioned to the VCNTL. For the device to regulate, the voltage on this pin must be at least 1.5V greater than the output voltage, and no less than VCNTL_min. |

| 5           | NC                                                                                                                                    | Not Internally Connected.                                                                                                                                                                                                                                                                                                                   |

| 6           | VOUT                                                                                                                                  | Output Voltage. This pin is power output of the device. A pull low resistance exists when the device is disabled by pulling low the EN pin.                                                                                                                                                                                                 |

| 7           | 7 FB Feedback Voltage. This pin is the inverting input to the error a from the output to GND is used to set the regulation voltage as |                                                                                                                                                                                                                                                                                                                                             |

| 8           | GND                                                                                                                                   | Ground.                                                                                                                                                                                                                                                                                                                                     |

| Exposed PAD | GND                                                                                                                                   | Ground. The exposed pad acts the dominant power dissipation path and should be soldered to well design PCB pads.                                                                                                                                                                                                                            |

Rev. 1.0 August 2015 **www.aosmd.com** Page 2 of 11

# **Block Diagram**

# **Absolute Maximum Ratings**

Exceeding the Absolute Maximum Ratings may damage the device.

| Parameter                 | Rating      |

|---------------------------|-------------|

| VIN                       | 1V to 6V    |

| VCNTL                     | 3V to 6V    |

| VOUT                      | 0.8V to 6V  |

| Other Pins                | -0.3V to 6V |

| ESD Rating <sup>(1)</sup> | 2kV         |

#### Note:

1. Devices are inherently ESD sensitive, handling precautions are required. Human body model rating: 1.5k $\Omega$  in series with 100pF.

# **Recommended Operating Conditions**

The device is not guaranteed to operate beyond the Recommended Operating Conditions.

| Parameter                                            | Rating          |

|------------------------------------------------------|-----------------|

| Supply Voltage (V <sub>IN</sub> )                    | 1.3V to 5.5V    |

| Supply Control Voltage (V <sub>CNTL</sub> )          | 3V to 5.5V      |

| Junction Temperature (T <sub>J</sub> )               | -40°C to +125°C |

| Ambient Temperature (T <sub>A</sub> )                | -40°C to +85°C  |

| Power Dissipation (P <sub>D</sub> )                  | 2W              |

| Package Thermal Resistance EPAD SO-8 $(\Theta_{JA})$ | 50°C/W          |

### **Electrical Characteristics**

$T_A$  = 25 °C,  $V_{IN}$  = 1.4V,  $V_{CNTL}$  =  $V_{EN}$  = 5V,  $C_{IN}$  =  $C_{OUT}$  =  $10\mu F$ , unless otherwise specified. Specifications in **BOLD** indicate a temperature of -40°C to +85°C.

| Symbol                           | Parameter                          | Conditions                                                                                     | Min.      | Тур.  | Max.  | Units  |

|----------------------------------|------------------------------------|------------------------------------------------------------------------------------------------|-----------|-------|-------|--------|

| INPUT STAC                       | SE .                               |                                                                                                |           |       |       |        |

| V <sub>IN</sub>                  | Input Voltage Range                | V <sub>OUT</sub> = 1.2V, I <sub>OUT</sub> = 100mA                                              | 1.3       |       | 5.5   | V      |

| V <sub>CNTL</sub>                | Input Control Voltage              |                                                                                                | 3         |       | 5.5   | V      |

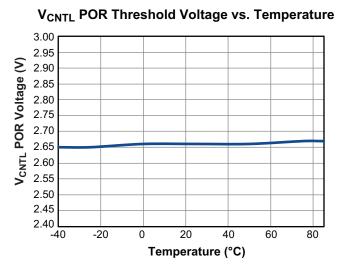

| V <sub>POR</sub>                 | POR                                |                                                                                                | 2.4       | 2.7   | 3     | V      |

| V <sub>UVLO_HYS</sub>            | Under-Voltage Lockout Hysteresis   |                                                                                                |           | 300   |       | mV     |

|                                  | Lancet Council of Council          | EN = IN, V <sub>OUT</sub> = V <sub>FB</sub> , no load                                          |           | 0.5   | 1     | mA     |

| I <sub>CNTL</sub>                | Input Supply Current               | EN = AGND                                                                                      |           |       | 20    | μΑ     |

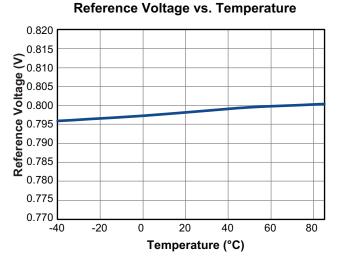

| $V_{FB}$                         | Feedback Reference Voltage         | T <sub>A</sub> = 25 °C, no load                                                                | 0.788     | 0.800 | 0.812 | V      |

| I <sub>FB</sub>                  | Feedback Bias Current              |                                                                                                |           | 0.02  |       | μΑ     |

| REGULATIO                        | N                                  |                                                                                                |           |       | •     |        |

| A\/                              | Line Regulation (V <sub>IN</sub> ) | V <sub>IN</sub> = 1.4V to 5V, I <sub>OUT</sub> = 100mA,<br>V <sub>OUT</sub> = 1.2V             |           | 0.015 | 0.15  | % / ΔV |

| $\Delta V_{FB}$                  | Load Regulation                    | V <sub>IN</sub> = 1.8V, I <sub>OUT</sub> = 100mA to 2A,<br>V <sub>OUT</sub> = 1.2V             |           | 0.45  | 1.5   | %      |

| V (2)                            | Dron Veltone                       | I <sub>OUT</sub> = 300mA, V <sub>EN</sub> = V <sub>CNTL</sub> = 5V,<br>V <sub>OUT</sub> = 1.2V | , 40 50 m | mV    |       |        |

| V <sub>DROP</sub> <sup>(2)</sup> | Drop Voltage                       |                                                                                                | 180       | 250   | mV    |        |

| R <sub>PULL-DOWN</sub>           | V <sub>OUT</sub> Pull-down         |                                                                                                |           | 90    |       | Ω      |

| ENABLE / P                       | OK .                               | •                                                                                              | •         | •     |       |        |

| V <sub>EN_HI</sub>               | Enable High Level                  |                                                                                                | 1.2       |       |       | V      |

| V <sub>EN_LOW</sub>              | Disable Low Level                  |                                                                                                |           |       | 0.2   | V      |

| I <sub>EN</sub>                  | Enable Bias Current                | V <sub>EN</sub> = 5.5V                                                                         |           | 12    |       | μΑ     |

| V <sub>POK_TH</sub>              | POK Threshold                      | $V_{IN} = V_{EN} = V_{CNTL} = 5V$ , No load,<br>$V_{OUT} = 1.2V$                               |           | 90    |       | %      |

| V <sub>POK_HYS</sub>             | POK Hysteresis                     | $V_{IN} = V_{EN} = V_{CNTL} = 5V$ , No load,<br>$V_{OUT} = 1.2V$                               |           | 10    |       | %      |

| T <sub>POK_ON</sub>              | POK Time Delay (ON)                | $V_{IN} = V_{EN} = V_{CNTL} = 5V$ , No load,<br>$V_{FB} > 90\% V_{REF}$                        |           | 1     |       | ms     |

| T <sub>POK_OFF</sub>             | POK Time Delay (OFF)               | $V_{IN} = V_{EN} = V_{CNTL} = 5V$ , No load,<br>$V_{FB} < 10\%^*V_{REF}$                       |           | 50    |       | μs     |

| V <sub>POK_LOW</sub>             | POK Pull-low Voltage               | POK sink current = 5mA                                                                         |           |       | 0.35  | V      |

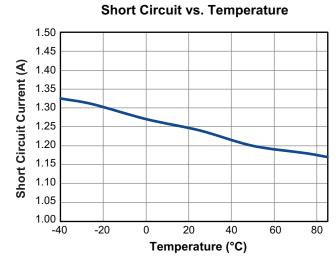

| PROTECTIO                        | N                                  |                                                                                                |           |       |       |        |

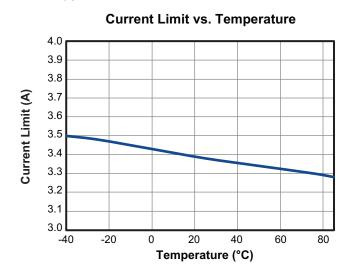

| I <sub>LIM</sub> <sup>(3)</sup>  | Current Limit                      |                                                                                                |           | 3.5   |       | Α      |

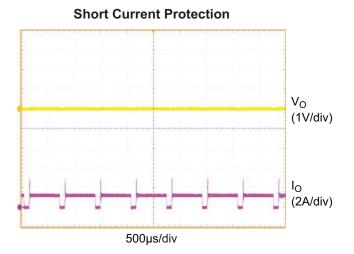

| I <sub>SC</sub>                  | Short Circuit Current              | V <sub>OUT</sub> < 0.2V                                                                        |           | 0.8   |       | Α      |

| T <sub>SD</sub>                  | Thermal Shutdown Threshold         |                                                                                                |           | 160   |       | °C     |

| ΔT <sub>SD</sub>                 | Thermal Shutdown Hysteresis        |                                                                                                |           | 60    |       | °C     |

#### Notes:

Rev. 1.0 August 2015 **www.aosmd.com** Page 4 of 11

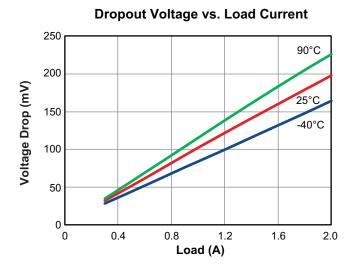

<sup>2.</sup> The dropout voltage is defined as  $V_{\text{IN}}$  -  $V_{\text{OUT}}$ , which is measured when  $V_{\text{OUT}}$  is  $V_{\text{OUT}}$  - 100mV.

<sup>3.</sup> The current limit was measured by the constant current limit value when VOUT is shorted directly. It is noted that the output capacitor current was not included.

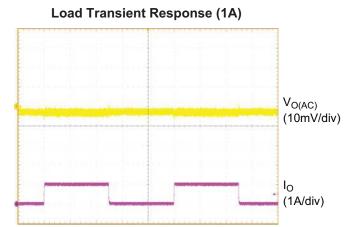

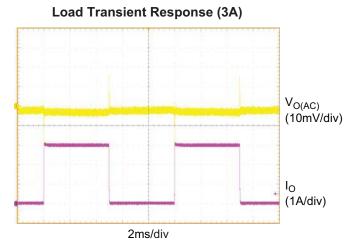

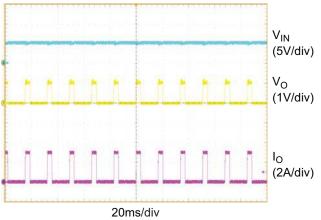

### **Functional Characteristics**

Circuit of Typical Application 1.  $T_A$  = 25°C,  $V_{IN}$  = 1.5V,  $V_{CNTL}$  = 5V,  $V_{OUT}$  = 1.05V, unless otherwise specified.

2ms/div

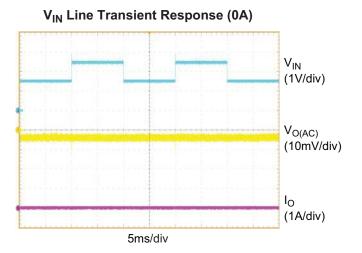

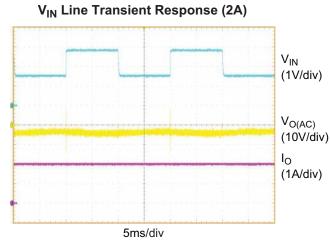

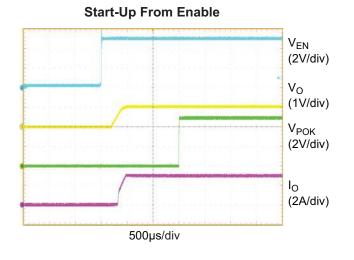

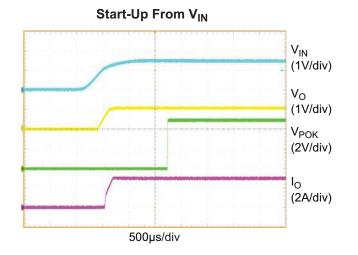

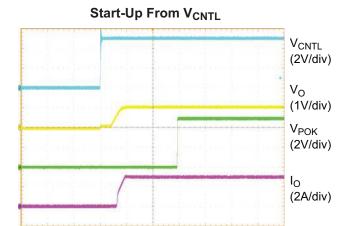

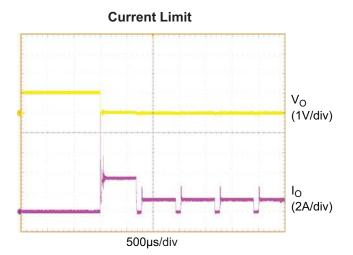

## **Functional Characteristics** (Continued)

Circuit of Typical Application 1.  $T_A$  = 25°C,  $V_{IN}$  = 1.5V,  $V_{CNTL}$  = 5V,  $V_{OUT}$  = 1.05V, unless otherwise specified.

500µs/div

Rev. 1.0 August 2015 **www.aosmd.com** Page 6 of 11

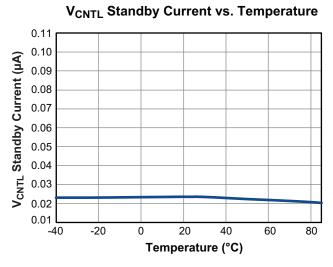

# **Typical Performance Characteristics**

Circuit of Typical Application 1.  $T_A$  = 25°C,  $V_{IN}$  = 1.5V,  $V_{CNTL}$  = 5V,  $V_{OUT}$  = 1.05V, unless otherwise specified.

### **Application Information**

#### **Output Voltage Setting**

The output voltage can be set by the output voltage divider. Typically, the adjustable range of the output voltage is from 1V to  $(V_{IN} - V_{drop})$ . The output voltage is set by the equation below:

$$V_{OUT} = 0.8 V \times \frac{R1 + R2}{R2}$$

### Supply Voltage (VCNTL)

Supply voltage is used to provide the power for the internal circuits. For the device to regulate, the voltage on this pin must be at least 1.5V greater than the output voltage, and no less than  $V_{CNTL\_min}$ . A  $0.1\mu F$  or more ceramic capacitor close to the pin is required to filter the control voltage.

#### **Enable (EN)**

The EN pin is used to turn off the regulator by pulling this pin below 0.8V. When the linear regulator is operated in the disable mode, the quiescent current can be limited below several ten micro-amp level.

### **Input / Output Capacitor**

A 10 $\mu$ F or more capacitances for the input side (VIN) is necessary. This not only decouples the noise from input side, but also keeps the input impedance as low as possible. In addition, a 22 $\mu$ F or more capacitances for the VIN above 4.5V is recommended for much lower input impedance.

A  $10\mu\text{F}$  output capacitor is typically used with a  $0.1\mu\text{F}$  ceramic capacitor for the output terminal (VOUT). Internal type-II compensation network allows lower ESR capacitors without stability problem.

#### Power OK (POK)

The POK pin is used to provide a logic signal to notice that the regulator works well. When the output voltage through the voltage divider is regulated above 90% of reference voltage, this pin will be as a high impedance status due to the open-drain output. An external pull-up resister is necessary to provide high-level signal. The sink capability of the POK pin is limited below 5mA. Typically, a  $5.1k\Omega$  resister for the 5V is recommended.

#### **Over Temperature Protection (OTP)**

It is recommended that the junction temperature can be kept below the recommended operation condition 125 degree for maximum reliability. This power dissipation is conducted through the package into the ambient environment, and, in the process, the temperature of the die  $(T_i)$  rises above ambient.

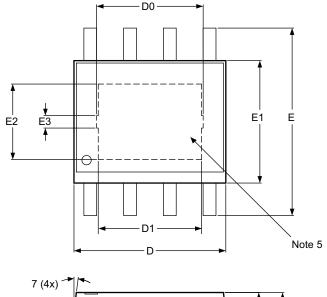

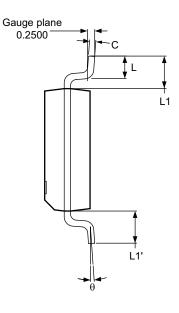

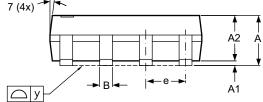

## Package Dimensions, SO-8 EP1

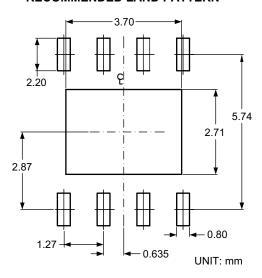

### **RECOMMENDED LAND PATTERN**

### **Dimensions in millimeters**

| Symbols | Min.     | Max.     |      |  |  |

|---------|----------|----------|------|--|--|

| Α       | 1.40     | 1.55     | 1.70 |  |  |

| A1      | 0.00     | 0.05     | 0.10 |  |  |

| A2      | 1.40     | 1.50     | 1.60 |  |  |

| В       | 0.31     | 0.406    | 0.51 |  |  |

| С       | 0.17     | _        | 0.25 |  |  |

| D       | 4.80     | 4.96     | 5.00 |  |  |

| D0      | 3.20     | 3.40     | 3.60 |  |  |

| D1      | 3.10     | 3.30     | 3.50 |  |  |

| Е       | 5.80     | 6.00     | 6.20 |  |  |

| е       | _        | 1.27     | _    |  |  |

| E1      | 3.80     | 3.90     | 4.00 |  |  |

| E2      | 2.21     | 2.41     | 2.61 |  |  |

| E3      | (        | 0.40 REF | =    |  |  |

| L       | 0.40     | 1.27     |      |  |  |

| У       | _        | _        | 0.10 |  |  |

| θ       | 0°       | 3°       | 8°   |  |  |

| L1–L1'  | _        | 0.04     | 0.12 |  |  |

| L1      | 1.04 REF |          |      |  |  |

### **Dimensions in inches**

| Symbols | Min.         | Nom.    | Max.  |  |  |  |

|---------|--------------|---------|-------|--|--|--|

| Α       | 0.055        | 0.061   | 0.067 |  |  |  |

| A1      | 0.000        | 0.002   | 0.004 |  |  |  |

| A2      | 0.055        | 0.059   | 0.063 |  |  |  |

| В       | 0.012        | 0.016   | 0.020 |  |  |  |

| С       | 0.007        | _       | 0.010 |  |  |  |

| D       | 0.189        | 0.195   | 0.197 |  |  |  |

| D0      | 0.126        | 0.134   | 0.142 |  |  |  |

| D1      | 0.122        | 0.130   | 0.138 |  |  |  |

| Е       | 0.228        | 0.236   | 0.244 |  |  |  |

| е       | _            | 0.050   | _     |  |  |  |

| E1      | 0.150        | 0.153   | 0.157 |  |  |  |

| E2      | 0.087        | 0.095   | 0.103 |  |  |  |

| E3      | 0            | .016 RE | F     |  |  |  |

| L       | 0.016        | 0.050   |       |  |  |  |

| у       | _            | _       | 0.004 |  |  |  |

| θ       | 0°           | 3°      | 8°    |  |  |  |

| L1–L1'  | — 0.002 0.00 |         |       |  |  |  |

| L1      | 0.041 REF    |         |       |  |  |  |

### Notes:

- 1. Package body sizes exclude mold flash and gate burrs.

- 2. Dimension L is measured in gauge plane.

- 3. Tolerance 0.10mm unless otherwise specified.

- 4. Controlling dimension is millimeter, converted inch dimensions are not necessarily exact.

- 5. Die pad exposure size is according to lead frame design.

- 6. Followed from JEDEC MS-012

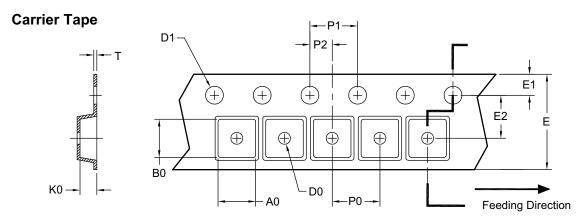

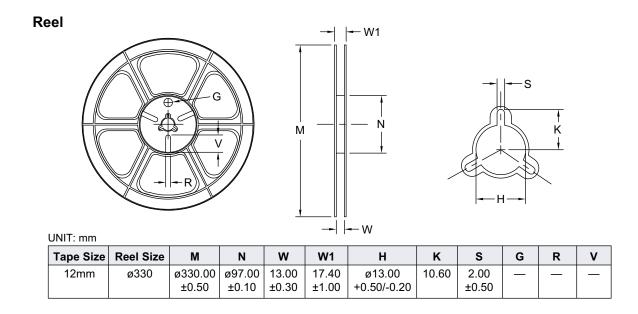

# Tape and Reel Dimensions, SO-8 EP1

UNIT: mm

| Package | A0    | В0    | K0    | D0    | D1    | Е     | E1    | E2    | P0    | P1    | P2    | Т     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| SO-8    | 6.40  | 5.20  | 2.10  | 1.60  | 1.50  | 12.00 | 1.75  | 5.50  | 8.00  | 4.00  | 2.00  | 0.25  |

| (12mm)  | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 |

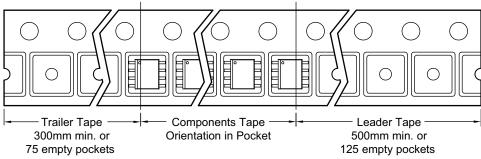

# Leader/Trailer and Orientation

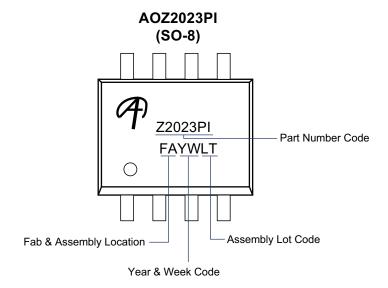

### Part Marking

#### **LEGAL DISCLAIMER**

Alpha and Omega Semiconductor makes no representations or warranties with respect to the accuracy or completeness of the information provided herein and takes no liabilities for the consequences of use of such information or any product described herein. Alpha and Omega Semiconductor reserves the right to make changes to such information at any time without further notice. This document does not constitute the grant of any intellectual property rights or representation of non-infringement of any third party's intellectual property rights.

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rev. 1.0 August 2015 **www.aosmd.com** Page 11 of 11