# DSLVDS1001-1002EVM User's Guide

#### **Contents**

| 1       | Introduction                                |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------|--|--|--|--|--|--|--|--|

|         | 1.1 Features                                |  |  |  |  |  |  |  |  |

|         | 1.2 Applications                            |  |  |  |  |  |  |  |  |

| 2       | Ordering Information                        |  |  |  |  |  |  |  |  |

| 3 Setup |                                             |  |  |  |  |  |  |  |  |

|         | 3.1 Hardware Description and Setup          |  |  |  |  |  |  |  |  |

|         | 3.2 DSLVDS1001-1002EVM Performance Plots    |  |  |  |  |  |  |  |  |

| 4       | Board Layout                                |  |  |  |  |  |  |  |  |

| 5       | Schematic                                   |  |  |  |  |  |  |  |  |

| 6       | Bill of Materials                           |  |  |  |  |  |  |  |  |

|         | List of Figures                             |  |  |  |  |  |  |  |  |

| 1       | DSLVDS1001-1002EVM Input and Output Diagram |  |  |  |  |  |  |  |  |

| =       |                                             |  |  |  |  |  |  |  |  |

| 2       | DSLVDS1001-1002EVM Setup Configuration      |  |  |  |  |  |  |  |  |

| 3       | DSLVDS1001 3.3 V LVCMOS Input               |  |  |  |  |  |  |  |  |

| 4       | DSLVDS1002 LVCMOS Output                    |  |  |  |  |  |  |  |  |

| 5       | DSLVDS1001-1002EVM Top Layer                |  |  |  |  |  |  |  |  |

| 6       | DSLVDS1001-1002EVM Bottom Layer             |  |  |  |  |  |  |  |  |

|         | List of Tables                              |  |  |  |  |  |  |  |  |

| 1       | Description of Jumper Settings              |  |  |  |  |  |  |  |  |

| 2       | Bill of Materials                           |  |  |  |  |  |  |  |  |

#### **Trademarks**

All trademarks are the property of their respective owners.

#### 1 Introduction

The DSLVDS1001-1002EVM is an evaluation module designed for performance and functional evaluation of the Texas Instruments DSLVDS1001 3.3-V LVDS Single High Speed Differential Line Driver and DSLVDS1002 3.3-V LVDS Single High Speed Differential Line Receiver. With this kit, users can quickly evaluate the output waveform characteristics and signal integrity supported by the DSLVDS1001 and DSLVDS1002. Header pins allow access to the DSLVDS1001 and DSLVDS1002 inputs and outputs and also facilitate connection to lab equipment or user systems for performance evaluation.

Introduction www.ti.com

www.ti.com Introduction

## 1.1 Features

#### DSLVDS1001:

- · Conforms to TIA/EIA-644-A Standard

- Up to 400-Mbps (200-MHz) Switching Rates

- 700-ps (100-ps Typical) Maximum Differential Skew

- 1.5-ns Maximum Propagation Delay

- Single 3.3-V Power Supply

## DSLVDS1002:

- · Compatible with ANSI TIA/EIA-644-A Standard

- Up to 400-Mbps (200-MHz) switching rates

- 100-ps differential skew (typical)

- 3.5-ns maximum propagation delay

- Single 3.3-V Power Supply

# 1.2 Applications

- Board to Board Communication

- Wireless/Telecom Infrastructure

- Medical/Health

- · Multi-Function Printers

- · Factory Automation and Control

- EPOS/ECR/Cash Drawer

# 2 Ordering Information

| EVM ID             | Device ID              | Device Package |  |

|--------------------|------------------------|----------------|--|

| DSLVDS1001-1002EVM | DSLVDS1001, DSLVDS1002 | SOT-23         |  |

Setup www.ti.com

## 3 Setup

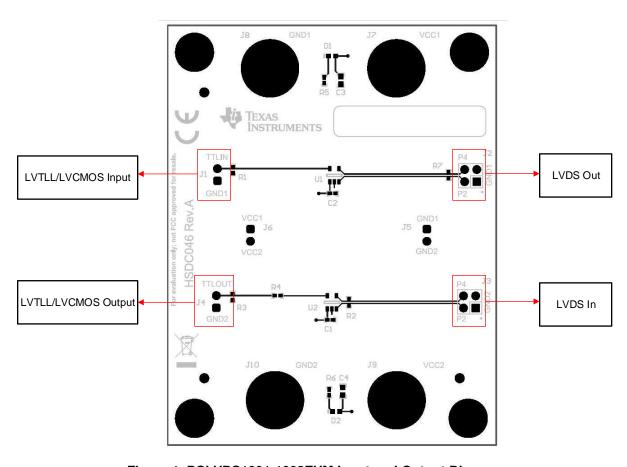

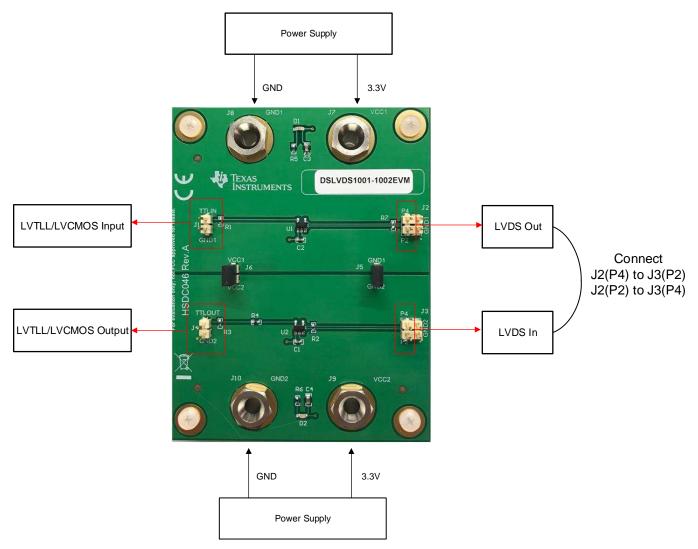

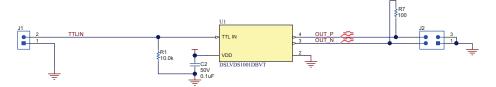

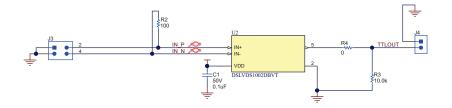

The DSLVDS1001 is a LVDS Single High Speed Differential Line Driver, and the DSLVDS1002 is a LVDS Single High Speed Differential Line Receiver. When operating the DSLVDS1001-1002EVM, jumper setting definitions can be referenced in Table 1, while signal input and output connection descriptions can be found in Figure 1. When using the DSLVDS1001 and DSLVDS1002 together, the typical configuration is to connect the DSLVDS1001 outputs (J2) such that they drive the inputs of the DSLVDS1002 (J3). The setup configuration is shown in Figure 2

| Component Name |                                           | Comments                          |  |  |

|----------------|-------------------------------------------|-----------------------------------|--|--|

| J5             |                                           | Shunt for GND1 and GND2           |  |  |

| J6             |                                           | Shunt for VCC1 and VCC2           |  |  |

| J7             | GND1                                      | GND for DSLVDS1001                |  |  |

| J8             | VCC1                                      | 3.3-V power supply for DSLVDS1001 |  |  |

| J9             | J9 VCC2 3.3-V power supply for DSLVDS1002 |                                   |  |  |

| J10            | GND2                                      | GND for DSLVDS1002                |  |  |

**Table 1. Description of Jumper Settings**

Figure 1. DSLVDS1001-1002EVM Input and Output Diagram

## 3.1 Hardware Description and Setup

#### 3.1.1 Termination Resistor

By factory default, the DSLVDS1001-1002EVM comes with populated termination resistors R2 on the DSLVDS1002 inputs and unpopulated termination resistors R7 on the DSLVDS1001 outputs.

www.ti.com Setup

In order to measure LVDS signals properly, a  $100-\Omega$  termination resistor must be present across each differential pair at the point of measurement. However, if multiple  $100-\Omega$  termination resistors are placed across a differential pair between the transmitter and receiver, the signal becomes double terminated. Double termination should be avoided, since this reduces the output amplitude and noise margin.

Populate R7 with  $100-\Omega$  termination resistors

- if the DSLVDS1001 output is measured by a high-impedance differential probe.

- if the DSLVDS1001 output interfaces with an external load that does not have an appropriate 100-Ω differential termination.

Remove R7 (or keep R7 unpopulated)

- if the DSLVDS1001 output interfaces with a DSLVDS1002 input by connecting J4 to J1.

- if the DSLVDS1001 output interfaces with an external load that has an appropriate 100-Ω differential termination.

## 3.1.2 Hardware Setup

DSLVDS1001-1002EVM can be powered using a single power supply or two separate power supplies.

When using a single power supply, J5 and J6 should be connected with jumpers. When using two separate power supplies, J5 and J6 should be left open.

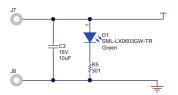

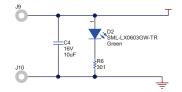

- 1. Connect a 3.3-V DC power supply (30 mA max) to the EVM. The LEDs D1 and D2 should turn on to specify that the board is powered.

- 2. Apply a high-speed 3.3-V LVTTL/LVCMOS signal to the DSLVDS1001 inputs on header J1.

- 3. The DSLVDS1001 LVDS output signals can be measured differentially on an oscilloscope by applying a Tektronix P6247 probe or equivalent differential probe at header J4 to measure the differential signal across the  $100-\Omega$  termination resistors R7, when R7 is populated. The expected output waveform is a  $\pm 350$ -mV LVDS signal.

- 4. Apply a high-speed ±350-mV (700-mV<sub>pp</sub> differential) LVDS signal to the DSLVDS1002 inputs on header J3. If desired, LVDS output from DSLVDS1001 can be connected to LVDS input of DSLVDS1002. If this is done, make sure R7 is not populated to avoid double-termination.

- 5. The DSLVDS1002 LVTTL/LVCMOS output signals can be measured on an oscilloscope by applying a Tektronix P6247 probe or equivalent differential probe at header J4.

Setup www.ti.com

Figure 2. DSLVDS1001-1002EVM Setup Configuration

www.ti.com Setup

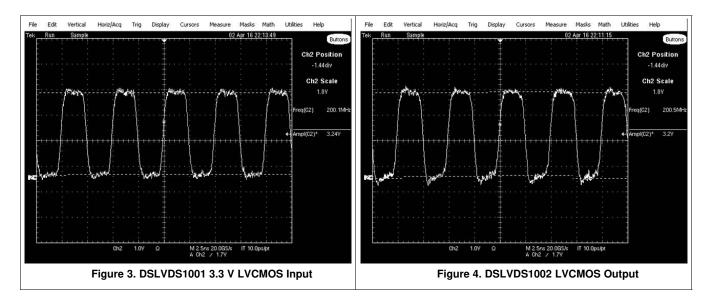

## 3.2 DSLVDS1001-1002EVM Performance Plots

The following plots show typical waveforms measured on the DSLVDS1001-1002EVM inputs and outputs using the hardware setup in Figure 2. For these measurements, the following parameters were used:

- Operating Frequency: 200 MHz (400 Mbps)

- DSLVDS1001 Input: 3.3 V LVCMOS square wave to J1

- DSLVDS1002 Input: LVDS signal to LVDS IN $\pm$  from DSLVDS1001 output LVDS OUT1 $\pm$ . 100- $\Omega$  termination resistor R7 not populated

- DSLVDS1002 Output: Measured at TTLOUT

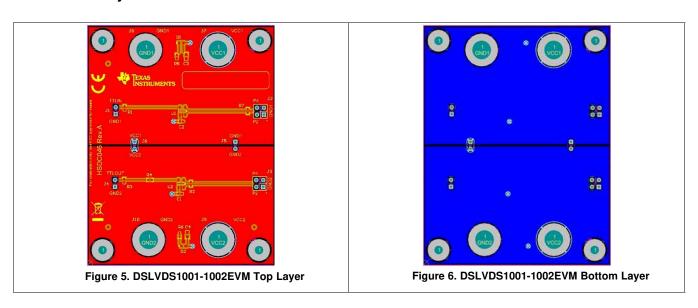

## 4 Board Layout

Schematic www.ti.com

# 5 Schematic

www.ti.com Bill of Materials

# 6 Bill of Materials

## **Table 2. Bill of Materials**

| Designator          | Quantity | Value      | Description                                                                   | Package<br>Reference           | Part Number             | Manufacturer           |

|---------------------|----------|------------|-------------------------------------------------------------------------------|--------------------------------|-------------------------|------------------------|

| PCB                 | 1        |            | Printed Circuit Board                                                         |                                | HSDC046                 | Any                    |

| C1, C2              | 2        | 0.1 μF     | CAP, CERM, 0.1 μF, 50 V, +/- 10%, X7R, 0402                                   | 0402                           | C1005X7R1H10<br>4K050BB | TDK                    |

| C3, C4              | 2        | 10 μF      | CAP, CERM, 10 μF, 16 V, +/- 20%, X5R, 0603                                    | 0603                           | EMK107BBJ106<br>MA-T    | Taiyo Yuden            |

| D1, D2              | 2        | Green      | LED, Green, SMD                                                               | LED, GREEN,<br>0603            | SML-<br>LX0603GW-TR     | Lumex                  |

| H1, H2, H3,<br>H4   | 4        |            | Machine Screw, Round, #4-40 x 1/4, Nylon, Philips panhead                     | Screw                          | NY PMS 440<br>0025 PH   | B&F Fastener<br>Supply |

| H5, H6, H7,<br>H8   | 4        |            | Standoff, Hex, 0.5"L #4-40 Nylon                                              | Standoff                       | 1902C                   | Keystone               |

| J1, J4, J5, J6      | 4        |            | Header, 100 mil, 2 x 1, Gold, TH                                              | 2 × 1 Header                   | TSW-102-07-G-<br>S      | Samtec                 |

| J2, J3              | 2        |            | Header, 100 mil, 2 × 2, Gold, TH                                              | 2 × 2 Header                   | TSW-102-07-G-<br>D      | Samtec                 |

| J7, J8, J9, J10     | 4        |            | Standard Banana Jack, Uninsulated                                             | Pomona_3267                    | 3267                    | Pomona<br>Electronics  |

| LBL1                | 1        |            |                                                                               | PCB Label 1.25<br>× 0.250 inch | THT-13-457-10           | Brady                  |

| R1, R3              | 2        | 10.0<br>kΩ | RES, 10.0 kΩ, 1%, 0.063 W, 0402                                               | 0402                           | RC0402FR-<br>0710KL     | Yageo America          |

| R2                  | 1        | 100 Ω      | RES, 100 Ω, 1%, 0.063 W, 0402                                                 | 0402                           | RC0402FR-<br>07100RL    | Yageo America          |

| R4                  | 1        | 0 Ω        | RES, 0 Ω, 5%, 0.1 W, AEC-Q200<br>Grade 0, 0402                                | 0402                           | ERJ-2GE0R00X            | Panasonic              |

| R5, R6              | 2        | 301 Ω      | RES, 301 Ω, 1%, 0.063 W, AEC-<br>Q200 Grade 0, 0402                           | 0402                           | CRCW0402301<br>RFKED    | Vishay-Dale            |

| SH-J1, SH-J2        | 2        | 1 × 2      | Shunt, 100 mil, Gold plated, Black                                            | Shunt                          | SNT-100-BK-G            | Samtec                 |

| U1                  | 1        |            | Single High Speed Differential<br>Driver, 5-pin SOT-23, Pb-Free               | DBV0005A                       | DSLVDS1001DB<br>VT      | Texas<br>Instruments   |

| U2                  | 1        |            | 3-V LVDS Single CMOS Differential<br>Line Receiver, 5-pin SOT-23, Pb-<br>Free | DBV0005A                       | DSLVDS1002DB<br>VT      | Texas<br>Instruments   |

| FID1, FID2,<br>FID3 | 0        |            | Fiducial mark. There is nothing to buy or mount.                              | N/A                            | N/A                     | N/A                    |

| R7                  | 0        | 100        | RES, 100, 1%, 0.063 W, 0402                                                   | 0402                           | RC0402FR-<br>07100RL    | Yageo America          |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated