# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

#### **General Description**

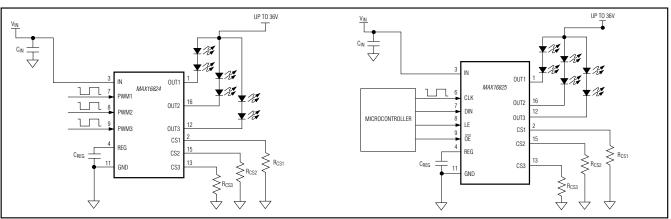

The MAX16824/MAX16825 three-channel LED drivers operate over a 6.5V to 28V input voltage range. These devices provide three open-drain constant-current-sinking outputs that are rated to 36V and deliver up to 150mA of current to each string of high-brightness LEDs (HB LEDs). The current at each output is programmable by means of an external current-sense resistor. The MAX16824 features three PWM inputs that control the duty cycle of the output current, allowing a wide LED dimming range to be implemented. The PWM inputs also function as on/off control for each corresponding output. The MAX16825 offers a 4-wire serial interface, a 3-bit shift register, and a 3-bit transparent latch. The serial interface allows a microcontroller to configure the output channels using four inputs (DIN, CLK, LE, OE) and a data output (DOUT). DOUT allows multiple drivers to be cascaded and operated together.

The MAX16824/MAX16825's on-board pass elements minimize the need for external components, while at the same time, providing  $\pm 5\%$  LED current accuracy. Additional features include a +5V ( $\pm 5\%$ ) regulated output with 4mA output current capability and thermal protection.

The MAX16824/MAX16825 are available in a thermally enhanced 16-pin TSSOP-EP package and specified over the -40 $^{\circ}$ C to +125 $^{\circ}$ C temperature range.

### **Applications**

Industrial Lighting

- Architectural and Decorative Lighting

- Mood Lighting

- Indoor and Outdoor LED Video Displays

- Automotive Lighting

- LCD Display Backlighting

#### Features

- 6.5V to 28V Operating Range

- Outputs Connected to 36V Supply for Long LED Strings

- Three 36V-Rated Output Channels with Independently Adjustable LED Current

- ♦ 150mA Output Current Per Channel

- ±5% LED Current Accuracy

- PWM Dimming Three Independent Dimming Control Inputs (MAX16824) 4-Wire Serial Interface LED Current Chopping (MAX16825)

- +5V (±5%) Regulated Output with 4mA Source Capability

- Fast Transient Dimming Response

- ♦ 200mV Current-Sense Reference Reduces Power Loss

- Thermal Shutdown

- ♦ -40°C to +125°C Operating Temperature Range

- Thermally Enhanced, 16-Pin TSSOP Exposed Pad Package

### **Ordering Information**

| PART           | TEMP RANGE      | PIN PACKAGE  |

|----------------|-----------------|--------------|

| MAX16824AUE+   | -40°C to +125°C | 16 TSSOP-EP* |

| MAX16824AUE/V+ | -40°C to +125°C | 16 TSSOP-EP* |

| MAX16825AUE+   | -40°C to +125°C | 16 TSSOP-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

N denotes an automotive qualified part.

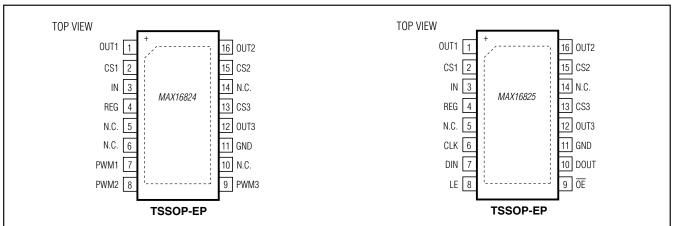

Pin Configurations appear at end of data sheet.

### **Typical Operating Circuits**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

#### **ABSOLUTE MAXIMUM RATINGS**

| IN to GND                             | 0.3V to +30V |

|---------------------------------------|--------------|

| OUT1, OUT2, OUT3 to GND               | 0.3V to +40V |

| CS1, CS2, CS3, REG to GND             | 0.3V to +6V  |

| PWM1, PWM2, PWM3 to GND               | 0.3V to +6V  |

| DIN, CLK, LE, OE, DOUT to GND         | 0.3V to +6V  |

| Maximum Current into Any Pin          |              |

| (except OUT1, OUT2, OUT3)             | ±20mA        |

| Maximum Current into OUT1, OUT2, OUT3 |              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-------------------------------------------------------|

| 16-Pin TSSOP-EP (derate 26.1mW/°C above +70°C)2089mW  |

| Operating Temperature Range40°C to +125°C             |

| Junction Temperature+150°C                            |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

16 TSSOP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )....+38.3°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )....+3°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 12V, C_{REG} = 1\mu F \text{ to GND}, I_{REG} = 0, R_{CS} = 2\Omega \text{ from CS} \text{ to GND}, T_J = T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}$ . Typical values are at  $T_J = T_A = +25^{\circ}\text{C}$ .) (Note 2)

| PARAMETER                    | SYMBOL            | CONDITIONS                                                  | MIN  | ТҮР  | MAX  | UNITS |  |

|------------------------------|-------------------|-------------------------------------------------------------|------|------|------|-------|--|

| Supply Voltage Range         | V <sub>IN</sub>   |                                                             | 6.5  |      | 28.0 | V     |  |

| GND Current                  | I <sub>GND</sub>  | $I_{OUT1} = I_{OUT2} = I_{OUT3} = 100$ mA                   |      | 5    | 10   | mA    |  |

| LED Current-Sense Accuracy   |                   | 10mA < I <sub>OUT</sub> < 100mA                             |      |      | 5    | %     |  |

| (Note 3)                     |                   | 10mA < I <sub>OUT</sub> < 150mA                             |      |      | 7    | 70    |  |

| Dropout Voltage (Note 4)     |                   | IOUT_ = 100mA (current pulsed)                              |      | 0.75 | 1.5  | - V   |  |

|                              | $\Delta V_{DO}$   | I <sub>OUT</sub> = 150mA (current pulsed)                   |      | 1.2  | 2.25 |       |  |

| Output Current Slew Rate     |                   | Current rising, $V_{OUT} = 4V$                              |      | 100  |      | mA/µs |  |

| Output Current Leakage       | ILEAK             | $V_{PWM1} = V_{PWM2} = V_{PWM3} = 0V$                       |      |      | 1    | μA    |  |

| CURRENT SENSE                |                   |                                                             |      |      |      |       |  |

| Regulated CS_ Voltage        | V <sub>CS</sub> _ | $V_{CS1} = V_{CS2} = V_{CS3}$                               | 190  | 200  | 210  | mV    |  |

| OVERTEMPERATURE PROTECT      | ΓΙΟΝ              |                                                             |      |      |      |       |  |

| Thermal Shutdown Temperature |                   |                                                             |      | 165  |      | °C    |  |

| Thermal Shutdown Hysteresis  |                   |                                                             |      | 23   |      | °C    |  |

| +5V REGULATOR (REG)          |                   |                                                             |      |      |      |       |  |

| Output Voltage               | VREG              | I <sub>REG</sub> = 0mA (Note 5)                             | 4.75 | 5    | 5.25 | V     |  |

| REG Output Current           | IREG              | 4.75V < V <sub>REG</sub>                                    | 4    |      |      | mA    |  |

| REG Short-Circuit Current    | IREGSC            | V <sub>REG</sub> = 0V (Note 6)                              | 15   | 40   | 90   | mA    |  |

| LOGIC INPUT (PWM1, PWM2, PV  | VM3)              |                                                             | ·    |      |      |       |  |

| PWM_ Input Bias Current      | IPWM              | $V_{PWM1} = V_{PWM2} = V_{PWM3} = 5V$                       |      |      | 1    | μA    |  |

| PWM_ Input-Voltage High      | VIH               |                                                             | 4    |      |      | V     |  |

| PWM_ Input-Voltage Low       | VIL               |                                                             |      |      | 0.6  | V     |  |

| PWM_Turn-On Delay            |                   | 50% of V <sub>PWM</sub> to 50% of $\Delta$ V <sub>OUT</sub> |      |      | 475  | ns    |  |

| PWM_Turn-Off Delay           |                   | 50% of V <sub>PWM</sub> to 50% of $\Delta$ V <sub>OUT</sub> |      |      | 150  | ns    |  |

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, C_{REG} = 1\mu F \text{ to GND}, I_{REG} = 0, R_{CS} = 2\Omega \text{ from CS} \text{ to GND}, T_J = T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}$ . Typical values are at  $T_J = T_A = +25^{\circ}\text{C}$ .) (Note 2)

| PARAMETER                              | SYMBOL                           | CONDITIONS                                                                                                                                     | MIN | ТҮР | MAX | UNITS |

|----------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| OUTPUTS (OUT1, OUT2, OUT3)             | 1                                | · · · · · ·                                                                                                                                    |     |     |     |       |

| Turn-On Time                           | t <sub>R</sub>                   | $\ensuremath{PWM}\xspace_{rising}$ time, $\ensuremath{t}\xspace_{R}$ , is measured from 20% to 80% of $\ensuremath{I}\xspace_{UUT}\xspace_{I}$ |     |     | 1   | μs    |

| Turn-Off Time                          | tF                               | $PWM\_$ falling time, $t_F,$ is measured from 80% to 20% of $I_{OUT\_}$                                                                        |     |     | 1   | μs    |

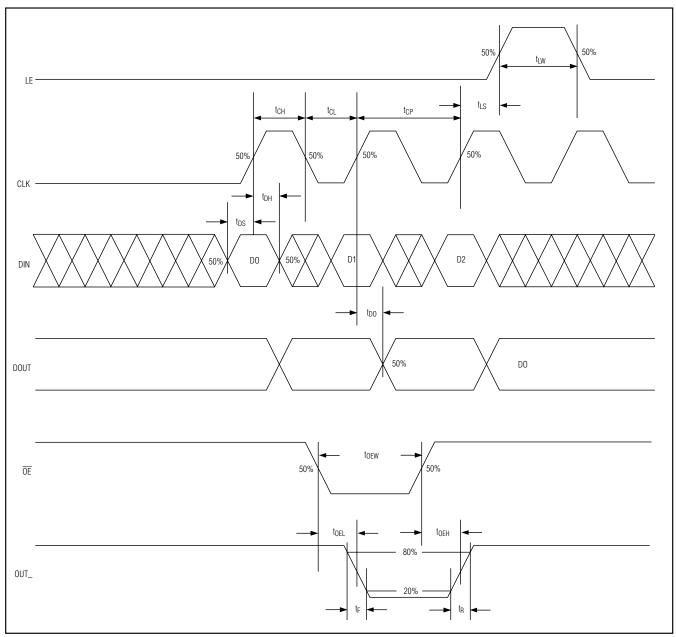

| SPI INTERFACE (CLK, LE, OE, D          | IN, DOUT) (F                     | igures 3 and 4)                                                                                                                                |     |     |     |       |

| DIN, CLK, LE, OE Input Bias<br>Current |                                  | $V_{\text{DIN}} = V_{\text{CLK}} = V_{\text{LE}} = V_{\overline{\text{OE}}} = 0 \text{ or } 5V$                                                |     |     | 1   | μA    |

| DIN, CLK, LE, OE Input-Voltage<br>High | VIH                              |                                                                                                                                                | 2.2 |     |     | V     |

| DIN, CLK, LE, OE Input-Voltage<br>Low  | VIL                              |                                                                                                                                                |     |     | 0.5 | V     |

| CLK Clock Period                       | tCP                              | 50% of CLK rising to 50% of next CLK rising, Figure 3                                                                                          | 50  |     |     | ns    |

| CLK Pulse-Width High                   | tсн                              | 50% of CLK rising to 50% of CLK falling,<br>Figure 3                                                                                           | 24  |     |     | ns    |

| CLK Pulse-Width Low                    | tCL                              | 50% of CLK falling to 50% of CLK rising,<br>Figure 3                                                                                           | 24  |     |     | ns    |

| DIN Setup Time                         | tDS                              | 50% of DIN rising to 50% of CLK rising,<br>Figure 3                                                                                            | 5   |     |     | ns    |

| DIN Hold Time                          | tDH                              | 50% of CLK rising to 50% of DIN falling,<br>Figure 3                                                                                           | 10  |     |     | ns    |

| DOUT Propagation Delay                 | tdo                              | 50% of CLK rising to 50% of DOUT rising/<br>falling, Figure 3                                                                                  | 5   |     |     | ns    |

| DOUT Rise/Fall Time                    | t <sub>DR</sub> /t <sub>DF</sub> | C <sub>DOUT</sub> = 10pF, 10% to 90% of DOUT<br>rising/falling edge (Note 7)                                                                   |     |     | 15  | ns    |

| DOUT Voltage High                      | V <sub>DOH</sub>                 | I <sub>SOURCE</sub> = 4mA                                                                                                                      | 4.5 |     |     | V     |

| DOUT Voltage Low                       | VDOL                             | I <sub>SINK</sub> = 4mA                                                                                                                        |     |     | 0.5 | V     |

| LE Pulse-Width High                    | tLW                              | 50% of LE rising to 50% of LE falling,<br>Figure 3                                                                                             | 20  |     |     | ns    |

| LE Setup Time                          | tLS                              | 50% of CLK rising to 50% of LE rising,<br>Figure 3                                                                                             | 15  |     |     | ns    |

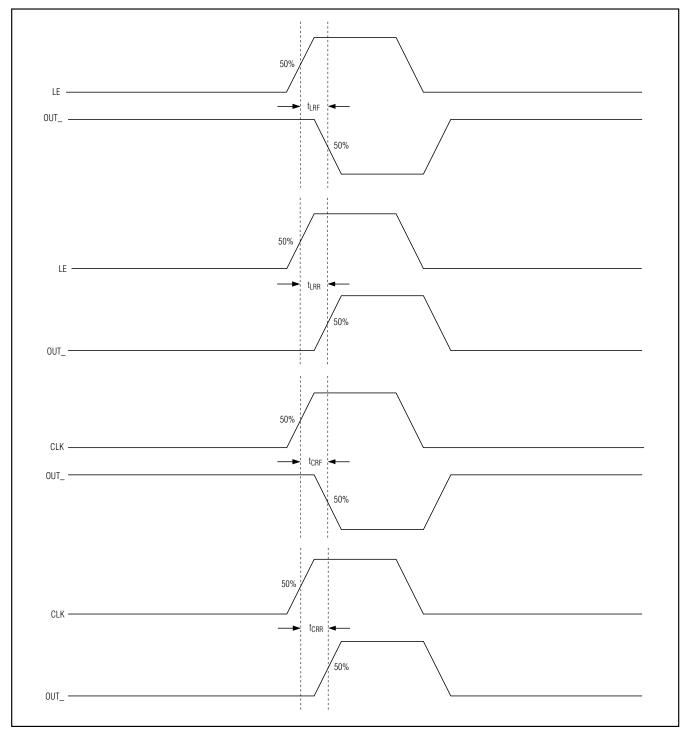

| LE Rising to OUT_ Rising Delay         | t <sub>LRR</sub>                 | 50% of LE rising to 50% of OUT_ rising,<br>Figure 4                                                                                            |     |     | 150 | ns    |

| LE Rising to OUT_ Falling Delay        | t <sub>LRF</sub>                 | 50% of LE rising to 50% of OUT_ falling,<br>Figure 4                                                                                           |     |     | 475 | ns    |

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, C_{REG} = 1\mu F \text{ to GND}, I_{REG} = 0, R_{CS} = 2\Omega \text{ from CS} \text{ to GND}, T_J = T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}$ . Typical values are at  $T_J = T_A = +25^{\circ}\text{C}$ .) (Note 2)

| PARAMETER                        | SYMBOL           | CONDITIONS                                                             | MIN | ТҮР | MAX | UNITS |

|----------------------------------|------------------|------------------------------------------------------------------------|-----|-----|-----|-------|

| CLK Rising to OUT_ Rising Delay  | <sup>t</sup> CRR | 50% of CLK rising to 50% of OUT_ rising,<br>Figure 4                   |     |     | 150 | ns    |

| CLK Rising to OUT_ Falling Delay | <sup>t</sup> CRF | 50% of CLK rising to 50% of OUT_ falling,<br>Figure 4                  |     |     | 475 | ns    |

| OE Rising to OUT_ Rising Delay   | toeh             | 50% of $\overline{\text{OE}}$ rising to 50% of OUT_ rising, Figure 3   |     |     | 150 | ns    |

| OE Falling to OUT_ Falling Delay | toel             | 50% of $\overline{\text{OE}}$ falling to 50% of OUT_ falling, Figure 3 |     |     | 475 | ns    |

Note 2: All devices are 100% production tested at  $T_J = +25^{\circ}C$  and  $T_J = +125^{\circ}C$ . Limits to  $-40^{\circ}C$  are guaranteed by design.

Note 3: This specification does not include sense resistor tolerance and ground error.

Note 4: Dropout is measured as follows:  $R_{CS}$  = 1.21 $\Omega$  from CS\_ to GND. Force 100mA into OUT\_ and measure the dropout voltage from OUT\_ to CS\_. DVDO = ( $\Delta$ OUT\_ - V<sub>CS</sub>).

Note 5: OUT's current regulation varies with load across REG (see the Typical Operating Characteristics).

Note 6: Overtemperature protection does not function if the output of the 5V reference (REG) is shorted to ground.

Note 7: Guaranteed by design, not production tested.

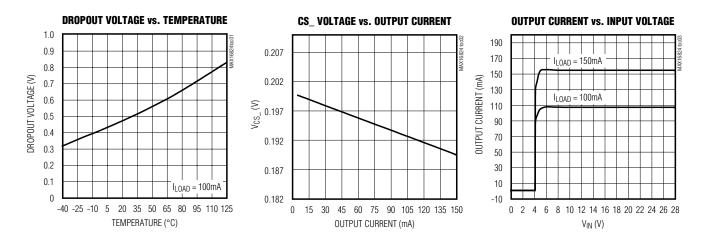

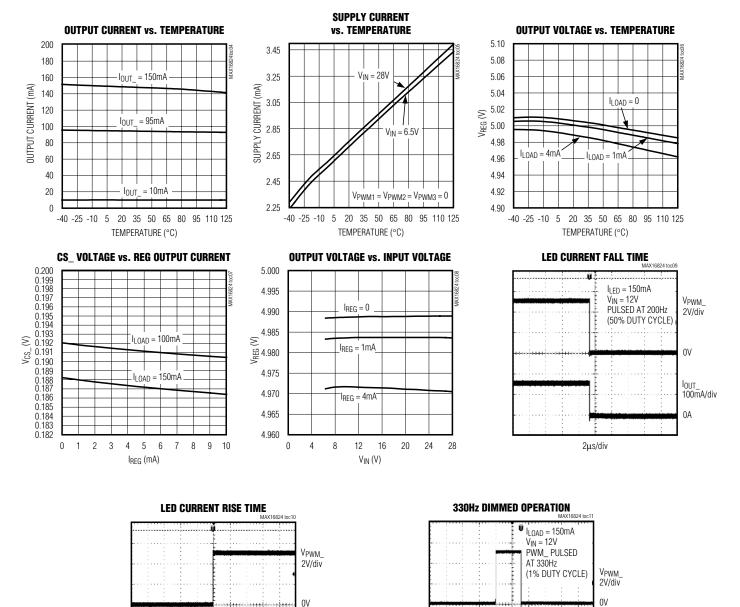

### **Typical Operating Characteristics**

$(V_{IN} = 12V, C_{REG} = 1\mu F \text{ to GND}, I_{REG} = 0, R_{CS} = 2\Omega \text{ from CS} \text{ to GND}, T_A = +25^{\circ}C, \text{ unless otherwise noted}$ . Typical values are at  $T_A = +25^{\circ}C.$ )

# MAX16824/MAX16825 High-Voltage, Three-Channel Linear High-Brightness LED Drivers

#### **Typical Operating Characteristics (continued)**

(VIN = 12V, CREG = 1µF to GND, IREG = 0, RCS\_ = 2 $\Omega$  from CS\_ to GND, TA = +25°C, unless otherwise noted. Typical values are at TA = +25°C.)

I<sub>OUT</sub>\_ 100mA/div

0A

$I_{\rm LED} = 150 \, \text{mA}$

PULSED AT 200Hz

(50% DUTY CYCLE)

$V_{IN} = 12V$

2µs/div

I<sub>OUT</sub>\_\_\_\_\_ 100mA/div

0A

20µs/div

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

### **Pin Description**

| PIN          |                   | NAME | FUNCTION                                                                                                                                                                                                                                       |  |  |

|--------------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX16824     | MAX16824 MAX16825 |      | FUNCTION                                                                                                                                                                                                                                       |  |  |

| 1            | 1                 | OUT1 | Channel 1 LED Driver Output. OUT1 is an open-drain, constant-current-sinking output rated to 36V.                                                                                                                                              |  |  |

| 2            | 2                 | CS1  | Channel 1 Sense Amplifier Negative Input. Connect a current-sense resistor between CS1 and GND to program the output current level for channel 1.                                                                                              |  |  |

| 3            | 3                 | IN   | Positive Input Supply. Bypass with a 0.1µF (min) capacitor to GND.                                                                                                                                                                             |  |  |

| 4            | 4                 | REG  | +5V-Regulated Output. Connect a 1µF capacitor from REG to GND.                                                                                                                                                                                 |  |  |

| 5, 6, 10, 14 | 5, 14             | N.C. | No Connection. Must be left unconnected.                                                                                                                                                                                                       |  |  |

| 7            | —                 | PWM1 | Dimming Input 1. PWM1 is a dimming input for channel 1. A logic-low turns off OUT1 and a logic-high turns on OUT1.                                                                                                                             |  |  |

| 8            | _                 | PWM2 | Dimming Input 2. PWM2 is a dimming input for channel 2. A logic-low turns off OUT2 and a logic-high turns on OUT2.                                                                                                                             |  |  |

| 9            | _                 | PWM3 | Dimming Input 3. PWM3 is a dimming input for channel 3. A logic-low turns off OUT3 and a logic-high turns on OUT3.                                                                                                                             |  |  |

| 11           | 11                | GND  | Ground                                                                                                                                                                                                                                         |  |  |

| 12           | 12                | OUT3 | Channel 3 LED Driver Output. OUT3 is an open-drain, constant-current-sinking output rated to 36V.                                                                                                                                              |  |  |

| 13           | 13                | CS3  | Channel 3 Sense Amplifier Negative Input. Connect a current-sense resistor between CS3 and GND to program the output current level for channel 3.                                                                                              |  |  |

| 15           | 15                | CS2  | Channel 2 Sense Amplifier Negative Input. Connect a current-sense resistor between CS2 and GND to program the output current level for channel 2.                                                                                              |  |  |

| 16           | 16                | OUT2 | Channel 2 LED Driver Output. OUT2 is an open-drain, constant-current-sinking output rated to 36V.                                                                                                                                              |  |  |

| _            | 7                 | DIN  | Serial-Data Input. Data is loaded into the internal 3-bit shift register on the rising edge of CLK.                                                                                                                                            |  |  |

| _            | 8                 | LE   | Latch-Enable Input. Data loaded transparently from the internal shift register to the output latch while LE is high. Data is latched into the output latch on the LE's falling edge and retained while LE is low.                              |  |  |

| _            | 9                 | ŌĒ   | Output Enable Input. Drive $\overline{OE}$ high to place all outputs into a high-impedance mode without altering the contents of the output latches. Drive $\overline{OE}$ low to force all outputs to follow the state of the output latches. |  |  |

| _            | 10                | DOUT | Serial-Data Output. Data is clocked out of the internal 3-bit shift register to DOUT on the rising edge of CLK. DOUT is a replica of the shift register's last bit.                                                                            |  |  |

| _            | 6                 | CLK  | Clock Input                                                                                                                                                                                                                                    |  |  |

|              | _                 | EP   | Exposed Pad. Connect EP to a large-area ground plane for effective power dissipation.<br>Do not use as the IC ground connection.                                                                                                               |  |  |

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

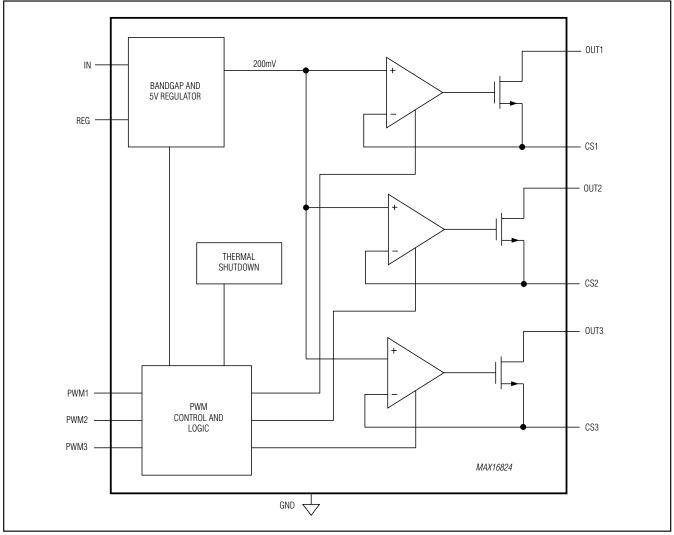

Figure 1. Internal Block Diagram (MAX16824)

#### **Detailed Description**

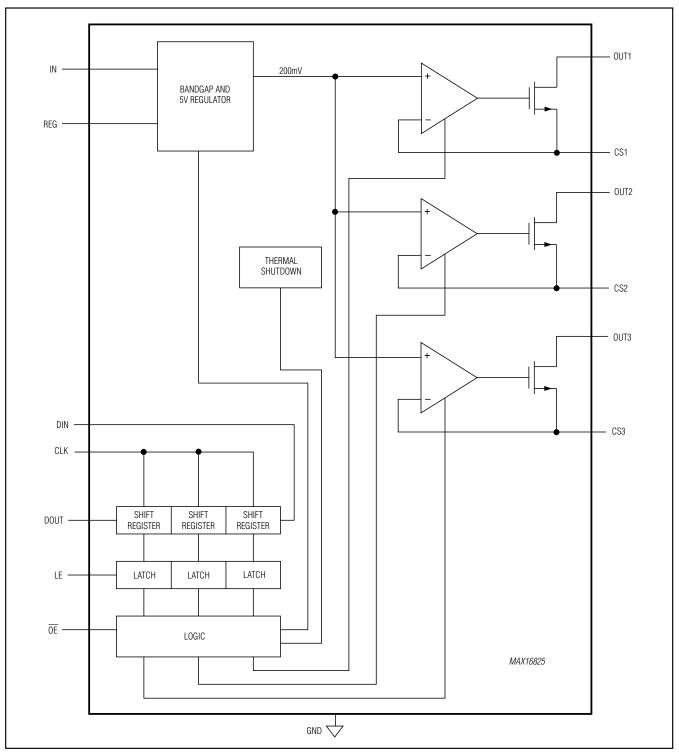

The MAX16824/MAX16825 are three-channel LED drivers that operate from a 6.5V to 28V input voltage range. These devices provide three independent opendrain, constant-current-sinking outputs rated to 36V and deliver up to 150mA of current to each HB LED string. The current in each channel is programmable using an external current-sense resistor in series with each internal power MOSFET's source. The MAX16824 features three separate PWM inputs that allow a wide range of independent dimming level at each of the three outputs. The PWM inputs also function as on/off control inputs for each corresponding output (Figure 1).

The 4-wire serial interface comprises a 3-bit shift register and a 3-bit transparent latch. The shift register is updated using a clock input (CLK) and a data input

control the state of each output (Figure 2).

updated using a clock input (CLK) and a data input (DIN). DOUT is the last bit of the shift register. This feature allows multiple drivers to be cascaded and operated together. The latch is transparent from the shift register outputs to the LED output when LE is high while it latches the shift register state on the falling edge of LE. The output-enable input  $(\overline{OE})$  allows simultaneous enabling or disabling of all three outputs.

The MAX16825 includes a 4-wire serial interface to

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

Figure 2. Internal Block Diagram (MAX16825)

# MAX16824/MAX16825 High-Voltage, Three-Channel Linear High-Brightness LED Drivers

On-board pass elements minimize the need for external components while providing  $\pm 5\%$  LED current accuracy. Additional features include a +5V ( $\pm 5\%$ ) regulated output with 4mA output current capability and thermal protection.

The MAX16824/MAX16825 use a feedback loop to linearly control the current at each output. The voltage across each sense resistor is regulated to 200mV by the internal feedback loop. The output current is set by selecting the value of R<sub>CS</sub>.

#### +5V Regulator (REG)

The MAX16824/MAX16825 include a fixed +5V output regulator that delivers up to 4mA of load current for auxiliary low power applications throughout the 6.5V to 28V input voltage range. Connect a  $1\mu$ F compensation capacitor from REG to ground.

#### **Thermal Protection**

The MAX16824/MAX16825 enter a thermal shutdown mode in the event of overheating. When the junction temperature exceeds  $T_J = +165^{\circ}$ C, the internal thermal protection circuit turns off the series pass elements. The MAX16824/MAX16825 recover from thermal shutdown mode when the junction temperature drops by 23°C. The thermal protection does not operate if the regulator (REG) is in a short-circuit condition.

#### 4-Wire Serial Interface (MAX16825)

The MAX16825 features a 4-wire serial interface (DIN, CLK, LE,  $\overline{OE}$ ) and a data output (DOUT) that allows the use of a microcontroller to write brightness data to the MAX16825. The serial-interface data word length is 3 bits (D0, D1, D2). The functions of the interface inputs are as follows: DIN is the serial-data input, which must be stable when it is sampled by the MAX16825 on the rising edge of CLK. Data shifts in with the MSB first. This means that data bit D2 is clocked in first, followed by 2 more data bits (D1 and finishing with the LSB D0). CLK is the serial-clock input, which shifts data at DIN into the MAX16825's 3-bit shift register on the rising edge. LE is the latch-enable input that allows the transfer of data from the MAX16825's 3-bit shift register to its 3-bit latch when LE is high (transparent latch) and latches the data on the falling edge of LE (Figure 4).

Output enable  $(\overline{OE})$  provides simultaneous control of the output drivers. Driving  $\overline{OE}$  high places outputs OUT1, OUT2, and OUT3 into a high-impedance mode without altering the contents of the output latches. Driving  $\overline{OE}$  low allows outputs OUT1, OUT2, and OUT3 to follow the state of the output latches.

$\overline{\text{OE}}$  is independent of the operation of the serial interface. Data can be shifted into the serial-interface shift register and latched regardless of the state of  $\overline{\text{OE}}$ . DOUT is the serial-data output that shifts data out from the MAX16825's 3-bit shift register on the rising edge of CLK. Data at DIN propagates through the shift register and appears at DOUT three clock cycles later.

#### **Applications Information**

#### **Programming the LED Current**

The MAX16824/MAX16825 use sense resistors to set the output current in each channel. To set the LED current for a particular channel, connect a sense resistor across the corresponding current-sense input (CS\_) and GND. For better performance, connect the low side of the current-sense resistors to the IC's ground terminal and the high side to the CS\_ terminal with short traces. The value of the sense resistor for a given desired current is calculated with the following equation:

$$\mathsf{R}_{\mathsf{CS}}(\Omega) = \frac{\mathsf{V}_{\mathsf{CS}}(\mathsf{V})}{\mathsf{I}_{\mathsf{OUT}}(\mathsf{A})}$$

where V<sub>CS</sub> is 200mV and I<sub>OUT</sub> is I<sub>LED</sub> (see the *Electrical Characteristics* table).

#### **LED Supply Voltage Considerations**

For proper operation, the minimum LED supply voltage (applied between the LED string anode and ground) must always be:

$$V_{\text{LED(MIN)}} \ge V_{\text{CS}} + V_{\text{FT(MAX)}} + \Delta V_{\text{DO}}$$

where V<sub>CS</sub> is the voltage drop across the sense resistor R<sub>CS</sub>, V<sub>FT(MAX)</sub> is the total forward voltage of all series connected LEDs and  $\Delta$ V<sub>DO</sub> is the maximum dropout voltage of the regulator.

#### **Pulse-Width Dimming (MAX16824)**

The MAX16824 includes pulsed-width current dimming inputs (PWM\_) to control the LED brightness. An application of up to 5kHz signal or less is recommended at PWM\_ input for proper operation. PWM\_ also functions as an active-high enable input for each output channel. A logic-low at PWM\_ turns off OUT\_ and a logic-high turns on OUT\_.

#### **Pulse-Width Dimming (MAX16825)**

The MAX16825 provides three methods of pulsed-width current dimming.

One method of pulse dimming the output channels is to drive  $\overline{\text{OE}}$  low while latching a different set of three bits

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

Figure 3. 4-Wire Serial-Interface Timing Diagram

data. Holding  $\overline{\text{OE}}$  low allows the output channels to follow the state of the output latches. The duty cycle depends on LE's frequency. All output channels are affected at the same time.

Another method of <u>pulse</u> dimming the outputs is to hold LE high and drive <u>OE</u> with a PWM signal. Because the input bits are always latched, the serial input constantly refreshes the register. The control bits must be carefully selected to dim the outputs properly.

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

Figure 4. LE and CLK to OUT\_ Timing

# MAX16824/MAX16825 **High-Voltage, Three-Channel Linear High-Brightness LED Drivers**

A third method is to hold both LE and  $\overline{OE}$  in the enabled state. This allows the data bits to directly control the output channels, and hence, pulse dim the output current. Make sure that the clock frequency does not exceed the maximum rate at which the device can change the state of the output channels.

#### **Power Dissipation**

The power dissipation (PD) of the MAX16824/ MAX16825 is determined from the following equation:

$P_{D} = (V_{IN} \times I_{IN}) + (V_{INI} - V_{I} + V_{CS1}) \times (I_{I} + V_{CS1}) \times (I_{I} + V_{CS1})$ +  $(V_{INL} - V_{LED2} - V_{CS2}) \times (I_{LED2} \times DUTY2)$ +  $(V_{INL} - V_{LED3} - V_{CS3}) \times (I_{LED3} \times DUTY3)$

where:

$V_{IN}$  = supply voltage VINL = supply voltage to the LED strings IIN = supply current

V<sub>LED</sub> = total forward voltage for one LED string ILED = LED current

Vcs = 200mV drop across Rcs

DUTY\_ = PWM\_ duty cycle

The worst-case power dissipation occurs when the drop across each internal MOSFET is at its maximum with all three channels delivering the maximum allowable output current. The maximum drop across the internal MOSFETs is determined by:

VINL - VLED - VCS when VLED is at its minimum.

Higher ambient temperature increases the thermal stress even further due to the reduction in voltage drop across the LEDs. The MAX16824/MAX16825 thermal specifications are given according to the JEDEC-51 guidelines. Good mechanical/thermal design practices must be applied to help maintain the device junction temperature below the absolute maximum ratings at all times.

#### **Chip Information**

PROCESS: BICMOS-DMOS

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE     | PACKAGE | OUTLINE NO.    | LAND           |

|-------------|---------|----------------|----------------|

| TYPE        | CODE    |                | PATTERN NO.    |

| 16 TSSOP-EP | U16E+3  | <u>21-0108</u> | <u>90-0120</u> |

**Pin Configurations**

# High-Voltage, Three-Channel Linear High-Brightness LED Drivers

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                   | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 11/07            | Initial release                                                                                               | _                |

| 1                  | 1/08             | Updated data sheet with automotive temperature specification                                                  | 1, 2, 3, 4, 7    |

| 2                  | 4/09             | Updated the Ordering Information and LED Supply Voltage Considerations sections.                              | 1, 6, 7, 9, 12   |

| 3                  | 1/13             | Corrected Absolute Maximum Ratings on the continuous power dissipation; added Package Thermal Characteristics | 2–4              |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

© 2013 Maxim Integrated Products, Inc.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.