# Active Clamp Voltage Mode PWM Controller for Off-Line Applications

The NCP1280 provides a highly integrated solution for off-line power supplies requiring high-efficiency and low parts count. This voltage mode controller provides control outputs for driving a forward converter primary MOSFET and an auxiliary MOSFET for active clamp circuit. The second output with its programmable delay can also be used for driving a synchronous rectifier on the secondary or for asymmetric half bridge circuits. Incorporation of high voltage startup circuitry (with 700 V capability) reduces parts count and system power dissipation. Additional features such as line UV/OV protection, soft-start, single resistor programmable (high) frequency oscillator, line voltage feedforward, dual mode overcurrent protection and maximum duty cycle control, allow converter optimization at minimal cost. Compared to a traditional forward converter, an NCP1280 based converter can offer significant efficiency improvements and system cost savings.

#### **Features**

- Internal High Voltage Startup Regulator (25 V to 700 V)

- Dual Control Outputs with Adjustable Overlap Delay

- Programmable Maximum Duty Cycle Control

- Single Resistor Oscillator Frequency Setting

- Fast Line Feedforward

- Line Under/Overvoltage Lockout

- Dual Mode Overcurrent Protection

- Programmable Soft-Start

- Precision 5.0 V Reference

- Pb-Free Package is Available\*

# **Typical Applications**

- Off-Line Power Converters in 100-500 W Range

- Desktop Power Supplies (High-End)

- Industrial Power Supplies

- Plasma/LCD TV Front-End

# ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAM** 16 SO-16 NCP1280G **D SUFFIX AWLYWW** CASE 751B 8888888 NCP1280 = Device Code = Assembly Location Α WL = Wafer Lot = Year ww = Work Week

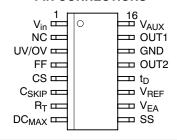

#### **PIN CONNECTIONS**

= Pb-Free Package

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

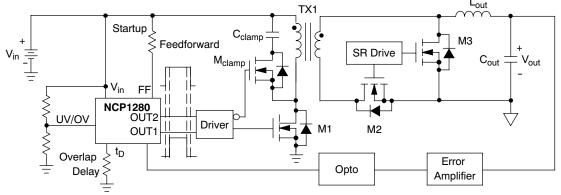

Figure 1. Forward Converter for Off-line Applications Using PFC Inputs

1

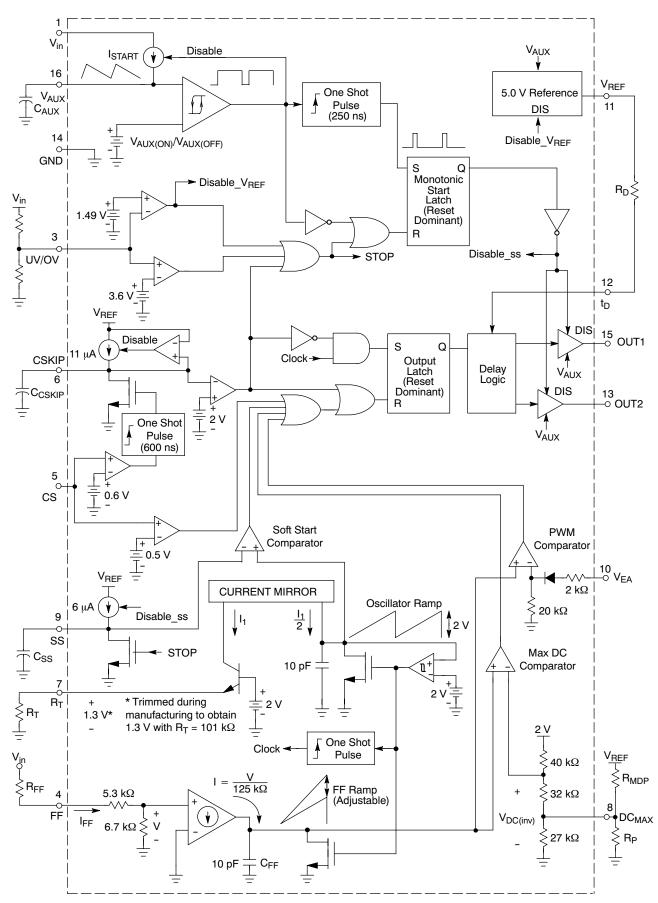

Figure 2. NCP1280 Functional Block Diagram

# **PIN DESCRIPTION**

| Pin | Name              | Application Information                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | V <sub>in</sub>   | This pin is connected to the input voltage of the system. The voltage can be a rectified, filtered line voltage or output of a power factor correction (PFC) front end. A constant current source supplies current from this pin to the capacitor connected on the V <sub>AUX</sub> pin. The charge current is typically 13.8 mA. Maximum input voltage is 700 V.                               |  |  |  |  |

| 2   | NC                | Not Connected.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 3   | UV/OV             | Provides protection under line undervoltage and overvoltage conditions. The built in voltage range is ~ 2:1. If needed, the OV function can be disabled by a Zener from this pin to ground.                                                                                                                                                                                                     |  |  |  |  |

| 4   | FF                | An external resistor between $V_{in}$ and this pin adjusts the amplitude of the Feedforward Ramp in proportion to $V_{in}$ . By varying the feedforward ramp amplitude in proportion to the input voltage, open loop line regulation is improved.                                                                                                                                               |  |  |  |  |

| 5   | CS                | Overcurrent sense input. If the CS voltage exceeds 0.48 V or 0.57 V, the converter enters the Cycle by Cycle or Cycle Skip current limit mode, respectively.                                                                                                                                                                                                                                    |  |  |  |  |

| 6   | CSKIP             | The capacitor connected between this pin and ground sets the Cycle Skip period. A soft-start sequence follows at the conclusion of the fault period.                                                                                                                                                                                                                                            |  |  |  |  |

| 7   | R <sub>T</sub>    | A single external resistor between this pin and GND sets the oscillator fixed frequency.                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 8   | DC <sub>MAX</sub> | An external resistor between this pin and GND sets the voltage on the Max DC Comparator inverting input. The duty cycle is limited by comparing the voltage on the Max DC Comparator inverting input to the Feedforward Ramp.                                                                                                                                                                   |  |  |  |  |

| 9   | SS                | An internal 6.2 $\mu$ A current source charges the external capacitor connected to this pin. The duty cycle is limited during startup by comparing the voltage on this pin to the Oscillator Ramp.                                                                                                                                                                                              |  |  |  |  |

| 10  | V <sub>EA</sub>   | The error signal from an external error amplifier, typically supplied through an optocoupler, is fed into this input and compared to the Feedforward Ramp. A series diode and resistor offset the voltage on this pin before it is applied to the PWM Comparator inverting input.                                                                                                               |  |  |  |  |

| 11  | $V_{REF}$         | Precision 5.0 V reference output. Maximum output current is 6 mA.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

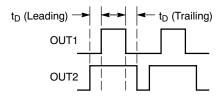

| 12  | t <sub>D</sub>    | An external resistor between V <sub>REF</sub> and this pin sets the overlap delay between OUT1 and OUT2 transitions.                                                                                                                                                                                                                                                                            |  |  |  |  |

| 13  | OUT2              | Output of the PWM controller with leading and trailing edge overlap delay. OUT2 can be used to drive a synchronous rectifier topology, an active clamp/reset switch, or both.                                                                                                                                                                                                                   |  |  |  |  |

| 14  | GND               | Control circuit ground.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 15  | OUT1              | Main output of the PWM controller.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 16  | V <sub>AUX</sub>  | Positive input supply voltage. This pin is connected to an external capacitor for energy storage. An internal current supplies current from $V_{in}$ to this pin. Once the voltage on $V_{AUX}$ reaches 11 V, the current source turns OFF. It turns ON again once $V_{AUX}$ falls to 7 V. During normal operation, power is supplied to the IC via this pin, by means of an auxiliary winding. |  |  |  |  |

# **ORDERING INFORMATION**

| Device      | Package            | Shipping <sup>†</sup> |

|-------------|--------------------|-----------------------|

| NCP1280DR2  | SO-16              | 2500 / Tape & Reel    |

| NCP1280DR2G | SO-16<br>(Pb-Free) | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# MAXIMUM RATINGS (Note 1)

| Rating                                                                          | Symbol                      | Value                              | Unit |

|---------------------------------------------------------------------------------|-----------------------------|------------------------------------|------|

| Input Line Voltage                                                              | V <sub>in</sub>             | -0.3 to 700                        | V    |

| Auxiliary Supply Voltage                                                        | V <sub>AUX</sub>            | -0.3 to 18                         | V    |

| Transient Auxiliary Supply Voltage (Duration < 10 ms, I <sub>AUX</sub> < 10 mA) | V <sub>AUX(transient)</sub> | -0.3 to 20                         | V    |

| Auxiliary Supply Input Current                                                  | I <sub>AUX</sub>            | 35                                 | mA   |

| OUT1 and OUT2 Voltage                                                           | V <sub>OUT</sub>            | -0.3 to (V <sub>AUX</sub> + 0.3 V) | V    |

| OUT1 and OUT2 Output Current                                                    | I <sub>OUT</sub>            | 10                                 | mA   |

| 5.0 V Reference Voltage                                                         | V <sub>REF</sub>            | -0.3 to 6.0                        | V    |

| 5.0 V Reference Output Current                                                  | I <sub>REF</sub>            | 6.0                                | mA   |

| All Other Inputs/Outputs Voltage                                                | V <sub>IO</sub>             | -0.3 to V <sub>REF</sub>           | V    |

| All Other Inputs/Outputs Current                                                | I <sub>IO</sub>             | 10                                 | mA   |

| Operating Junction Temperature                                                  | TJ                          | -40 to 125                         | °C   |

| Storage Temperature Range                                                       | T <sub>stg</sub>            | -55 to 150                         | °C   |

| Power Dissipation at T <sub>A</sub> = 25°C                                      | P <sub>D</sub>              | 0.77                               | W    |

| Thermal Resistance, Junction to Ambient                                         | $R_{	hetaJA}$               | 130                                | °C/W |

<sup>1.</sup> Maximum Ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum–rated conditions is not implied. Functional operation should be restricted to the Recommended Operating Conditions.

Pin 1 is the HV startup of the device and is rated to the max rating of the part, or 700 V.

Machine Model Method 700 V.

Pins 2–16: Human Body Model 4000 V per MIL–STD–883, Method 3015.

Machine Model Method 200 V.

A. This device series contains ESD protection and exceeds the following tests:

**ELECTRICAL CHARACTERISTICS** ( $V_{in}$  = 82 V,  $V_{AUX}$  = 12 V,  $V_{EA}$  = 2 V,  $R_{T}$  = 101 kΩ,  $C_{CSKIP}$  = 6800 pF,  $R_{D}$  = 60.4 kΩ,  $R_{FF}$  = 1.0 MΩ, for typical values  $T_{J}$  = 25°C, for min/max values,  $T_{J}$  = -40°C to 125°C, unless otherwise noted)

| Characteristic                                                                                                                                                                                         | Symbol                                                          | Min              | Тур                | Max               | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------|--------------------|-------------------|------|

| STARTUP CONTROL AND V <sub>AUX</sub> REGULATOR                                                                                                                                                         |                                                                 |                  |                    |                   |      |

| V <sub>AUX</sub> Regulation<br>Startup Threshold/V <sub>AUX</sub> Regulation Peak (V <sub>AUX</sub> increasing)<br>Minimum Operating V <sub>AUX</sub> Valley Voltage After Turn-On<br>Hysteresis       | V <sub>AUX(on)</sub><br>V <sub>AUX(off)</sub><br>V <sub>H</sub> | 10.5<br>6.6<br>- | 11.0<br>7.0<br>4.0 | 11.5<br>7.4<br>-  | V    |

| Minimum Startup Voltage (Pin 1)<br>$I_{START} = 1.5 \text{ mA}, V_{AUX} = V_{AUX(on)} - 0.2 \text{ V}, I_{REF} = 0 \text{ A}$                                                                          | V <sub>START(min)</sub>                                         | -                | _                  | 25                | V    |

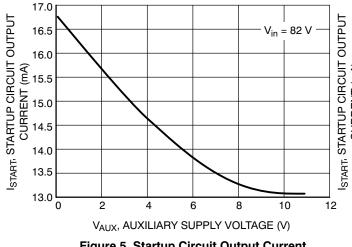

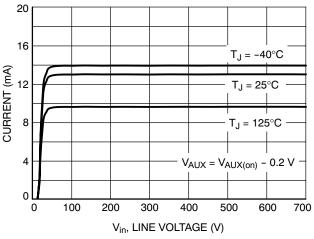

| Startup Circuit Output Current $ \begin{array}{l} V_{AUX} = 0 \ V \\ T_J = 25^{\circ}C \\ T_J = -40^{\circ}C \ to \ 125^{\circ}C \\ V_{AUX} = V_{AUX(on)} - 0.2 \ V \\ T_J = 25^{\circ}C \end{array} $ | I <sub>START</sub>                                              | 13<br>10<br>10   | 17.5<br>-<br>13.8  | 21<br>25<br>17    | mA   |

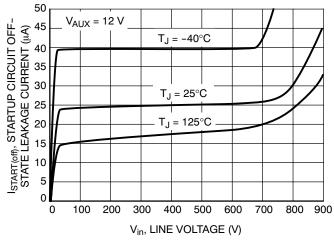

| $T_J$ = -40°C to 125°C  Startup Circuit Off-State Leakage Current ( $V_{in}$ = 700 V) $T_J$ = 25°C $T_J$ = -40°C to 125°C                                                                              | ISTART(off)                                                     | -<br>-           | 23<br>-            | 50<br>100         | μΑ   |

| Startup Circuit Breakdown Voltage (Note 2) I <sub>START(off)</sub> = 50 μA, T <sub>J</sub> = 25°C                                                                                                      | V <sub>(BR)DS</sub>                                             | 700              | -                  | -                 | ٧    |

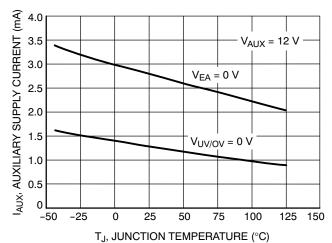

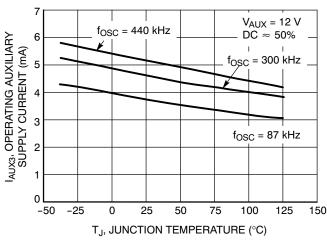

| Auxiliary Supply Current After V <sub>AUX</sub> Turn-On Outputs Disabled V <sub>EA</sub> = 0 V V <sub>UV/OV</sub> = 0.7 V Outputs Enabled                                                              | laux1<br>laux2<br>laux3                                         | -<br>-<br>-      | 2.7<br>1.3<br>4.6  | 5.0<br>2.5<br>6.5 | mA   |

| LINE UNDER/OVERVOLTAGE DETECTOR                                                                                                                                                                        | •                                                               |                  | •                  | •                 |      |

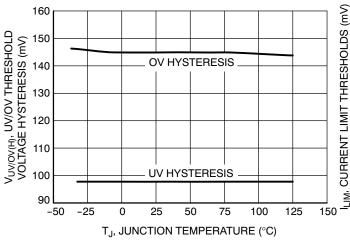

| Undervoltage Threshold (V <sub>in</sub> Increasing)                                                                                                                                                    | V <sub>UV</sub>                                                 | 1.40             | 1.52               | 1.64              | ٧    |

| Undervoltage Hysteresis                                                                                                                                                                                | V <sub>UV(H)</sub>                                              | 0.080            | 0.098              | 0.120             | ٧    |

| Overvoltage Threshold (V <sub>in</sub> Increasing)                                                                                                                                                     | V <sub>OV</sub>                                                 | 3.47             | 3.61               | 3.75              | ٧    |

| Overvoltage Hysteresis                                                                                                                                                                                 | V <sub>OV(H)</sub>                                              | -                | 0.145              | -                 | V    |

| Undervoltage Propagation Delay to Output                                                                                                                                                               | t <sub>UV</sub>                                                 | -                | 250                | -                 | ns   |

| Overvoltage Propagation Delay to Output                                                                                                                                                                | t <sub>OV</sub>                                                 | 1                | 160                | -                 | ns   |

| CURRENT LIMIT                                                                                                                                                                                          |                                                                 |                  |                    |                   |      |

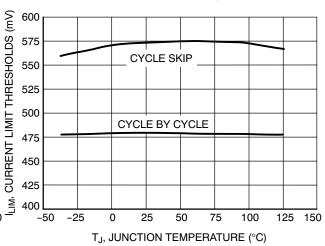

| Cycle by Cycle Threshold Voltage                                                                                                                                                                       | I <sub>LIM1</sub>                                               | 0.44             | 0.48               | 0.52              | V    |

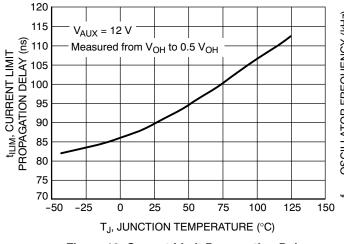

| Propagation Delay to Output ( $V_{EA}$ = 2.0 V)<br>$V_{CS}$ = $I_{LIM1}$ to 2.0 V, measured when $V_{OUT}$ reaches 0.5 $V_{OH}$                                                                        | t <sub>ILIM</sub>                                               | -                | 90                 | 150               | ns   |

| Cycle Skip Threshold Voltage                                                                                                                                                                           | I <sub>LIM2</sub>                                               | 0.54             | 0.57               | 0.62              | ٧    |

| Cycle Skip Charge Current (V <sub>CSKIP</sub> = 0 V)                                                                                                                                                   | I <sub>CSKIP</sub>                                              | 8.0              | 12.3               | 15                | μΑ   |

<sup>2.</sup> Guaranteed by design only.

**ELECTRICAL CHARACTERISTICS** ( $V_{in}$  = 82 V,  $V_{AUX}$  = 12 V,  $V_{EA}$  = 2 V,  $R_{T}$  = 101 kΩ,  $C_{CSKIP}$  = 6800 pF,  $R_{D}$  = 60.4 kΩ,  $R_{FF}$  = 1.0 MΩ, for typical values  $T_{J}$  = 25°C, for min/max values,  $T_{J}$  = -40°C to 125°C, unless otherwise noted)

| Characteristic                                                                                                                    | Symbol                               | Min        | Тур          | Max        | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------|--------------|------------|------|

| OSCILLATOR                                                                                                                        |                                      |            |              |            |      |

| Frequency (R <sub>T</sub> = 101 k $\Omega$ )<br>$T_J = 25^{\circ}C$<br>$T_J = -40^{\circ}C$ to 125°C                              | fosc1                                | 285<br>280 | 300          | 315<br>320 | kHz  |

| Frequency (R <sub>T</sub> = 220 k $\Omega$ , V <sub>EA</sub> = 1.0 V)<br>$T_J$ = 25°C<br>$T_J$ = -40°C to 125°C                   | fosc2                                | 142<br>140 | 150<br>-     | 158<br>160 | kHz  |

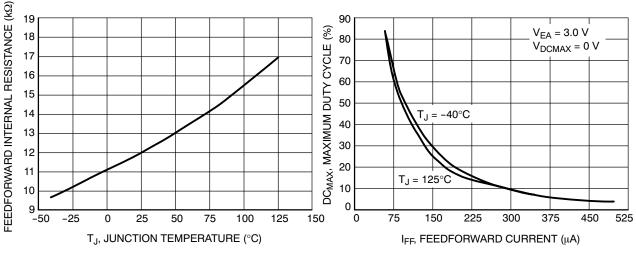

| MAXIMUM DUTY CYCLE COMPARATOR                                                                                                     |                                      |            |              |            |      |

| Maximum Duty Cycle ( $V_{EA}$ = 3.0 V, $T_J$ = 25°C) $R_P$ = 0 $\Omega$ , $R_{MDP}$ = open $R_P$ = open, $R_{MDP}$ = open         | DC <sub>MAX</sub>                    | 57<br>75   | 62<br>80     | 66<br>85   | %    |

| Open Circuit Voltage                                                                                                              | $V_{DCMAX}$                          | 0.40       | 0.47         | 0.60       | V    |

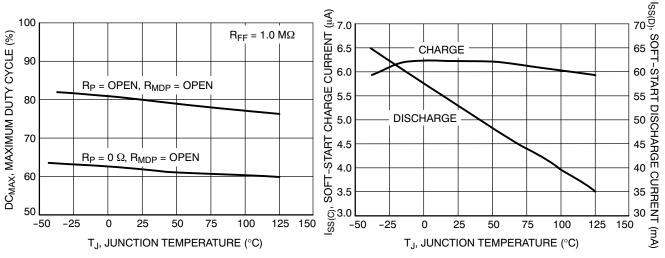

| SOFT-START                                                                                                                        |                                      |            |              |            |      |

| Charge Current (V <sub>SS</sub> = 1.0 V)                                                                                          | I <sub>SS(C)</sub>                   | 5.0        | 6.2          | 7.4        | μΑ   |

| Discharge Current (V <sub>SS</sub> = 5.0 V, V <sub>UV/OV</sub> = 0 V)                                                             | I <sub>SS(D)</sub>                   | 20         | 52.5         | -          | mA   |

| PWM COMPARATOR                                                                                                                    |                                      |            |              |            |      |

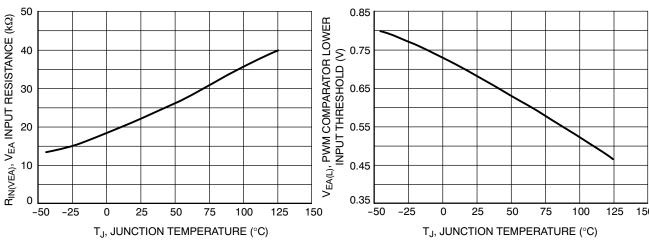

| Input Resistance (V <sub>1</sub> = 1.25 V, V <sub>2</sub> = 1.50 V)<br>$R_{IN(VEA)} = (V_2 - V_1)/(I_2 - I_1)$                    | R <sub>IN(VEA)</sub>                 | 8.0        | 22           | 60         | kΩ   |

| Lower Input Threshold                                                                                                             | V <sub>EA(L)</sub>                   | 0.3        | 0.7          | 0.9        | V    |

| Delay to Output (from V <sub>OH</sub> to 0.5 V <sub>OH</sub> )                                                                    | t <sub>PWM</sub>                     | -          | 200          | -          | ns   |

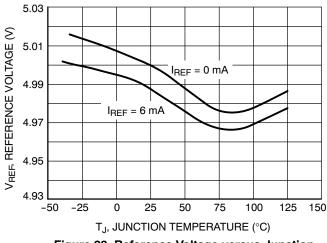

| 5.0 V REFERENCE                                                                                                                   |                                      |            |              |            |      |

| Output Voltage ( $I_{REF} = 0 \text{ mA}$ )<br>$T_J = 25^{\circ}\text{C}$<br>$T_J = -40^{\circ}\text{C}$ to $125^{\circ}\text{C}$ | V <sub>REF</sub>                     | 4.9<br>4.8 | 5.0<br>-     | 5.1<br>5.1 | V    |

| Load Regulation (I <sub>REF</sub> = 0 to 6 mA)                                                                                    | V <sub>REF(Load)</sub>               | -          | 10           | 50         | mV   |

| Line Regulation (V <sub>AUX</sub> = 7.5 to 16 V)                                                                                  | V <sub>REF(Line)</sub>               | -          | 50           | 100        | mV   |

| CONTROL OUTPUTS                                                                                                                   |                                      |            | •            | •          | •    |

| Output Voltage (I <sub>OUT</sub> = 0 mA)<br>Low State<br>High State                                                               | V <sub>OL</sub><br>V <sub>OH</sub>   |            | 0.25<br>11.8 | -<br>-     | V    |

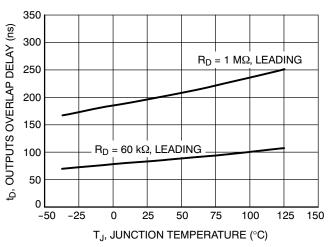

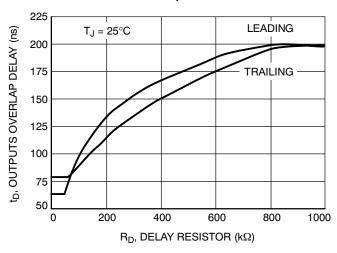

| Overlap Delay $\begin{array}{l} R_D = 1 \ M\Omega \\ \text{Leading} \\ \text{Trailing} \end{array}$                               | t <sub>D</sub>                       | -          | 200<br>170   | -<br>-     | ns   |

| $R_{D}=60~{ m k}\Omega$<br>Leading<br>Trailing                                                                                    |                                      | 50<br>32   | 90<br>72     | 130<br>130 |      |

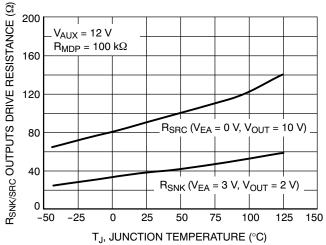

| Drive Resistance ( $V_{in}$ = 15 V)<br>Sink ( $V_{EA}$ = 0 V, $V_{OUT}$ = 2 V)<br>Source ( $V_{EA}$ = 3 V, $V_{OUT}$ = 10 V)      | R <sub>SNK</sub><br>R <sub>SRC</sub> | 20<br>50   | 40<br>90     | 80<br>170  | Ω    |

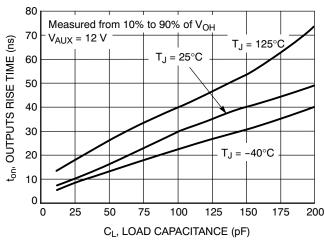

| Rise Time (C <sub>L</sub> = 100 pF, 10% to 90% of V <sub>OH</sub> )                                                               | t <sub>on</sub>                      | -          | 30           | -          | ns   |

| Fall Time (C <sub>L</sub> = 100 pF, 90% to 10% of V <sub>OH</sub> )                                                               | t <sub>off</sub>                     | _          | 12           | _          | ns   |

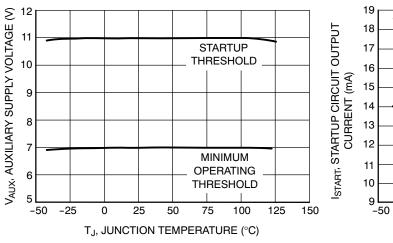

Figure 3. Auxiliary Supply Voltage Thresholds versus Junction Temperature

Figure 4. Startup Circuit Output Current versus Junction Temperature

Figure 5. Startup Circuit Output Current versus Auxiliary Supply Voltage

Figure 6. Startup Circuit Output Current versus Line Voltage

Figure 7. Startup Circuit Off-State Leakage Current versus Line Voltage

Figure 8. Auxiliary Supply Current versus Junction Temperature

4.0 3.5 V<sub>UV/OV</sub>, UV/OV VOLTAGE (V) **OV THRESHOLD** 3.0 2.5 2.0 1.5 **UV THRESHOLD** 1.0 0.5 -25 -50 25 50 75 100 125 150 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 9. Operating Auxiliary Supply Current versus Junction Temperature

Figure 10. Line Under/Overvoltage Thresholds versus Junction Temperature

Figure 11. Line Under/Overvoltage Thresholds Hysteresis versus Junction Temperature

Figure 12. Current Limit Thresholds versus

Junction Temperature

Figure 13. Current Limit Propagation Delay versus Junction Temperature

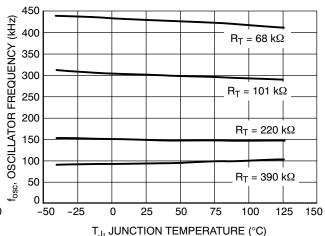

Figure 14. Oscillator Frequency versus Junction Temperature

Figure 15. Oscillator Frequency versus Junction Temperature

Figure 16. Oscillator Frequency versus

Timing Resistor

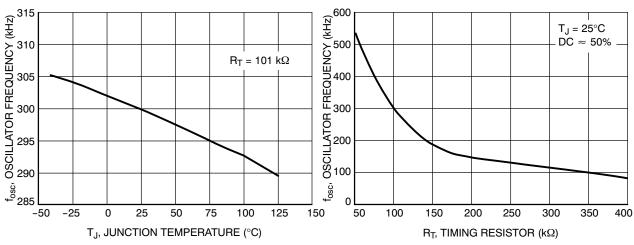

Figure 17. Feedforward Internal Resistance versus Junction Temperature

Figure 18. Maximum Duty Cycle versus Feedforward Current

Figure 19. Maximum Duty Cycle versus Junction Temperature

Figure 20. Soft-Start Charge/Discharge Currents versus Junction Temperature

Figure 21. V<sub>EA</sub> Input Resistance versus Junction Temperature

Figure 22. PWM Comparator Lower Input Threshold versus Junction Temperature

Figure 23. Reference Voltage versus Junction Temperature

Figure 24. Outputs Overlap Delay versus Junction Temperature

Figure 25. Outputs Overlap Delay versus Delay Resistor

Figure 26. Outputs Drive Resistance Voltage versus Junction Temperature

# **TYPICAL CHARACTERISTICS**

35 Measured from 90% to 10% of VOH 30  $V_{AUX} = 12 V$ OUTPUTS FALL TIME (ns)  $T_J = 125^{\circ}C$ 25 20  $T_J = 25^{\circ}C$ 15 10  $T_J = -40^{\circ}C$ ġ. 5 0 75 100 125 150 175 200 CI, LOAD CAPACITANCE (pF)

Figure 27. Outputs Rise Time versus Load Capacitance

Figure 28. Outputs Fall Time versus Load Capacitance

# **DETAILED OPERATING DESCRIPTION**

#### Introduction

An NCP1280 based system offers significant efficiency improvements and system cost savings over a converter using a traditional forward topology. The NCP1280 provides two control outputs. OUT1 controls the primary switch of a forward converter. OUT2 has an adjustable overlap delay, which can be used to control an active clamp/reset switch or any other complementary drive topology, such as an asymmetric half-bridge. In addition, OUT2 can be used to control a synchronous rectifier topology, eliminating the need of external control circuitry. Other distinctive features include: two mode overcurrent protection, line under/overvoltage detectors, fast line feedforward, soft-start and a maximum duty cycle limit. The Functional Block Diagram is shown in Figure 2.

The features included in the NCP1280 provide some of the advantages of Current-Mode Control, such as fast line feedforward, and cycle by cycle current limit. It eliminates the disadvantages of low power jitter, slope compensation and noise susceptibility.

# **Active Clamp Topology**

The transformer reset voltage in a traditional forward converter is set by the turns ratio and input voltage. Where as the reset voltage of an active clamp topology is constant over the converter off time and only depends on the input voltage and duty cycle. This translates into a lower voltage stress on the main switch, allowing the use of lower voltage MOSFETs. In general, lower voltage MOSFETs have lower cost and ON resistance. Therefore, lower system cost and higher efficiency can be achieved. In addition, the lower voltage stress allows the converter to operate at a higher duty cycle for a given primary switch voltage stress. This allows a reduction in primary peak current and secondary side voltage stress as well as smaller secondary inductor size.

# **High Voltage Startup Regulator**

The NCP1280 contains an internal 700 V startup regulator that eliminates the need for external startup components. In addition, this regulator increases the efficiency of the supply as it uses no power when in the normal mode of operation, but instead uses power supplied by an auxiliary winding.

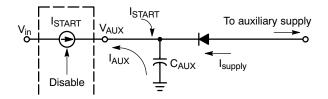

The startup regulator consists of a constant current source that supplies current from the input line voltage (Vin) to the capacitor on the V<sub>AUX</sub> pin (C<sub>AUX</sub>). The startup current is typically 13.8 mA. Once VAUX reaches 11 V, the startup regulator turns OFF and the outputs are enabled. When VAUX reaches 7 V, the outputs are disabled and the startup regulator turns ON. This "7-11" mode of operation is known as Dynamic Self Supply (DSS). The V<sub>AUX</sub> pin can be biased externally above 7 V once the outputs are enabled to prevent the startup regulator from turning ON. It is recommended to bias the V<sub>AUX</sub> pin using an auxiliary supply generated by an auxiliary winding from the power transformer. An independent voltage supply can also be used. If using an independent voltage supply and VAUX is biased before the outputs are enabled or while a fault is present, the One Shot Pulse Generator (Figure 2) will not be enabled and the outputs will remain OFF.

As the DSS sources current to the  $V_{AUX}$  pin, a diode should be placed between  $C_{AUX}$  and the auxiliary supply as shown in Figure 29. This will allow the NCP1280 to charge  $C_{AUX}$  while preventing the startup regulator from sourcing current into the auxiliary supply.

Figure 29. Recommended VAUX Configuration

Power to the controller while operating in the self-bias or DSS mode is provided by  $C_{AUX}$ . Therefore,  $C_{AUX}$  must be sized such that a  $V_{AUX}$  voltage greater than 7 V is maintained while the outputs are switching and the converter reaches regulation. Also, the  $V_{AUX}$  discharge time (from 11 V to 7 V) must be greater that the soft-start charge period to assure the converter turns ON.

The startup circuit is rated at a maximum voltage of 700 V. If the device operates in the DSS mode, power dissipation should be controlled to avoid exceeding the maximum power dissipation of the controller.

# Line Under/Overvoltage Shutdown

The NCP1280 incorporates line undervoltage and overvoltage shutdown (UV/OV) circuits. The under voltage (UV) threshold is 1.52 V and the overvoltage threshold (OV) is 3.61 V, for a ratio of 1:2.4. If the input voltage range exceeds the pre-set OV threshold, the OV function can be disabled by connecting a Zener from this pin to ground. The Zener voltage should be less than 3.6 V.

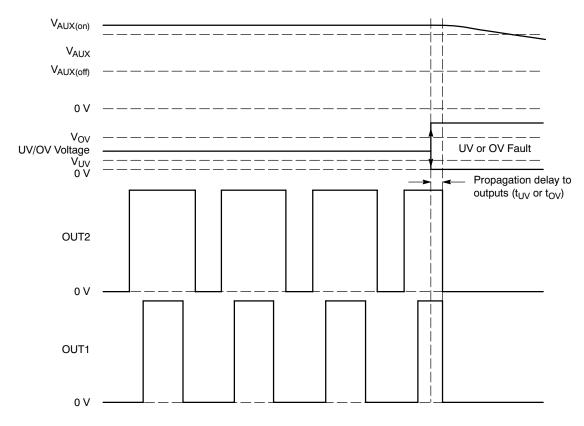

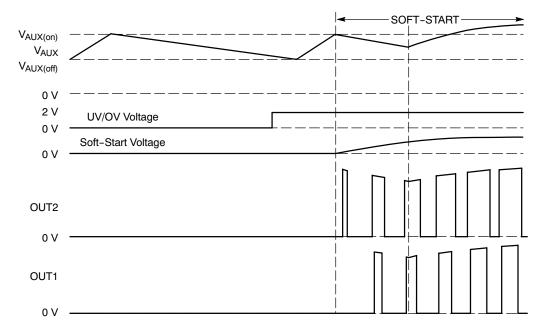

The UV/OV circuit can be biased using an external resistor divider from the input line. The resistor divider must be sized to enable the controller once  $V_{\rm in}$  is within the required operating range. If the UV or OV threshold is reached, the soft-start capacitor is discharged, and the outputs are immediately disabled with no overlap delay as shown in Figure 30. Also, if an UV condition is detected, the 5.0 V Reference Supply is disabled.

Figure 30. UV/OV Fault Timing Diagram

Once the UV or OV condition is removed and  $V_{AUX}$  reaches 11 V, the controller initiates a soft-start cycle. Figure 31 shows the relationship between the UV/OV voltage, the outputs and the soft-start voltage.

The UV/OV pin can also be used to implement a remote enable/disable function. Biasing the UV/OV pin below its UV threshold disables the converter.

Figure 31. Soft-Start Timing Diagram (Using Auxiliary Winding)

# **Feedforward Ramp Generator**

The NCP1280 incorporates line feedforward (FF) to compensate for changes in line voltage. A FF Ramp proportional to  $V_{in}$  is generated and compared to  $V_{EA}$ . If the line voltage changes, the FF Ramp slope changes accordingly. The duty cycle will be adjusted immediately instead of waiting for the line voltage change to propagate around the system and be reflected back on  $V_{EA}$ .

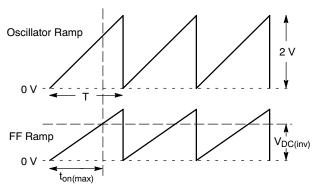

A resistor between  $V_{in}$  and the FF pin  $(R_{FF})$  sets the feedforward current  $(I_{FF})$ . The FF Ramp is generated by charging an internal 10 pF capacitor  $(C_{FF})$  with a constant current proportional to  $I_{FF}$ . The FF Ramp is finished (capacitor is discharged) once the Oscillator Ramp reaches 2.0 V. Please refer to Figure 2 for a functional drawing of the Feedforward Ramp generator.

$I_{\rm FF}$  is usually a few hundred microamps, depending on the operating frequency and the required duty cycle. If the operating frequency and maximum duty cycle are known,  $I_{\rm FF}$  is calculated using the equation below:

$$I_{FF} = \frac{C_{FF} \times V_{DC(inv)} \times 125 \text{ k}\Omega}{6.7 \text{ k}\Omega \times t_{on(max)}}$$

where  $V_{DC(inv)}$  is the voltage on the inverting input of the Max DC Comparator and  $t_{on(max)}$  is the maximum ON time.

Figure 18 shows the relationship between  $I_{FF}$  and  $DC_{MAX}$ . For example, if a system is designed to operate at 200 kHz, with a 60% maximum duty cycle at 100 V, the  $DC_{MAX}$  pin can be grounded and  $I_{FF}$  is calculated as follows:

$$\begin{split} T &= \frac{1}{f} = \frac{1}{200 \text{ kHz}} = 5.0 \text{ } \mu\text{s} \\ t_{ON(max)} &= DC_{MAX} \times T = 0.6 \times 5.0 \text{ } \mu\text{s} = 3.0 \text{ } \mu\text{s} \\ I_{FF} &= \frac{C_{FF} \times V_{DC(inv)} \times 125 \text{ } k\Omega}{6.7 \text{ } k\Omega \times t_{ON(max)}} \\ &= \frac{10 \text{ } pF \times 0.888 \text{ } V \times 125 \text{ } k\Omega}{6.7 \text{ } k\Omega \times 3.0 \text{ } \mu\text{s}} = 55.2 \text{ } \mu\text{A} \end{split}$$

For a minimum line voltage of 100 V, the required feedforward resistor is calculated using the equation below:

$$\mathsf{RFF} = \frac{\mathsf{V_{in}}}{\mathsf{IFF}} - 12.0 \; \mathsf{k}\Omega = \frac{100 \; \mathsf{V}}{\mathsf{55.2 \; \mathsf{uA}}} - 12.0 \; \mathsf{k}\Omega \approx 1.82 \; \mathsf{M}\Omega$$

From the above calculations it can be observed that  $I_{FF}$  is controlled predominantly by the value of  $R_{FF}$ , as the resistance seen into the FF pin is only 12 k $\Omega$ . If a tight maximum duty cycle control overtemperature is required,  $R_{FF}$  should have a low thermal coefficient.

#### **Current Limit**

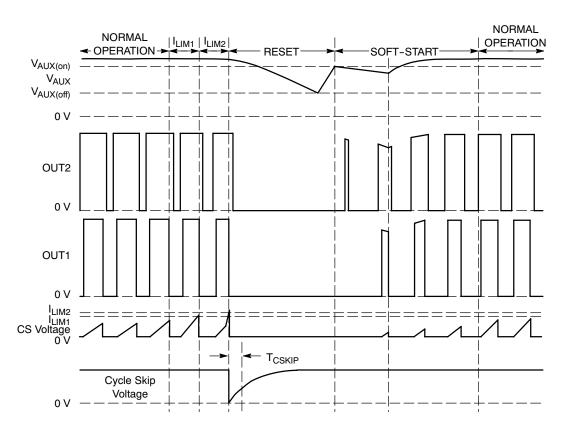

The NCP1280 has two overcurrent protection modes, cycle by cycle and cycle skip. It allows the NCP1280 to handle momentary and hard shorts differently for the best tradeoff in performance and safety. The outputs are disabled typically 90 ns after a current limit fault is detected.

The cycle by cycle mode terminates the conduction cycle (reducing the duty cycle) if the voltage on the CS pin exceeds 0.48 V. If the voltage on the CS pin exceeds 0.57 V, the converter enters the cycle skip (CSKIP) mode. While in the CSKIP mode, the soft-start capacitor is discharged and the converter is disabled by a time determined by the CSKIP timer.

The CSKIP timer is set by immediately discharging the capacitor on the CSKIP pin ( $C_{CSKIP}$ ), and then charging it with a constant current source of 12.3  $\mu$ A. The cycle skip period ends when the voltage on the cycle skip capacitor reaches 2.0 V. The cycle skip capacitor is calculated using the equation below:

$$C_{\mbox{CSKIP}} \approx \frac{T_{\mbox{CSKIP}} \times 12.3 \ \mu\mbox{A}}{2 \ \mbox{V}} \label{eq:CSKIP}$$

Using the above equation, a cycle skip period of  $11.0 \,\mu s$  requires a cycle skip capacitor of  $68 \, pF$ . The differences between the cycle by cycle and cycle skip modes are observed in Figure 32.

Figure 32. Overcurrent Faults Timing Diagram

Once the cycle skip period is complete and  $V_{AUX}$  reaches 11 V, a soft-start sequence commences. The possible minimum OFF time is set by  $C_{CSKIP}$ . However, the actual OFF time is generally greater than  $C_{CSKIP}$  because it is the cycle skip period added to the time it takes  $V_{AUX}$  to reach 11 V.

# Oscillator

The NCP1280 oscillator frequency is set by a single external resistor connected between the  $R_{T}$  pin and GND. The oscillator is designed to operate up to 500 kHz.

The voltage on the  $R_T$  pin is laser trim adjusted during manufacturing to 1.3 V for an  $R_T$  of 101 k $\Omega$ . A current set by  $R_T$  generates an Oscillator Ramp by charging an internal 10 pF capacitor as shown in Figure 2. The period ends (capacitor is discharged) once the Oscillator Ramp reaches 2.0 V. If  $R_T$  increases, the current and the Oscillator Ramp slope decrease, thus reducing the frequency. If  $R_T$  decreases, the opposite effect is obtained. Figure 16 shows the relationship between  $R_T$  and the oscillator frequency.

# **Maximum Duty Cycle**

A dedicated internal comparator limits the maximum ON time of OUT1 by comparing the FF Ramp to  $V_{DC(inv)}$ . If the FF Ramp voltage exceeds  $V_{DC(inv)}$ , the output of the Max DC Comparator goes high. This will reset the Output Latch, thus turning OFF the outputs and limiting the duty cycle.

Duty cycle is defined as:

$$DC = \frac{t_{OI}}{T} = t_{OI} \times f$$

Therefore, the maximum ON time can be set to yield the desired DC if the operating frequency is known. The maximum ON time is set by adjusting the FF Ramp to reach  $V_{DC(inv)}$  in a time equal to  $t_{on(max)}$  as shown in Figure 33. The maximum ON time should be set for the minimum line voltage. As line voltage increases, the slope of the FF Ramp increases. This reduces the duty cycle below  $DC_{MAX}$ , which is a desirable feature as the duty cycle is inversely proportional to line voltage.

Figure 33. Maximum ON Time Limit Waveforms

An internal resistor divider from a 2.0 V reference is used to set  $V_{DC(inv)}$ . If the  $DC_{MAX}$  pin is grounded,  $V_{DC(inv)}$  is 0.88 V. If the pin is floating,  $V_{DC(inv)}$  is 1.19 V. This is equivalent to 60% or 80% of a 1.5 V FF Ramp.  $V_{DC(inv)}$  can be adjusted to other values by using an external resistor network on the  $DC_{MAX}$  pin. For example, if the minimum line voltage is 100 V,  $R_{FF}$  is 1.82 M $\Omega$ , operating frequency is 200 kHz and a maximum duty cycle of 70% is required,  $V_{DC(inv)}$  is calculated as follows:

$$V_{DC(inv)} = \frac{I_{FF} \times 6.7 \text{ k}\Omega \times t_{on(max)}}{C_{FF} \times 125 \text{ k}\Omega}$$

$$V_{DC(inv)} = \frac{55.2 \ \mu A \times 6.7 \ k\Omega \times 3.5 \ \mu s}{10 \ pF \times 125 \ k\Omega} = 1.04 \ V$$

This can be achieved by connecting a 19.6  $k\Omega$  resistor from the  $DC_{MAX}$  pin to GND. The maximum duty cycle limit can be disabled connecting a 100  $k\Omega$  resistor between the  $DC_{MAX}$  and  $V_{REF}$  pins.

#### 5.0 V Reference

The NCP1280 includes a precision 5.0 V reference output. The reference output is biased directly from  $V_{AUX}$  and it can supply up to 6 mA. Load regulation is 50 mV and line regulation is 100 mV over the complete operating range.

It is recommended to bypass the reference output with a  $0.1~\mu F$  ceramic capacitor. The reference output is disabled when an UV fault is present.

# **PWM Comparator**

In steady state operation, the PWM comparator adjusts the duty cycle by comparing the error signal to the FF Ramp. The error signal is fed into the  $V_{EA}$  input. The  $V_{EA}$  input can be driven directly with an optocoupler and a pullup resistor from  $V_{REF}$ . The drive of the  $V_{EA}$  pin is simplified by internally incorporating a series diode and resistor. The series diode provides a 0.7 V offset between  $V_{EA}$  input and the PWM comparator inverting input. The outputs are enabled if the  $V_{EA}$  voltage is approximately 0.7 above the valley voltage of the FF Ramp.

The pullup resistor is selected such that in the absence of the error signal, the voltage on the  $V_{EA}$  pin exceeds the peak amplitude of the FF Ramp. Otherwise, the converter will not be able to reach maximum duty cycle. The  $V_{EA}$  range required to control the DC from 0% to DC<sub>MAX</sub> is given by the equation below:

$$V_{EA(L)} < V_{EA} < \left(\frac{IFF \times DC}{186.56 \text{ pf} \times f} + V_{EA(L)}\right)$$

where,  $V_{EA(L)}$  is the PWM comparator lower input threshold.

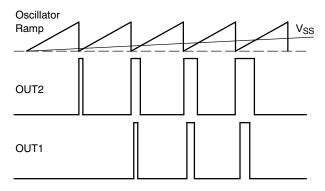

# Soft-Start

Soft-start (SS) allows the converter to gradually reach steady state operation, thus reducing startup stress and surges on the system. The duty cycle is limited during a soft-start sequence by comparing the Oscillator Ramp to the SS voltage ( $V_{SS}$ ) by means of the Soft-Start Comparator.

A 6.2  $\mu A$  current source starts to charge the capacitor on the SS pin once faults are removed and  $V_{AUX}$  reaches 11 V. The Soft–Start Comparator controls the duty cycle while the SS voltage is below 2.0 V. Once  $V_{SS}$  reaches 2.0 V, it exceeds the Oscillator Ramp voltage and the Soft–Start Comparator does not limit the duty cycle. Figure 34 shows the relationship between the outputs duty cycle and the soft–start voltage.

Figure 34. Soft-Start Timing Diagram

If the soft-start period is too long,  $V_{AUX}$  will discharge to 7 V before the converter output is completely in regulation causing the outputs to be disabled. If the converter output is not completely discharged when the outputs are re-enabled, the converter will eventually reach regulation exhibiting a non-monotonic startup behavior. But, if the converter output is completely discharged when the outputs are re-enabled, the cycle may repeat and the converter will not start.

In the event of an UV, OV, or cycle skip fault, the soft-start capacitor is discharged. Once the fault is removed, a soft-start cycle commences. The soft-start steady state voltage is approximately 4.1 V.

# **Control Outputs**

The NCP1280 has two in-phase control outputs, OUT1 and OUT2, with adjustable overlap delay ( $t_D$ ). OUT2 precedes OUT1 during a low to high transition and OUT1 precedes OUT2 at any high to low transition. Figure 35 shows the relationship between OUT1 and OUT2.

Figure 35. Control Outputs Timing Diagram

Generally, OUT1 controls the main switching element. Output 2, once inverted, can control a synchronous rectifier. The overlap delay prevents simultaneous conduction. Output 2 can also be used to control an active clamp reset.

Once  $V_{AUX}$  reaches 11 V, the internal startup circuit is disabled and the One Shot Pulse Generator is enabled. If no faults are present, the outputs turn ON. Otherwise, the outputs remain OFF until the fault is removed and  $V_{AUX}$  reaches 11 V again.

The control outputs are biased from  $V_{AUX}$ . The outputs can supply up to 10 mA each and their high state voltage is usually 0.2 V below  $V_{AUX}$ . Therefore, the auxiliary supply voltage should not exceed the maximum input voltage of the driver stage.

If the control outputs need to drive a large capacitive load, a driver should be used between the NCP1280 and the load. ON Semiconductor's MC33152 is a good selection for an integrated driver. Figures 27 and 28 shows the relationship between the output's rise and fall times vs capacitive load.

# **Time Delay**

The overlap delay between the outputs is set connecting a resistor ( $R_D$ ) between the  $t_D$  and  $V_{REF}$  pins. A minimum overlap delay of 80 ns is obtained when  $R_D$  is 60 k $\Omega$ . If  $R_D$  is not present, the delay is 200 ns.

The output duty cycle can be adjusted from 0% to 85% selecting appropriate values of  $R_{FF}$  and  $V_{DC(inv)}$ . It should be noted that the overlap delay may cause OUT2 to reach 100% duty cycle. Therefore, if OUT2 is used, the maximum duty cycle of OUT2 needs to be kept below 100%. The maximum overlap delay,  $t_{D(max)}$ , depends on the maximum duty cycle and frequency of operation. The maximum overlap delay is calculated using the equation below.

$$t_{D(max)} \leq \frac{(1 - DC)}{2f}$$

For example, if the converter operates at a frequency of 300 kHz with a maximum duty cycle of 80%, the maximum allowed overlap delay is 333 ns. However, this is a theoretical limit and variations over the complete operating range should be considered when selecting the overlap delay.

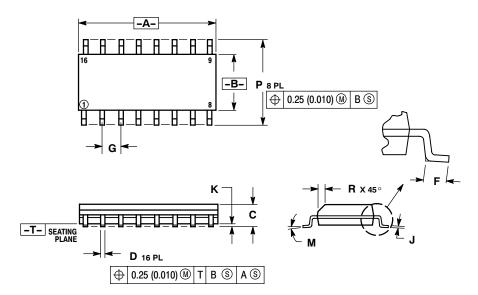

# PACKAGE DIMENSIONS

SO-16 **D SUFFIX** CASE 751B-05 ISSUE J

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN   | IETERS | INCHES |       |  |

|-----|----------|--------|--------|-------|--|

| DIM | MIN      | MAX    | MIN    | MAX   |  |

| Α   | 9.80     | 10.00  | 0.386  | 0.393 |  |

| В   | 3.80     | 4.00   | 0.150  | 0.157 |  |

| С   | 1.35     | 1.75   | 0.054  | 0.068 |  |

| D   | 0.35     | 0.49   | 0.014  | 0.019 |  |

| F   | 0.40     | 1.25   | 0.016  | 0.049 |  |

| G   | 1.27 BSC |        | 0.050  | BSC   |  |

| J   | 0.19     | 0.25   | 0.008  | 0.009 |  |

| K   | 0.10     | 0.25   | 0.004  | 0.009 |  |

| M   | 0°       | 7°     | 0°     | 7°    |  |

| P   | 5.80     | 6.20   | 0.229  | 0.244 |  |

| R   | 0.25     | 0.50   | 0.010  | 0.019 |  |

The product described herein (NCP1280) may be covered by one or more U.S. patents. There may be other patents pending.

ON Semiconductor and were registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 61312, Phoenix, Arizona 85082-1312 USA

Phone: 480-829-7710 or 800-344-3860 Toll Free USA/Canada

Fax: 480-829-7709 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81-3-5773-3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.