Data brief

# Demonstration board for STDRIVEG600 600V high speed half-bridge gate driver with enhancement mode GaN HEMT

#### **Features**

- Half-Bridge topology featuring 600V STDRIVEG600 gate driver

- Equipped with 150 mΩ 650V HEMT GaN

- GaN in 5x6mm PowerFLAT package with Kelvin source

- HV bus up to 500 V

- 4.75 to 6.5 V VCC gate driver supply voltage, limited by GaN V<sub>GS</sub> rating

- On-board adjustable deadtime generator to convert single PWM signal in independent High-Side and Low-Side deadtimes

- · Separated inputs with external deadtime can also be used

- On-board 3.3V regulator for external circuitry supply

- 25°C/W junction-to-ambient thermal resistance to evaluate large power topologies

- · High frequency connector for gate GaN power transistor monitoring

- · Optional low-side shunt

- · RoHS compliant.

### **Description**

The STDRIVEG600 is a high-speed half-bridge gate driver optimized to drive high-voltage enhanced mode GaN HEMTs. It features an integrated bootstrap diode and allows supplying external switches up to 20 V, with undervoltage protection tailored for GaN HEMTs.

The EVSTDRIVEG600DG board is easy to use and quick and adapt for evaluating the characteristics of STDRIVEG600 driving 650 V e-Mode GaN switches.

It provides an on-board programmable dead time generator and a 3.3 V linear voltage regulator to supply external logic controllers like microcontrollers.

Spare footprints are also included to allow customizing the board for the final application, such as separate input signal or single PWM signal, use of optional external bootstrap diode, separate supply for VCC, PVCC or BOOT and the use of low-side shunt resistor for peak current mode topologies.

The EVSTDRIVEG600DG is 50 x 70 mm wide, FR-4 PCB resulting in 25 °C/W  $R_{\text{th(J-A)}}$  in still air.

#### Product status link

**EVSTDRIVEG600DG**

## 1 Safety and operating instructions

#### 1.1 General terms

#### Warning:

During assembly, testing, and operation, the evaluation board poses several inherent hazards, including bare wires, moving or rotating parts and hot surfaces

#### Danger:

There is danger of serious personal injury, property damage or death due to electrical shock and burn hazards if the kit or components are improperly used or installed incorrectly.

The kit is not electrically isolated from the high-voltage supply DC input. No insulation is ensured between the accessible parts and the high voltage. All measuring equipment must use adequately insulated probes, clamps and connecting wires. Never touch the evaluation board while it is energized as it is capable of causing electrical shock hazard.

All operations involving transportation, installation and use, and maintenance must be performed by skilled technical personnel able to understand and implement national accident prevention regulations. For the purposes of these basic safety instructions, "skilled technical personnel" are suitably qualified people who are familiar with the installation, use and maintenance of power electronic systems.

### 1.2 Intended use of demonstration board

The board is designed for demonstration purposes only, and must not be used for electrical installations or machinery. Technical data and information concerning the power supply conditions are detailed in the documentation and should be strictly observed.

### 1.3 Installing the demonstration board

- The installation and cooling of the demonstration board must be in accordance with the specifications and target application.

- The board must be protected against excessive strain. In particular, components should not be bent or isolating distances altered during transportation or handling.

- No contact must be made with other electronic components and contacts.

- The board contains electrostatically-sensitive components that are prone to damage if used incorrectly. Do

not mechanically damage or destroy the electrical components (potential health risks).

DB4464 - Rev 2 page 2/17

#### 1.4 Operating the demonstration board

To operate properly the board, follow these safety rules.

- 1. Work Area Safety:

- The work area must be clean and tidy.

- Do not work alone when boards are energized.

- Protect against inadvertent access to the area where the board is energized using suitable barriers and signs.

- A system architecture that supplies power to the evaluation board must be equipped with additional control and protective devices in accordance with the applicable safety requirements (i.e., compliance with technical equipment and accident prevention rules).

- Use non-conductive and stable work surface.

- Use adequately insulated clamps and wires to attach measurement probes and instruments.

#### 2. Electrical Safety:

- Remove power supply from the board and electrical loads before performing any electrical measurement.

- Proceed with the arrangement of measurement setup, wiring or configuration paying attention to high voltage sections.

- Once the setup is complete, energize the board.

#### Danger:

Do not touch the board when it is energized or immediately after it has been disconnected from the voltage supply as several parts and power terminals containing potentially energized capacitors need time to discharge.

Do not touch the boards after disconnection from the voltage supply as several parts, included PCB, may still be very hot.

The kit is not electrically isolated from DC input.

#### 3. Personal Safety

- Always wear suitable personal protective equipment such as, for example, insulating gloves and safety glasses.

- Take adequate precautions and install the board in such a way to prevent accidental touch. Use

protective shields such as, for example, insulating box with interlocks if necessary.

DB4464 - Rev 2 page 3/17

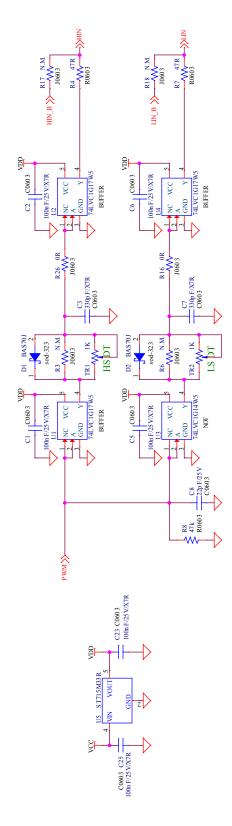

# 2 Schematic diagrams

Figure 1. EVSTDRIVEG600DG schematic - STDRIVEG600 driver, power stage and connectors 9 <del>-</del><del>aa</del>-D4 P LVA 662 A PGND D5 N.M. PLVA662A C14 N.M. C0402 C18 N.M. C0402 R0402 R10 50R R0402 R12 50R R0402 C13 = 47n/F25V/X7R C0402 HON 10R A Z COCO Z C15 4.7uF/50V

DB4464 - Rev 2 page 4/17

Figure 2. EVSTDRIVEG600DG schematic - Deadtime generator

DB4464 - Rev 2 page 5/17

### 3 Board power-up and input connection

The following picture shows how to supply the EVSTDRIVEG600DG, how to provide LIN and HIN inputs and set the programmable deadtime generator.

TR2: Low-side J4 & J6: Half bridge deadtime generator high voltage supply J4: HV BUS Single signal input for deadtime generator Direct LIN & HIN inputs J5: OUT, Half-bridge middle point (see Table 2) J2: Driver supply and inputs connector J6: POWER GROUND TR1: High-side deadtime generator GND VCC J1: 6V gate driver supply

Figure 3. EVSTDRIVEG600DG - Supply and signal connection

The LIN, HIN inputs can be provided form the on-board deadtime generator or directly from an external generator or control device (as DSP/MCU).

The deadtime value set by the on-board dead time generator, fed by PWM input signal on J2, can be tuned by setting TR1 and TR2. The typical dead time value with the trimmer in the default manufacturing middle position is about 100 ns. It is possible to change dead time generator range by changing C3 and C7.

TR2 sets the deadtime before low side turn-on.

TR1 sets the deadtime before high side turn-on.

**Table 1. Connector Map**

| Ref | Pin#  | Name      | Function               | Description                                                                                                                    |

|-----|-------|-----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| J2  | 1     | VCC       | INPUT power            | Board Supply voltage (recommended value 6 V)                                                                                   |

|     | 2     | VDD (3V3) | OUT power              | Output voltage of on-board 3.3 V regulator: it can be used to supply external circuitry (up to about 50 mA)                    |

|     | 3     | GND       | PWR                    | Board reference potential                                                                                                      |

|     | 4     | HIN_B     | INPUT digital          | HIN direct input signal (0 to 3.3 V or up to 20 V): mount R17 and remove R4 - see Table 2 and Table 3                          |

|     | 5     | LIN_B     | INPUT digital          | LIN direct input signal (0 to 3.3 V or up to 20 V): mount R18 and remove R7 - see Table 2 and Table 3                          |

|     | 6     | GND       | PWR                    | Board reference potential                                                                                                      |

|     | 7     | PWM       | INPUT digital          | PWM input signal (0 to 3.3 V or 5 V) – see Table 2 and Table 3                                                                 |

|     | 8     | SD_IN     | INPUT / OUT<br>digital | Disable input signal (0 to 3.3 V or up to 20 V) – see Table 3  Open-drain output signals over-temperature protection           |

|     | 9     | GND       | PWR                    | Board reference potential                                                                                                      |

| J4  | 1,2,3 | HV        | INPUT Power            | These three pins are connected to high voltage (HV) of GaN power stage.  Connect the half bridge high voltage positive supply. |

DB4464 - Rev 2 page 6/17

| Ref | Pin#  | Name      | Function     | Description                                                                                                                                                                                          |

|-----|-------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J5  | 1,2,3 | OUT       | OUTPUT Power | These three pins are connected to OUT pin of power stage: connect the load to this terminal                                                                                                          |

| J6  | 1,2,3 | GND_POWER | PWR          | These three pins are connected to power ground.                                                                                                                                                      |

|     | ' '   |           |              | Connect the half bridge high voltage negative supply.                                                                                                                                                |

| J12 | 1     | VCC       | INPUT Power  | Board driver supply voltage (recommended value 6 V)                                                                                                                                                  |

|     | 2     | GND       | POWER        | Board reference potential                                                                                                                                                                            |

| CN1 |       | GH        | OUTPUT       | To be used to monitor the gate of high-side GaN power transistor (GH) with high bandwidth, high voltage differential probes (optically isolated probes with MMCX connector are strongly recommended) |

| CN2 |       | GL        | OUTPUT       | To be used to monitor the gate of low-side GaN power transistor (GL). Recommended to be used with high bandwidth differential probes (optically isolated) with proper MMCX male connector.           |

Table 2. Device input selection

| R4, R7          | R17, R18 | Input source      | Function and description                                                                          |

|-----------------|----------|-------------------|---------------------------------------------------------------------------------------------------|

| 0-47 Ω (closed) | Open     | J2: PWM pin       | LIN & HIN are generated by the on-board deadtime generator from a single PWM signal on J2, pin 7. |

| Open            | 0-47 Ω   | J2: LIN_B & HIN_B | Direct connection to LIN and HIN STDRIVEG600 pins.                                                |

| Open            | (closed) | pins              | LIN, HIN input range: up to 20 V.                                                                 |

Table 3. Input signal truth table

| SD/OD | PWM | LIN | HIN |

|-------|-----|-----|-----|

| L     | X   | L   | L   |

| Н     | L   | Н   | L   |

| Н     | Н   | L   | Н   |

The recommended power-on sequence is to turn VCC on first, then apply the HV bus voltage. The recommended power-off sequence is to turn-off the HV bus supply first, then VCC.

DB4464 - Rev 2 page 7/17

# 4 Bill of materials

Table 4. EVSTDRIVEG600DG bill of materials

| Reference                | Description                                                           | Value or Generic Part Number Package |

|--------------------------|-----------------------------------------------------------------------|--------------------------------------|

| CN1                      | MMCX Straight Receptacle                                              | Cinch 135-3701-201 or equivalent     |

| CN2                      | MMCX Straight Receptacle                                              | N.M.                                 |

| C1, C2, C5, C6, C23, C25 | SMT ceramic capacitor                                                 | 100 nF / 25 V / X7R, 0603            |

| C3, C7                   | SMT ceramic capacitor                                                 | 330 pF / X7R, 0603                   |

| C8, C20, C22             | SMT ceramic capacitor                                                 | 22 pF / 25 V, 0603                   |

| C10, C12                 | SMT ceramic capacitor                                                 | 1 μF / 25 V / X5R, 0805              |

| C13, C16, C17            | SMT ceramic capacitor                                                 | 47 nF / 25 V / X7R, 0402             |

| C14, C18                 | SMT ceramic capacitor                                                 | N.M., 0402                           |

| C15                      | SMT ceramic capacitor                                                 | 4.7 μF / 25 V / X7R, 0805            |

| C19                      | SMT ceramic capacitor                                                 | 1 nF / 25 V, 0603                    |

| C21                      | SMT ceramic capacitor                                                 | 1 μF / 10 V / X7R, 0603              |

| C24                      | SMT ceramic capacitor                                                 | 470 nF / 630 V / X7R, 2225           |

| D1, D2                   | Low capacitance, low series inductance and resistance Schottky diodes | BAS70JFILM, SOD-323                  |

| D3                       | Fast Rectifier                                                        | N.M., TUMD2SM                        |

| D3A                      | Fast Rectifier                                                        | N.M., SMA                            |

| D4                       | 6.2 V Low-voltage avalanche regulator diodes                          | PLVA662A, SOT23                      |

| D5                       | 6.2 V Low-voltage avalanche regulator diodes                          | N.M., SOT23                          |

| JP1, JP2                 | SMT jumper                                                            | OPEN, Soldering pads                 |

| J1                       | Terminal block T.H. 2 pos, 5.08 mm                                    | 2 Poles, Pitch 5.08 mm               |

| J2                       | Strip connector 9 pos, 2.54 mm                                        | STRIP 1x9                            |

| J3                       | Strip connector 4 pos, 2.54 mm                                        | N.M.                                 |

| J4, J5, J6, J8           | Strip connector 3 pos, 2.54 mm                                        | STRIP 1x3                            |

| J7                       | Strip connector 2 pos, 2.54 mm                                        | STRIP 1x2                            |

| Q1, Q2                   | Bottom-side cooled 650 V E-mode GaN transistor                        | GS-065-011-1-L, 5x6 mm               |

| Q3                       | NPN General Purposes Transistor                                       | N.M., SOT23                          |

| R1, R2                   | SMT resistor                                                          | 0 Ω, 0402                            |

| R3, R6, R17, R18         | SMT resistor                                                          | N.M., 0603                           |

| R4, R7                   | SMT resistor                                                          | 47 Ω, 0603                           |

| R8                       | SMT resistor                                                          | 47 kΩ, 0603                          |

| R9                       | SMT resistor                                                          | N.M., 0603                           |

| R10, R12                 | SMT resistor                                                          | 50 Ω, 0402                           |

| R11, R13                 | SMT resistor                                                          | 1 Ω, 0402                            |

| R14                      | SMT resistor                                                          | 10 kΩ, 0603                          |

| R15                      | SMT resistor                                                          | 1 kΩ, 0603                           |

| R16, R26, R27, R28, R29  | SMT resistor                                                          | 0 Ω, 0603                            |

| R19, R20                 | SMT resistor                                                          | 10 ΜΩ, 1206                          |

DB4464 - Rev 2 page 8/17

| Reference                                                | Description                                                              | Value or Generic Part Number Package |

|----------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------|

| R21, R22, R23, R30                                       | SMT resistor                                                             | 0 Ω, 0805                            |

| R24                                                      | SMT resistor                                                             | 10 Ω, 0603                           |

| R25                                                      | SMT resistor                                                             | 10 Ω, 0805                           |

| TR1, TR2                                                 | 5 mm Square Surface Mount Miniature Trimmers<br>Multi-Turn Cermet Sealed | 1 kΩ, TSM4YJ                         |

| TP1, TP2, TP3, TP4, TP5, TP6, TP8, TP9, TP10, TP11, TP12 | Test point for probe                                                     | Metallized Hole, 0.8 mm diameter     |

| U1, U2, U4                                               | Single Schmitt-trigger buffer                                            | 74LVC1G17W5, SOT23-5L                |

| U3                                                       | Single Schmitt-trigger inverter                                          | 74LVC1G14W5, SOT23-5L                |

| U5                                                       | High input voltage, 85 mA LDO linear regulator                           | ST715M33R, SOT23-5L                  |

| U6                                                       | High voltage and high-speed half-bridge gate driver                      | STDRIVEG600, SO16                    |

DB4464 - Rev 2 page 9/17

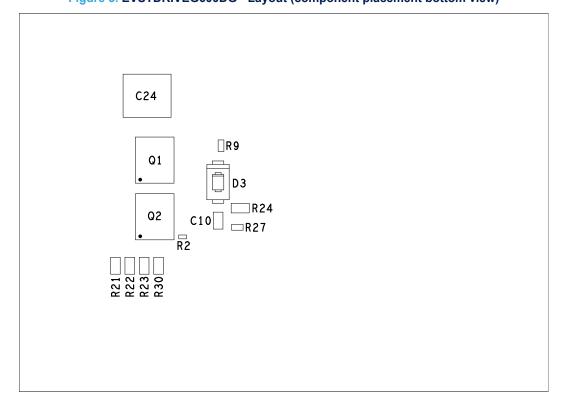

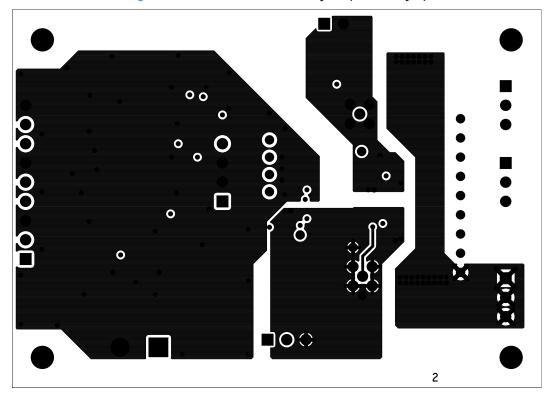

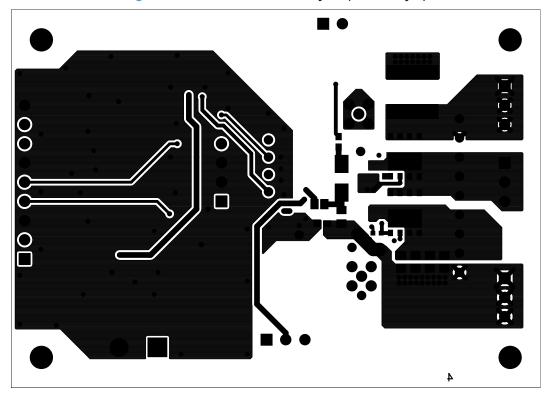

# 5 Layout and component placements

$\oplus$ CN1 0 TP1  $\mathsf{TP4}\,\bigcirc$ 0 TP110C13 TP6 🔾 0 R10 □ R1 TP3 0 R11 0C14 ∘ ]J5 TP2 TP5O □C16 □C17 □JP1 □R12 □R13 **□C18** TP8O TP90 TP10 CN2 TP12 J6 0 0 J8 °

Figure 4. EVSTDRIVEG600DG - Layout (component placement top view)

Figure 5. EVSTDRIVEG600DG - Layout (component placement bottom view)

DB4464 - Rev 2 page 10/17

Figure 6. EVSTDRIVEG600DG - Layout (top layer)

DB4464 - Rev 2 page 11/17

Figure 8. EVSTDRIVEG600DG - Layout (inner 3 layer)

DB4464 - Rev 2 page 12/17

# **Revision history**

**Table 5. Document revision history**

| Date        | Version | Changes                                                   |

|-------------|---------|-----------------------------------------------------------|

| 22-Jun-2021 | 1       | Initial release.                                          |

| 19-Oct-2021 | 2       | Changed cover image in Section ■ Cover image and Figure 3 |

DB4464 - Rev 2 page 13/17

# **Contents**

| 1                    | Safe                                 | Safety and operating instructions   |    |  |  |

|----------------------|--------------------------------------|-------------------------------------|----|--|--|

|                      | 1.1                                  | General terms                       | 2  |  |  |

|                      | 1.2                                  | Intended use of demonstration board | 2  |  |  |

|                      | 1.3                                  | Installing the demonstration board  | 2  |  |  |

|                      | 1.4                                  | Operating the demonstration board   | 3  |  |  |

| 2 Schematic diagrams |                                      | 4                                   |    |  |  |

| 3                    | Board power-up and input connection6 |                                     |    |  |  |

| 4                    | Bill of materials8                   |                                     |    |  |  |

| 5                    | Layout and component placements10    |                                     |    |  |  |

| Rev                  | /ision                               | history                             | 13 |  |  |

| Coi                  | ntents                               | \$                                  | 14 |  |  |

| Lis                  | t of ta                              | bles                                | 15 |  |  |

| Lis                  | t of fig                             | gures                               | 16 |  |  |

# **List of tables**

| Table 1. | Connector Map                     | 6 |

|----------|-----------------------------------|---|

|          | Device input selection            |   |

| Table 3. | Input signal truth table          | 7 |

|          | EVSTDRIVEG600DG bill of materials |   |

| Table 5. | Document revision history         | 3 |

DB4464 - Rev 2 page 15/17

# **List of figures**

| Figure 1. | EVSTDRIVEG600DG schematic - STDRIVEG600 driver, power stage and connectors | 4  |

|-----------|----------------------------------------------------------------------------|----|

| Figure 2. | EVSTDRIVEG600DG schematic - Deadtime generator                             | Ę  |

| Figure 3. | EVSTDRIVEG600DG - Supply and signal connection                             | 6  |

| Figure 4. | EVSTDRIVEG600DG - Layout (component placement top view)                    | 1( |

| Figure 5. | EVSTDRIVEG600DG - Layout (component placement bottom view)                 | 10 |

| Figure 6. | EVSTDRIVEG600DG - Layout (top layer)                                       | 11 |

| Figure 7. | EVSTDRIVEG600DG - Layout (inner 2 layer)                                   | 11 |

| Figure 8. | EVSTDRIVEG600DG – Layout (inner 3 layer)                                   | 12 |

| Figure 9. | EVSTDRIVEG600DG - Layout (bottom layer)                                    | 12 |

DB4464 - Rev 2 page 16/17

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DB4464 - Rev 2 page 17/17