### **MAX77857**

## **General Description**

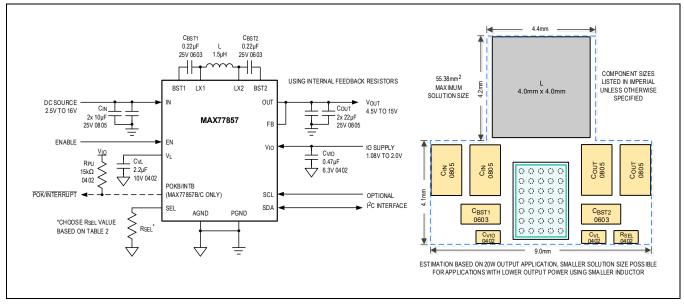

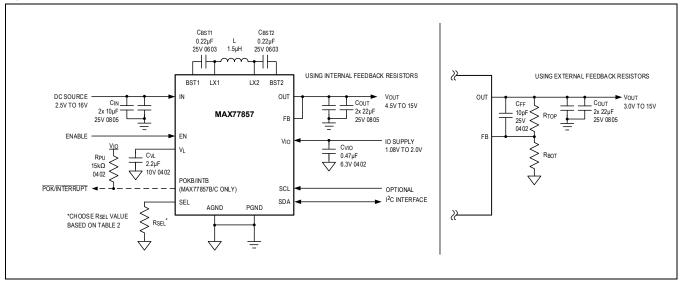

The MAX77857 is a high-efficiency, high-performance buck-boost converter targeted for systems requiring a wide input voltage range (2.5V to 16V). It features 7A switching current and can supply up to 6A output current in buck mode and up to 4A in boost mode (Boost Ratio  $\leq$  1.3). It operates in PWM mode and implements an automatic SKIP mode to improve light-load efficiency.

The default output voltage is 5V when using internal feedback resistors. It can also be configured to any default output voltages between 3V and 15V when using external feedback resistors. The output voltage is adjustable dynamically through the I<sup>2</sup>C serial interface (see the <u>Output Voltage Configuration</u> section).

The SEL pin allows a single external resistor to program four different I<sup>2</sup>C interface slave addresses, four different switching current limit thresholds, and selection between external/internal feedback resistors. The different switching current limit thresholds allow the use of lower profile and smaller external components that are optimized for a particular application. The use of external feedback resistors allows for a wider output voltage range and customizable output voltages at startup.

The I<sup>2</sup>C serial interface is optional and allows for dynamically controlling the output voltage, slew rate of the output voltage change, switching-current limit threshold, switching frequency, and forced PWM mode operation. The I<sup>2</sup>C-programmed settings have priority over the R<sub>SEL</sub> decoded settings.

The MAX77857 is available in a 2.83mm x 2.03mm, 35bump and 31-bump wafer-level package (WLP) and a 3.5mm x 3.5mm, 16-lead Flip Chip QFN package (FC2QFN).

### **Applications**

- USB Power Delivery (USB-PD) OTG

- Qualcomm<sup>®</sup> Quick Charge<sup>™</sup>

- USB V<sub>BUS</sub> Supply and DRP (Dual Role Power) Ports

- DSLR, DSLR Lens

- Display Power

- Up to 3-Cell Li-Ion Battery Applications

- Notebook Computer, Tablet PC

### **Benefits and Features**

- Wide Input Voltage Range: 2.5V to 16V

- Default Output Voltage

- 5V with Internal Feedback Resistors

- 3V to 15V with External Feedback Resistors

- I<sup>2</sup>C-Programmable Output Voltage after Startup

4.5V to 15V with Internal Feedback Resistors

- 3.0V to 15V with External Feedback Resistors, See Table 1

- Maximum Output Current

- Buck Mode: Up to 6A

- Boost Mode: Up to 4A (Boost Ratio ≤ 1.3)

- 7A Typical Switching Current

- R<sub>SEL</sub> Configuration

- I<sup>2</sup>C Interface Slave Address

- Switching Current Limit Threshold

- Internal/External Feedback Resistors

- I<sup>2</sup>C Programming

- Output Voltage (DVS)

- Slew Rate of Output Voltage Change

- Switching Current Limit Threshold

- Switching Frequency

- Forced PWM Mode Operation (FPWM)

- Power-OK (POK) Status and Fault Interrupt Masks

- Soft-Start

- Output Active Discharge

- Open-Drain Power-OK (POK) Monitor and Fault Condition Interrupt (MAX77857B/C Only)

- Protection Features

- Undervoltage Lockout (UVLO)

- Overcurrent Protection (OCP)

- Overvoltage Protection (OVP)

- Thermal Shutdown (THS)

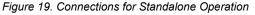

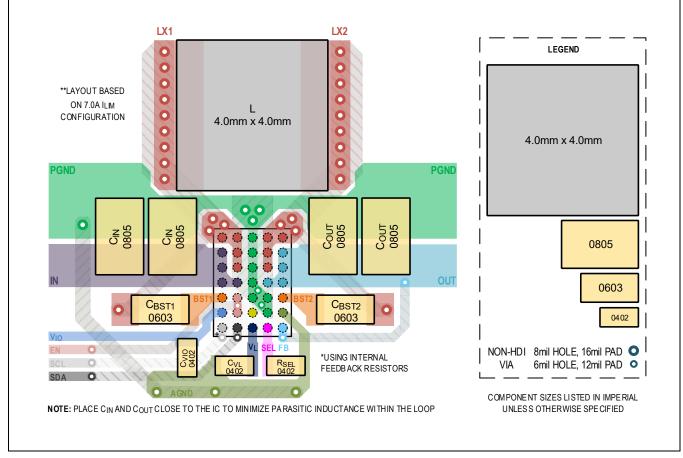

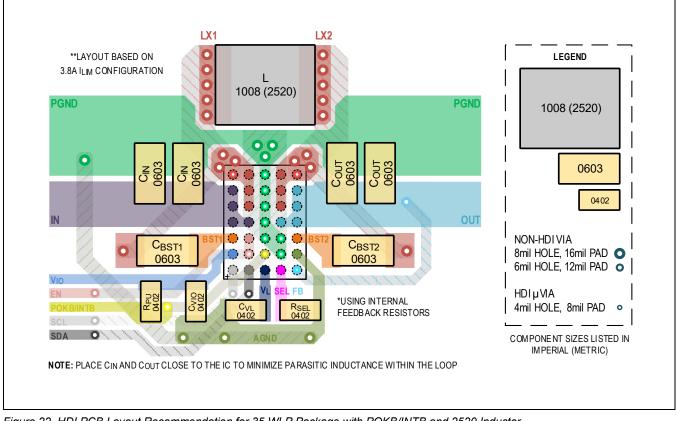

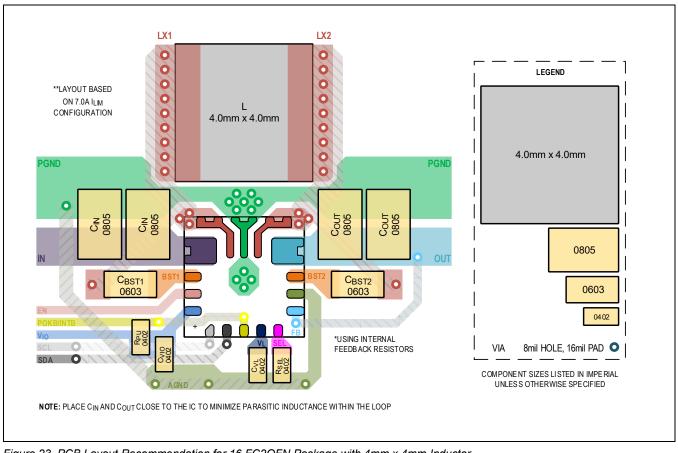

- High Density Interconnect (HDI) PCB not Required (See the <u>PCB Layout Guideline</u> section)

- Available in 2.83mm x 2.03mm 35 WLP or 31 WLP or 3.5mm x 3.5mm 16 FC2QFN

Ordering Information appears at end of data sheet.

Qualcomm Quick Charge is a product of Qualcomm Technologies, Inc. and/or its subsidiaries.

## MAX77857

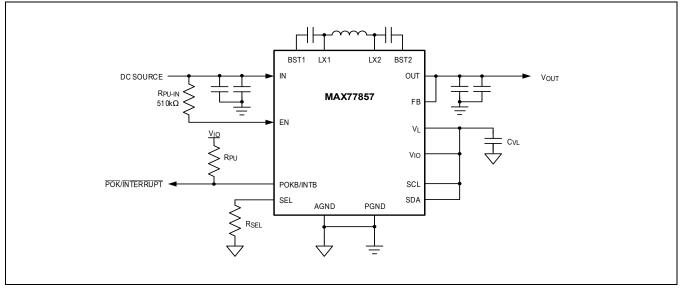

## **Simplified Application Circuit**

## MAX77857

## **Absolute Maximum Ratings**

| IN, LX1, LX2, OUT, FB to PGND     | 0.3V to +17.6V                  |

|-----------------------------------|---------------------------------|

| BST1, BST2 to AGND                | 0.3V to +20.0V                  |

| BST1 to LX1, BST2 to LX2          | 0.3V to +2.2V                   |

| POKB/INTB, SCL, SDA to AGND, PGND | -0.3V to V <sub>IO</sub> + 0.3V |

| $V_L,V_{IO},SEL,EN$ to AGND, PGND | 0.3V to +2.0V                   |

| PGND to AGND                      | 0.3V to +0.3V                   |

| Continuous Power Dissipation      |                                 |

| WLP Package (T <sub>A</sub> = +70°C, derate 20.4mW/°C a | bove +70°C  |

|---------------------------------------------------------|-------------|

| (Note 1))                                               | 1633mW      |

| FC2QFN Package (T <sub>A</sub> = +70°C, derate 20.7m)   | W/°C above  |

| +70°C (Note 1))                                         | 1656mW      |

| Maximum Junction Temperature                            | +150°C      |

| Storage Temperature Range65°                            | C to +150°C |

| Soldering Temperature (reflow)                          | +260°C      |

**Note 1:** Package thermal measurements were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-</u><u>tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| PARAMETER                  | SYMBOL           | CONDITION                                                                                                                      | TYPICAL RANGE   |

|----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Input Voltage Range        | V <sub>IN</sub>  |                                                                                                                                | 2.5V to 16V     |

| Output Voltage Bange       | V <sub>OUT</sub> | Internal feedback                                                                                                              | 4.5V to 15V     |

| Output Voltage Range       | •001             | External feedback                                                                                                              | 3V to 15V       |

|                            |                  | For continuous operation at 6A, the junction temperature $(T_J)$ is limited to                                                 |                 |

| Output Current Range       | lout             | +105°C. If the junction temperature is<br>higher than 105°C, the expected<br>lifetime at 6A continuous operation is<br>derated | 0A to 6A        |

| Junction Temperature Range | TJ               |                                                                                                                                | -40°C to +125°C |

## **Package Information**

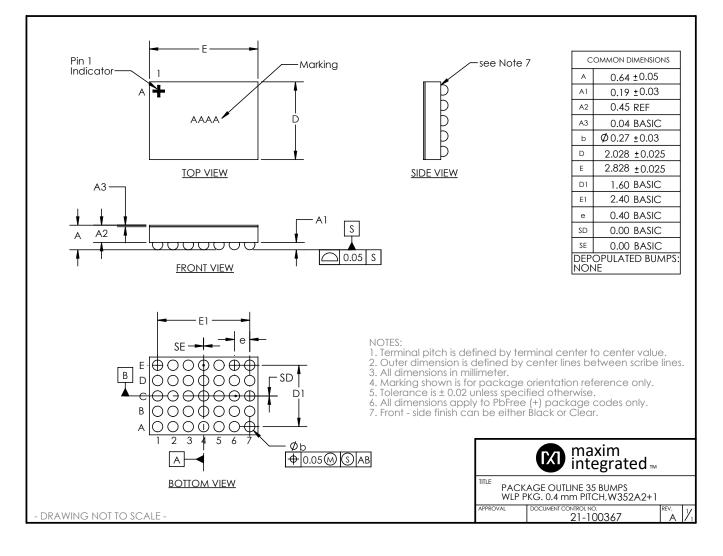

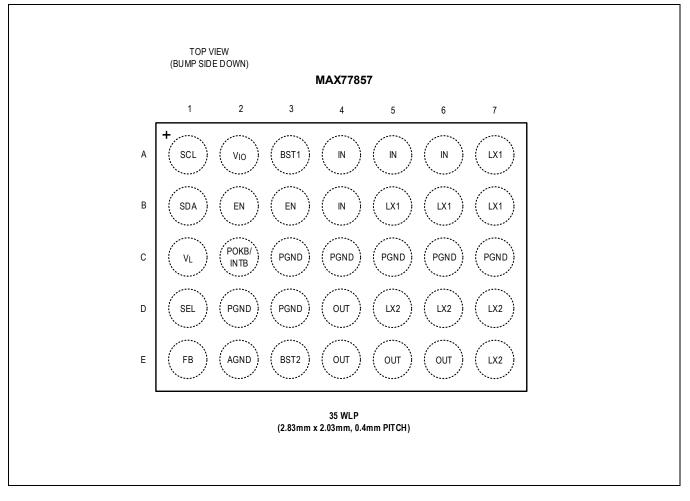

#### **35 WLP**

| Package Code                           | W352A2+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | <u>21-100367</u>               |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 49°C/W                         |

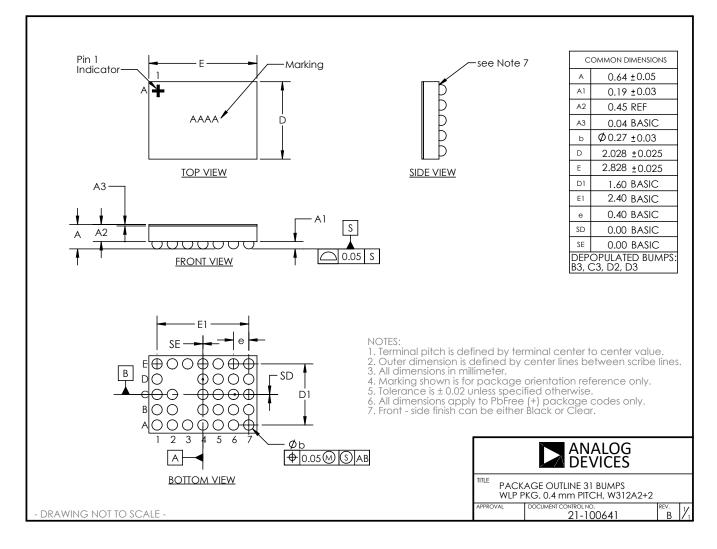

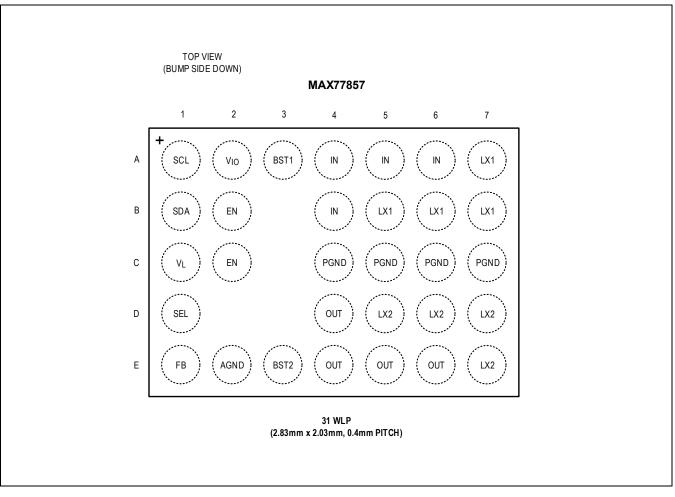

#### **31 WLP**

| Package Code                           | W312A2+2                       |  |

|----------------------------------------|--------------------------------|--|

| Outline Number                         | <u>21-100641</u>               |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |

| Thermal Resistance, Four-Layer Board:  |                                |  |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 49°C/W                         |  |

# MAX77857

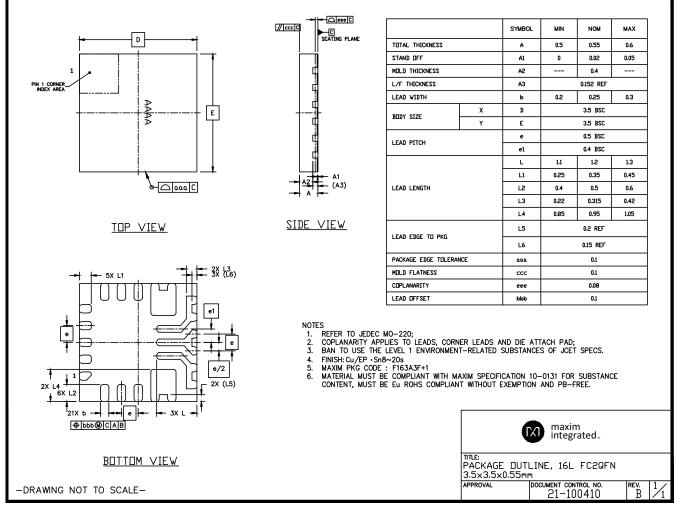

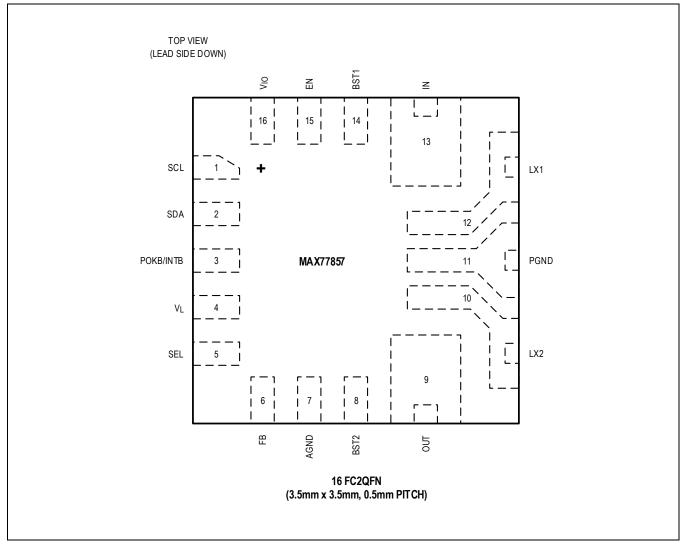

#### 16 FC2QFN

| Package Code                          | F163A3F+1        |

|---------------------------------------|------------------|

| Outline Number                        | <u>21-100410</u> |

| Land Pattern Number                   | <u>90-100141</u> |

| Thermal Resistance, Four-Layer Board: |                  |

| Junction-to-Ambient ( $\theta_{JA}$ ) | 48.3°C/W         |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

## **Electrical Characteristics**

$(V_{IN} = 7.6V, V_{OUT} = 5V, V_{VIO} = 1.8V, R_{SEL} = 536\Omega$ , Typicals are at  $T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . Limits over the operating temperature range  $(T_J = -40^{\circ}C \text{ to } +125^{\circ}C)$  and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                          | herwise noted.)<br>SYMBOL | COND                                                                                 | ITIONS                                                      | MIN   | TYP     | MAX   | UNITS    |

|----------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|---------|-------|----------|

| INPUT SUPPLY                                       |                           |                                                                                      |                                                             |       |         |       | ••       |

| Input Voltage Range                                | V <sub>IN</sub>           |                                                                                      |                                                             | 2.5   |         | 16    | V        |

| Input Undervoltage<br>Lockout (UVLO)               | V <sub>UVLO_R</sub>       | V <sub>IN</sub> rising                                                               |                                                             | 2.3   | 2.4     | 2.5   | V        |

| Input Undervoltage<br>Lockout (UVLO)<br>Hysteresis | V <sub>UVLO_HYS</sub>     | V <sub>UVLO_R</sub> – V <sub>UVLO_</sub>                                             | -                                                           |       | 150     |       | mV       |

| Shutdown Supply<br>Current                         | I <sub>SHDN</sub>         | EN = LOW, T <sub>J</sub> = -40                                                       | °C to +85°C                                                 |       | 2       | 6     | μA       |

| Quiescent Supply<br>Current                        | lQ                        | EN = HIGH, R <sub>SEL</sub><br>= short to GND, no<br>switching                       | SKIP mode, T <sub>J</sub> = -<br>40°C to +85°C<br>FPWM mode |       | 50<br>4 | 67    | μA<br>mA |

| OUTPUT VOLTAGE                                     |                           | Switching                                                                            | 11 Will mode                                                |       | 7       |       |          |

| Output Voltage                                     | V <sub>OUT</sub>          | Using internal feedba                                                                |                                                             | 4.5   |         | 15    | v        |

| Regulation Range                                   | 001                       | Using external feedb                                                                 | ack resistors                                               | 3.0   |         | 15    |          |

|                                                    |                           | V <sub>IN</sub> = 2.5V to 16V,<br>V <sub>OUT</sub> = 4.5V to                         | SKIP mode                                                   | -1.0  |         | +4.5  |          |

| Output Voltage<br>Accuracy                         | V <sub>OUT_ACC</sub>      | 15V, I <sub>OUT</sub> = 0mA,<br>using internal<br>feedback resistors                 | FPWM mode                                                   | -1.0  |         | +2.0  | %        |

| FB Accuracy                                        | V <sub>FB_ACC</sub>       | VREF[7:0] = 0x3D to                                                                  | 0xCC                                                        | -1.0  |         | +2.0  | %        |

| VL INTERNAL SUPPLY                                 | ·                         |                                                                                      |                                                             |       |         |       |          |

| V <sub>L</sub> Regulator Voltage                   | V <sub>VL</sub>           |                                                                                      |                                                             | 1.65  | 1.8     | 1.89  | V        |

| VIO SUPPLY                                         | ·                         |                                                                                      |                                                             |       |         |       |          |

| V <sub>IO</sub> Voltage Range                      | V <sub>VIO</sub>          |                                                                                      |                                                             | 1.08  |         | 2.0   | V        |

|                                                    | V <sub>VIO_VALID_R</sub>  | V <sub>IO</sub> rising                                                               |                                                             | 0.965 | 1.02    | 1.08  |          |

| V <sub>IO</sub> Valid Threshold                    | V <sub>VIO_VALID_F</sub>  | V <sub>IO</sub> falling                                                              |                                                             | 0.85  | 0.9     | 0.955 | V        |

| V <sub>IO</sub> Bias Current                       | I <sub>VIO</sub>          | No I <sup>2</sup> C interface (SD unconnected)                                       |                                                             |       |         | 2.0   | μA       |

|                                                    |                           | $f_{SCL} = f_{SDA} = 1MHz$                                                           |                                                             |       | 50      |       |          |

| ENABLE                                             | 1                         | 1                                                                                    |                                                             |       |         |       |          |

| EN Input LOW Voltage                               | V <sub>EN_IL</sub>        |                                                                                      |                                                             |       |         | 0.4   | V        |

| EN Input HIGH Voltage                              | V <sub>EN_IH</sub>        |                                                                                      |                                                             | 0.9   |         |       | V        |

| EN Internal Pulldown<br>Current                    | I <sub>EN_PD</sub>        | EN = HIGH                                                                            |                                                             |       | 0.1     |       | μA       |

| POWER-OK                                           | 1                         | 1                                                                                    |                                                             |       |         |       |          |

| POK Output LOW<br>Voltage                          | V <sub>POK_OL</sub>       | I <sub>POK</sub> = 1mA                                                               |                                                             |       |         | 0.3   | V        |

| POK Rising Threshold                               | V <sub>POK_R</sub>        | target V <sub>OUT</sub> voltage                                                      | sed as percentage of                                        | 90    | 95      |       | %        |

| POK Falling Threshold                              | V <sub>POK_F</sub>        | V <sub>OUT</sub> falling, expressed as percentage of target V <sub>OUT</sub> voltage |                                                             |       | 85      |       | %        |

| THERMAL PROTECTION                                 | N                         |                                                                                      |                                                             |       |         |       |          |

$(V_{IN} = 7.6V, V_{OUT} = 5V, V_{VIO} = 1.8V, R_{SEL} = 536\Omega$ , Typicals are at  $T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . Limits over the operating temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ) and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)

| characterization, unless of          |                       |                                                                                                |                                                                                       | MIN  | TVD   | MAY  |       |

|--------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|-------|------|-------|

| PARAMETER                            | SYMBOL                | CO                                                                                             | NDITIONS                                                                              | MIN  | TYP   | MAX  | UNITS |

| Thermal-Shutdown<br>Threshold        | T <sub>SHDN_R</sub>   | T <sub>J</sub> rising (Note 3)                                                                 |                                                                                       |      | 150   |      | °C    |

| Thermal-Shutdown<br>Hysteresis       | T <sub>SHDN_HYS</sub> | T <sub>SHDN_R</sub> – T <sub>SHD</sub>                                                         | <sub>N_F</sub> (Note 3)                                                               |      | 20    |      | °C    |

| BUCK-BOOST REGULA                    | TOR                   |                                                                                                |                                                                                       |      |       |      |       |

|                                      |                       |                                                                                                | FREQ[1:0] = 00                                                                        | 1.10 | 1.20  | 1.30 |       |

|                                      |                       |                                                                                                | FREQ[1:0] = 01                                                                        | 1.38 | 1.50  | 1.62 | -     |

| Switching Frequency                  | f <sub>SW</sub>       | I <sub>OUT</sub> = 0mA,<br>FPWM mode                                                           | FREQ[1:0] = 10<br>(default)                                                           | 1.66 | 1.80  | 1.94 | MHz   |

|                                      |                       |                                                                                                | FREQ[1:0] = 11                                                                        | 1.93 | 2.10  | 2.27 |       |

| Startup Delay Time                   | tSUDLY                | (Note 2)                                                                                       |                                                                                       |      | 100   |      | μs    |

| Soft-Start Time                      | t <sub>SS</sub>       | Measured from O<br>ramping during st<br>I <sub>OUT</sub> = 0mA (Note                           | Measured from OUT start ramping to stop ramping during startup, $C_{OUT} = 44\mu F$ , |      | 2.0   |      | ms    |

| Soft-Start Switching                 | I <sub>LIM_SS</sub>   | 3.8A) (Note 3)                                                                                 | /[2:0] = 100, 101, 110, or 111 (I <sub>LIM</sub> ≤<br>A) (Note 3)                     |      | A     |      |       |

| Current Limit                        | LIM_33                | ILIM[2:0] = 000, 0<br>3.8A) (Note 3)                                                           | 01, 010, or 011 (I <sub>LIM</sub> >                                                   |      | 3.8   |      |       |

|                                      |                       | ILIM[2:0] = 000                                                                                |                                                                                       | 6.2  | 7.0   | 8.3  |       |

|                                      |                       | ILIM[2:0] = 001 (l <sup>2</sup> C only, not available with $R_{SEL}$ ) (Note 3)                |                                                                                       |      | 6.2   |      |       |

|                                      |                       | ILIM[2:0] = 010                                                                                |                                                                                       | 4.8  | 5.6   | 6.9  |       |

| High-Side Switching                  |                       | ILIM[2:0] = 011 (I <sup>2</sup> C only, not available<br>with R <sub>SEL</sub> ) (Note 3)      |                                                                                       |      | 4.6   |      |       |

| Current Limit                        | ILIM                  | ILIM[2:0] = 100                                                                                |                                                                                       | 3.3  | 3.8   | 5.1  | A     |

|                                      |                       | ILIM[2:0] = 101 (I <sup>2</sup> C only, not available<br>with R <sub>SEL</sub> ) (Note 3)      |                                                                                       | 2.8  |       |      |       |

|                                      |                       | ILIM[2:0] = 110                                                                                |                                                                                       | 1.5  | 1.8   | 2.9  |       |

|                                      |                       | ILIM[2:0] = 111 (I <sup>2</sup><br>with R <sub>SEL</sub> ) (Note                               | <sup>2</sup> C only, not available<br>3)                                              |      | 0.99  |      |       |

|                                      |                       | ILIM[2:0] = 000 or                                                                             | <sup>-</sup> 001 (Note 3)                                                             |      | 2.5   |      |       |

|                                      |                       | ILIM[2:0] = 010 or                                                                             | <sup>-</sup> 011 (Note 3)                                                             |      | 1.8   |      |       |

| Valley Current Limit                 | ILIM_VALLEY           | ILIM[2:0] = 100 or                                                                             | 101 (Note 3)                                                                          | 1.0  |       |      | A     |

|                                      |                       | ILIM[2:0] = 110 or                                                                             | , ,                                                                                   | 0.3  |       |      | 1     |

| Skip Mode Switching<br>Current Limit | ILIM_SKIP             | SKIP mode (Note                                                                                | . ,                                                                                   |      | 1.4   |      | A     |

| Line Regulation                      | ΔV/V <sub>IN</sub>    | V <sub>IN</sub> = 2.5V to 16V, V <sub>OUT</sub> = 5V, I <sub>OUT</sub> = 0mA and 1A, FPWM mode |                                                                                       |      | ± 0.3 |      | %/V   |

| Load Regulation                      | ΔV/V <sub>OUT</sub>   |                                                                                                | $=$ 5V, $I_{OUT}$ = 0mA to 3A,                                                        |      | ± 0.6 |      | %/A   |

|                                      |                       |                                                                                                | D, code clamped below                                                                 |      | 0.299 |      |       |

| Internal Reference                   | V <sub>REF</sub>      | VREF[7:0] = 0x44, default value                                                                |                                                                                       |      | 0.333 |      | v     |

| Voltage                              | ' NEF                 |                                                                                                | C, code clamped above                                                                 |      | 1.000 |      | -     |

$(V_{IN} = 7.6V, V_{OUT} = 5V, V_{VIO} = 1.8V, R_{SEL} = 536\Omega$ , Typicals are at  $T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . Limits over the operating temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ) and relevant voltage range are guaranteed by design and characterization. unless otherwise noted.)

| PARAMETER                                           | SYMBOL                | CONDITIONS                                                                    | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------|-------|-------|-------|-------|

| Internal Reference<br>Voltage Programmable<br>Range | V <sub>REF</sub>      | VREF[7:0] = 0x3D to 0xCC                                                      | 0.299 |       | 1.000 | V     |

|                                                     |                       | SLEW_RATE[1:0] = 00, FREQ[1:0] = 10,<br>or 11                                 |       | 4/3   |       |       |

|                                                     |                       | SLEW_RATE[1:0] = 00, FREQ[1:0] = 00,<br>or 01                                 |       | 7/6   |       |       |

| Internal Reference DVS                              |                       | SLEW_RATE[1:0] = 01                                                           |       | 2/3   |       |       |

| Ramp Rate                                           | ∆V <sub>REF</sub> /∆t | SLEW_RATE[1:0] = 10                                                           |       | 1/3   |       | mV/μs |

|                                                     |                       | SLEW_RATE[1:0] = 11, FREQ[1:0] = 10,<br>or 11                                 |       | 17/75 |       |       |

|                                                     |                       | SLEW_RATE[1:0] = 11, FREQ[1:0] = 00,<br>or 01                                 |       | 1/6   |       |       |

| FB Input Leakage<br>Current                         | I <sub>FB_LK</sub>    |                                                                               | -1    |       | +1    | μA    |

| High-Side MOSFET On<br>Resistance                   | R <sub>DSON_HS</sub>  | IN to LX1, LX2 to OUT                                                         |       | 20    | 35    | mΩ    |

| Low-Side MOSFET On<br>Resistance                    | R <sub>DSON_LS</sub>  | LX1 to PGND, LX2 to PGND                                                      |       | 22    | 43    | mΩ    |

| Overvoltage-Limit<br>Threshold                      | V <sub>OVP</sub>      |                                                                               | 15.85 | 16.40 | 16.95 | V     |

| Overvoltage-Release<br>Threshold                    | V <sub>OVP_REL</sub>  |                                                                               | 15.25 | 15.50 | 16.20 | V     |

| Output Active Discharge<br>Current                  | IDISCHG               | EN = LOW or V <sub>IN</sub> < V <sub>UVLO_F</sub> , V <sub>OUT</sub> =<br>15V |       | 5     |       | mA    |

## **Electrical Characteristics–I<sup>2</sup>C Serial Interface**

$(V_{IN} = 7.6V, V_{OUT} = 5V, V_{VIO} = 1.8V, R_{SEL} = 536\Omega$ , Typicals are at  $T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . Limits over the operating temperature range  $(T_J = -40^{\circ}C \text{ to } +125^{\circ}C)$  and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                    | SYMBOL          | CONDITIONS                                                                     | MIN                        | TYP   | MAX                       | UNITS |

|----------------------------------------------|-----------------|--------------------------------------------------------------------------------|----------------------------|-------|---------------------------|-------|

| I/O STAGE                                    |                 | · · ·                                                                          |                            |       |                           |       |

| SCL, SDA Input HIGH<br>Voltage               | V <sub>IH</sub> |                                                                                | 0.7 x<br>V <sub>VIO</sub>  |       |                           | V     |

| SCL, SDA Input LOW<br>Voltage                | V <sub>IL</sub> |                                                                                |                            |       | 0.3 x<br>V <sub>VIO</sub> | V     |

| SCL, SDA Input V <sub>HY</sub><br>Hysteresis | nput Vene       | Fast mode/Fast-mode plus                                                       | 0.05 x<br>V <sub>VIO</sub> |       |                           | v     |

|                                              | VHYS            | High-speed mode                                                                | 0.1 x<br>V <sub>VIO</sub>  |       |                           |       |

| SDA Output LOW<br>Voltage                    | V <sub>OL</sub> | I <sub>SINK</sub> = 2mA (Fast mode/Fast-mode plus)<br>or 3mA (High-speed mode) |                            |       | 0.2 x<br>V <sub>VIO</sub> | V     |

| SCL, SDA Input<br>Capacitance                | CI              |                                                                                |                            |       | 10                        | pF    |

| SCL, SDA Input<br>Leakage Current            | I <sub>LK</sub> |                                                                                | -10                        | 0.001 | +10                       | μA    |

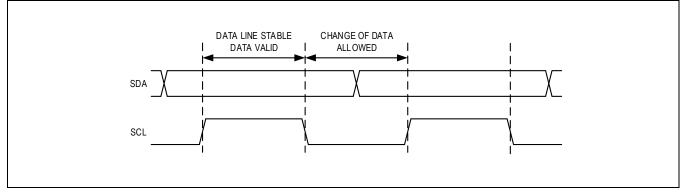

| TIMING (FAST MODE)                           |                 |                                                                                |                            |       |                           |       |

| Clock Frequency                              | fscl            |                                                                                | 0                          |       | 400                       | kHz   |

$(V_{IN} = 7.6V, V_{OUT} = 5V, V_{VIO} = 1.8V, R_{SEL} = 536\Omega$ , Typicals are at  $T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at  $T_J = +25^{\circ}C$ . Limits over the operating temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ) and relevant voltage range are guaranteed by design and characterization. unless otherwise noted.)

| PARAMETER                                            | SYMBOL                | CONDITIONS | MIN                                 | TYP | MAX  | UNITS |

|------------------------------------------------------|-----------------------|------------|-------------------------------------|-----|------|-------|

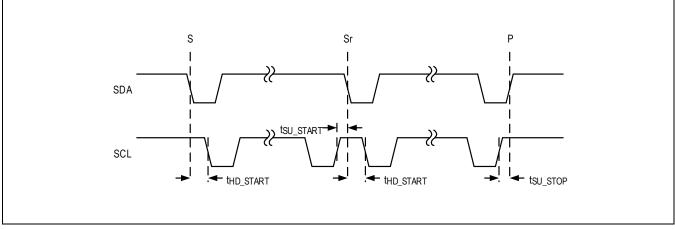

| Bus Free Time Between<br>STOP and START<br>Condition | <sup>t</sup> BUSF     |            | 1.3                                 |     |      | μs    |

| Hold Time (REPEATED)<br>START Condition              | <sup>t</sup> HD_START |            | 0.6                                 |     |      | μs    |

| SCL LOW Period                                       | t <sub>LOW</sub>      |            | 1.3                                 |     |      | μs    |

| SCL HIGH Period                                      | thigh                 |            | 0.6                                 |     |      | μs    |

| Setup Time REPEATED<br>START Condition               | <sup>t</sup> SU_START |            | 0.6                                 |     |      | μs    |

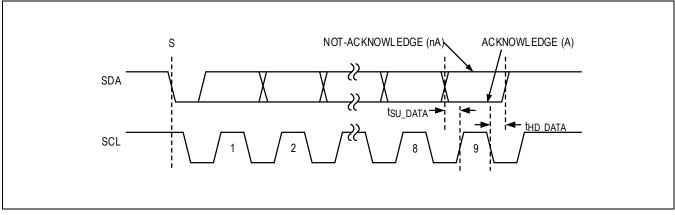

| DATA Setup Time                                      | T <sub>SU_DATA</sub>  |            | 100                                 |     |      | ns    |

| SCL, SDA Receiving<br>Rise Time                      | <sup>t</sup> R_REV    |            | 20                                  |     | 300  | ns    |

| SCL, SDA Receiving<br>Fall Time                      | <sup>t</sup> F_REV    |            | 20 x<br>(V <sub>VIO</sub><br>/5.5V) |     | 300  | ns    |

| Setup Time for STOP<br>Condition                     | t <sub>SU_STO</sub>   |            | 0.26                                |     |      | μs    |

| Data Valid Time                                      | <sup>t</sup> VD_DATA  |            |                                     |     | 900  | ns    |

| Data Valid Acknowledge<br>Time                       | t <sub>VD_ACK</sub>   |            |                                     |     | 900  | ns    |

| Bus Capacitance                                      | CB                    | (Note 2)   |                                     |     | 400  | pF    |

| Pulse Width of<br>Suppressed Spikes                  | t <sub>SP</sub>       |            |                                     |     | 140  | ns    |

| TIMING (FAST-MODE PL                                 | US)                   |            |                                     |     |      |       |

| Clock Frequency                                      | f <sub>SCL</sub>      |            | 0                                   |     | 1000 | kHz   |

| Bus Free Time Between<br>STOP and START<br>Condition | t <sub>BUSF</sub>     |            | 0.5                                 |     |      | μs    |

| Hold Time (REPEATED)<br>START Condition              | <sup>t</sup> HD_START |            | 0.26                                |     |      | μs    |

| SCL LOW Period                                       | <sup>t</sup> LOW      |            | 0.5                                 |     |      | μs    |

| SCL HIGH Period                                      | <sup>t</sup> HIGH     |            | 0.26                                |     |      | μs    |

| Setup Time REPEATED<br>START Condition               | <sup>t</sup> SU_START |            | 0.26                                |     |      | μs    |

| DATA Setup Time                                      | T <sub>SU_DATA</sub>  |            | 50                                  |     |      | ns    |

| SCL, SDA Receiving<br>Rise Time                      | <sup>t</sup> R_REV    |            |                                     |     | 120  | ns    |

| SCL, SDA Receiving<br>Fall Time                      | <sup>t</sup> F_REV    |            | 20 x<br>(V <sub>VIO</sub><br>/5.5V) |     | 120  | ns    |

| Setup Time for STOP<br>Condition                     | ts∪_sto               |            | 0.26                                |     |      | μs    |

| Data Valid Time                                      | <sup>t</sup> VD_DATA  |            |                                     |     | 450  | ns    |

| Data Valid Acknowledge<br>Time                       | t <sub>VD_ACK</sub>   |            |                                     |     | 450  | ns    |

| Bus Capacitance                                      | CB                    | (Note 2)   |                                     |     | 550  | pF    |

| Pulse Width of<br>Suppressed Spikes                  | t <sub>SP</sub>       |            |                                     |     | 140  | ns    |

| $(V_{IN} = 7.6V, V_{OUT} = 5V, V_{VIO} = 1.8V, R_{SEL} = 536\Omega$ , Typicals are at $T_A \approx T_J = +25^{\circ}C$ . Limits are 100% production tested at $T_J = +25^{\circ}C$ . |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Limits over the operating temperature range (T <sub>J</sub> = -40°C to +125°C) and relevant voltage range are guaranteed by design and                                               |

| characterization_unless otherwise noted )                                                                                                                                            |

| PARAMETER                               | SYMBOL                                            | CONDITIONS | MIN | TYP | MAX | UNITS |  |

|-----------------------------------------|---------------------------------------------------|------------|-----|-----|-----|-------|--|

| TIMING (HIGH-SPEED M                    | TIMING (HIGH-SPEED MODE, BUS CAPACITANCE = 100pF) |            |     |     |     |       |  |

| Clock Frequency                         | fscl                                              |            |     |     | 3.4 | MHz   |  |

| Hold Time (REPEATED)<br>START Condition | <sup>t</sup> HD_START                             |            | 160 |     |     | ns    |  |

| SCL LOW Period                          | tLOW                                              |            | 160 |     |     | ns    |  |

| SCL HIGH Period                         | <sup>t</sup> HIGH                                 |            | 60  |     |     | ns    |  |

| Setup Time REPEATED<br>START Condition  | <sup>t</sup> SU_START                             |            | 160 |     |     | ns    |  |

| DATA Hold Time                          | <sup>t</sup> HD_DATA                              |            |     |     | 95  | ns    |  |

| DATA Setup Time                         | T <sub>SU_DATA</sub>                              |            | 10  |     |     | ns    |  |

| SCL Rise Time                           | t <sub>R_SCL</sub>                                |            | 10  |     | 50  | ns    |  |

| SCL Fall Time                           | t <sub>F_SCL</sub>                                |            | 10  |     | 50  | ns    |  |

| SDA Rise Time                           | <sup>t</sup> R_SDA                                |            | 10  |     | 80  | ns    |  |

| SDA Fall Time                           | t <sub>F_SDA</sub>                                |            | 10  |     | 80  | ns    |  |

| Setup Time for STOP<br>Condition        | t <sub>SU_STOP</sub>                              |            | 160 |     |     | ns    |  |

| Bus Capacitance                         | CB                                                | (Note 2)   |     |     | 100 | pF    |  |

| Pulse Width of<br>Suppressed Spikes     | t <sub>SP</sub>                                   |            |     |     | 30  | ns    |  |

**Note 2:** Internal design target. Not production tested.

**Note 3:** Characterized by ATE or bench test. Not production tested.

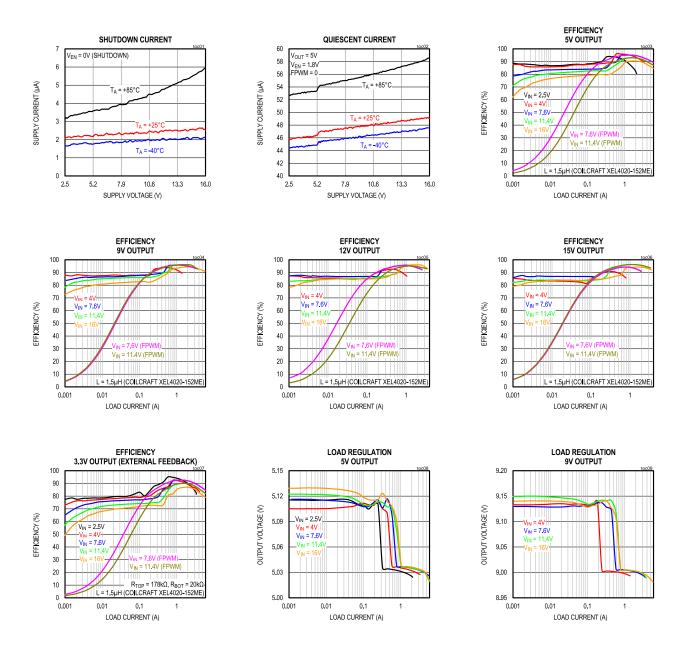

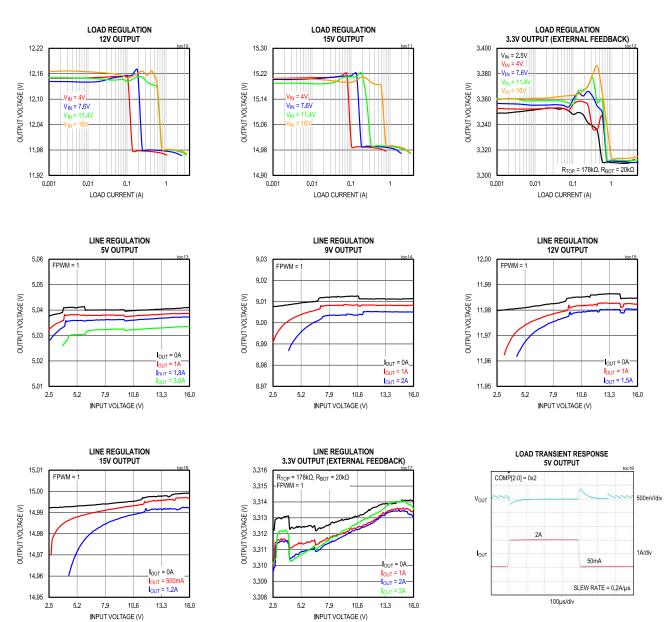

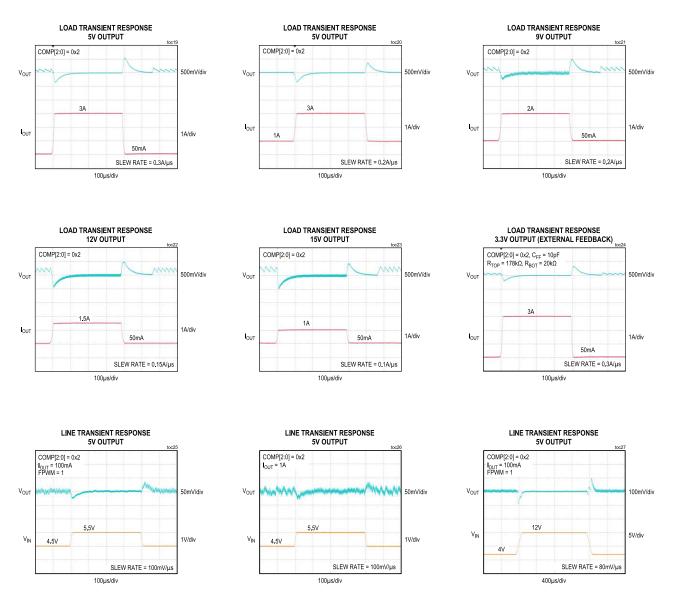

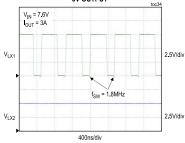

## **Typical Operating Characteristics**

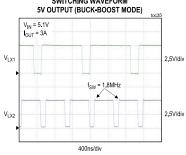

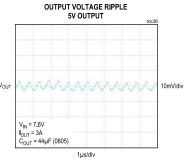

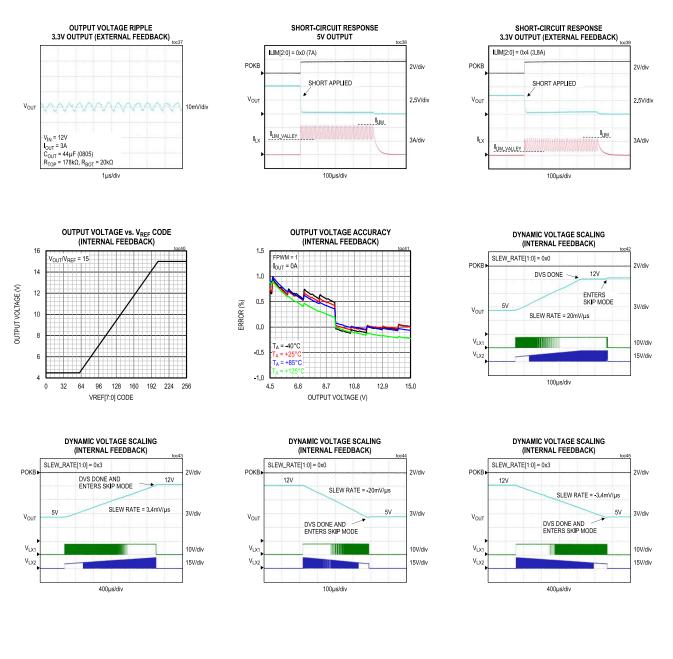

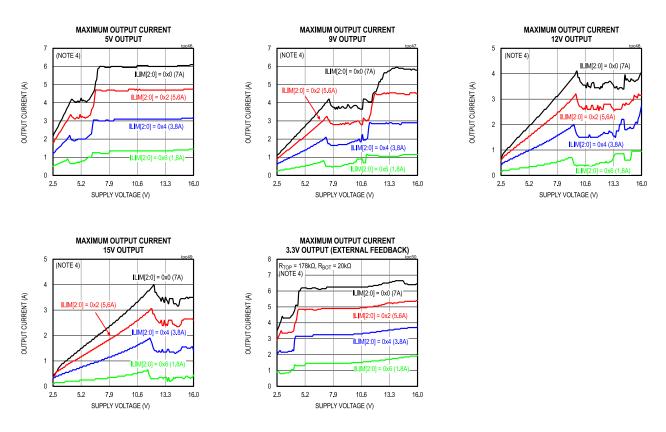

$(V_{IN} = 7.6V, V_{OUT} = 5V, L = 1.5\mu$ H (Coilcraft XEL4020-152ME),  $C_{OUT} = 2x 22\mu$ F, FPWM = 0, ILIM[2:0] = 0x0 (7A),  $f_{SW} = 1.8$ MHz, internal feedback configuration,  $T_A = +25^{\circ}$ C, unless otherwise noted. **Note 4**: Measurement limited by switching current limit. Actual maximum output current depends on system thermal performance.)

$(V_{IN} = 7.6V, V_{OUT} = 5V, L = 1.5\mu$ H (Coilcraft XEL4020-152ME), C<sub>OUT</sub> = 2x 22 $\mu$ F, FPWM = 0, ILIM[2:0] = 0x0 (7A), f<sub>SW</sub> = 1.8MHz, internal feedback configuration, T<sub>A</sub> = +25°C, unless otherwise noted. **Note 4**: Measurement limited by switching current limit. Actual maximum output current depends on system thermal performance.)

$(V_{IN} = 7.6V, V_{OUT} = 5V, L = 1.5\mu$ H (Coilcraft XEL4020-152ME), C<sub>OUT</sub> = 2x 22 $\mu$ F, FPWM = 0, ILIM[2:0] = 0x0 (7A), f<sub>SW</sub> = 1.8MHz, internal feedback configuration, T<sub>A</sub> = +25°C, unless otherwise noted. **Note 4**: Measurement limited by switching current limit. Actual maximum output current depends on system thermal performance.)

(V<sub>IN</sub> = 7.6V, V<sub>OUT</sub> = 5V, L = 1.5µH (Coilcraft XEL4020-152ME), C<sub>OUT</sub> = 2x 22µF, FPWM = 0, ILIM[2:0] = 0x0 (7A), f<sub>SW</sub> = 1.8MHz, internal feedback configuration, T<sub>A</sub> = +25°C, unless otherwise noted. Note 4: Measurement limited by switching current limit. Actual maximum output current depends on system thermal performance.)

$(V_{IN} = 7.6V, V_{OUT} = 5V, L = 1.5\mu$ H (Coilcraft XEL4020-152ME), C<sub>OUT</sub> = 2x 22µF, FPWM = 0, ILIM[2:0] = 0x0 (7A), f<sub>SW</sub> = 1.8MHz, internal feedback configuration, T<sub>A</sub> = +25°C, unless otherwise noted. **Note 4**: Measurement limited by switching current limit. Actual maximum output current depends on system thermal performance.)

$(V_{IN} = 7.6V, V_{OUT} = 5V, L = 1.5\mu$ H (Coilcraft XEL4020-152ME), C<sub>OUT</sub> = 2x 22 $\mu$ F, FPWM = 0, ILIM[2:0] = 0x0 (7A), f<sub>SW</sub> = 1.8MHz, internal feedback configuration, T<sub>A</sub> = +25°C, unless otherwise noted. **Note 4**: Measurement limited by switching current limit. Actual maximum output current depends on system thermal performance.)

# **Pin Configurations**

### **35 WLP**

### 16 FC2QFN

## **Pin Descriptions**

| PIN    |        | NAME      | FUNCTION                                               | Turne                                                                                                                                  |             |

|--------|--------|-----------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 35 WLP | 31 WLP | 16 FC2QFN |                                                        | FUNCTION                                                                                                                               | Туре        |

| A1     | A1     | 1         | SCL                                                    | $I^{2}C$ Serial Interface Clock (High-Z in OFF State). Connect to V <sub>IO</sub>                                                      | Digital     |

|        |        |           |                                                        | with a 1.5k $\Omega$ to 2.2k $\Omega$ pullup resistor.                                                                                 | Input       |

| B1     | B1     | 2         | SDA                                                    | $\rm I^2C$ Serial Interface Data (High-Z in OFF State). Connect to VIO                                                                 | Digital I/O |

|        |        |           | with a 1.5k $\Omega$ to 2.2k $\Omega$ pullup resistor. | Digital 1/0                                                                                                                            |             |

| C2     |        | 3         | POKB/                                                  | Buck-Boost Output Power-OK Monitor or Fault Interrupt Active-<br>Low Open-Drain Output. Connect to $V_{IO}$ with a 15k $\Omega$ pullup | Digital     |

| 02     |        | 3         | INTB                                                   | resistor. See the <u>Power-OK Monitor and Fault Interrupts</u> section for more details. Do not connect to this pin if not in use.     | Output      |

| C1     | C1     | 4         | VL                                                     | Low-Voltage Internal Supply. Powered from IN. Bypass to AGND with a 10V 2.2µF ceramic capacitor. Do not load this pin                  | Analog      |

MAX77857

|                   |                   |    |                                                                             | externally except for usage stated in the Non-I2C and                                                  |                |

|-------------------|-------------------|----|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------|

|                   |                   |    |                                                                             | Standalone Operation section.                                                                          |                |

| D1                | D1                | 5  | SEL                                                                         | Configuration Selection. Connect a resistor between SEL and                                            | Analog         |

|                   |                   |    |                                                                             | AGND. See <u>Table 2</u> for resistor values and configurations.<br>Using Internal Feedback Resistors: |                |

|                   |                   |    |                                                                             | Output Voltage Sense Input. Connect to the output at the point-                                        |                |

|                   |                   |    |                                                                             | of-load (close to output capacitor).                                                                   |                |

| E1                | E1                | 6  | FB                                                                          | Using External Feedback Resistors:                                                                     | Analog         |

|                   |                   | 0  | . 5                                                                         | Output Voltage Feedback Input. Connect to the center tap of an                                         | Analog         |

|                   |                   |    |                                                                             | external resistor divider from OUT to AGND to set the output                                           |                |

|                   |                   |    |                                                                             | voltage. See the <u>Output Voltage Configuration</u> section for more                                  |                |

|                   |                   |    |                                                                             | details.<br>Analog Ground. Connect to PGND on the PCB. See the <u>PCB</u>                              |                |

| E2                | E2                | 7  | AGND                                                                        | Layout Guideline section for more details.                                                             | Ground         |

| <b>F</b> 2        | <b>F</b> 2        | 8  | BST2                                                                        | LX2 High-Side FET Driver Supply. Connect a 25V 0.22µF                                                  | Power          |

| E3                | E3                | Ö  | 0012                                                                        | ceramic capacitor between BST2 and LX2.                                                                | Input          |

| D4, E4,           | D4, E4,           | 9  | OUT                                                                         | Buck-Boost Output. Bypass to PGND with two 25V 22 $\mu$ F                                              | Power          |

| E5, E6            | E5, E6            | Ŭ  |                                                                             | ceramic capacitors as close as possible.                                                               | Output         |

| D5, D6,<br>D7, E7 | D5, D6,<br>D7, E7 | 10 | LX2                                                                         | Buck-Boost Switching Node 2                                                                            | Power          |

| C3, C4,           | D7, L7            |    |                                                                             |                                                                                                        |                |

| C5, C6,           | C4, C5,           | 11 | PGND                                                                        | Power Ground. Connect to AGND on the PCB. See the PCB                                                  | <b>a</b> .     |

| C7, D2,           |                   |    | PGND                                                                        | Layout Guidelines section for more details.                                                            | Ground         |

| D3                |                   |    |                                                                             |                                                                                                        |                |

| A7, B5,           | A7, B5,           | 12 | LX1                                                                         | Buck-Boost Switching Node 1                                                                            | Power          |

| B6, B7            | B6, B7            |    |                                                                             | Ű                                                                                                      |                |

| A4, A5,           | A4, A5,           | 13 | IN                                                                          | Buck-Boost Input. Bypass to PGND with two 25V 10µF ceramic                                             | Power          |

| A6, B4            | A6, B4            |    |                                                                             | capacitors as close as possible.<br>LX1 High-Side FET Driver Supply. Connect a 25V 0.22µF              | Input<br>Power |

| A3                | A3                | 14 | BST1                                                                        | ceramic capacitor between BST1 and LX1.                                                                | Input          |

|                   |                   |    |                                                                             | Active-High Buck-Boost Enable Input. Compatible with the VIO                                           |                |

|                   |                   |    |                                                                             | voltage domain. Pulldown internally with 0.1µA current source.                                         | Distal         |

| B2, B3 B2, C2     | B2, C2 15 EN      | EN | See the <u>Non-I<sup>2</sup>C and Standalone Operation</u> section for more | Digital                                                                                                |                |

|                   |                   |    |                                                                             | information if application desires to control EN with IN (i.e., start                                  | Input          |

|                   |                   |    |                                                                             | up MAX77857 whenever IN's voltage is valid).                                                           |                |

|                   |                   |    | VIO                                                                         | IO Voltage Supply. Bypass to AGND with a 6.3V $0.47\mu$ F ceramic                                      | Power          |

| A2                | A2                | 16 | VI0                                                                         | capacitor. Registers are held in reset and regulator remains                                           | Input          |

|                   |                   |    |                                                                             | disabled when this pin's voltage is invalid.                                                           | •              |

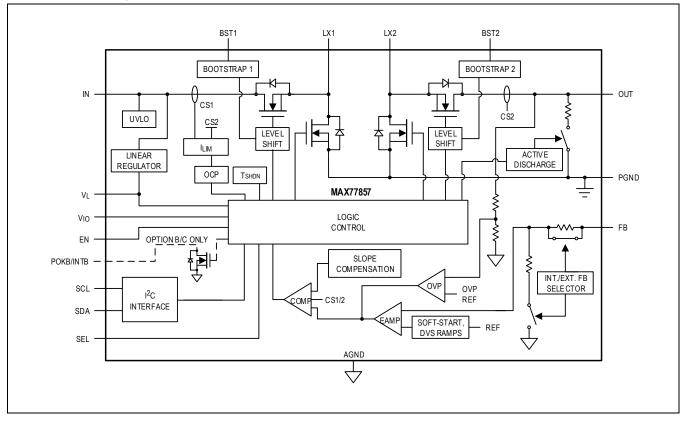

# **Functional Diagrams**

MAX77857

## **Detailed Description**

#### **General Description**

The MAX77857 is a high-efficiency, high-performance buck-boost converter targeted for systems requiring a wide input voltage range (2.5V to 16V). The IC can supply up to 6A of output current in buck mode and up to 4A in boost mode (boost ratio  $\leq$  1.3). The IC allows systems to change the output voltage and load current capacity dynamically through the I<sup>2</sup>C serial interface. The IC supports the standard 5V/3A USB V<sub>BUS</sub> requirement as well as USB PD requirements. Systems equipped with MAX77857 can provide fast-charging peripheral devices with higher output voltage, minimizing power loss across cable/connector and reducing charging time.

The IC operates either in SKIP mode or in forced-PWM (FPWM) mode, depending on the operating conditions, to optimize the efficiency. The default output voltage is 5V when using internal feedback resistors. The IC can also be configured to any default output voltages between 3V and 15V when using external feedback resistors. The output voltage is adjustable dynamically (DVS) between 4.5V and 15V in 73.5mV steps when using internal feedback resistors, or between 3V to 15V when using external feedback resistors (with step-size dependent on the external feedback resistor ratio), by programming the internal reference voltage through the I<sup>2</sup>C serial interface. See the <u>Output Voltage Configuration</u> section for more information.

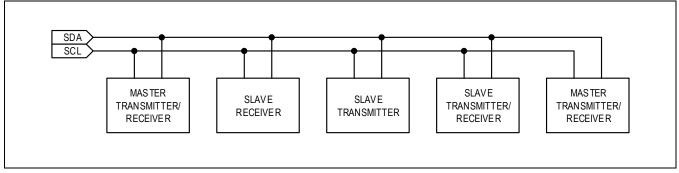

The SEL pin allows a single external resistor, R<sub>SEL</sub>, to connect to AGND to program the following:

- I<sup>2</sup>C Interface Slave Address (4 options)

- Switching Current Limit Threshold (4 options)

- Feedback Resistor Selection (Internal or external)

The different I<sup>2</sup>C interface slave addresses accommodate multiple devices in a system with a limited I<sup>2</sup>C bus. The different switching current limit thresholds allow the use of lower profile and smaller external components optimized for a particular application. The use of external feedback resistors allows for a wider output voltage range and customizable output voltages at startup. See the <u>SEL Pin Configuration</u> section for more information.

An optional I<sup>2</sup>C serial interface allows dynamic control of the following:

- Output Voltage (using Internal Reference Voltage)

- Slew Rate of Output Voltage Change (4 options)

- Switching Current Limit Threshold (8 options)

- Switching Frequency (4 options)

- Forced-PWM Mode Operation

- Power-OK (POK) Status and Fault Interrupts

- Internal Compensation

The different switching frequencies provide options to improve the EMI performance by avoiding EMI sensitive frequency bands. The  $I^2$ C-programmed settings have priority over the R<sub>SEL</sub> decoded settings.

#### Start-Up

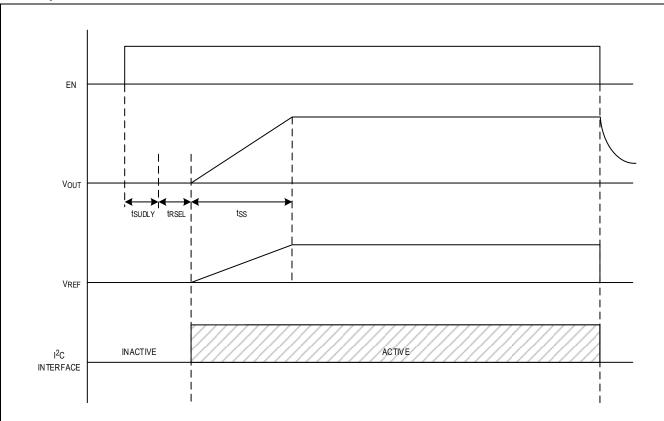

Figure 1. Start-Up Waveform

The start-up behavior is depicted in <u>Figure 1</u>. When input voltage  $V_{IN}$  is above UVLO threshold  $V_{UVLO_R}$  and EN pin is at logic HIGH, the IC starts up by first turning on the internal bias circuitry ( $V_L$ ), which takes typically 100µs ( $t_{SUDLY}$ ) to settle. The IC then senses the SEL pin resistance to set the I<sup>2</sup>C interface slave address, switching current limit threshold, and the use of internal or external feedback resistors. The R<sub>SEL</sub> reading takes typically 200µs ( $t_{RSEL}$ ) to complete. See the <u>SEL Pin Configuration</u> section for more information. Next, the IC checks if the V<sub>IO</sub> voltage is valid. If so, it activates the I<sup>2</sup>C interface and begins the buck-boost soft-start process (see the <u>Soft-Start</u> section).

When EN toggles to logic HIGH, if output-active discharge is still active from a previous shutdown event, the IC waits for active discharge to finish before it initiates the startup sequence.

It is possible to use the internal regulator  $V_L$  to provide power to the  $V_{IO}$  pin, or to use  $V_{IN}$  to control the EN pin. See the <u>Non-I<sup>2</sup>C and Standalone Configuration</u> section for more details.

### Soft-Start

The IC features soft-start to avoid a large amount of input current drawn from the system supply during startup. The default soft-start time ( $t_{SS}$ ) is 2ms typical. During soft-start, the internal reference voltage ( $V_{REF}$ ) slowly ramps up to the target value. The switching current limit threshold during soft-start is reduced to 3.8A if the  $I_{LIM}$  setting is set to be higher than such value (through  $R_{SEL}$ ). If the  $I_{LIM}$  setting is set to be 3.8A or lower, then the same switching current limit threshold applies during soft-start. After soft-start finishes, the normal switching current limit threshold applies.

For the MAX77857C, if V<sub>OUT</sub> does not reach POK level (typically 95% of the V<sub>OUT</sub> target) after soft-start timer ( $t_{SS}$ ) expires, the IC latches off. This behavior does not apply to the MAX77857A/B. See the <u>Immediate Shutdown and Latch-Off Condition</u> section for more information.

#### Shutdown

Pull the EN pin to logic LOW to shut down the IC. In a shutdown event, the IC stops switching, resets all registers, and activates the output-active discharge until the output voltage ( $V_{OUT}$ ) drops below about 2.5V or after 500ms, whichever occurs sooner.

#### **Immediate Latch-Off Conditions**

The IC has a latch-off feature to protect itself under certain fault conditions by shutting down the buck-boost regulator.

Immediate Shutdown Conditions:

- IN UVLO: V<sub>IN</sub> < Input UVLO Falling Threshold (V<sub>UVLO F</sub>)

- VIO UVLO: V<sub>VIO</sub> < VIO Valid Falling Threshold (V<sub>VIO VALID F</sub>)

Latch-Off Conditions:

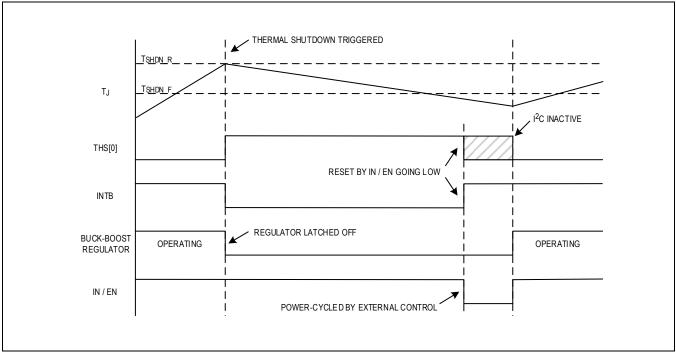

- Thermal Shutdown:  $T_J$  > Thermal-Shutdown Rising Threshold ( $T_{SHDN,R}$ ) (See the <u>Thermal Shutdown (THS)</u> section)

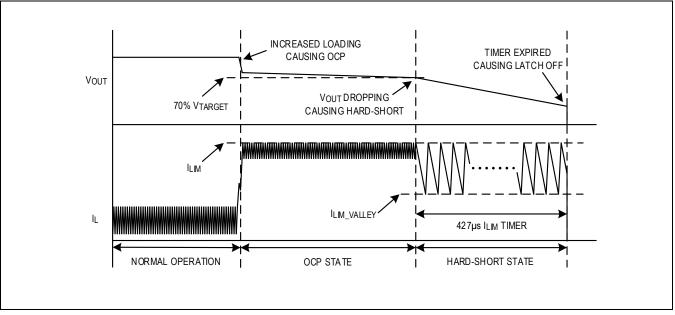

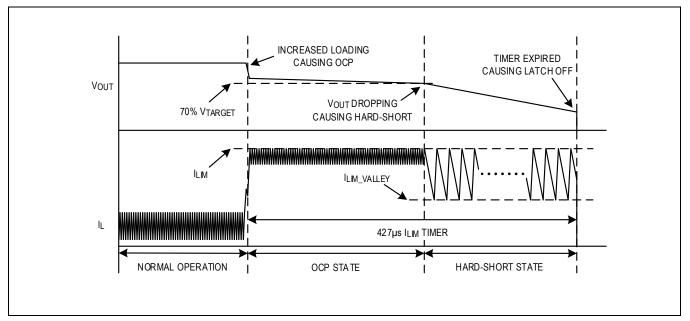

- OCP/HARDSHORT: ILIM Timer > 427µs (See the <u>Overcurrent Protection (OCP)</u> section)

- Start-Up (MAX77857C Only): V<sub>OUT</sub> < POK Level after Soft-Start Timer (t<sub>SS</sub>) Expires (See the <u>Soft-Start</u> section)

The events in this category are associated with potentially hazardous system states. Under immediate shutdown conditions, the IC shuts down the buck-boost regulator output and the I<sup>2</sup>C serial communication bus and resets all registers, until the system recovers from these fault conditions. Under latch-off conditions, the IC shuts down the buck-boost regulator output only, while keeping the I<sup>2</sup>C serial communication bus active and preserving the state of the registers. To recover from latch-off, the fault condition needs to be removed from the system, and a power-cycling EN or IN pin is required. Active discharge is engaged when the buck-boost regulator is shut down from all fault conditions except for thermal shutdown. See the <u>Output Active Discharge</u> section for more information.

#### **Output Active Discharge**

The IC includes an internal switch that provides a path to discharge the energy stored in the output capacitor to PGND. Output active discharge is activated whenever the buck-boost regulator is disabled (by a shutdown event or by any conditions described in the <u>Immediate Shutdown and Latch-Off Conditions</u> section, except for thermal shutdown). The amount of discharge current is 5mA typical when  $V_{OUT}$  is at 15V, and it decreases as  $V_{OUT}$  decreases during the discharge. When the active discharge is enabled, the EN pin control signal is ignored. After  $V_{OUT}$  has dropped below 2.5V (typical) or the 600ms timer has expired, whichever occurs sooner, active discharge is disabled. When the buckboost regulator is operating, the internal discharging switch is disconnected from the output.

#### **Buck-Boost Regulator**

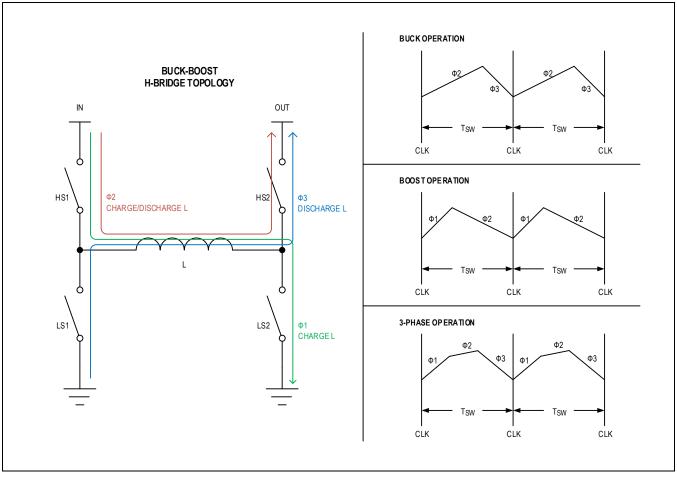

The MAX77857 buck-boost regulator utilizes a four-switch H-bridge configuration and contains buck, boost, or 3-phase operating modes. This topology maintains output voltage regulation over the input voltage range. The buck-boost regulator is ideal in up to 3-cell Li-ion battery-powered applications, providing 3V to 15V of output voltage range. High switching frequency and a unique control algorithm allow for the smallest solution size, low output noise, and the highest efficiency across a wide input voltage and output current range.

#### **Buck-Boost Control Scheme**

The buck-boost regulator operates using a fixed-frequency pulse-width modulated (PWM) control scheme with currentmode compensation. The buck-boost utilizes an H-bridge topology using a single inductor. The default switching

frequency is 1.8MHz. The bitfield FREQ[1:0] sets the switching frequency. The different switching frequencies provide options to avoid EMI-sensitive frequency bands and improve EMI performance.

The H-bridge topology has three switching phases, as shown in *Figure 2*:

- Φ1 switch phase (HS1 = ON, LS2 = ON) stores energy in the inductor and ramps up inductor current at a rate proportional to input voltage divided by inductance: V<sub>IN</sub>/L.

- Φ2 switch phase (HS1 = ON, HS2 = ON) ramps inductor current up (in buck mode) or down (in boost mode) at a rate proportional to the differential voltage across the inductor: (V<sub>IN</sub> - V<sub>OUT</sub>)/L

- Φ3 switch phase (LS1 = ON, HS2 = ON) releases energy from the inductor and ramps down inductor current at a rate proportional to output voltage divided by inductance: -V<sub>OUT</sub>/L.

Boost mode operation ( $V_{IN} < V_{OUT}$ ) utilizes  $\Phi$ 1 and  $\Phi$ 2 within a single clock period. See the representation of the inductor current waveform for boost mode operation in *Figure 2*. Buck mode operation ( $V_{IN} > V_{OUT}$ ) utilizes  $\Phi$ 2 and  $\Phi$ 3 within a single clock period. See the representation of the inductor current waveform for buck mode operation in *Figure 2*. 3-Phase mode operation ( $V_{IN} \approx V_{OUT}$ ) utilizes  $\Phi$ 1,  $\Phi$ 2, and  $\Phi$ 3 within a single clock period. See the representation of the inductor current waveform for See the representation of the inductor current waveform for 3-phase mode operation in *Figure 2*.

Figure 2. Buck-Boost H-Bridge Topology

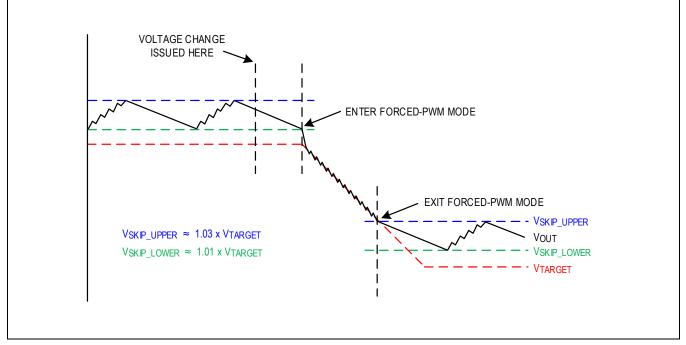

#### SKIP Mode and Forced-PWM (FPWM) Mode

The IC automatically enters SKIP mode operation at no load or light load conditions to improve efficiency. In SKIP mode, output voltage  $V_{OUT}$  is regulated between SKIP mode upper threshold ( $V_{SKIP\_UPPER}$ ) and lower threshold ( $V_{SKIP\_UPPER}$ ), which are typically 3% and 1% above output voltage target ( $V_{TARGET}$ ), respectively. The IC

automatically transitions from SKIP mode to PWM mode depending on output load condition and input/output voltage ratio.

Another way to enable PWM mode operation is by writing 1 to the FPWM[0] bitfield through the I<sup>2</sup>C serial interface. This forces PWM mode operation regardless of output load current. Forced-PWM (FPWM) mode benefits applications where the lowest output ripple is required, whereas SKIP mode helps maximize the buck-boost regulator's efficiency at light loads.

Regardless of the FPWM[0] bitfield setting, the IC enters FPWM mode when  $V_{OUT}$  is changed to a different  $V_{TARGET}$  (DVS) to speed up the transition time. During DVS events that transition from a higher  $V_{OUT}$  to a lower one, the IC enters FPWM mode when  $V_{OUT}$  falls below  $V_{SKIP\_LOWER}$  of the old  $V_{TARGET}$  and stays in FPWM mode until  $V_{OUT}$  falls below  $V_{SKIP\_UPPER}$  of the new  $V_{TARGET}$ . Then  $V_{OUT}$  naturally drops based on the output load condition until it falls to  $V_{SKIP\_LOWER}$ , at which the SKIP mode switching cycle resumes. *Figure 3* depicts such operation during DVS.

Figure 3. SKIP Mode Threshold and FPWM Mode Operation During DVS

### **Output Voltage Configuration**

The IC supports a wide output voltage range between 4.5V and 15V when using internal feedback resistors, and between 3.0V and 15V when using external feedback resistors. The use of internal feedback resistors provides benefits of fewer external components and less overall solution size, while the use of external feedback resistors allows for wider output voltage range and customizable output voltage  $V_{OUT}$  at startup without using the I<sup>2</sup>C serial interface. The selection between using internal or external feedback resistors is configurable by  $R_{SEL}$ . See the <u>SEL Pin Configuration</u> section for more information.

#### Internal Feedback Resistor Configuration

When using internal feedback resistors, the  $V_{OUT}$  range is between 4.5V and 15V in 73.5mV steps. The default  $V_{OUT}$  is 5V ( $V_{REF}$  = 0.333V). Use the appropriate  $R_{SEL}$  value to configure the IC for using internal feedback resistors, and connect the FB pin directly to the OUT pin at the local output capacitor.

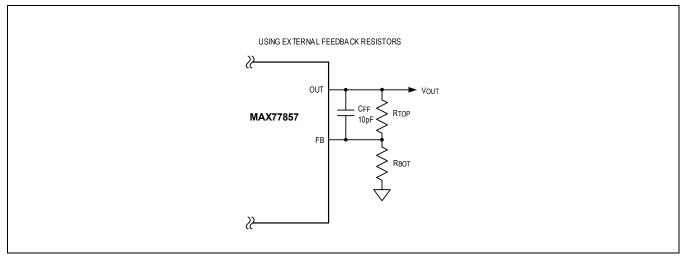

#### **External Feedback Resistor Configuration**

When using external feedback resistors, the  $V_{OUT}$  range is between 3.0V and 15V. The actual output voltage range and step size depend on the external feedback resistor ratio. Use the appropriate  $R_{SEL}$  value to configure the IC for using external feedback resistors, and connect a resistor divider between OUT, FB, and AGND as shown in *Figure 4*. It is also

recommended to add a 10pF feedforward capacitor (C<sub>FF</sub>) in parallel with the top feedback resistor (R<sub>TOP</sub>). Choose R<sub>TOP</sub> (from OUT to FB) between 150k $\Omega$  and 330k $\Omega$ . Resistors with 1% tolerance (or better) are highly recommended to keep the accuracy of V<sub>OUT</sub>. Calculate the value of R<sub>BOT</sub> (from FB to AGND) for the desired V<sub>OUT</sub> at startup with the following equation:

$$R_{BOT} = \frac{R_{TOP} \times V_{REF}}{V_{OUT} - V_{REF}}, V_{OUT} \le V_{OVP}$$

where V<sub>REF</sub> is the default internal reference voltage.

Figure 4. Connecting External Feedback Resistors to MAX77857

With default V<sub>REF</sub> of 0.333V, <u>*Table 1*</u> lists the recommended external feedback resistor values (in E192 series) for common startup output voltages.

| DEFAULT<br>V <sub>REF</sub> (V) | R <sub>TOP</sub> (kΩ) | R <sub>BOT</sub> (kΩ) | STARTUP<br>V <sub>OUT</sub> (V) | PROGRAMMABLE<br>V <sub>OUT</sub> RANGE (V) | V <sub>OUT</sub> STEP SIZE<br>(mV) |

|---------------------------------|-----------------------|-----------------------|---------------------------------|--------------------------------------------|------------------------------------|

|                                 | 160                   | 20                    | 3                               | 3.0 to 9.0                                 | 44.1                               |

|                                 | 178                   | 20                    | 3.3                             | 3.0 to 9.9                                 | 48.5                               |

| 0.000                           | Internal Feed         | back Resistors        | 5                               | 4.5 to 15                                  | 73.5                               |

| 0.333                           | 312                   | 12                    | 9                               | 8.1 to 15                                  | 132.3                              |

|                                 | 232                   | 6.65                  | 12                              | 10.7 to 15                                 | 175.8                              |

|                                 | 234                   | 5.3                   | 15                              | 13.5 to 15                                 | 221.2                              |

### Table 1. Feedback Resistor Value Recommendations

### **Dynamic Voltage Scaling (DVS)**

$V_{OUT}$  is dynamically adjustable by programming  $V_{REF}$  through the I<sup>2</sup>C serial interface. The bitfield VREF[7:0] sets the V<sub>REF</sub>. V<sub>REF</sub> ranges between 0.299V and 1V in 4.9mV steps. When using internal feedback resistors, V<sub>OUT</sub> ranges between 4.5V and 15V in 73.5mV steps, and it can be calculated with the following equation:

$$V_{OUT} = V_{REF} \times 15$$

When using external feedback resistors, the  $V_{OUT}$  range and step size vary based on the external feedback resistor values. The  $V_{OUT}$  step size can be calculated with the following equation:

$$V_{OUT\_STEP} = \left(\frac{4.9mV}{R_{BOT}}\right) \times (R_{BOT} + R_{TOP})$$

To calculate the V<sub>OUT</sub> range, use the following equation and plug in the minimum V<sub>REF</sub> of 0.299V and maximum V<sub>REF</sub> of 1V:

$$V_{OUT} = \left(\frac{V_{REF}}{R_{BOT}}\right) \times (R_{BOT} + R_{TOP}), V_{OUT} \le V_{OVP}$$

Note that  $V_{OUT}$  cannot exceed output voltage range, or it triggers overvoltage protection. See the <u>Overvoltage Protection</u> (<u>OVP</u>) section for more information.

The bitfield SLEW\_RATE[1:0] sets the V<sub>REF</sub> DVS ramp rate ( $\Delta V_{REF}/\Delta t$ ), with the default value of 4/3mV/µs. The actual V<sub>OUT</sub> DVS ramp rate ( $\Delta V_{OUT}/\Delta t$ ) can be calculated from the V<sub>REF</sub> DVS ramp rate ( $\Delta V_{REF}/\Delta t$ ) using the above equations for external feedback resistors. For example, if using internal feedback resistors, the default  $\Delta V_{REF}/\Delta t$  of 4/3mV/µs corresponds to the  $\Delta V_{OUT}/\Delta t$  of 20mV/µs.

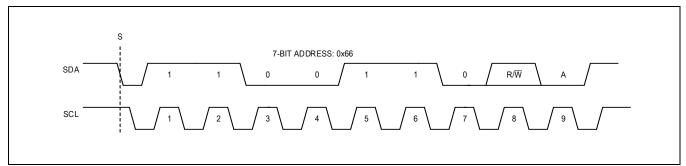

#### **SEL Pin Configuration**

The SEL pin allows a single resistor ( $R_{SEL}$ ) connecting the SEL pin to AGND to configure high side switching current limit threshold ( $I_{LIM}$ ),  $I^2C$  serial interface slave address, and the use of internal or external feedback resistors. Resistors with 1% tolerance (or better) should be used for  $R_{SEL}$ . <u>*Table 2*</u> lists nominal  $R_{SEL}$  values with corresponding settings.

| R <sub>SEL</sub> (Ω) | FEEDBACK<br>RESISTOR<br>SELECTION | TYPICAL<br>I <sub>LIM</sub> (A) | I <sup>2</sup> C SLAVE<br>ADDRESS<br>(7-BIT) | R <sub>SEL</sub> (Ω) | FEEDBACK<br>RESISTOR<br>SELECTION | TYPICAL<br>I <sub>LIM</sub> (A) | I <sup>2</sup> C SLAVE<br>ADDRESS<br>(7-BIT) |

|----------------------|-----------------------------------|---------------------------------|----------------------------------------------|----------------------|-----------------------------------|---------------------------------|----------------------------------------------|

| SHORT TO<br>GND      |                                   |                                 | 110 0110 (0x66)                              | 3740                 |                                   |                                 | 110 0110 (0x66)                              |

| 200                  |                                   | 7.0                             | 110 0111 (0x67)                              | 8060                 |                                   | 7.0                             | 110 0111 (0x67)                              |

| 309                  |                                   |                                 | 110 1110 (0x6E)                              | 12400                |                                   |                                 | 110 1110 (0x6E)                              |

| 422                  |                                   |                                 | 110 1111 (0x6F)                              | 16900                |                                   |                                 | 110 1111 (0x6F)                              |

| 536                  |                                   |                                 | 110 0110 (0x66)                              | 21500                |                                   |                                 | 110 0110 (0x66)                              |

| 649                  |                                   | 5.6                             | 110 0111 (0x67)                              | 26100                |                                   | 5.6                             | 110 0111 (0x67)                              |

| 768                  | Internal                          |                                 | 110 1110 (0x6E)                              | 30900                | External                          | 5.0                             | 110 1110 (0x6E)                              |

| 909                  | feedback                          |                                 | 110 1111 (0x6F)                              | 36500                | feedback                          |                                 | 110 1111 (0x6F)                              |

| 1050                 | resistors                         |                                 | 110 0110 (0x66)                              | 42200                | resistors                         |                                 | 110 0110 (0x66)                              |

| 1210                 |                                   | 2.0                             | 110 0111 (0x67)                              | 48700                |                                   | 2.0                             | 110 0111 (0x67)                              |

| 1400                 |                                   | 3.8                             | 110 1110 (0x6E)                              | 56200                |                                   | 3.8                             | 110 1110 (0x6E)                              |

| 1620                 |                                   |                                 | 110 1111 (0x6F)                              | 64900                |                                   |                                 | 110 1111 (0x6F)                              |

| 1870                 | ]                                 |                                 | 110 0110 (0x66)                              | 75000                |                                   |                                 | 110 0110 (0x66)                              |

| 2150                 | ]                                 | 1.8                             | 110 0111 (0x67)                              | 86600                |                                   | 1 0                             | 110 0111 (0x67)                              |

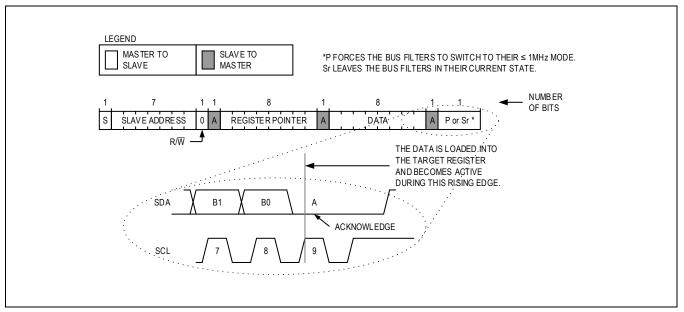

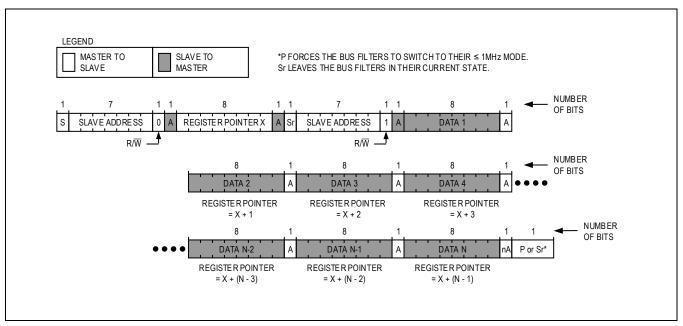

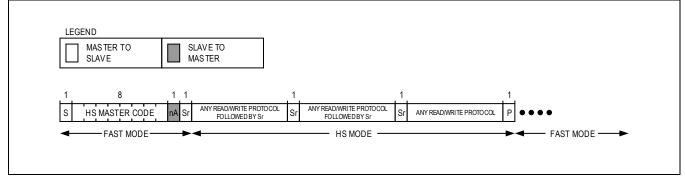

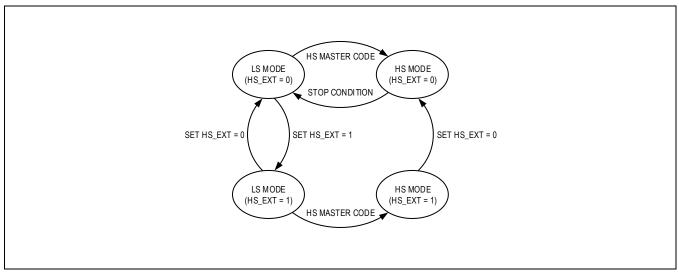

| 2490                 | ]                                 | 1.0                             | 110 1110 (0x6E)                              | 100000               |                                   | 1.8                             | 110 1110 (0x6E)                              |