SLVS566C - MARCH 2005-REVISED MARCH 2013

# BIAS POWER SUPPLY FOR TV AND MONITOR TFT LCD PANELS

Check for Samples: TPS65160, TPS65160A

#### **FEATURES**

- 8-V to 14-V Input Voltage Range

- V<sub>S</sub> Output Voltage Range up to 20 V

- 1% Accurate Boost Converter With 2.8-A Switch Current

- 1.5% accurate 1.8-A Step-Down Converter

- 500-kHz/750-kHz Fixed Switching Frequency

- Negative Charge Pump Driver for VGL

- Positive Charge Pump Driver for VGH

- · Adjustable Sequencing for VGL, VGH

- Gate Drive Signal to Drive External MOSFET

- Internal and Adjustable Soft Start

- Short-Circuit Protection

- 23-V (TPS65160) Overvoltage Protection

- 19.5-V (TPS65160A) Overvoltage Protection

- Thermal Shutdown

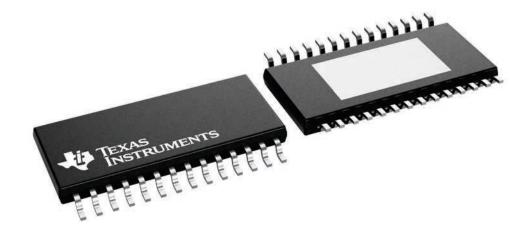

- Available in HTSSOP-28 Package

#### **APPLICATIONS**

TFT LCD Displays for Monitor and LCD TV

## **DESCRIPTION**

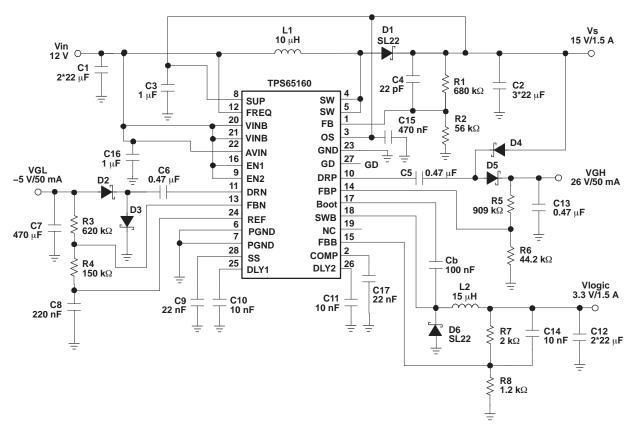

The TPS65160 offers a compact power supply solution to provide all four voltages required by thin-film transistor (TFT) LCD panel. With its high current capabilities, the device is ideal for large screen monitor panels and LCD TV applications.

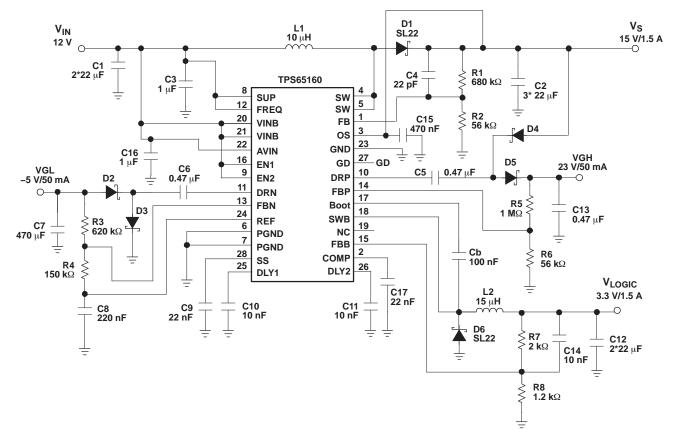

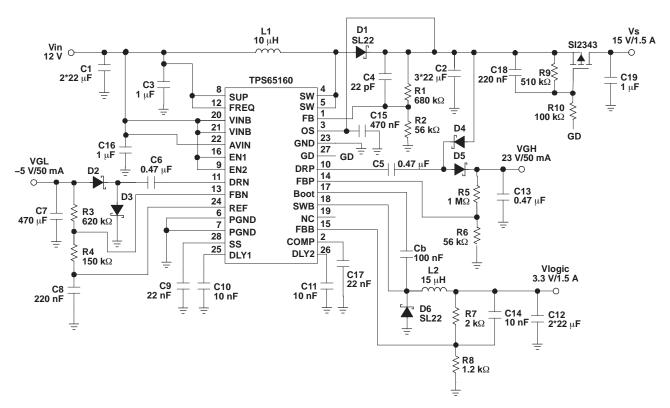

#### TYPICAL APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **DESCRIPTION (CONTINUED)**

The device can be powered directly from a 12-V input voltage generating the bias voltages VGH and VGL, as well as the source voltage  $V_S$  and logic voltage for the LCD panels. The device consists of a boost converter to provide the source voltage  $V_S$  and a step-down converter to provide the logic voltage for the system. A positive and a negative charge-pump driver provide adjustable regulated output voltages VGL and VGH to bias the TFT. Both boost and step-down converters, as well as the charge-pump driver, operate with a fixed switching frequency of 500 kHz or 750 kHz, selectable by the FREQ pin. The TPS65160 includes adjustable power-on sequencing. The device includes safety features like overvoltage protection of the boost converter and short-circuit protection of the buck converter, as well as thermal shutdown. Additionally, the device incorporates a gate drive signal to control an isolation MOSFET switch in series with  $V_S$  or VGH. See the application circuits at the end of this data sheet.

#### ORDERING INFORMATION (1)

| T <sub>A</sub> | UVLO<br>(typ) | Overvoltage protection Vs (typ) | ORDERING     | PACKAGE <sup>(2)</sup> | PACKAGE<br>MARKING |

|----------------|---------------|---------------------------------|--------------|------------------------|--------------------|

| 40°C to 95°C   | 6 V           | 23 V                            | TPS65160PWP  | HTSSOP28 (PWP)         | TPS65160           |

| –40°C to 85°C  | 8 V           | 19.5 V                          | TPS65160APWP | HTSSOP28 (PWP)         | TPS65160A          |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                                               | UNIT                         |

|-----------------------------------------------|------------------------------|

| Voltages on pin VIN, SUP <sup>(2)</sup>       | –0.3 V to 16.5 V             |

| Voltages on pin EN1, EN2, FREQ <sup>(2)</sup> | -0.3 V to 15 V               |

| Voltage on pin SW (2)                         | 25 V                         |

| Voltage on pin SWB <sup>(2)</sup>             | 20 V                         |

| Voltages on pin OS, GD <sup>(2)</sup>         | 25 V                         |

| Continuous power dissipation                  | See Dissipation Rating Table |

| Operating junction temperature                | -40°C to 150°C               |

| stg Storage temperature range                 | −65°C to 150°C               |

| Temperature (soldering, 10 s)                 | 260°C                        |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### (2) All voltage values are with respect to network ground terminal.

#### **DISSIPATION RATINGS**

| PACKAGE       | RTH <sub>JA</sub>                         | T <sub>A</sub> ≤ 25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------------|-------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 28-Pin HTSSOP | 28°C/W (PowerPAD <sup>(1)</sup> soldered) | 3.57 W                                | 1.96 W                                | 1.42 W                                |

(1) See Texas Instruments application report SLMA002 regarding thermal characteristics of the PowerPAD package.

<sup>(2)</sup> The PWP package is available taped and reeled. Add R-suffix to the device type (TPS65160PWPR) to order the device taped and reeled. The TPS65160PWPR package has quantities of 2000 devices per reel. Without suffix, the TPS65160PWP is shipped in tubes with 50 devices per tube.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                    |                                                   |           | MIN | NOM  | MAX  | UNIT |

|--------------------|---------------------------------------------------|-----------|-----|------|------|------|

| Vs                 | Output voltage range of the main boost converter  | TPS65160  |     |      | 20   | V    |

|                    |                                                   | TPS65160A |     |      | 17.5 | V    |

| V <sub>SUP</sub>   | Maximum operating voltage at the charge-pump dri  |           |     | 15   | V    |      |

| 0                  | Input capacitor at VINB                           |           |     | 2x22 |      | μF   |

| C <sub>IN</sub>    | Input capacitor AVIN                              |           |     | 1    |      | μF   |

|                    | Inductor boost converter <sup>(1)</sup>           |           |     | 10   |      |      |

| L                  | Inductor buck converter <sup>(1)</sup>            |           |     | 15   |      | μH   |

| V <sub>LOGIC</sub> | Output voltage range of the step-down converter V | LOGIC     | 1.8 |      | 5.0  | V    |

| 0                  | Output capacitor boost converter                  |           |     | 3x22 |      |      |

| Co                 | Output capacitor buck converter                   |           |     | 2x22 |      | μF   |

| T <sub>A</sub>     | Operating ambient temperature                     |           | -40 |      | 85   | °C   |

| TJ                 | Operating junction temperature                    |           | -40 |      | 125  | °C   |

<sup>(1)</sup> See application section for further information.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12 V, SUP =  $V_{IN}$ , EN1 = EN2 =  $V_{IN}$ ,  $V_S$  = 15 V,  $V_{LOGIC}$  = 3.3 V,  $T_A$  = -40°C to 85°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                   | PARAMETE                         | R                            | TEST CONDITIONS                                                | MIN   | TYP   | MAX   | UNIT |

|-------------------|----------------------------------|------------------------------|----------------------------------------------------------------|-------|-------|-------|------|

| SUPPL             | Y CURRENT                        |                              |                                                                |       |       |       |      |

| .,                | I and the second                 | TPS65160                     |                                                                | 8     |       | 14    | V    |

| $V_{IN}$          | Input voltage range              | TPS65160A                    |                                                                | 9.2   |       | 14    | V    |

| I <sub>QIN</sub>  | Quiescent current into AVIN      |                              | VGH = 2 × V <sub>S</sub> ,<br>Boost converter not<br>switching |       | 0.2   | 2     | mA   |

|                   | Quiescent current into VINB      |                              | VGH = 2 × V <sub>S</sub> ,<br>Buck converter not<br>switching  |       | 0.2   | 0.5   | MA   |

|                   | Shutdown current into AVIN       |                              | EN1 = EN2 = GND                                                |       | 0.1   | 2     |      |

| I <sub>SD</sub>   | Shutdown current into VINB       |                              | EN1 = EN2 = GND                                                |       | 0.1   | 2     | μΑ   |

|                   | Shutdown current into SUP        |                              | EN1 = EN2 = GND                                                |       | 0.1   | 4     | μΑ   |

| I <sub>SUP</sub>  | Quiescent current into SUP       |                              | $VGH = 2 \times V_S$                                           |       | 0.2   | 2     | mA   |

| .,                | Undervoltage lockout threshold   | TPS65160                     | V <sub>IN</sub> falling                                        |       | 6     | 6.4   | V    |

| $V_{UVLO}$        |                                  | TPS65160A                    | V <sub>IN</sub> falling                                        |       | 8     | 8.8   | V    |

| $V_{REF}$         | Reference voltage                |                              |                                                                | 1.203 | 1.213 | 1.223 | V    |

|                   | Thermal shutdown                 |                              | Temperature rising                                             |       | 155   |       | °C   |

|                   | Thermal shutdown hysteresis      |                              |                                                                |       | 5     |       | °C   |

| LOGIC             | SIGNALS EN1, EN2, FREQ           |                              |                                                                |       |       |       |      |

| V <sub>IH</sub>   | High-level input voltage EN1, EN | 2                            |                                                                | 2.0   |       |       | V    |

| V <sub>IL</sub>   | Low-level input voltage EN1, EN  | 2                            |                                                                |       |       | 0.8   | V    |

| V <sub>IH</sub>   | High-level input voltage FREQ    |                              |                                                                | 1.7   |       |       | V    |

| V <sub>IL</sub>   | Low-level input voltage FREQ     | Low-level input voltage FREQ |                                                                |       |       | 0.4   | V    |

| I <sub>I</sub>    | Input leakage current            |                              | EN1 = EN2 = FREQ =<br>GND or V <sub>IN</sub>                   |       | 0.01  | 0.1   | μA   |

| CONTR             | ROL AND SOFT START DLY1, DL      | Y2, SS                       |                                                                |       |       |       |      |

| I <sub>DLY1</sub> | Delay1 charge current            |                              |                                                                | 3.3   | 4.8   | 6.2   | μΑ   |

| I <sub>DLY2</sub> | Delay2 charge current            |                              | V <sub>THRESHOLD</sub> = 1.213 V                               | 3.3   | 4.8   | 6.2   | μΑ   |

| I <sub>SS</sub>   | SS charge current                |                              |                                                                | 6     | 9     | 12    | μΑ   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12 V, SUP =  $V_{IN}$ , EN1 = EN2 =  $V_{IN}$ ,  $V_S$  = 15 V,  $V_{LOGIC}$  = 3.3 V,  $T_A$  = -40°C to 85°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                     | PARAMET                             | TEST CONDITIONS | MIN                                          | TYP    | MAX    | UNIT  |       |

|---------------------|-------------------------------------|-----------------|----------------------------------------------|--------|--------|-------|-------|

| INTERN              | IAL OSCILLATOR                      |                 |                                              | *      |        |       |       |

|                     | Ossillator fra museum               |                 | FREQ = high                                  | 600    | 750    | 900   | 1.11= |

| fosc                | Oscillator frequency                |                 | FREQ = low                                   | 400    | 500    | 600   | kHz   |

| BOOST               | CONVERTER (V <sub>S</sub> )         |                 |                                              |        |        |       |       |

|                     | Outrot valtage serve                | TPS65160        |                                              |        |        | 20    | V     |

| Vs                  | Output voltage range                | TPS65160A       |                                              |        |        | 17.5  | V     |

| $V_{FB}$            | Feedback regulation voltage         |                 |                                              | 1.136  | 1.146  | 1.156 | V     |

| I <sub>FB</sub>     | Feedback input bias current         |                 |                                              |        | 10     | 100   | nA    |

| _                   | N-MOSFET on-resistance (Q1)         |                 | I <sub>SW</sub> = 500 mA                     |        | 100    | 185   | mΩ    |

| r <sub>DS(on)</sub> | P-MOSFET on-resistance (Q2)         |                 | I <sub>SW</sub> = 200 mA                     |        | 10     | 16    | Ω     |

| I <sub>MAX</sub>    | Maximum P-MOSFET peak sw            | itch current    |                                              |        |        | 1     | Α     |

| I <sub>LIM</sub>    | N-MOSFET switch current limit       | (Q1)            |                                              | 2.8    | 3.5    | 4.2   | Α     |

| lleak               | Switch leakage current              |                 | V <sub>SW</sub> = 15 V                       |        | 1      | 10    | μΑ    |

| 1/                  | Overvoltage protection              | TPS65160        | V <sub>OUT</sub> rising                      | 22     | 23     | 24.5  | V     |

| Vovp                |                                     | TPS65160A       | V <sub>OUT</sub> rising                      | 18     | 19.5   | 20.5  | V     |

|                     | Line regulation                     |                 | 10.6 V ≤ Vin ≤ 11.6 V<br>at 1 mA             |        | 0.0008 |       | %/V   |

|                     | Load regulation                     |                 |                                              |        | 0.03   |       | %/A   |

| GATE D              | ORIVE (GD)                          |                 |                                              |        |        |       |       |

| $V_{GD}$            | Gate drive threshold <sup>(1)</sup> |                 | V <sub>FB</sub> rising                       | Vs-12% | Vs-8%  | Vs-4% | V     |

| V <sub>OL</sub>     | GD output low voltage               |                 | $I_{(sink)} = 500 \mu\text{A}$               |        |        | 0.3   | V     |

|                     | GD output leakage current           |                 | VGD = 20 V                                   |        | 0.05   | 1     | μΑ    |

| STEP-D              | OWN CONVERTER (V <sub>LOGIC</sub> ) |                 |                                              |        |        |       |       |

| $V_{LOGIC}$         | Output voltage range                |                 |                                              | 1.8    |        | 5     | V     |

| $V_{FBB}$           | Feedback regulation voltage         |                 |                                              | 1.195  | 1.213  | 1.231 | V     |

| I <sub>FBB</sub>    | Feedback input bias current         |                 |                                              |        | 10     | 100   | nA    |

| r <sub>DS(ON)</sub> | N-MOSFET on-resistance (Q1)         |                 | I <sub>SW</sub> = 500 mA                     |        | 175    | 300   | mΩ    |

| I <sub>LIM</sub>    | N-MOSFET switch current limit (Q1)  |                 |                                              | 2      | 2.6    | 3.3   | Α     |

| lleak               | Switch leakage current              |                 | V <sub>SW</sub> = 0 V                        |        | 1      | 10    | μΑ    |

|                     | Line regulation                     |                 | 10.6 V ≤ V <sub>IN</sub> ≤ 11.6 V<br>at 1 mA |        | 0.0018 |       | %/V   |

|                     | Load regulation                     |                 |                                              |        | 0.037  |       | %/A   |

<sup>(1)</sup> The GD signal is latched low when the main boost converter output V<sub>S</sub> is within regulation. The GD signal is reset when the input voltage or enable of the boost converter is cycled low.

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12 V, SUP =  $V_{IN}$ , EN1 = EN2 =  $V_{IN}$ ,  $V_S$  = 15 V,  $V_{LOGIC}$  = 3.3 V,  $T_A$  = -40°C to 85°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                     | PARAMETER                                                             | TEST CONDITIONS                                                 | MIN   | TYP   | MAX   | UNIT |

|---------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|-------|-------|-------|------|

| NEGAT               | VE CHARGE-PUMP VGL                                                    |                                                                 |       |       |       |      |

| VGL                 | Output voltage range                                                  |                                                                 |       |       | -2    | V    |

| $V_{FBN}$           | Feedback regulation voltage                                           |                                                                 | -36   | 0     | 36    | mV   |

| I <sub>FBN</sub>    | Feedback input bias current                                           |                                                                 |       | 10    | 100   | nA   |

| r <sub>DS(ON)</sub> | Q4 P-Channel switch r <sub>DS(ON)</sub>                               | I <sub>OUT</sub> = 20 mA                                        |       | 4.4   |       | Ω    |

| $V_{DropN}$         | Comment sink contract during (2)                                      | $I_{DRN} = 50 \text{ mA},$<br>$V_{FBN} = V_{FBNnominal} - 5\%$  | 130   |       | 190   |      |

|                     | Current sink voltage drop (2)                                         | $I_{DRN} = 100 \text{ mA},$<br>$V_{FBN} = V_{FBNnominal} - 5\%$ |       | 270   | 420   | mV   |

| POSITI              | E CHARGE-PUMP OUTPUT VGH                                              |                                                                 |       |       |       |      |

| $V_{FBP}$           | Feedback regulation voltage                                           |                                                                 | 1.187 | 1.213 | 1.238 | V    |

| I <sub>FBP</sub>    | Feedback input bias current                                           |                                                                 |       | 10    | 100   | nΑ   |

| r <sub>DS(ON)</sub> | Q3 N-Channel switch r <sub>DS(ON)</sub>                               | I <sub>OUT</sub> = 20 mA                                        |       | 1.1   |       | Ω    |

| , ,                 | Current source voltage drop                                           | $I_{DRP} = 50 \text{ mA},$<br>$V_{FBP} = V_{FBPnominal} - 5\%$  |       | 400   | 680   | \/   |

| $V_{DropP}$         | Current source voltage drop (Vsup – V <sub>DRP</sub> ) <sup>(3)</sup> | $I_{DRP} = 100 \text{ mA},$<br>$V_{FBP} = V_{FBPnominal} - 5\%$ |       | 850   | 1600  | mV   |

- (2) The maximum charge-pump output current is typically half the drive current of the internal current source or current sink.

- (3) The maximum charge-pump output current is typically half the drive current of the internal current source or current sink.

NOTE: The thermally enhanced PowerPAD™ is connected to PGND.

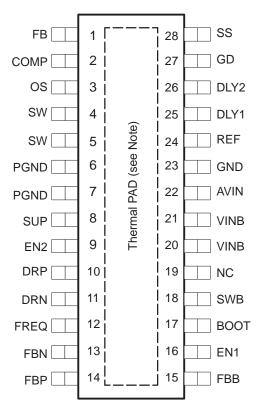

## **TERMINAL FUNCTIONS**

| TERM   | MINAL   |   | TERMINAL FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|---------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | AME NO. |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SUP    | 8       | ı | This is the supply pin of the positive and negative charge-pump driver and can be connected to the input or output of the TPS65160 main boost converter. Because the SUP pin is rated to a maximum voltage of 15 V, it needs to be connected to the input of the TPS65160 for an output voltage greater than 15 V.                                                                                                                                                            |

| FREQ   | 12      | I | Frequency adjust pin. This pin allows setting the switching frequency with a logic level to 500 kHz = low and 750 kHz = high.                                                                                                                                                                                                                                                                                                                                                 |

| AVIN   | 22      | I | Analog input voltage of the device. This is the input for the analog circuits of the device and should be bypassed with a 1-µF ceramic capacitor for good filtering.                                                                                                                                                                                                                                                                                                          |

| VINB   | 20, 21  | I | Power input voltage pin for the buck converter.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EN1    | 16      | I | This is the enable pin of the buck converter and negative charge pump. When this pin is pulled high, the buck converter starts up, and after a delay time set by DLY1, the negative charge pump comes up. This pin must be terminated and not be left floating. A logic high enables the device and a logic low shuts down the device.                                                                                                                                        |

| EN2    | 9       | I | The boost converter starts only with EN1 = high, after the step-down converter is enabled. EN2 is the enable pin of the boost converter and positive charge pump. When this pin is pulled high, the boost converter and positive charge pump starts up after the buck converter is within regulation and a delay time set by DLY2 has passed by. This pin must be terminated and not be left floating. A logic high enables the device and a logic low shuts down the device. |

| DRN    | 11      | 0 | Drive pin of the negative charge pump.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FBN    | 13      | I | Feedback pin of negative charge pump.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| REF    | 24      | 0 | Internal reference output typically 1.213 V                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PGND   | 6, 7    |   | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SS     | 28      | 0 | This pin allows setting the soft-start time for the main boost converter V <sub>S</sub> . Typically a 22-nF capacitor needs to be connected to this pin to set the soft-start time.                                                                                                                                                                                                                                                                                           |

| DLY1   | 25      | 0 | Connecting a capacitor from this pin to GND allows the setting of the delay time between $V_{LOGIC}$ (step-down converter output high) to VGL during start-up.                                                                                                                                                                                                                                                                                                                |

| DLY2   | 26      | 0 | Connecting a capacitor from this pin to GND allows the setting of the delay time between $V_{LOGIC}$ (step-down converter output high) to $V_{S}$ Boost converter and positive charge-pump VGH during start-up.                                                                                                                                                                                                                                                               |

| COMP   | 2       |   | This is the compensation pin for the main boost converter. A small capacitor and, if required, a resistor is connected to this pin.                                                                                                                                                                                                                                                                                                                                           |

| FBB    | 15      | I | Feedback pin of the buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SWB    | 18      | 0 | Switch pin of the buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC     | 19      |   | Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| воот   | 17      | I | N-channel MOSFET gate drive voltage for the buck converter. Connect a capacitor from the switch node SWB to this pin.                                                                                                                                                                                                                                                                                                                                                         |

| FBP    | 14      | I | Feedback pin of positive charge pump.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DRP    | 10      | 0 | Drive pin of the positive charge pump.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GD     | 27      |   | This is the gate drive pin which can be used to control an external MOSFET switch to provide input to output isolation of $V_S$ or VGH. See the circuit diagrams at the end of this data sheet. GD is an open-drain output and is latched low as soon as the boost converter is within 8% of its nominal regulated output voltage. GD goes high impedance when the EN2 input voltage is cycled low.                                                                           |

| GND    | 23      |   | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| os     | 3       | ı | Output sense pin. The OS pin is connected to the internal rectifier switch and overvoltage protection comparator. This pin needs to be connected to the output of the boost converter and cannot be connected to any other voltage rail. Connect a 470-nF capacitor from OS pin to GND to avoid noise coupling into this pin. The PCB trace of the OS pin needs to be wide because it conducts high current.                                                                  |

| FB     | 1       | I | Feedback of the main boost converter generating Vsource (V <sub>S</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                    |

| SW     | 4, 5    | ı | Switch pin of the boost converter generating Vsource (V <sub>S</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                       |

| PowerP | AD      |   | The PowerPAD needs to be connected and soldered to power ground (PGND).                                                                                                                                                                                                                                                                                                                                                                                                       |

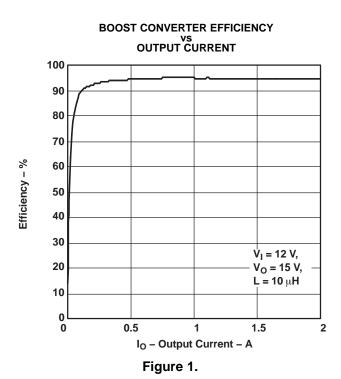

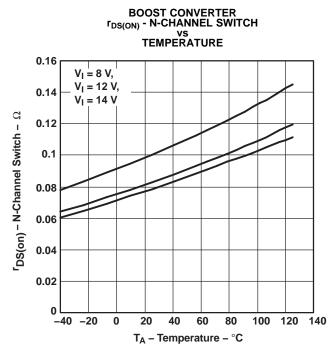

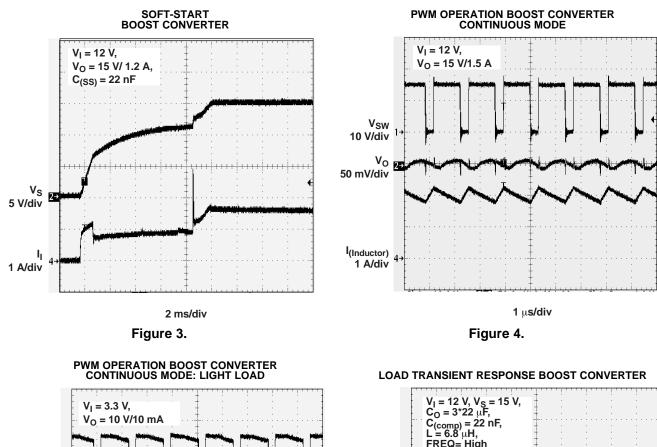

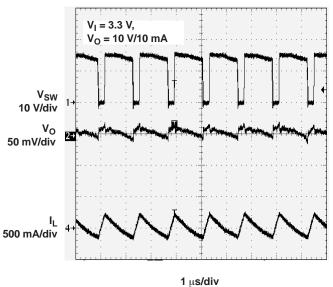

#### **TYPICAL CHARACTERISTICS**

## **Table 1. TABLE OF GRAPHS**

|                        |                                                |                                                              | FIGURE      |

|------------------------|------------------------------------------------|--------------------------------------------------------------|-------------|

| MAIN BO                | OST CONVERTER (Vs)                             |                                                              | <del></del> |

| η                      | Efficiency main boost converter Vs             | vs Load current V <sub>S</sub> = 15 V,V <sub>IN</sub> = 12 V | 1           |

| r <sub>DS(ON)</sub>    | N-channel main switch Q1                       | vs Input voltage and temperature                             | 2           |

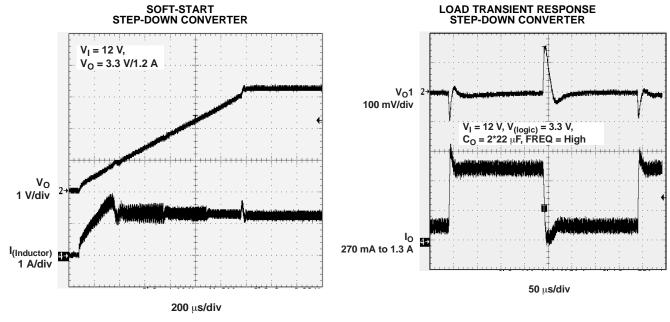

|                        | Soft-start boost converter                     | C <sub>SS</sub> = 22 nF                                      | 3           |

|                        | PWM operation at full-load current             |                                                              | 4           |

|                        | PWM operation at light-load current            |                                                              | 5           |

|                        | Load transient response                        |                                                              | 6           |

| STEP-DO                | WN CONVERTER (Vlogic)                          |                                                              |             |

| η                      | Efficiency main boost converter V <sub>S</sub> | vs Load current V <sub>LOGIC</sub> = 3.3 V,V = 12 V          | 7           |

| IN <sup>r</sup> DS(ON) | N-channel main switch Q1                       |                                                              | 8           |

|                        | PWM operation - continuous mode                |                                                              | 9           |

|                        | PWM operation - discontinuous mode             |                                                              | 10          |

|                        | Soft start                                     |                                                              | 11          |

|                        | Load transient response                        |                                                              | 12          |

| SYSTEM                 | PERFORMANCE                                    |                                                              |             |

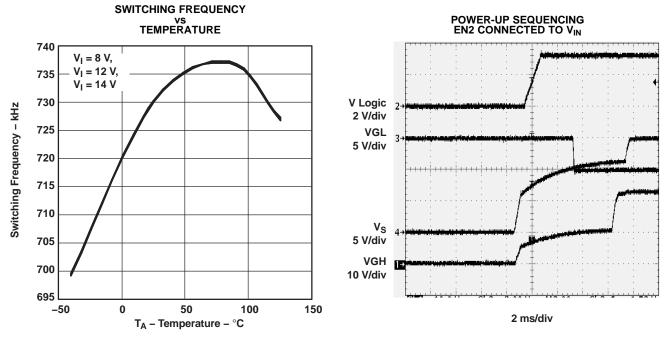

| f <sub>osc</sub>       | Oscillation frequency                          | vs Input voltage and temperature                             | 13          |

|                        | Power-up sequencing                            | EN2 connected to V <sub>IN</sub>                             | 14          |

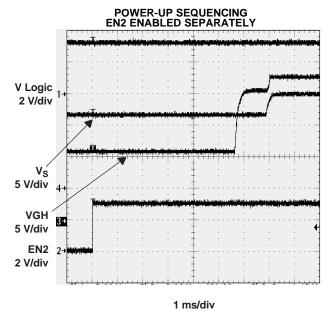

|                        | Power-up sequencing                            | EN2 enabled seperately                                       | 15          |

Figure 2.

Figure 5.

Figure 6.

Figure 11. Figure 12.

Figure 13. Figure 14.

Figure 15.

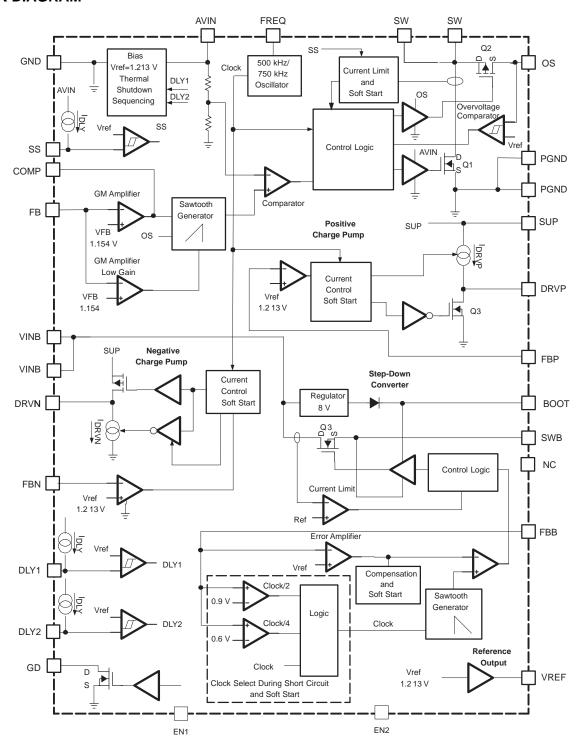

#### **BLOCK DIAGRAM**

#### DETAILED DESCRIPTION

#### **Boost Converter**

The main boost converter operates in pulse-width modulation (PWM) and at a fixed switching frequency of 500 kHz or 750 kHz set by the FREQ pin. The converter uses an unique fast response, voltage-mode controller scheme with input voltage feedforward. This achieves excellent line and load regulation (0.03%-A load regulation typical) and allows the use of small external components. To add higher flexibility to the selection of external component values, the device uses external loop compensation. Although the boost converter looks like a nonsynchronous boost converter topology operating in discontinuous conduction mode at light load, the TPS65160 maintains continuous conduction even at light-load currents. This is achieved with a novel architecture using an external Schottky diode with an integrated MOSFET in parallel connected between SW and OS. See the Functional Block Diagram. The intention of this MOSFET is to allow the current to go negative that occurs at light-load conditions. For this purpose, a small integrated P-Channel MOSFET with typically  $10-\Omega$   $r_{DS(on)}$  is sufficient. When the inductor current is positive, the external Schottky diode with the lower forward voltage conducts the current. This causes the converter to operate with a fixed frequency in continuous conduction mode over the entire load current range. This avoids the ringing on the switch pin as seen with standard nonsynchronous boost converter and allows a simpler compensation for the boost converter.

#### **Soft Start (Boost Converter)**

The main boost converter has an adjustable soft start to prevent high inrush current during start-up. The soft-start time is set by the external capacitor connected to the SS pin. The capacitor connected to the SS pin is charged with a constant current that increases the voltage on the SS pin. The internal current limit is proportional to the voltage on the soft-start pin. When the threshold voltage of the internal soft-start comparator is reached, the full current limit is released. The larger the soft-start capacitor value, the longer the soft-start time.

#### Overvoltage Protection of the Boost Converter

The main boost converter has an overvoltage protection to protect the main switch Q2 at pin (SW) in case the feedback (FB) pin is floating or shorted to GND. In such an event, the output voltage rises and is monitored with the overvoltage protection comparator over the OS pin. See the functional block diagram. As soon as the comparator trips at typically 23 V, TPS65160, (19 V, TPS65160A), the boost converter turns the N-Channel MOSFET switch off. The output voltage falls below the overvoltage threshold and the converter continues to operate.

#### Frequency Select Pin (FREQ)

The frequency select pin (FREQ) allows setting the switching frequency of the entire device to 500 kHz (FREQ = low) or 750 kHz (FREQ = high). A lower switching frequency gives a higher efficiency with a slightly reduced load transient regulation.

#### **Thermal Shutdown**

A thermal shutdown is implemented to prevent damage caused by excessive heat and power dissipation. Typically, the thermal shutdown threshold is 155°C.

#### **Step-Down Converter**

The nonsynchronous step-down converter operates at a fixed switching frequency using a fast response voltage mode topology with input voltage feedforward. This topology allows simple internal compensation, and it is designed to operate with ceramic output capacitors. The converter drives an internal 2.6-A N-channel MOSFET switch. The MOSFET driver is referenced to the switch pin SWB. The N-channel MOSFET requires a gate drive voltage higher than the switch pin to turn the N-Channel MOSFET on. This is accomplished by a bootstrap gate drive circuit running of the step-down converter switch pin. When the switch pin SWB is at ground, the bootstrap capacitor is charged to 8 V. This way, the N-channel gate drive voltage is typically around 8 V.

### **Soft Start (Step-Down Converter)**

To avoid high inrush current during start-up, an internal soft start is implemented in the TPS65160. When the step-down converter is enabled over EN1, its reference voltage slowly rises from zero to its power-good threshold of typically 90% of Vref. When the reference voltage reaches this power-good threshold, the error amplifier is released to its normal operation at its normal duty cycle. To further limit the inrush current during soft start, the converter frequency is set to  $1/4^{th}$  of the switching frequency fs and then 1/2 of fs determined by the comparator that monitors the feedback voltage. See the internal block diagram. Soft start is typically completed within 1 ms.

### **Short-Circuit Protection (Step-Down Converter)**

To limit the short-circuit current, the device has a cycle-by-cycle current limit. To avoid the short-circuit current rising above the internal current limit when the output is shorted to GND, the switching frequency is reduced as well. This is implemented by two comparators monitoring the feedback voltage. The step-down converter switching frequency is reduced to 1/2 of fs when the feedback is below 0.9 V and to 1/4<sup>th</sup> of the switching frequency when the feedback voltage is below 0.6 V.

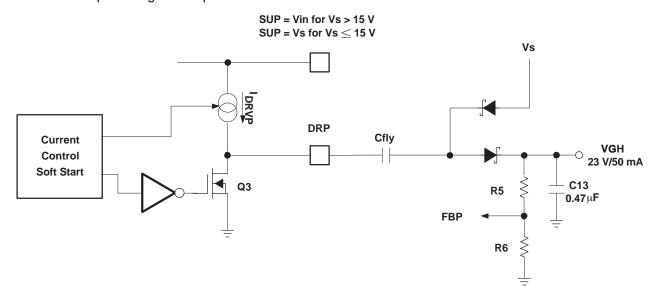

### **Positive Charge Pump**

The positive charge pump provides a regulated output voltage set by the external resistor divider. Figure 16 shows an extract of the positive charge-pump driver circuit. The maximum voltage which can be applied to the charge-pump driver supply pin, SUP, is 15 V. For applications where the boost converter voltage Vs is higher than 15 V, the SUP pin needs to be connected to the input. The operation of the charge-pump driver can be understood best with Figure 16. During the first cycle, Q3 is turned on and the flying capacitor Cfly charges to the source voltage, Vs. During the next clock cycle, Q3 is turned off and the current source charges the drive pin, DRP, up to the supply voltage, VSUP. Because the flying capacitor voltage sits on top of the drive pin voltage, the maximum output voltage is Vsup+Vs.

Figure 16. Extract of the Positive Charge-Pump Driver

If higher output voltages are required, another charge-pump stage can be added to the output.

Setting the output voltage:

$$V_{out} = 1.213 \times \left(1 + \frac{R5}{R6}\right)$$

$$R5 = R6 \times \left(\frac{V_{out}}{V_{FB}} - 1\right) = R6 \times \left(\frac{V_{out}}{1.213} - 1\right)$$

### **Negative Charge Pump**

The negative charge pump provides a regulated output voltage set by the external resistor divider. The negative charge pump operates similar to the positive charge pump with the difference that the voltage on the supply pin, SUP, is inverted. The maximum negative output voltage is  $VGL = (-V_{SUP}) + Vdrop$ . Vdrop is the voltage drop across the external diodes and internal charge-pump MOSFETs. In case VGL needs to be lower than  $-V_S$ , an additional charge-pump stage needs to be added.

Setting the output voltage:

$$V_{out} = -V_{REF} \times \frac{R3}{R4} = -1.213 \text{ V} \times \frac{R3}{R4}$$

$$R3 = R4 \times \frac{|V_{out}|}{V_{REF}} = R4 \times \frac{|V_{out}|}{1.213}$$

The lower feedback resistor value, R4, should be in a range between 40 k $\Omega$  to 120 k $\Omega$  or the overall feedback resistance should be within 500 k $\Omega$  to 1 M $\Omega$ . Smaller values load the reference too heavily, and larger values may cause stability problems. The negative charge pump requires two external Schottky diodes. The peak current rating of the Schottky diode has to be twice the load current of the output. For a 20-mA output current, the dual-Schottky diode BAT54 is a good choice.

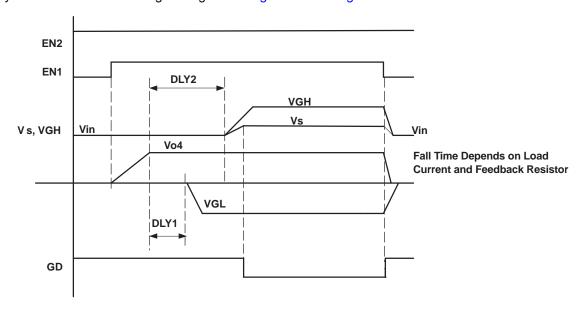

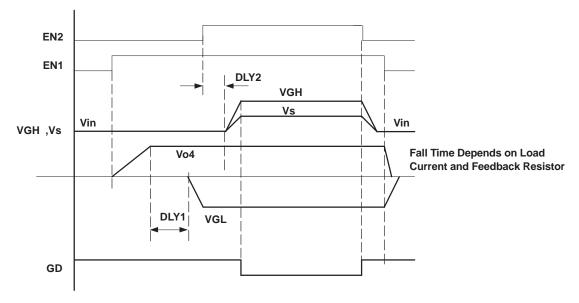

### Power-On Sequencing (EN1, EN2, DLY1, DLY2)

The TPS65160 has an adjustable power-on sequencing set by the capacitors connected to DLY1 and DLY2 and controlled by EN1 and EN2. Pulling EN1 high enables the step-down converter and then the negative charge-pump driver. DLY1 sets the delay time between the step-down converter and negative charge-pump driver. EN2 enables the boost converter and positive charge-pump driver at the same time. DLY2 sets the delay time between the step-down converter Vlogic and the boost converter Vs. This is especially useful to adjust the delay when EN2 is always connected to Vin. If EN2 goes high after the step-down converter is already enabled, then the delay DLY2 starts when EN2 goes high. See Figure 17 and Figure 18.

Figure 17. Power-On Sequencing With EN2 Always High (EN2=Vin)

Figure 18. Power-On Sequencing Using EN1 and EN2

# Setting the Delay Times DLY1, DLY2

Connecting an external capacitor to the DLY1 and DLY2 pins sets the delay time. If no delay time is required, these pins can be left open. To set the delay time, the external capacitor connected to DLY1 and DLY2 is charged with a constant current source of typically 4.8  $\mu$ A. The delay time is terminated when the capacitor voltage has reached the internal reference voltage of Vref = 1.213 V. The external delay capacitor is calculated:

$$C_{dly} = \frac{4.8 \mu A \times td}{Vref} = \frac{4.8 \mu A \times td}{1.213 V}$$

with td = Desired delay time

Example for setting a delay time of 2.3 mS:

$$C_{dly} = = \frac{4.8 \,\mu\text{A} \times 2.3 \,\text{ms}}{1.213 \,\text{V}} = 9.4 \,\text{nF} \Rightarrow \text{Cdly} = 10 \,\text{nF}$$

#### Gate Drive Pin (GD)

This is an open-drain output that goes low when the boost converter, Vs, is within regulation. The gate drive pin GD remains low until the input voltage or enable EN2 is cycled to ground.

#### **Undervoltage Lockout**

To avoid misoperation of the device at low input voltages, an undervoltage lockout is included which shuts down the device at voltages lower than 6 V.

## **Input Capacitor Selection**

For good input voltage filtering, low ESR ceramic capacitors are recommended. The TPS65160 has an analog input, AVIN, and two input pins for the buck converter VINB. A 1-µF input capacitor should be connected directly from the AVIN to GND. Two 22-µF ceramic capacitors are connected in parallel from the buck converter input VINB to GND. For better input voltage filtering, the input capacitor values can be increased. See Table 2 and the Application Information section for input capacitor recommendations.

#### **Table 2. Input Capacitor Selection**

| CAPACITOR  | VOLTAGE RATING | COMPONENT SUPPLIER        | COMMENTS               |

|------------|----------------|---------------------------|------------------------|

| 22 μF/1210 | 16 V           | Taiyo Yuden EMK325BY226MM | C <sub>IN</sub> (VINB) |

| 1 μF/1206  | 16 V           | Taiyo Yuden EMK316BJ106KL | C <sub>IN</sub> (AVIN) |

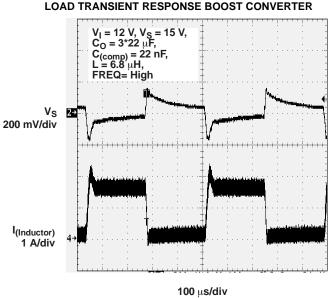

### **Boost Converter Design Procedure**

The first step in the design procedure is to verify whether the maximum possible output current of the boost converter supports the specific application requirements. A simple approach is to use the converter efficiency, by taking the efficiency numbers from the provided efficiency curves or to use a worst-case assumption for the expected efficiency, e.g., 80%.

1. Duty Cycle:

$$D = 1 - \frac{Vin \times \eta}{Vout}$$

2. Maximum output current:

$$I_{avg} = (1 - D) \times Isw = \frac{Vin}{Vout} \times 2.8 \text{ A with Isw} = minimum switch current of the TPS65160 (2.8 A).}$$

3. Peak switch current:

$$I_{swpeak} = \frac{Vin \times D}{2 \times fs \times L} + \frac{I_{out}}{1 - D}$$

With

Isw = converter switch current (minimum switch current limit = 2.8 A)

fs = converter switching frequency (typical 500 kHz/750 kHz)

L = Selected inductor value

$\eta$  = Estimated converter efficiency (use the number from the efficiency curves or 0.8 as an estimation)

The peak switch current is the steady-state peak switch current that the integrated switch, inductor, and external Schottky diode must be able to handle. The calculation must be done for the minimum input voltage where the peak switch current is highest.

## **Inductor Selection (Boost Converter)**

The TPS65160 operates typically with a 10-µH inductor. Other possible inductor values are 6.8-µH or 22-µH. The main parameter for the inductor selection is the saturation current of the inductor, which should be higher than the peak switch current as previously calculated, with additional margin to cover for heavy load transients. The alternative, more conservative approach, is to choose the inductor with saturation current at least as high as the typical switch current limit of 3.5 A. The second important parameter is the inductor DC resistance. Usually, the lower the DC resistance the higher the efficiency. The efficiency difference between different inductors can vary between 2% to 10%. Possible inductors are shown in Table 3.

**Table 3. Inductor Selection (Boost Converter)**

| INDUCTOR VALUE | COMPONENT SUPPLIER           | DIMENSIONS in mm               | Isat/DCR     |

|----------------|------------------------------|--------------------------------|--------------|

| 22 µH          | Coilcraft MSS1038-103NX      | $10,2 \times 10,2 \times 3,6$  | 2.9 A/73 mΩ  |

| 22 µH          | Coilcraft DO3316-103         | $12,85 \times 9,4 \times 5,21$ | 3.8 A/38 mΩ  |

| 10 μH          | Sumida CDRH8D43-100          | $8.3 \times 8.3 \times 4.5$    | 4.0 A/29 mΩ  |

| 10 μH          | Sumida CDH74-100             | $7.3 \times 8.0 \times 5.2$    | 2.75 A/43 mΩ |

| 10 μH          | Coilcraft MSS1038-103NX      | $10,2 \times 10,2 \times 3,6$  | 4.4 A/35 mΩ  |

| 6.8 µH         | Wuerth Elektronik 7447789006 | $7,3 \times 7,3 \times 3,2$    | 2.5 A/44 mΩ  |

#### **Output Capacitor Selection (Boost Converter)**

For best output voltage filtering, a low ESR output capacitor is recommended. Ceramic capacitors have a low ESR value and work best with the TPS65160. Usually, three 22-µF ceramic output capacitors in parallel are sufficient for most applications. If a lower voltage drop during load transients is required, more output capacitance can be added. See Table 4 for the selection of the output capacitor.

#### **Table 4. Output Capacitor Selection (Boost Converter)**

| CAPACITOR  | VOLTAGE RATING | COMPONENT SUPPLIER        |

|------------|----------------|---------------------------|

| 22 μF/1812 | 16 V           | Taiyo Yuden EMK432BJ226MM |

## **Rectifier Diode Selection (Boost Converter)**

To achieve high efficiency, a Schottky diode should be used. The reverse voltage rating should be higher than the maximum output voltage of the converter. The average rectified forward-current rating needed for the Schottky diode is calculated as the off-time of the converter times the maximum switch current of the TPS65160:

$$D = 1 - \frac{Vout}{Vin}$$

$$I_{avg} = (1 - D) \times Isw = \frac{Vin}{Vout} \times 2.8 \text{ A with Isw} = minimum switch current of the TPS65160 (2.8 A).}$$

Usually, a Schottky diode with 2-A maximum average rectified forward-current rating is sufficient for most applications. Secondly, the Schottky rectifier has to be able to dissipate the power. The dissipated power is the average rectified forward current times the diode forward voltage.

$P_D = I_{avg} \times V_F = Isw \times (1 \times D) \times V_F$  (with Isw = minimum switch current of the TPS65160 (2.6 A)

Table 5. Rectifier Diode Selection (Boost Converter)

| CURRENT RATING I <sub>avg</sub> | Vr   | V <sub>forward</sub> | Rθ <sub>JA</sub> | SIZE | COMPONENT SUPPLIER               |

|---------------------------------|------|----------------------|------------------|------|----------------------------------|

| 3 A                             | 20 V | 0.36 at 3 A          | 46°C/W           | SMC  | MBRS320, International Rectifier |

| 2 A                             | 20 V | 0.44 V at 3 A        | 75°C/W           | SMB  | SL22, Vishay Semiconductor       |

| 2 A                             | 20 V | 0.5 at 2 A           | 75°C/W           | SMB  | SS22, Fairchild Semiconductor    |

## Setting the Output Voltage and Selecting the Feedforward Capacitor (Boost Converter)

The output voltage is set by the external resistor divider and is calculated as:

$$V_{out} = 1.146 V \times \left(1 + \frac{R1}{R2}\right)$$

Across the upper resistor, a bypass capacitor is required to achieve a good load transients response and to have a stable converter loop. Together with R1, the bypass capacitor Cff sets a zero in the control loop. Depending on the inductor value, the zero frequency needs to be set. For a 6.8- $\mu$ H or 10- $\mu$ H inductor, fz = 10 kHz and for a 22- $\mu$ H inductor, fz = 7 kHz.

$$Cff = \frac{1}{2 \times \pi \times f_{Z} \times R1} = \frac{1}{2 \times \pi \times 10 \text{ kHz} \times R1}$$

A value coming closest to the calculated value should be used.

## **Compensation (COMP) (Boost Converter)**

The regulator loop can be compensated by adjusting the external components connected to the COMP pin. The COMP pin is the output of the internal transconductance error amplifier. A single capacitor connected to this pin sets the low-frequency gain. Usually, a 22-nF capacitor is sufficient for most of the applications. Adding a series resistor sets an additional zero and increases the high-frequency gain. The following formula calculates at what frequency the resistor increases the high-frequency gain.

$$f_{Z} = \frac{1}{2 \times \pi \times Cc \times Rc}$$

Lower input voltages require a higher gain and therefore a lower compensation capacitor value.

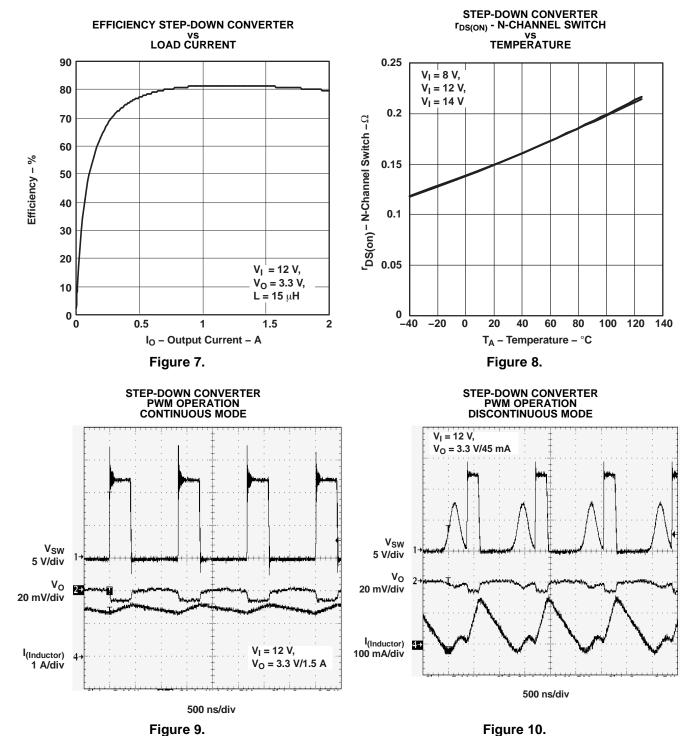

### Step-Down Converter Design Procedure

#### **Setting the Output Voltage**

The step-down converter uses an external voltage divider to set the output voltage. The output voltage is calculated as:

$$V_{\text{out}} = 1.213 \text{ V} \times \left(1 + \frac{\text{R1}}{\text{R2}}\right)$$

with R1 as 1.2 k $\Omega$ , and internal reference voltage V(ref)typ = 1.213 V

At load current <1 mA, the device operates in discontinuous conduction mode. When the load current is reduced to zero, the output voltage rises slightly above the nominal output voltage. At zero load current, the device skips clock cycles but does not completely stop switching; thus, the output voltage sits slightly higher than the nominal output voltage. Therefore, the lower feedback resistor is selected to be around 1.2 k $\Omega$  to always have around 1-mA minimum load current.

#### **Selecting the Feedforward Capacitor**

The feedforward capacitor across the upper feedback resistor divider sets a zero in the converter loop transfer function. For a 15- $\mu$ H inductor, fz = 8 kHz and when a 22- $\mu$ H inductor is used, fz = 17 kHz.

(Example for the 3.3-V output)

$$C_Z = \frac{1}{2 \times \pi \times 8 \text{ kHz} \times \text{R1}} = \frac{1}{2 \times \pi \times 8 \text{ kHz} \times 2 \text{k}\Omega} = 9.9 \text{ nF} \approx 10 \text{ nF}$$

Usually a capacitor value closest to the calculated value is selected.

#### Inductor Selection (Step-Down Converter)

The TPS65160 operates typically with a 15-µH inductor value. For high efficiencies the inductor should have a low DC resistance to minimize conduction losses. This needs to be considered when selecting the appropriate inductor. In order to avoid saturation of the inductor, the inductor should be rated at least for the maximum output current of the converter, plus the inductor ripple current that is calculated as:

$$\Delta I_{L} = Vout \times \frac{1 - \frac{Vout}{Vin}}{L \times f}$$

$I_{Lmax} = I_{outmax} + \frac{\Delta I_{L}}{2}$

With:

f = Switching frequency (750 kHz, 500 kHz minimal)

$L = Inductor value (typically 15 \mu H)$

$\Delta I_1$  = Peak-to-peak inductor ripple current

I<sub>Lmax</sub> = Maximum inductor current

The highest inductor current occurs at maximum Vin. A more conservative approach is to select the inductor current rating just for the typical switch current of 2.6 A.

Table 6. Inductor Selection (Step-Down Converter)

| INDUCTOR VALUE | COMPONENT SUPPLIER      | DIMENSIONS in mm              | Isat/DCR      |

|----------------|-------------------------|-------------------------------|---------------|

| 15 µH          | Sumida CDRH8D28-150     | $8,3 \times 8,3 \times 3,0$   | 1.9 A/53 mΩ   |

| 15 µH          | Coilcraft MSS1038-153NX | $10.2 \times 10.2 \times 3.6$ | 3.6 A/50 mΩ   |

| 15 µH          | Wuerth 7447789115       | $7.3 \times 7.3 \times 3.2$   | 1.75 A/100 mΩ |

#### Rectifier Diode Selection (Step-Down Converter)

To achieve high efficiency, a Schottky diode should be used. The reverse voltage rating should be higher than the maximum output voltage of the step-down converter. The averaged rectified forward current at which the Schottky diode needs to be rated is calculated as the off-time of the step-down converter times the maximum switch current of the TPS65160:

$$D = 1 - \frac{Vout}{Vin}$$

$$I_{avg} = (1 - D) \times Isw = 1 - \frac{Vout}{Vin} \times 2 A$$

with Isw = minimum switch current of the TPS65160 (2 A)

Usually, a Schottky diode with 1.5-A or 2-A maximum average rectified forward current rating is sufficient for most applications. Secondly, the Schottky rectifier has to be able to dissipate the power. The dissipated power is the average rectified forward current times the diode forward voltage.

$P_D = I_{avg} \times V_F = Isw \times (1 - D) \times V_F$  with Isw = minimum switch current of the TPS65160 (2 A).

Table 7. Rectifier Diode Selection (Step-Down Converter)

| CURRENT RATING I <sub>avg</sub> | Vr   | V <sub>forward</sub> | $R\theta_{JA}$ | SIZE | COMPONENT SUPPLIER               |

|---------------------------------|------|----------------------|----------------|------|----------------------------------|

| 3 A                             | 20 V | 0.36 V at 3 A        | 46°C/W         | SMC  | MBRS320, International Rectifier |

| 2 A                             | 20 V | 0.44 V at 2 A        | 75°C/W         | SMB  | SL22, Vishay Semiconductor       |

| 2 A                             | 20 V | 0.5 V at 2 A         | 75°C/W         | SMB  | SS22, Fairchild Semiconductor    |

| 1.5 A                           | 20 V | 0.445 V at 1.0 A     | 88°C/W         | SMA  | SL12, Vishay Semiconductor       |

#### **Output Capacitor Selection (Step-Down Converter)**

The device is designed to work with ceramic output capacitors. When using a 15-µH inductor, two 22-µF ceramic output capacitors are recommended. More capacitance can be added to improve the load transient response.

**Table 8. Output Selection (Boost Converter)**

| CAPACITOR  | VOLTAGE RATING | COMPONENT SUPPLIER        |

|------------|----------------|---------------------------|

| 22 μF/0805 | 6.3 V          | Taiyo Yuden JMK212BJ226MG |

### **Layout Consideration**

The PCB layout is an important step in the power supply design. An incorrect layout could cause converter instability, load regulation problems, noise, and EMI issues. Especially with a switching dc-dc converter at high load currents, too-thin PCB traces can cause significant voltage spikes. Good grounding becomes important as well. If possible, a common ground plane to minimize ground shifts between analog (GND) and power ground (PGND) is recommended. Additionally, the following PCB design layout guidelines are recommended for the TPS65160:

- 1. Separate the power supply traces for AVIN and VINB, and use separate bypass capacitors.

- 2. Use a short and wide trace to connect the OS pin to the output of the boost converter.

- 3. To minimize noise coupling into the OS pin, use a 470-nF bypass capacitor to GND.

- 4. Use short traces for the charge-pump drive pins (DRN, DRP) of VGH and VGL because these traces carry switching waveforms.

- 5. Place the flying capacitors as close as possible to the DRP and DRN pin, avoiding a high voltage spike at these pins.

- 6. Place the Schottky diodes as close as possible to the IC, respective to the flying capacitors connected to the DRP and DRN.

- 7. Route the feedback network of the negative charge pump away from the drive pin traces (DRN) of the negative charge pump. This avoids parasitic coupling into the feedback network of the negative charge pump giving good output voltage accuracy and load ragulation. To do this, use the FREQ pin and trace to isolate DRN from FBN.

#### **APPLICATION INFORMATION**

Figure 19. Positive-Charge Pump Doubler Running From the Output  $V_S$  (SUP =  $V_S$ )

Required When Higher VGH Voltages Are Needed.

Figure 20. Driving an Isolation FET for V<sub>S</sub> using the GD Pin

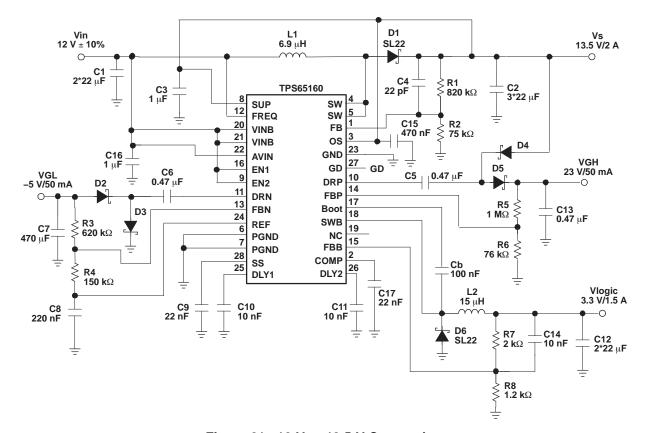

Figure 21. 12-V to 13.5-V Conversion

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |               |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| TPS65160APWP     | ACTIVE        | HTSSOP       | PWP                | 28   | 50             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPS65160A            | Samples |

| TPS65160APWPR    | ACTIVE        | HTSSOP       | PWP                | 28   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPS65160A            | Samples |

| TPS65160PWP      | ACTIVE        | HTSSOP       | PWP                | 28   | 50             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPS65160             | Samples |

| TPS65160PWPR     | ACTIVE        | HTSSOP       | PWP                | 28   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPS65160             | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

## PACKAGE OPTION ADDENDUM

10-Dec-2020

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Jan-2022

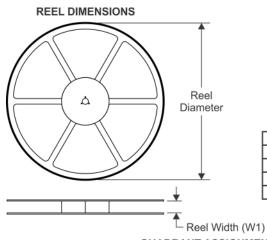

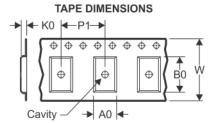

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

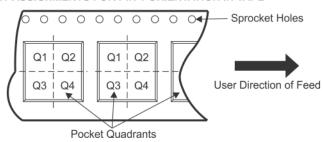

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

## \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS65160APWPR | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

| TPS65160PWPR  | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

www.ti.com 5-Jan-2022

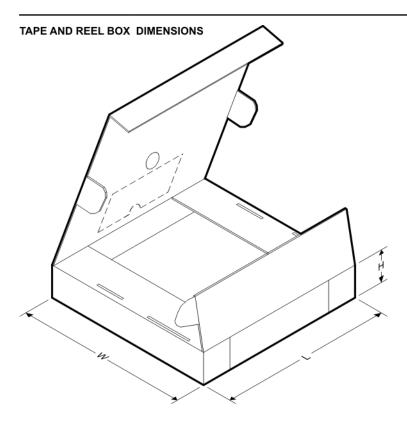

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS65160APWPR | HTSSOP       | PWP             | 28   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS65160PWPR  | HTSSOP       | PWP             | 28   | 2000 | 350.0       | 350.0      | 43.0        |

# PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jan-2022

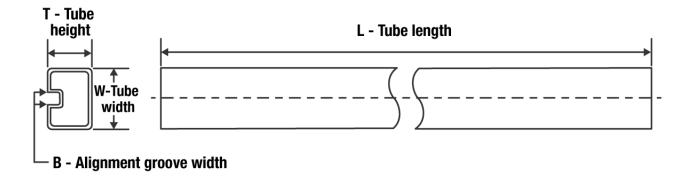

## **TUBE**

#### \*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPS65160APWP | PWP          | HTSSOP       | 28   | 50  | 530    | 10.2   | 3600   | 3.5    |

| TPS65160PWP  | PWP          | HTSSOP       | 28   | 50  | 530    | 10.2   | 3600   | 3.5    |

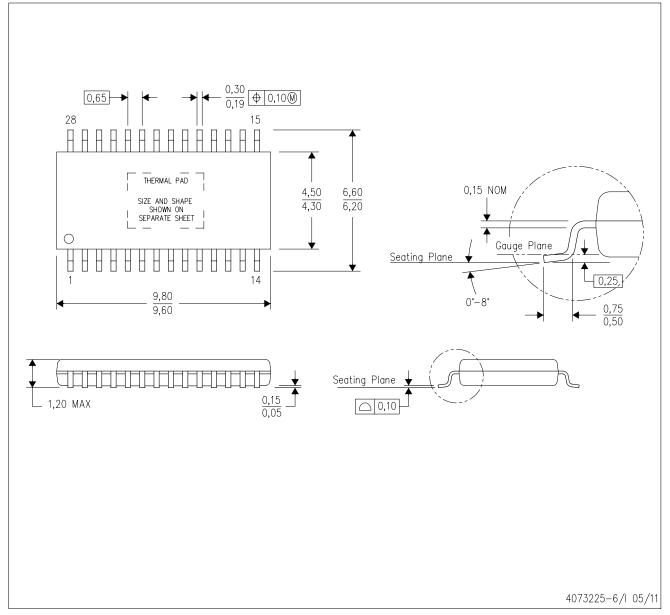

4.4 x 9.7, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

www.ti.com

PWP (R-PDSO-G28)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

4206332-33/AO 01/16

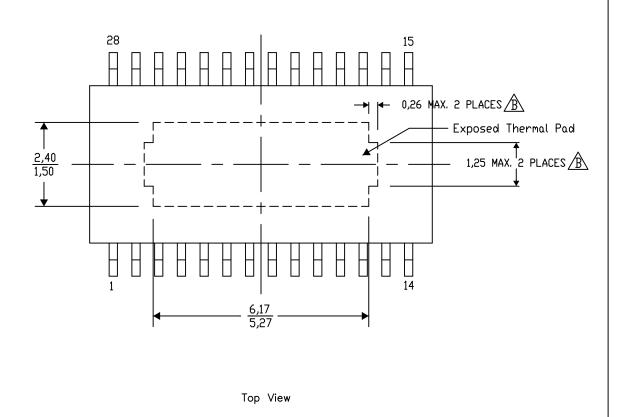

# PWP (R-PDSO-G28) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

B. Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

Exposed Thermal Pad Dimensions

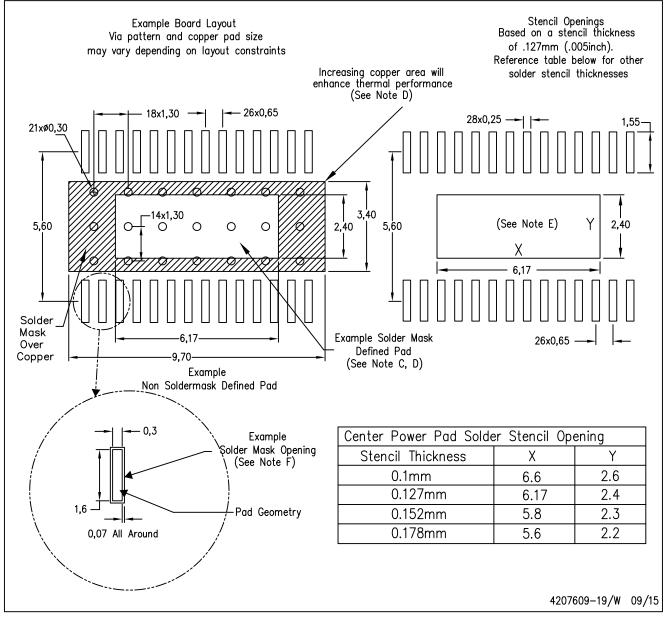

# PWP (R-PDSO-G28)

# PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets.

- E. For specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated