# **IQS680** Datasheet

Combination sensor with dual channel capacitive proximity/touch, Pyroelectric Infrared Radial sensor and metal detection capabilities

The IQS680 ProxFusion<sup>®</sup> IC is a multifunctional Capacitance, Pyroelectric Infrared Radial (PIR) & Inductance sensor designed for applications such as domestic energy efficient lighting applications with movement detection. The IQS680 is an ultra-low power solution designed for short or long term activations through any of the sensing channels. The IQS680 operates standalone or via the I<sup>2</sup>C protocol and custom configurations are stored in an on-chip EEPROM.

### **Features**

#### Unique combination of Sensors:

- Capacitive Sensing

- Inductive Sensing

- PIR Sensing

#### Capacitive Sensing

- 2pF to 200pF external capacitive load capability

- Fully adjustable sensing options

- o Mutual- or self-capacitance.

#### Inductive Sensing

- Distinguish between ferrous and nonferrous metals

- Only external sense coil required (PCB) trace)

- PIR Sensing:

- o DSP algorithm for long range movement detection.

- o Automatic drift compensation.

- Multiple integrated UI's

- Automatic Tuning Implementation (ATI) performance enhancement (10bit ATI)

- **EEPROM** included on-chip for calibration data and settings.

- Minimal external components

- Standard I<sup>2</sup>C interface (polling with sub 1ms) clock stretching)

- Optional RDY indication for standalone mode operation

- Low Power Consumption:

- 300uA (100 Hz response)

- 10uA (10 Hz response)

- Supply Voltage: 1.8V to 3.6V

- Under Cabinet Lighting (UCL)

- Standard PIR sensor cost reduction

- Smart Lights

- Night Lights

- Battery powered PIR sensors solutions

- Movement detection

#### Figure 1: Under cabinet UI (PIR and Prox)

#### Figure 2: In cabinet UI (Inductive sensor)

Representations only, not actual markings

#### IQ Switch<sup>®</sup> ProxFusion<sup>®</sup> Series

### **Table of Contents**

| 1 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                                          |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|   | 1.1 ProxFusion <sup>®</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                                                          |

|   | 1.2 PACKAGING AND PIN-OUT                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                                                                                          |

|   | TABLE 1-1: PIN-OUT DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6                                                                                                                          |

|   | 1.3 REFERENCE SCHEMATIC                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                                          |

|   | 1.4 SENSOR CHANNEL COMBINATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                                                                                                          |

|   | TABLE 1-2         SENSOR - CHANNEL ALLOCATION                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                                                                                                          |

|   | 1.5 FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                                                                                                                          |

|   | 1.6 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                                                                                                          |

| 2 | USER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

|   | 2.1 MOVEMENT DETECTION UI                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

|   | 2.2 METAL DETECTION UI                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

|   | 2.3 EVENT OUTPUT RESPONSES                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

| 3 | INDUCTIVE SENSING                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                                                                                         |

|   | 3.1 Channel specifications                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   | TABLE 3-1         INDUCTIVE SENSOR – CHANNEL ALLOCATION                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            |

|   | 3.2 HARDWARE CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   | TABLE 3-2         INDUCTIVE COIL HARDWARE DESCRIPTION.                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

|   | 3.3 Register configuration                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   | INDUCTIVE SENSING SETTINGS REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

|   | 3.4 Sensor data output and flags                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                                                                                         |

| 4 | PYROELECTRIC INFRARED RADIAL (PIR) SENSING                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                                         |

|   | 4.1 Channel Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   | TABLE 4-1         PIR sensor – channel allocation                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                         |

|   | 4.2 HARDWARE CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                                         |

|   | TABLE 4-2         PIR HARDWARE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   | 4.3 Register configuration                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|   | PIR AND CAPACITIVE SENSING SETTINGS REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

|   | 4.4 Sensor data output and flags                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 5 | USER CONFIGURABLE SETTINGS (UCS)                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                                                         |

| 5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 5 | 5.1 SAMPLING FREQUENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| 5 | TABLE 5-1         SAMPLE FREQUENCY OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

| 5 | TABLE 5-1     SAMPLE FREQUENCY OPTIONS       5.2     INPUT OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 5 | TABLE 5-1       SAMPLE FREQUENCY OPTIONS         5.2       INPUT OPTIONS         TABLE 5-2       USER INPUT OPTIONS                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 5 | TABLE 5-1       SAMPLE FREQUENCY OPTIONS         5.2       INPUT OPTIONS         TABLE 5-2       USER INPUT OPTIONS         5.3       OUTPUT FORMAT OPTIONS                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 5 | TABLE 5-1       SAMPLE FREQUENCY OPTIONS         5.2       INPUT OPTIONS         TABLE 5-2       USER INPUT OPTIONS         5.3       OUTPUT FORMAT OPTIONS         TABLE 5-3: OUTPUT FORMATS                                                                                                                                                                                                                                                                          |                                                                                                                            |

| 5 | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODES                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 5 | TABLE 5-1       SAMPLE FREQUENCY OPTIONS         5.2       INPUT OPTIONS         TABLE 5-2       USER INPUT OPTIONS         5.3       OUTPUT FORMAT OPTIONS         TABLE 5-3: OUTPUT FORMATS         5.4       LIGHTING MODES         TABLE 5-4: OUTPUT MODES                                                                                                                                                                                                         |                                                                                                                            |

| 5 | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 5 | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD                                                                                                                                                                                                                                                                 | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20                                                             |

| 5 | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD                                                                                                                                                                                                                                               | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20<br>20                                                       |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLDS                                                                                                                                                                                                                        | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20<br>20<br>20<br>20                                           |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLD5.9PIR ATI THRESHOLD                                                                                                                                                                                                     | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>20                                     |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLDS5.9PIR ATI THRESHOLDTABLE 5-5: PIR DEVIATION THRESHOLDS                                                                                                                                                                 | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLDS5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS                                                                                                                                                                            | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODES5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLDS5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR TRIGGER TIME OUT                                                                                                                                   |                                                                                                                            |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLD5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR TRIGGER TIME OUT5.12MINIMUM PIR STABILIZATION TIME                                                                                                                   |                                                                                                                            |

| 6 | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLDS5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR TRIGGER TIME OUT5.12MINIMUM PIR STABILIZATION TIMEDEVICE CLOCK, POWER MANAGEMENT AND MODE OPERATION                                                                 |                                                                                                                            |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODESTABLE 5-4: OUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLD5.9PIR ATI THRESHOLD5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR TRIGGER TIME OUT5.12MINIMUM PIR STABILIZATION TIME6.1DEVICE MAIN OSCILLATOR                                                                      |                                                                                                                            |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODES5.4CUTPUT MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLD5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR RIGER TIME OUT5.12MINIMUM PIR STABILIZATION TIME6.1DEVICE CLOCK, POWER MANAGEMENT AND MODE OPERATION6.2DEVICE MODES                                                          | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 |

| 6 | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMAT OPTIONS5.4LIGHTING MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLD5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR TRIGGER TIME OUT5.12MINIMUM PIR STABILIZATION TIME6.1DEVICE CLOCK, POWER MANAGEMENT AND MODE OPERATION6.2DEVICE MODES6.3STREAMING AND STANDALONE MODE:                               |                                                                                                                            |

|   | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMATS5.4LIGHTING MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLD5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR TRIGGER TIME OUT5.12MINIMUM PIR STABILIZATION TIME <b>DEVICE CLOCK, POWER MANAGEMENT AND MODE OPERATION</b> 6.1DEVICE MAIN OSCILLATOR6.3STREAMING AND STANDALONE MODE: <b>COMMUNICATION</b> |                                                                                                                            |

| 6 | TABLE 5-1SAMPLE FREQUENCY OPTIONS5.2INPUT OPTIONSTABLE 5-2USER INPUT OPTIONS5.3OUTPUT FORMAT OPTIONSTABLE 5-3: OUTPUT FORMAT OPTIONS5.4LIGHTING MODES5.5AUTO-OFF5.6PROXIMITY THRESHOLD5.7TOUCH THRESHOLD5.8PIR EVENT THRESHOLD5.9PIR ATI THRESHOLD5.10NUMBER OF PIR EVENTS5.11PIR TRIGGER TIME OUT5.12MINIMUM PIR STABILIZATION TIME6.1DEVICE CLOCK, POWER MANAGEMENT AND MODE OPERATION6.2DEVICE MODES6.3STREAMING AND STANDALONE MODE:                               |                                                                                                                            |

#### IQ Switch<sup>®</sup> ProxFusion<sup>®</sup> Series

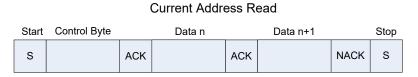

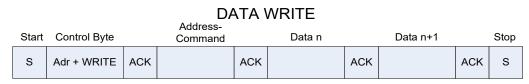

|    | 7.3      | I <sup>2</sup> C Write                                                               |      |

|----|----------|--------------------------------------------------------------------------------------|------|

|    | 7.4      | END OF COMMUNICATION SESSION / WINDOW                                                | . 24 |

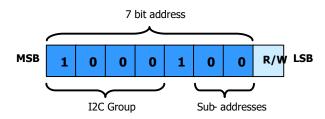

|    | 7.5      | DEVICE ADDRESS AND SUB-ADDRESSES                                                     | . 24 |

|    | 7.6      | Additional OTP options                                                               |      |

|    | 7.7      | I <sup>2</sup> C Specific Commands                                                   |      |

|    | 7.8      | I <sup>2</sup> C I/O CHARACTERISTICS                                                 |      |

|    | TABLE 7- | •                                                                                    |      |

|    | TABLE 7- | •                                                                                    |      |

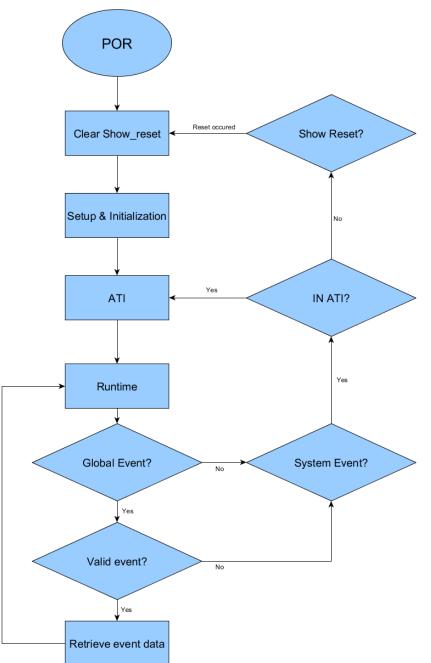

|    | 7.9      | RECOMMENDED COMMUNICATION AND RUNTIME FLOW DIAGRAM                                   |      |

| 8  | WRI      | TING TO THE EEPROM                                                                   |      |

|    | 8.1      | EEPROM AND THE IQS680                                                                | . 27 |

|    | 8.2      | EEPROM STRUCTURE                                                                     |      |

|    | 8.3      | How to write to the EEPROM                                                           |      |

|    |          | 1: DATA IN HEXADECIMAL VALUES THAT SHOULD BE WRITTEN TO EEPROM                       |      |

|    |          | 2: How to write to EEPROM                                                            |      |

| 9  | IQS6     | 80 REGISTER MAP                                                                      |      |

|    | TABLE 9- |                                                                                      |      |

|    | 9.1      | DEVICE INFORMATION DATA                                                              | . 31 |

|    | 9.2      | DEVICE SPECIFIC DATA                                                                 |      |

|    | 9.3      | CHANNEL COUNTS (RAW DATA)                                                            |      |

|    | 9.4      | CHANNEL COUNTS (FILTERED DATA)                                                       |      |

|    | 9.5      | PROXFUSION SENSOR SETTINGS BLOCK 0                                                   |      |

|    | 9.6      | PROXFUSION SENSOR SETTINGS BLOCK 1                                                   |      |

|    | 9.7      | PROXFUSION UI SETTINGS                                                               |      |

|    | 9.8      | INDUCTIVE UI SETTINGS                                                                |      |

|    | 9.9      | PIR SENSOR SETTINGS                                                                  |      |

|    | 9.10     | Device and Power Mode Settings                                                       |      |

| 10 | ) ELEC   | TRICAL CHARACTERISTICS                                                               |      |

|    | 10.1     | Absolute Maximum Specifications                                                      |      |

|    |          | D-1: Absolute maximum specification                                                  |      |

|    | 10.2     | VOLTAGE REGULATION SPECIFICATIONS.                                                   |      |

|    |          | D-2 INTERNAL REGULATOR OPERATING CONDITIONS                                          |      |

|    | 10.3     | POWER ON-RESET/BROWN OUT                                                             |      |

|    |          | D-3: POWER ON-RESET AND BROWN OUT DETECTION SPECIFICATIONS ERROR! BOOKMARK NOT DEFIN |      |

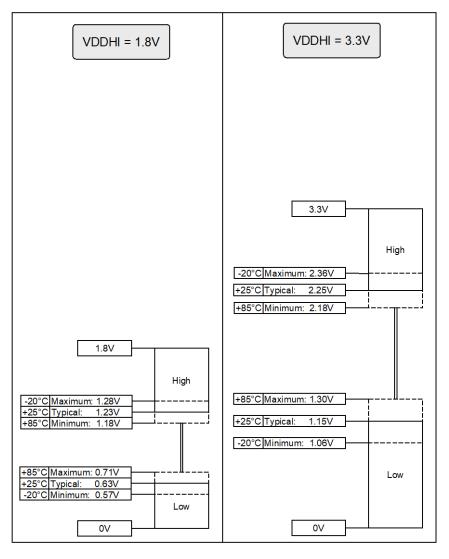

|    | 10.4     | DIGITAL INPUT/OUTPUT TRIGGER LEVELS                                                  |      |

|    |          | D-4 DIGITAL INPUT/OUTPUT TRIGGER LEVEL SPECIFICATIONS.                               |      |

|    | 10.5     |                                                                                      |      |

|    |          | D-5: IC SUBSYSTEM CURRENT CONSUMPTION                                                | -    |

|    |          | D-6: PIR AND CAPACITIVE SENSING CURRENT CONSUMPTION                                  | -    |

|    |          | D-7: INDUCTIVE SENSING CURRENT CONSUMPTION                                           |      |

| 11 |          |                                                                                      |      |

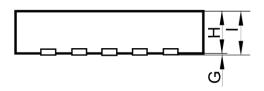

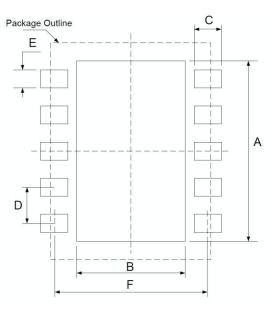

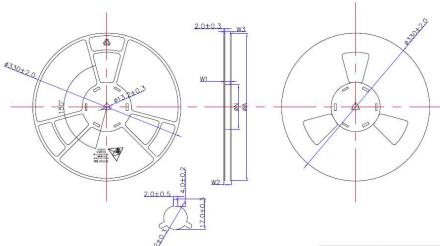

|    | 11.1     | DFN10 PACKAGE AND FOOTPRINT SPECIFICATIONS                                           |      |

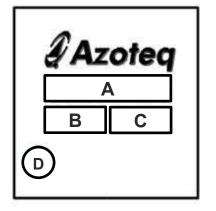

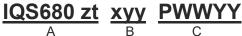

|    | 11.2     | DEVICE MARKING AND ORDERING INFORMATION                                              |      |

|    | 11.3     | TAPE AND REEL SPECIFICATION                                                          |      |

|    | 11.4     | MSL LEVEL                                                                            | -    |

| 12 |          | ASHEET REVISIONS                                                                     | -    |

|    | 12.1     | REVISION HISTORY                                                                     |      |

|    | 12.2     | ERRATA                                                                               |      |

| 13 |          | TACT INFORMATION                                                                     |      |

|    |          |                                                                                      |      |

| 14 |          | APPENDIX A: EEPROM Sample Code                                                       | 54   |

## List of Abbreviations

| ATI              | Automatic Tuning Implementation   |

|------------------|-----------------------------------|

| BOD              | Brown Out Detection               |

| FOV              | Field Of View                     |

| GND              | Ground                            |

| I <sup>2</sup> C | Inter-Integrated Circuit          |

| ICI              | Internal Capacitor Implementation |

| LTA              | Long Term Average                 |

| MSL              | Moisture Sensitivity Level        |

| OTP              | One-Time Programmable             |

| PIR              | Pyroelectric Infrared Radial      |

| POR              | Power On Reset                    |

| PWM              | Pulse Width Modulation            |

| THR              | Threshold                         |

| ТО               | Time-Out                          |

| UI               | User Interface                    |

# List of symbols

| C <sub>ATI</sub>  | ATI Compensation               |

|-------------------|--------------------------------|

| CS <sub>PIR</sub> | PIR sensor Counts              |

| CS <sub>SS</sub>  | Steady-State CS <sub>PIR</sub> |

| CST               | Touch Counts                   |

| Cs                | Internal Reference Capacitor   |

| Cx                | Sense electrode                |

| D <sub>THR</sub>  | PIR Counts Deviation Threshold |

| <b>f</b> s        | Sampling frequency             |

| MATI              | ATI Multiplier                 |

| PTHR              | Proximity event Threshold      |

| Rx                | Receiving electrode            |

| T <sub>THR</sub>  | Touch event Threshold          |

| T <sub>X</sub>    | Transmission electrode         |

| $V_{\text{DD}}$   | Supply voltage                 |

| Vss               | Ground                         |

# **1** Introduction

### 1.1 **ProxFusion**<sup>®</sup>

The ProxFusion<sup>®</sup> sensor series provide all the proven ProxSense<sup>®</sup> engine capabilities with additional sensors types. A combined sensor solution is available within a single platform.

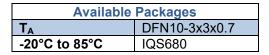

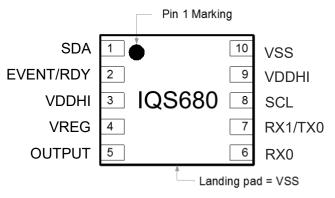

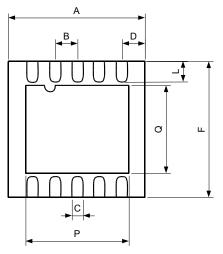

### 1.2 Packaging and Pin-Out

The IQS680 is available in the DFN10 packaging. The pin-outs and functionality are given below.

Figure 1.1: IQS680 pin-out (DFN10 package; device markings may differ)

| Pin | Name   | Туре              | Function                                             |

|-----|--------|-------------------|------------------------------------------------------|

| 1   | SDA    | I <sup>2</sup> C  | SDA (I <sup>2</sup> C Data signal)                   |

| 2   | EVENT  | Digital Out       | Active output on movement and when PIR is blocked    |

| 2   | RDY    | I <sup>2</sup> C  | <b>RDY</b> (I <sup>2</sup> C Ready interrupt signal) |

| 3   | VDDHI  | Supply Input      | Supply: 1.8V – 3.6V                                  |

| 4   | VREG   | Regulator output  | Requires external capacitors                         |

| 5   | OUTPUT | Digital Out       | Active high/low open-drain/push-pull output with PWM |

| 6   | Rx0    | Analogue          | Charge Receive electrode for sensors                 |

| 7   | Rx1    | Analogue          | Charge Receive electrode for sensors                 |

| 7   | Tx0    | Analogue          | Charge Transfer electrode for sensors                |

| 8   | SCL    | I <sup>2</sup> C  | SCL (I <sup>2</sup> C Clock signal)                  |

| 9   | VDDHI  | Supply Input      | Supply: 1.8V – 3.6V                                  |

| 10  | VSS    | Voltage reference | Ground connection                                    |

#### Table 1-1: Pin-out descriptions

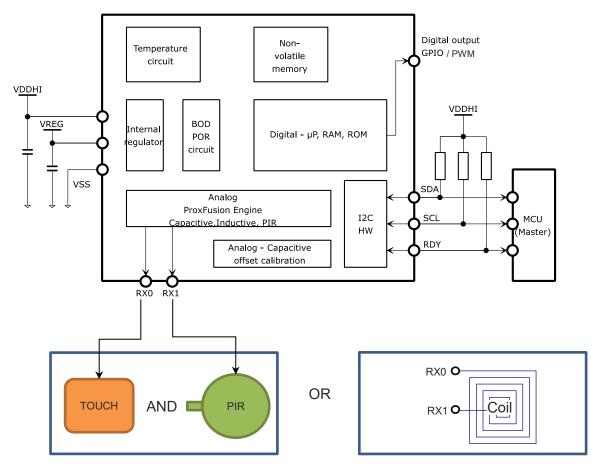

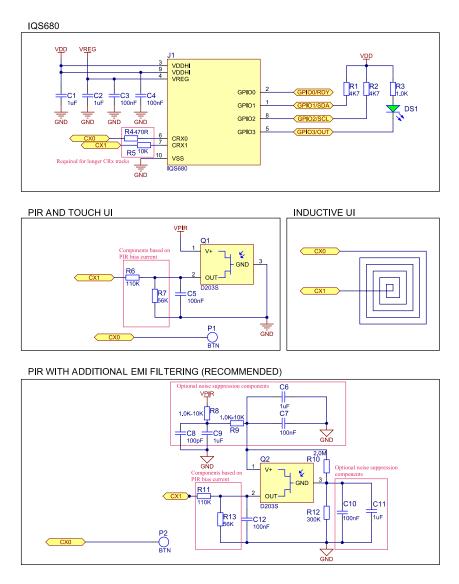

### 1.3 Reference schematic

The PIR can be powered from either VREG or VDD. For long range (> 1m) applications, it is suggested to power the PIR from VDD. For shorter range and lower power applications it is suggested to power the PIR from VREG. An RC filter is placed at the PIR output if required. The PIR sensors need to be placed as close as possible to the IQS680 to ensure RF immunity. By-pass capacitors can be used on the output signal of the PIR as well as the power supply rails to remove unwanted noise. As seen in Figure 1-2, noise suppression components can be added if a problem is experienced with noise. These components can be changed based on the noise requirements of the application. Resistors **R4** and **R5** and needs to be added if the PIR sensor cannot be placed close to the IC. Resistors **R6**, **R7**, **R11** and **R13** are calculated based on the bias current requirement of the PIR element. If using the Inductive UI **R4** and **R5** should be replaced with a ferrite bead to increase RF immunity.

### Figure 1.2 IQS680 reference schematic

### 1.4 Sensor channel combinations

The table below summarizes the IQS680's sensor and channel associations.

|            | Sensor / UI type      | CH0                 | CH1   | CH2                           |

|------------|-----------------------|---------------------|-------|-------------------------------|

| Capacitive | Movement<br>detection | ⊙ <b>Touch</b>      | • PIR |                               |

| Inductive  | Metal<br>detection    | ∘Touch<br>rejection |       | <ul> <li>Inductive</li> </ul> |

#### Table 1-2Sensor - channel allocation

Key:

- Optional implementation

- Fixed use for UI

### 1.5 Features

The IQS680 is a capacitive sensing controller designed for both integrated and standalone Pyroelectric Infrared Radial (PIR) sensing applications. The device offers highly dynamic and adjustable PIR sensing range, depending on the lens chosen (0 - 10m), as well as a high sensitivity proximity (Prox) and contact (Touch) detection through a dedicated sensor line (C<sub>X</sub>).

The device includes advanced Digital Signal Processing (DSP) capabilities for on-chip PIR signal analysis. This, combined with the Automatic Tuning Implementation (ATI) algorithm which calibrates the device to the sense electrode, yields a highly stable, high sensitivity movement detection controller. Further features of the device include an internal voltage regulator and Internal Capacitor Implementation (ICI) to reduce external components. The analogue circuitry is also capable of Power On Reset (POR) detection as well as Brown Out Detection (BOD).

Furthermore, the device has an inductive sensing mode that allows for the detection of non-ferrous metals near the sensor.

The device can also be configured by means of an on-chip EEPROM, such as choosing the device output format, event durations, sensitivity and storing calibration data. The output options include an open-drain or push-pull, active high or low output with Pulse Width Modulation (PWM) as well as the standard I<sup>2</sup>C interface.

### 1.6 **Operation**

The device has been designed to be used in standalone battery-operated automated lighting applications with on/off touch control capabilities. Furthermore, a standard I<sup>2</sup>C interface allows the device to be used in an integrated environment.

The capacitive sensing line of the device can reliably observe the measured results at various levels, which enables it to distinguish between a Prox or Touch event. This allows for a variety of User Interface (UI) responses. The ATI algorithm allows for the adaptation to a wide range of sensing pad sizes.

# 2 User Interface

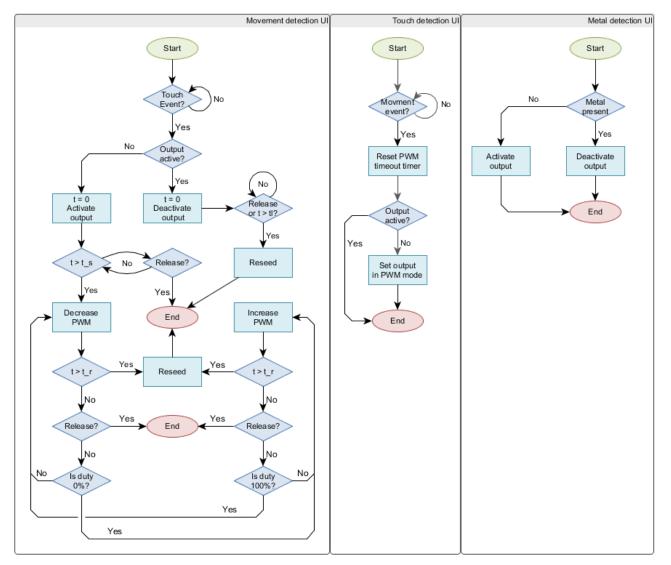

Although standard  $I^2C$  interface is available, the IQS680 is designed as a standalone device with a single logic output. There are three User Interfaces (UI's) on the device, namely Movement detection, Touch detection and Metal detection. The first UI uses a PIR sensor to detect movement over a distance and the second senses touch by means of a capacitive sensing electrode (C<sub>x</sub>). The latter operates with a single copper coil to detect non-ferrous metals in close proximity.

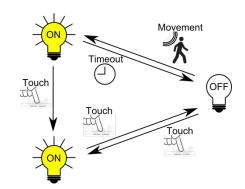

Flow-diagrams of the three UI's are given in Figure 2.1 below. Note that when the output is in PWM mode, it is not considered to be in an active state. More detail is provided on this in the subsections that follow.

### Figure 2.1: UI flow-diagrams

### 2.1 Movement detection UI

#### 2.1.1 PIR sensor

The PIR sensor functions as the movement over a distance interface. Typical PIR sensors have a sensing range of up to 10m, with a radial FOV of 120°. Care should be taken when designing the housing of the PIR sensor as well as the choice of lens, as this plays a pivotal role in sensitivity, range and FOV of the PIR sensor.

Given that the output is in an inactivate state, the IQS680 will switch the output into PWM mode if any movement is detected within the PIR's FOV. The output will exit PWM mode after a predefined time period, upon which the output will return to an idle state.

However, if movement is detected whilst the output is already in PWM mode, the deactivation timers will be reset. This implies that the device will only return to an idle state once no movement was detected of the given time period. As long as the output is active, any movement detection will be ignored.

#### 2.1.2 Touch button

There are 2 trigger levels to which the capacitive electrode will respond.

The first of these is a Prox event. This event should trigger once the user comes within a small distance to the  $C_x$  (in the order of 5cm). This trigger level will not result in an active output, but instead the device will enter Zoom mode. In this mode, the device will sample  $C_x$ at 60Hz rather than the selected frequency ( $f_s$ ) chosen by the designer. This mode switching feature increases the responsiveness of the touch functionality of the device whilst maintaining low power consumption during idle operation.

The second trigger level is a Touch event. This is triggered when the user physically touches the device surface directly above the  $C_X$  pad.

In the case that the output is inactive during the touch event, the output will be activated. If the touch remains for longer than 1s the output will start to dim. If a PWM duty of 0% is reached, the duty will start to increase. This process will continue until the touch is released.

If the output is active when a touch event is registered, the output will be deactivated.

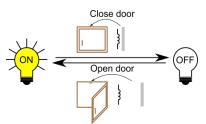

### 2.2 Metal detection UI

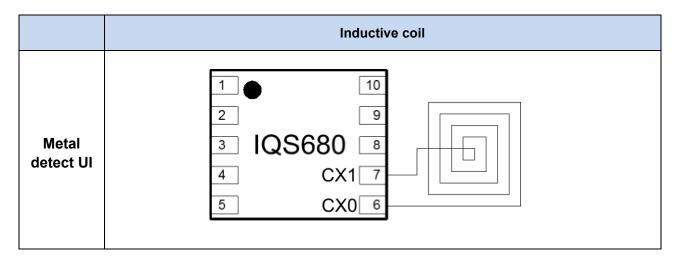

#### 2.2.1 Inductive coil

With a coil connected between the  $C_{X0}$  and  $C_{X1}$  pins, the IQS680 passes a current though the coil and detects any deviations in the current. The IQS680 interprets these fluctuations in current as the presence or absence of metals, such as copper, in the magnetic field generated by the current passed through the coil.

If the IQS680 detect metal in close proximity to the coil, the output is deactivated and inversely, if no metal is detected the output is activated.

A second optional capacitive measurement is also done on the coil to detect and compensate for any capacitive effect that may be exerted on the coil. This allows the IQS680 to refrain from responding to any touches made on the coil.

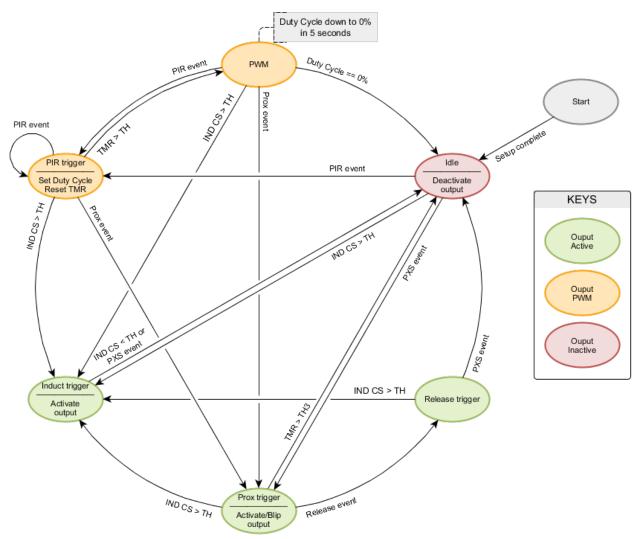

### 2.3 Event output responses

The following figure depicts the responses of the device for all the possible user inputs, given all the possible states of the output.

Figure 2.2: State diagram of the IQS680 output

# 3 Inductive sensing

### 3.1 Channel specifications

The IQS680 requires 2 sensing lines for inductive sensing. Channel 2 is dedicated to the inductive UI.

#### Table 3-1 Inductive sensor – channel allocation

| Mode      | CH0              | CH1 | CH2                           |

|-----------|------------------|-----|-------------------------------|

| Inductive | oTouch rejection |     | <ul> <li>Inductive</li> </ul> |

Key:

- Optional implementation

- Fixed use for UI

### 3.2 Hardware configuration

A ferrite bead can be placed in series with the coil to increase RF immunity.

### Table 3-2 Inductive coil hardware description

## 3.3 Register configuration

### 3.3.1 Registers to configure for inductive sensing:

### Inductive sensing settings registers.

| Address           | Name                             | Description                                                | Recommended setting                                                                               |

|-------------------|----------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| <u>0x50</u>       | Ch0 ProxFusion<br>Settings 0     | Sensor mode and configuration.                             | Sensor mode should be set to<br>Capacitive mode.<br>RX 0 and RX 1 should be<br>enabled and no Tx. |

| <u>0x52</u>       | Ch2 ProxFusion<br>Settings 0     | Sensor mode and configuration of each channel.             | Sensor mode should be set to<br>Inductive mode.<br>Enable TX1 and RX0                             |

| <u>0x53</u>       | ProxFusion Settings 1            | Global settings for the ProxSense sensors                  | None                                                                                              |

| <u>0x54, 0x56</u> | Ch0/Ch2 ProxFusion<br>Settings 2 | ATI settings for<br>ProxFusion sensors                     | ATI target should be more than<br>ATI base to achieve an ATI                                      |

| <u>0x57</u>       | ProxFusion Settings 3            | Additional Global settings for ProxFusion sensors          | Touch detection enabled                                                                           |

| <u>0x60</u>       | Proximity Threshold              | Proximity Threshold for UI                                 | Less than touch threshold                                                                         |

| <u>0x61</u>       | Touch Threshold                  | Touch Threshold for UI                                     | None                                                                                              |

| <u>0x90</u>       | Inductive Prox<br>Threshold      | Proximity Threshold for<br>Inductive UI                    | Less than Enter/Exit Threshold                                                                    |

| <u>0x97</u>       | Metal Enter NM<br>Threshold      | Enter Threshold in non-<br>metal state for Inductive<br>UI | None                                                                                              |

| <u>0x98</u>       | Metal Enter M Threshold          | Enter Threshold in metal state for Inductive UI            | None                                                                                              |

| <u>0x99</u>       | Metal Exit NM Threshold          | Exit Threshold in non-<br>metal state for Inductive<br>UI  | None                                                                                              |

| <u>0x9A</u>       | Metal Exit M Threshold           | Exit Threshold in metal state for Inductive UI             | None                                                                                              |

### 3.4 Sensor data output and flags

The following registers can be monitored by the master to detect inductive sensor related events.

a) Event Flags (0x10) to prompt for inductive sensor activity. Bit 4 denoted as IND ENTER will indicate when a metal object enters the induction sensing area. Bit 5 denoted as IND EXIT will indicate when a metal object exits the induction sensing area.

|             | Event Flags (0x10) |               |         |              |   |   |                |       |  |  |  |  |  |  |

|-------------|--------------------|---------------|---------|--------------|---|---|----------------|-------|--|--|--|--|--|--|

| Bit Number  | 7                  | 6             | 6 5 4 3 |              | 2 | 1 | 0              |       |  |  |  |  |  |  |

| Data Access |                    |               |         | Read         | ł |   |                |       |  |  |  |  |  |  |

| Name        | SHOW RESET         | - IND<br>EXIT |         | IND<br>ENTER | - | - | PIR<br>TRIGGER | TOUCH |  |  |  |  |  |  |

b) <u>Global Ul Flags (0x12)</u> to prompt for inductive sensor activation. Bit3 denoted as METAL PRESENT will indicate the detection of a metal object using the inductive sensing. Bit 6/7 provides the classic prox/touch two level activation outputs.

|                | Global UI Flags (0x12) |              |             |                |              |               |              |             |  |  |  |  |  |  |  |

|----------------|------------------------|--------------|-------------|----------------|--------------|---------------|--------------|-------------|--|--|--|--|--|--|--|

| Bit Number     | r 7 6 5 4 3 2 1        |              |             |                |              |               |              |             |  |  |  |  |  |  |  |

| Data<br>Access |                        |              |             | Read           |              |               |              |             |  |  |  |  |  |  |  |

| Name           | METAL<br>PRESENT       | TOUCH<br>CH2 | PROX<br>CH2 | PIR<br>TRIGGER | PIR<br>EVENT | STABLE<br>CH0 | TOUCH<br>CH0 | PROX<br>CH0 |  |  |  |  |  |  |  |

c) <u>Channel Counts Ch2 (0x24 - 0x25)</u> registers will provide a combined 16-bit value to acquire the magnitude of the inductive sensed object.

|             | Channel counts Ch2 (0x24/0x25) |                                    |  |  |  |  |  |    |    |                |  |  |  |  |  |  |

|-------------|--------------------------------|------------------------------------|--|--|--|--|--|----|----|----------------|--|--|--|--|--|--|

| Bit Number  | 15                             | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |    |    |                |  |  |  |  |  |  |

| Data Access |                                |                                    |  |  |  |  |  | Re | ad |                |  |  |  |  |  |  |

| Name        |                                | Count High Byte                    |  |  |  |  |  |    |    | Count Low Byte |  |  |  |  |  |  |

d) Metal Detect Base (0x34 - 0x35) registers will provide a combined 16-bit value of the metal detect base value.

|             | Metal Detect Base (0x34/0x35) |                                    |  |  |  |  |  |    |    |     |       |        |      |       |      |  |

|-------------|-------------------------------|------------------------------------|--|--|--|--|--|----|----|-----|-------|--------|------|-------|------|--|

| Bit Number  | 15                            | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |    |    |     |       |        |      |       |      |  |

| Data Access |                               |                                    |  |  |  |  |  | Re | ad |     |       |        |      |       |      |  |

| Name        | Metal Detect Base High Byte   |                                    |  |  |  |  |  |    |    | Met | al De | tect E | Base | Low E | Byte |  |

# e) Channel 2 LTA (0x36-0x37) registers will provide a combined 16-bit value of the LTA of channel 2.

| Channel 2 LTA (0x36/0x37) |    |                            |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|---------------------------|----|----------------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit Number                | 15 | 14                         | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Data Access               |    | Read                       |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name                      |    | LTA High Byte LTA Low Byte |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

# 4 Pyroelectric Infrared Radial (PIR) sensing

### 4.1 Channel Specifications

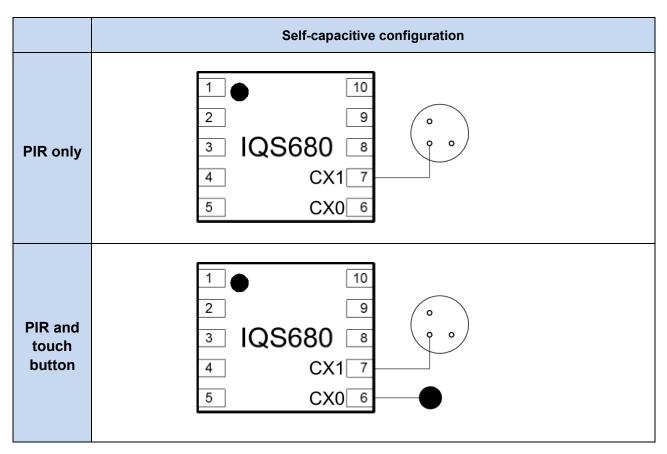

The IQS680 requires one sensing line for PIR sensing and one sensing line for touch sensing. Channel 1 is dedicated to the PIR UI.

#### Table 4-1 PIR sensor – channel allocation

| Mode                  | CH0    | CH1   | CH2 |

|-----------------------|--------|-------|-----|

| Movement<br>detection | ∘Touch | • PIR |     |

Key:

- o Optional implementation

- Fixed use for UI

### 4.2 Hardware Configuration

In the table below are multiple options of configuring sensing (CX) electrodes to realize different implementations.

#### Table 4-2 PIR hardware description

# 4.3 Register configuration

### 4.3.1 Registers to configure for the PIR and capacitive sensing:

### PIR and capacitive sensing settings registers

| Address           | Name                             | Description                                       | Recommended setting                                                                      |

|-------------------|----------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------|

| <u>0x50</u>       | Ch0 ProxFusion<br>Settings 0     | Sensor mode and configuration.                    | Sensor mode should be set to<br>capacitive mode.<br>RX 0 should be enabled and<br>no Tx. |

| <u>0x51</u>       | Ch1 ProxFusion<br>Settings 0     | Sensor mode and configuration.                    | Sensor mode should be set to<br>PIR mode.<br>RX 1 should be enabled and<br>no TX.        |

| <u>0x53</u>       | ProxFusion Settings 1            | Global settings for the ProxSense sensors         | None                                                                                     |

| <u>0x54, 0x55</u> | Ch0/Ch1 ProxFusion<br>Settings 2 | ATI settings for<br>ProxFusion sensors            | ATI target should be more<br>than ATI base to achieve an<br>ATI                          |

| <u>0x57</u>       | ProxFusion Settings 3            | Additional Global settings for ProxFusion sensors | None                                                                                     |

| <u>0x60</u>       | Proximity threshold              | Proximity Threshold for UI                        | Less than touch threshold                                                                |

| <u>0x61</u>       | Touch threshold                  | Touch Threshold for UI                            | None                                                                                     |

| <u>0x90</u>       | PIR Settings                     | PIR Global Settings                               | Ignore polarity of events                                                                |

| <u>0x91,0x92</u>  | PIR Threshold                    | PIR Event Threshold for UI                        | PIR Exit Event Threshold ≤<br>PIR Enter Event Threshold                                  |

| <u>0x93</u>       | PIR Threshold Scale<br>Factor    | PIR Threshold Scale<br>Factor for UI              | None                                                                                     |

### 4.4 Sensor data output and flags

The following registers can be monitored by the master to detect PIR/touch sensor related events.

a) Event Flags (0x10) to prompt for PIR or touch sensor activity. Bit 1 denoted as PIR TRIGGER will indicate when the PIR is triggered by movement. Bit 0 denoted as TOUCH will indicate when the touch sensor is activated.

| Event Flags (0x10) |            |   |             |              |   |   |                |       |  |

|--------------------|------------|---|-------------|--------------|---|---|----------------|-------|--|

| Bit Number         | 7          | 6 | 5           | 4            | 3 | 2 | 1              | 0     |  |

| Data Access        |            |   |             | Read         | d |   |                |       |  |

| Name               | SHOW RESET | - | IND<br>EXIT | IND<br>ENTER |   |   | PIR<br>TRIGGER | тоисн |  |

b) <u>Global Ul Flags (0x12)</u> to prompt for PIR or touch sensor activation. Bit3 denoted as **PIR** EVENT will indicate that a PIR event has occurred. Bit 0/1 provides the classic prox/touch two level activation outputs.

|                | Global UI Flags (0x12) |                 |             |                |              |               |              |             |  |  |  |  |

|----------------|------------------------|-----------------|-------------|----------------|--------------|---------------|--------------|-------------|--|--|--|--|

| Bit Number     | 7                      | 7 6 5 4 3 2 1 0 |             |                |              |               |              |             |  |  |  |  |

| Data<br>Access |                        |                 |             | Read           |              |               |              |             |  |  |  |  |

| Name           | METAL<br>PRESENT       | TOUCH<br>CH2    | PROX<br>CH2 | PIR<br>TRIGGER | PIR<br>EVENT | STABLE<br>CH0 | TOUCH<br>CH0 | PROX<br>CH0 |  |  |  |  |

c) Lighting Flags (0x13) to prompt for lighting activity. Bit 4 is set when the PWM output is changing and is cleared when the PWM output is constant. Bit 3 is set when the duty cycle of the PWM output is increasing and is cleared when the duty cycle of the PWM output is decreasing.

|             | Lighting Flags (0x13) |            |              |        |              |   |                      |                    |  |  |  |

|-------------|-----------------------|------------|--------------|--------|--------------|---|----------------------|--------------------|--|--|--|

| Bit Number  | 7                     | 6          | 5            | 4      | 3            | 2 | 1                    | 0                  |  |  |  |

| Data Access |                       |            |              |        | Read         |   |                      |                    |  |  |  |

| Name        | PIR<br>STABLE         | PIR<br>RDY | BLIP<br>BUSY | FADING | FADING<br>IN |   | PIR/IND<br>ACTIVATED | TOUCH<br>ACTIVATED |  |  |  |

d) Channel Counts (Raw) Ch1 (0x22 - 0x23) registers will provide a combined 16-bit value of the raw value.

|             | Channel counts Ch1 (0x22-0x23) |                                |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-------------|--------------------------------|--------------------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit Number  | 15                             | 14                             | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Data Access |                                | Read                           |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name        |                                | Count High Byte Count Low Byte |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

e) <u>Channel Counts (filtered) Ch1 (0x34 - 0x37)</u> registers will provide a combined 16-bit value of several filtered values. Channel 1 PDS provides the positive delta sum value. The delta is the difference between the previous sample counts and the current sample counts. Therefore, this value increase if the difference between the previous sample and current sample is positive (counts increasing).

|             |    |                            |    |    | Ch | anne | I 1 P | DS (0 | x34/0 | )x35) |   |   |   |   |   |   |

|-------------|----|----------------------------|----|----|----|------|-------|-------|-------|-------|---|---|---|---|---|---|

| Bit Number  | 15 | 14                         | 13 | 12 | 11 | 10   | 9     | 8     | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

| Data Access |    | Read                       |    |    |    |      |       |       |       |       |   |   |   |   |   |   |

| Name        |    | PDS High Byte PDS Low Byte |    |    |    |      |       |       |       |       |   |   |   |   |   |   |

Channel 1 NDS provides the negative delta sum value. The delta is the difference between the previous sample counts and the current sample counts. Therefore, this value increase if the difference between the previous sample and current sample is negative (counts decreasing).

|             | Channel 1 NDS (0x36/0x37) |                            |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-------------|---------------------------|----------------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit Number  | 15                        | 14                         | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Data Access |                           | Read                       |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name        |                           | NDS High Byte NDS Low Byte |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

# 5 User Configurable Settings (UCS)

This section describes the user configurable options of the IQS680 in detail. User options are selected though the Azoteq GUI, which is used to write it in the device's EEPROM.

### 5.1 Sampling frequency

The frequency at which the device samples the sensors directly relates to its power consumption, where a higher sample rate requires a more power. The designer may select 1 of 4 possible sample frequencies as shown in Table 5-1. The sampling frequency can be set in the <u>Sample Period (0xD5)</u> register and <u>Active Sample Period Adjustment (0xD4)</u> registers.

| Table 5-1 | Sample | frequency | options |

|-----------|--------|-----------|---------|

|-----------|--------|-----------|---------|

| FREQ: Device sampling frequency select |        |  |  |  |  |  |  |  |  |

|----------------------------------------|--------|--|--|--|--|--|--|--|--|

| 10 Hz                                  | 50 Hz  |  |  |  |  |  |  |  |  |

| 20 Hz                                  | 100 Hz |  |  |  |  |  |  |  |  |

For a sampling frequency of 10 Hz and 20 Hz a <u>PIR Filter Beta Value</u> of 2 is recommended and for a sampling frequency of 50 Hz and 100 Hz a <u>PIR Filter Beta Value</u> of 3 is recommended.

### 5.2 Input Modes

The IQS680 includes 3 input modes, which define the sensors attached to the device. The mode can be selected in the <u>ProxFusion Settings 0 (0x50-0x53; bits 7-4)</u> registers. These modes are given in the Table 5-2

Table 5-2User Input Modes

| INPUT: Input type select   |

|----------------------------|

| PIR sensor only            |

| PIR and capacitive sensors |

| Coil (metal detect) sensor |

### 5.3 Output Pin Configuration

The IQS680 output pin (pin 5) can be used in 4 different configurations. These configurations, given in Table 5-3, allow the designer to operate the load in the best configuration for the given application. The output configuration can be set in the <u>System Settings 0 (0xD2; bits 7&2)</u> register.

#### Table 5-3: Output formats

| <b>OUTPUT<sub>F</sub>:</b> Output configuration select |  |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|--|

| Active High & Push-pull                                |  |  |  |  |  |  |

| Active Low & Push-pull                                 |  |  |  |  |  |  |

| Active High & Open-drain                               |  |  |  |  |  |  |

| Active Low & Open-drain                                |  |  |  |  |  |  |

### 5.4 Output Modes

The IQS680 includes 3 output modes. These modes, given in Table 5-4, allow the designer to operate the load in the best configuration for the given application. Before selecting the output mode, the user should ensure that the output pin is configured correctly, as described above. The generated output signal is a function of the selected output pin configuration and the selected output mode.

#### Table 5-4: Output modes

| OUTPUT <sub>T</sub> : Output mode select |

|------------------------------------------|

| On/Off                                   |

| Varied PWM                               |

| Fixed PWM                                |

| Pulse                                    |

In the "On/Off" output mode, the IQS680 will always activate the output on any event with a 100% PWM duty. In the "Varied PWM" mode, the IQS680 will cycle through a 0 - 100% PWM duty when a prolonged touch event is detected (longer than 1s), given that the touch event has activated the load. The "Pulse" mode will only generate a short pulse (10us - 250us, selectable in the Light Time Out (0xD8) register ) for any event. The output mode can be set in the System Settings 1 (0xD3; bits 1-0) register.

### 5.5 Auto-off

By default, the device's output will remain in an active state perpetually, given that the output is in a load driven mode. However, if the auto-off feature is selected, the output will be deactivated after a period of 1 hour. Therefore, if the output is retriggered continuously, the output will turn off after 1 hour. The Auto-off bit can be set in the <u>System Settings 0 (0xD2; bit 4)</u> register.

### 5.6 **Proximity threshold**

The Proximity Threshold ( $P_{THR}$ ) defines the minimum required divergence of the Touch CS (CS<sub>T</sub>) from the Long Term Average (LTA) for more than 4 consecutive cycles to trigger a proximity event. The IQS680 proximity threshold range is 0 - 255, where typical values are approximately 8, enabling the designer to obtain the desired sensitivity and noise immunity for the touch electrode. The Proximity Threshold ( $P_{THR}$ ) can be set in <u>P Threshold (0x60) register</u>.

### 5.7 Touch threshold

Similar to the proximity threshold, the Touch Threshold  $(T_{THR})$  defines the minimum required diverngence of the CS<sub>T</sub> from the LTA for more than 2 consecutive cycles to trigger a touch event. The following equation illustrates how it is determined whether a touch event has occurred:

$$LTA \times \frac{CS_T}{256} > T_{THR}.$$

The IQS680 touch threshold range is 0 - 255. The touch threshold is selected by the designer to obtain the desired touch sensitivity. The Touch Threshold ( $T_{THR}$ ) can be set in the <u>Threshold (0x61)</u> register.

### 5.8 **PIR event thresholds**

Unlike the touch events, which are based on the absolute  $CS_T$  measurement, PIR events are based on the differential measurement of the PIR sensor CS ( $CS_{PIR}$ ). Thus, a PIR Event Threshold ( $E_{THR}$ ) defines the minimum required *rate* of divergence of  $CS_{PIR}$  from its Steady-State CS ( $CS_{SS}$ ) to trigger a PIR event.

The IQS680 PIR event threshold ranges from 0 - 255, which is chosen to obtain the desired sensitivity and noise immunity for the PIR sensor. A PIR Event is triggered if the Positive Delta Sum (PDS) or Negative Delta Sum (NDS) is greater than the product of the <u>PIR Threshold Scale Factor</u> (0x93) and the <u>PIR Enter Event Threshold (0x91)</u>.

$(PIR_{NDS} \text{ or } PIR_{PDS}) > PIR_{Enter} \times PIR_{Scale}$

Before another event can be triggered the Positive Delta Sum (PDS) or Negative Delta Sum (NDS) needs to be below the product of the <u>PIR Threshold Scale Factor (0x93)</u> and the <u>PIR Exit Event</u> <u>Threshold (0x92)</u> value.

$$(PIR_{NDS} \text{ or } PIR_{PDS}) < PIR_{Exit} \times PIR_{Scale}$$

PIR Exit Event Threshold (0x91) should be less than or equal to PIR Enter Event Threshold (0x92).

$$PIR_{Enter} \leq PIR_{Exit}$$

### 5.9 **PIR ATI threshold**

The PIR sensor is susceptible to ambient noise such as fluctuation in temperature over the course of 24 hours. These changes directly impact the sensitivity of the sensor.

In order to maintain a non-variant sensitivity, the IQS680 will monitor the difference of the  $CS_{SS}$  value from the selected ATI target value and compare it to the PIR ATI Threshold (ATI<sub>THR</sub>) to determine if the device will recalibrate the PIR sensor.

$$CS_{SS} \ge \frac{ATI_{THR}}{255} \times ATI_{Target}$$

,

There are various possible values for  $ATI_{THR}$ , some are given in the table below.

#### Table 5-5: PIR deviation thresholds

| ATI <sub>THR</sub> : PIR ATI THR select |                   |  |  |  |  |  |

|-----------------------------------------|-------------------|--|--|--|--|--|

| 16                                      | More conservative |  |  |  |  |  |

| 24                                      |                   |  |  |  |  |  |

| 32                                      | Less conservative |  |  |  |  |  |

The PIR ATI threshold can be set in the <u>Ch1 ATI Threshold (0x47)</u> register.

### 5.10 Number of PIR events

In order to improve the IQS680's resilience against false triggers (important for security applications), the device can be set up to prevent the output from activating until a given number of PIR events has occurred in short succession. The number of events may range from 1 to 4. The number of PIR events can be set in the <u>PIR Settings 0 (0x90, bit4-5)</u> register.

### 5.11 PIR Trigger Time Out

If a PIR event has occurred, given that the output is in a load driven mode, the device's output will go in an active or PWM state for a selected period. This period can be selected in steps of 4.2 seconds, ranging from 4.2 to 1071 seconds. The PIR Trigger Time Out can be set in <u>PIR Trigger Time Out (0xD9)</u> register.

When a consecutive PIR event occur before the selected period has elapsed, the internal timer will reset and the output will remain active. This implies that the PIR Trigger Time Out defines the time the output will remain active after the last PIR event has occurred.

### 5.12 Minimum PIR Stabilization Time