SLVSCZ3-MARCH 2015

# TPS2477x 2.5 to 18-V High Performance Hot Swap

#### **Features**

- 2.5V to 18V Bus Operation (30V abs max)

- Programmable Protection Settings:

- Current Limit: ±5% at 10mV

- Fast Trip: ±10% at 20mV

- Programmable FET SOA Protection

- Programable Response Time for Fast Trip

- Dual Timer (Inrush/Fault)

- Analog Current Monitor (1% at 25mV)

- Programmable UV and OV

- Status Flags for Faults and Power Good

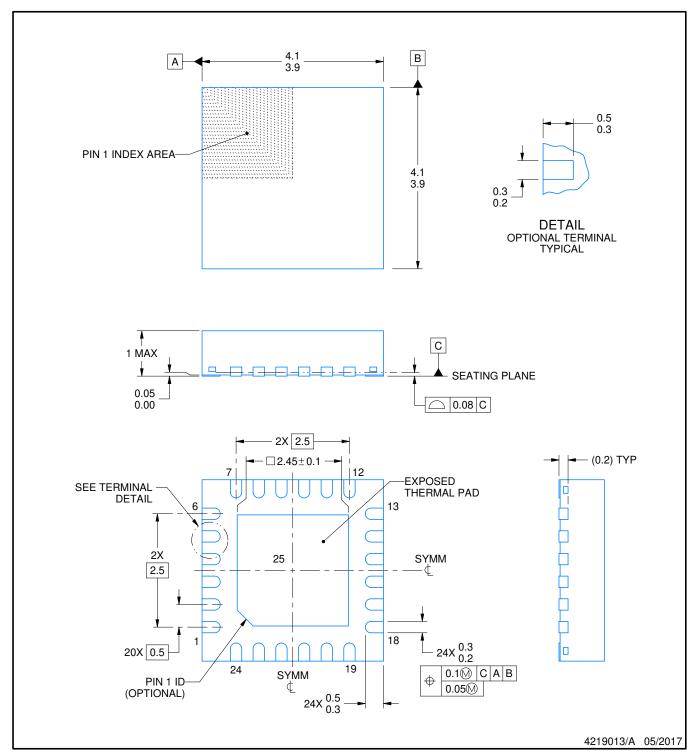

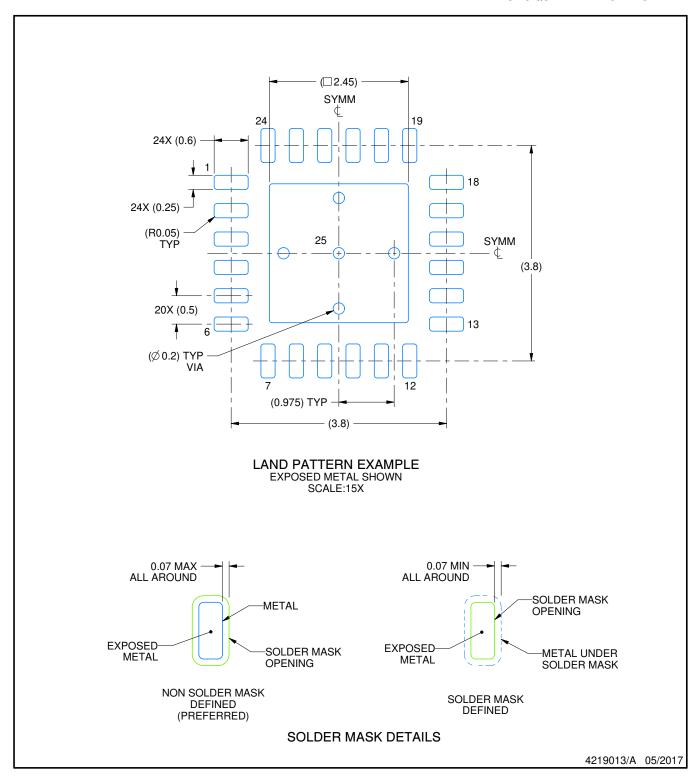

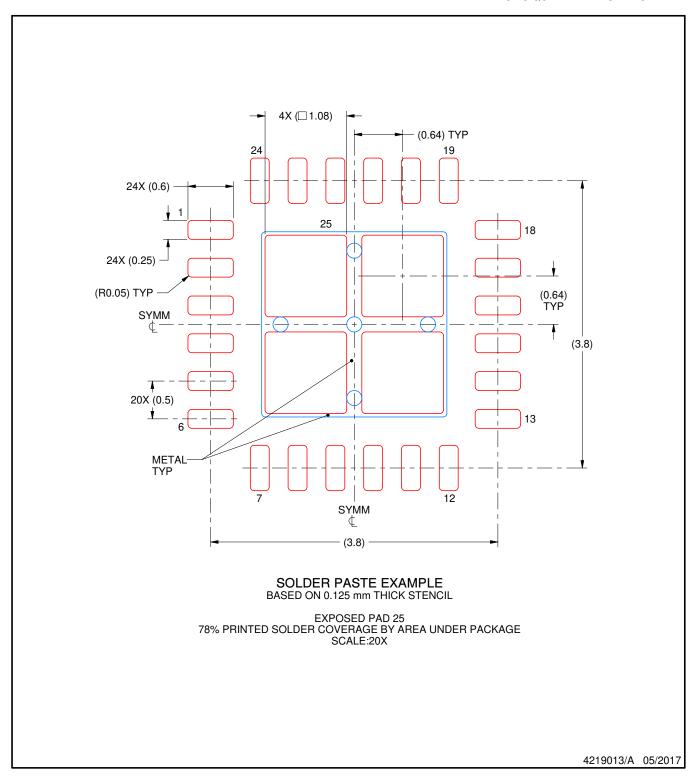

- 4mm × 4mm 24-pin QFN

- 70 = Latch, 71 = Retry, 72 = Fast Latch Off

## **Applications**

- **Enterprise Storage**

- **Enterprise Server**

- **Networking Cards**

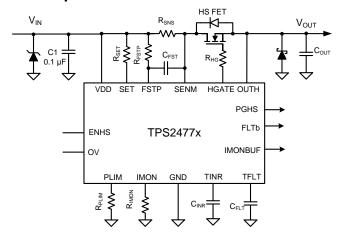

- 240 VA Applications

## 3 Description

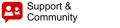

The TPS2477x is a high performance analog Hot Swap Controller for 2.5 V to 18 V systems. The precise and highly programmable protection settings of the TPS2477x aid the design of high power high availability systems where isolating faults is critical.

Programmable current limit, fast shut down, and fault timer protect the load and supply during fault conditions such as a hot - short. The fast shutdown threshold and response time can be tuned to ensure a fast response to real faults, while avoiding nuisance trips. Programmable Safe Operating Area (SOA) protection and the inrush timer keep the MOSFET safe under all conditions. After asserting power good, TPS2477x acts as a circuit breaker and runs the fault timer during over current events, but doesn't current limit. It shuts down after the fault timer expires. Two independent timers (inrush/fault) allow the user to customize protection based on system requirements.

Finally, the flexibility of the TPS2477x aid Hot Swap design for the 240 VA requirement and a design example is shown in the datasheet.

## Device Information<sup>(1)</sup>

| PART NUMBER                      | PACKAGE  | BODY SIZE (NOM)   |

|----------------------------------|----------|-------------------|

| TPS24770<br>TPS24771<br>TPS24772 | RGE (24) | 4.00 mm x 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

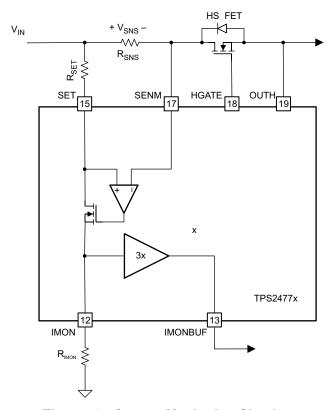

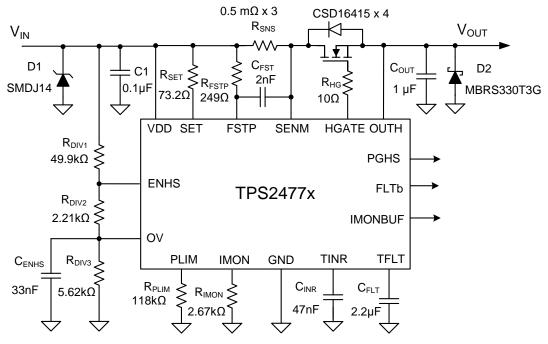

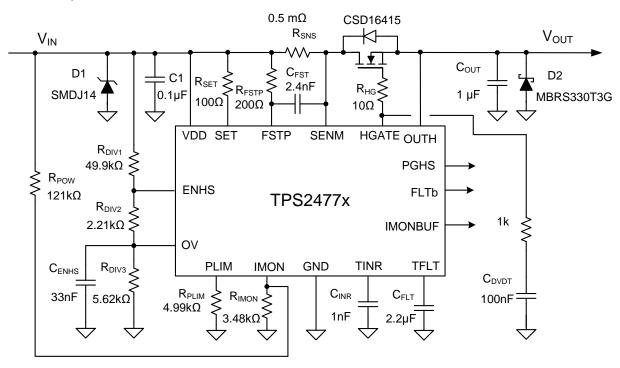

## **Simplified Schematic**

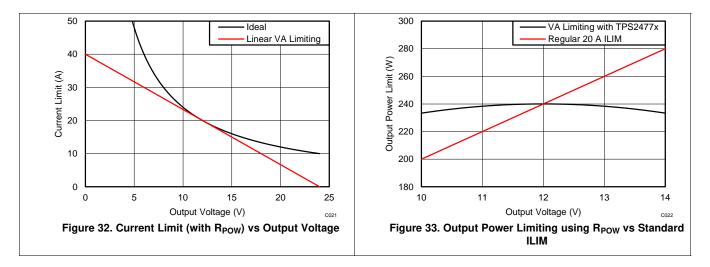

## Limiting Output Power to 240VA 20 A I<sub>LIM</sub> vs TPS2477x Implementation

## **Table of Contents**

| 1      | Features 1                           |    | 9.2 Functional Block Diagram                     |    |

|--------|--------------------------------------|----|--------------------------------------------------|----|

| 2      | Applications 1                       |    | 9.3 Feature Description                          | 11 |

| 3      | Description 1                        |    | 9.4 Device Functional Modes                      | 16 |

| 4      | Simplified Schematic 1               | 10 | Application and Implementation                   | 17 |

| 5      | Revision History2                    |    | 10.1 Application Information                     | 17 |

| 6      | Device Comparison Table              |    | 10.2 Typical Application                         | 17 |

| 7      | Pin Configuration and Functions      | 11 | Power Supply Recommendations                     | 40 |

| ,<br>8 | Specifications                       | 12 | Layout                                           | 40 |

| 0      | 8.1 Absolute Maximum Ratings         |    | 12.1 Layout Guidelines                           | 40 |

|        | 8.2 ESD Ratings                      |    | 12.2 Layout Example                              | 42 |

|        | 8.3 Recommended Operating Conditions | 13 | Device and Documentation Support                 | 43 |

|        | 8.4 Thermal Information              |    | 13.1 Related Links                               | 43 |

|        | 8.5 Electrical Characteristics       |    | 13.2 Trademarks                                  | 43 |

|        | 8.6 Timing Requirements              |    | 13.3 Electrostatic Discharge Caution             | 43 |

|        | 8.7 Typical Characteristics          |    | 13.4 Glossary                                    | 43 |

| 9      | Detailed Description 10              | 14 | Mechanical, Packaging, and Orderable Information | 49 |

|        | 9.1 Overview                         |    | inomation                                        |    |

|        |                                      |    |                                                  |    |

# 5 Revision History

| DATE       | REVISION | NOTES            |

|------------|----------|------------------|

| March 2015 | *        | Initial release. |

Submit Documentation Feedback

# 6 Device Comparison Table

**NSTRUMENTS**

| PART NUMBER <sup>(1)</sup> | LATCH / RETRY OPTION |

|----------------------------|----------------------|

| TPS24770                   | Latch                |

| TPS24771                   | Auto – Retry         |

| TPS24772                   | Fast Latch Off       |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

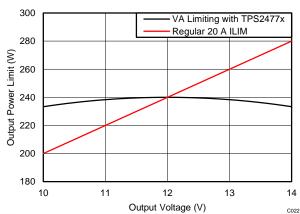

## 7 Pin Configuration and Functions

#### **Pin Functions**

| PII     | V                | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                             |  |  |

|---------|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO.              |                     |                                                                                                                         |  |  |

| ENHS    | 2                | - 1                 | Active-high enable input of Hot Swap. Logic input. Connects to resistor divider.                                        |  |  |

| FLTb    | 4                | 0                   | Active-low, open-drain output indicating various faults.                                                                |  |  |

| FSTP    | 16               | I                   | Fast trip programming set pin for Hot Swap. A resistor is connected from positive terminal of R <sub>SNS</sub> to FSTP. |  |  |

| GND     | 10               | _                   | Ground.                                                                                                                 |  |  |

| HGATE   | 18               | 0                   | Gate driver output for external Hot Swap MOSFET.                                                                        |  |  |

| IMON    | 12               | I/O                 | Analog monitor and current limit program point. Connect R <sub>IMON</sub> to ground.                                    |  |  |

| IMONBUF | 13               | 0                   | Voltage output proportional to the load current (0V-3.0V).                                                              |  |  |

| NC      | 1,3, 6,<br>20–24 | NC                  | No connect. Tie to ground or leave floating.                                                                            |  |  |

(1) I = Input; O = Output; P = Power, NC = No Connect

## Pin Functions (continued)

| PI   | N   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                              |

|------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. |                     |                                                                                                                                                                                          |

| OUTH | 19  | I                   | Output voltage sensor for monitoring Hot Swap MOSFET's power. Connects to the source terminal of the Hot Swap N channel MOSFET.                                                          |

| OV   | 9   | I                   | Overvoltage comparator input. Connects to resistor divider. HGATE is pulled low when OV exceeds the threshold. Connect to ground when not used.                                          |

| PGHS | 5   | 0                   | Active-high, open-drain power-good indicator.                                                                                                                                            |

| PLIM | 11  | I                   | Power limit programming pin. A resistor from this pin to GND sets the maximum power dissipation for the Hot Swap FET. Connect a $4.99~\mathrm{k}\Omega$ resistor to disable power limit. |

| SENM | 17  | I                   | Current-sensing input for the sense resistor. Directly connects to the negative terminal of the sense resistor.                                                                          |

| SET  | 15  | I                   | Current-limit programming set pin for Hot Swap. A resistor is connected from positive terminal of the sensing resistor.                                                                  |

| TFLT | 8   | I/O                 | Fault timer, which runs when the device is in regular operation and there is an overcurrent condition.                                                                                   |

| TINR | 7   | I/O                 | Inrush timer, which runs during the inrush operation (start-up) if the part is in current limit or power limit.                                                                          |

| VDD  | 14  | Р                   | Power Supply                                                                                                                                                                             |

## 8 Specifications

## 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                |                                                | MIN  | MAX                                       | UNIT     |

|----------------|------------------------------------------------|------|-------------------------------------------|----------|

| Input Voltage  | VDD,SET, FSTP,SENM, OUTH, ENHS, FLTb, PGHS, OV | -0.3 | 30                                        | ٧        |

|                | HGATE to OUTH                                  | -0.3 | 15                                        | V        |

|                | SET to VDD                                     | -0.3 | 0.3                                       | ٧        |

| input voitage  | SENM, FSTP to VDD                              | -0.6 | 0.3                                       | ٧        |

|                | TINR, TFLT, PLIM, IMON                         | -0.3 | 30<br>15<br>0.3<br>0.3<br>3.6<br>7<br>5 r | <b>V</b> |

|                | IMONBUF                                        | -0.3 | 7                                         | V        |

| Sink Current   | FLTb, PGHS                                     |      | 5                                         | mA       |

| Source Current | IMON, IMONBUF                                  |      | 5                                         | mA       |

| Storage temper | ature, T <sub>stg</sub>                        | -65  | 150                                       | ô        |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 8.2 ESD Ratings

|                                   |               |                                                                     | VALUE | UNIT |

|-----------------------------------|---------------|---------------------------------------------------------------------|-------|------|

| v (1)                             | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)              | ±1500 | V    |

| V <sub>(ESD)</sub> <sup>(1)</sup> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (3) | ±500  | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) measures device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Documentation Feedback

<sup>(2)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

STRUMENTS

over operating free-air temperature range (unless otherwise noted)

|                                      |                                                   | MIN  | MAX  | UNIT     |

|--------------------------------------|---------------------------------------------------|------|------|----------|

| lanut valtaga                        | VDD, SENM, SET, FSTP                              | 2.5  | 18   | <b>\</b> |

| input voitage                        | ENHS, FLTb, PGHS, OUTH                            | 0    | 18   | V        |

| Sink current                         | FLTb, PGHS                                        | 0    | 2    | mA       |

| Source current                       | IMON                                              | 0    | 1    | mA       |

| External resistance                  | PLIM                                              | 4.99 | 500  | kΩ       |

|                                      | IMON                                              | 1    | 6    | kΩ       |

|                                      | FSTP                                              | 10   | 4000 | Ω        |

|                                      | SET                                               | 10   | 400  | Ω        |

| R <sub>IMON</sub> / R <sub>SET</sub> | w/o R <sub>STBL</sub>                             | 10   | 70   |          |

|                                      | With appropriate R <sub>STBL</sub> <sup>(1)</sup> | 3    | 10   |          |

|                                      | with $C_{HGATE} > 47nF$ (2)                       | 10   | 200  |          |

|                                      | TINR, TFLT                                        | 1    |      | nF       |

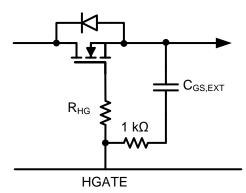

| Fortament connection                 | HGATE, (2)                                        | 0    | 1    | μF       |

| Input voltage                        |                                                   | 30   | pF   |          |

|                                      | IMONBUF                                           |      | 100  | pF       |

| Operating junction temp              | perature, T <sub>J</sub>                          | -40  | 125  | °C       |

- Refer to  $R_{STBL}$  Requirment for  $R_{IMON}$  /  $R_{SET}$  < 10 as described in section Select  $R_{SNS}$  and  $V_{SNS,CL}$  Setting. External capacitance tied to HGATE, should be in series with a resistor no less than 1k $\Omega$ .

#### 8.4 Thermal Information

|                       | Junction-to-ambient thermal resistance  Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance  Junction-to-top characterization parameter  Junction-to-board characterization parameter | RGE     | LIMIT  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

|                       |                                                                                                                                                                                                                   | 24 PINS | UNIT   |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance                                                                                                                                                                            | 34.6    |        |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance                                                                                                                                                                         | 38.4    |        |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                                                                                                                                                                              | 12.9    | 00/14/ |

| ΨЈТ                   | Junction-to-top characterization parameter                                                                                                                                                                        | 0.5     | °C/W   |

| ΨЈВ                   | Junction-to-board characterization parameter                                                                                                                                                                      | 12.9    |        |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                                                                                                                                                                      | 3.2     |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 8.5 Electrical Characteristics

Unless otherwise noted these limits apply to the following: -40°C < T<sub>J</sub><125°C; 2.5V < V<sub>VDD</sub>, V<sub>OUT</sub> < 18V; V<sub>ENHS</sub> = 2 V; V<sub>OV</sub> = 0 V; V<sub>HGATE</sub>, V<sub>PGHS</sub>, V<sub>FLTB</sub>, and V<sub>IMONBUF</sub> are floating; C<sub>INR</sub> = 1nF; C<sub>FLT</sub> = 1nF; R<sub>SET</sub> = 44.2  $\Omega$ ; R<sub>IMON</sub> = 2.98k  $\Omega$ ; R<sub>FSTP</sub> = 200  $\Omega$ ;  $R_{PLIM} = 52 \text{ k}\Omega.$

|                       | PARAMETER                                            | TEST CONDITION                    | MIN | TYP  | MAX  | UNIT |

|-----------------------|------------------------------------------------------|-----------------------------------|-----|------|------|------|

| INPUT SUPP            | PLY (VDD)                                            | ·                                 |     |      |      |      |

| V <sub>UVR</sub>      | UVLO threshold, rising                               |                                   | 2.2 | 2.32 | 2.45 | V    |

| V <sub>UVhyst</sub>   | UVLO hysteresis                                      |                                   |     | 0.10 |      | V    |

| $I_{QON}$             | Supply current: I <sub>VDD</sub> + I <sub>OUTH</sub> | Device on, V <sub>ENHS</sub> = 2V |     | 2.95 | 4    | mA   |

| Hot Swap FE           | ET ENABLE (ENHS)                                     |                                   |     |      |      |      |

| V <sub>ENHS</sub>     | Threshold voltage, rising                            |                                   | 1.3 | 1.35 | 1.4  | V    |

| V <sub>ENHShyst</sub> | Hysteresis                                           |                                   |     | 50   |      | mV   |

| I <sub>ENHS</sub>     | Input Leakage Current                                | 0 ≤ V <sub>ENHS</sub> ≤ 30V       | -1  |      | 1    | μΑ   |

| OVER VOLT             | AGE (OV)                                             |                                   |     |      |      |      |

| V <sub>OVR</sub>      | Threshold voltage, rising                            |                                   | 1.3 | 1.35 | 1.4  | mV   |

| V <sub>OVhyst</sub>   | Hysteresis                                           |                                   |     | 50   |      | mV   |

| lov                   | Input leakage current                                | 0 ≤ V <sub>OV</sub> ≤ 30V         | -1  |      | 1    | μΑ   |

Product Folder Links: TPS24772 TPS24771 TPS24770

## **Electrical Characteristics (continued)**

Unless otherwise noted these limits apply to the following: -40°C <  $T_J$ <125°C; 2.5V <  $V_{VDD}$ ,  $V_{OUT}$  < 18V;  $V_{ENHS}$  = 2 V;  $V_{OV}$  = 0 V;  $V_{HGATE}$ ,  $V_{PGHS}$ ,  $V_{FLTB}$ , and  $V_{IMONBUF}$  are floating;  $C_{INR}$  = 1nF;  $C_{FLT}$  = 1nF;  $R_{SET}$  = 44.2  $\Omega$ ;  $R_{IMON}$  = 2.98k  $\Omega$ ;  $R_{FSTP}$  = 200  $\Omega$ ;  $R_{PLIM}$  = 52 k $\Omega$ .

|                               | PARAMETER                                                                 | TEST CONDITION                                                                                                                                    | MIN    | TYP   | MAX    | UNIT   |

|-------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|--------|

| POWER LIMIT                   | PROGRAMING (PLIM)                                                         |                                                                                                                                                   |        |       |        |        |

| V <sub>PLIM.BIAS</sub>        | Bias voltage                                                              | Sourcing 10µA                                                                                                                                     | 0.65   | 0.675 | 0.7    | V      |

| 1 LIW,DIAO                    | <u> </u>                                                                  | $R_{PLIM} = 52 \text{ k}\Omega; V_{SENM-OUTH} = 12V$                                                                                              | 114.75 | 135   | 155.25 |        |

|                               |                                                                           | $R_{PLIM} = 105 \text{ k}\Omega; V_{SENM-OUTH} = 12V$                                                                                             | 56.95  | 67    | 77.05  |        |

| $V_{\text{IMON,PL}}$          | Regulated IMON voltage during power limit                                 | $R_{PLIM} = 261 \text{ k}\Omega; V_{SENM-OUTH} = 12V$                                                                                             | 18.9   | 27    | 35.1   | mV     |

| · IMON,PL                     | riogalatea interviolage adming perior initia                              | $R_{PLIM} = 105 \text{ k}\Omega; V_{SENM-OUTH} = 2V$                                                                                              | 341.7  | 402   | 462.3  |        |

|                               |                                                                           | $R_{PLIM} = 105 \text{ k}\Omega; V_{SENM-OUTH} = 18V$                                                                                             | 38.25  | 45    | 51.75  |        |

| SI OW TRIP T                  | HRESHOLD (SET)                                                            | TIPLIM = 100 102; VSENM-OUTH=10 V                                                                                                                 | 00.20  |       | 01.70  |        |

| V <sub>OS_SET</sub>           | Input referred offset (V <sub>SNS</sub> to V <sub>IMON</sub> scaling)     | D 4400 D 0104 4010 W 40 W                                                                                                                         | -150   |       | 150    | μV     |

| V <sub>GE SET</sub>           | Gain error (V <sub>SNS</sub> to V <sub>IMON</sub> scaling) <sup>(1)</sup> | $R_{SET} = 44.2\Omega$ ; $R_{IMON}=3k\Omega$ to 1.2kΩ ( $V_{SNS,CL}=10mV$ to 25mV)                                                                | -0.4%  |       | 0.4%   | μν     |

| _                             | HRESHOLD PROGRAMMING (FSTP)                                               | · · · · · · · · · · · · · · · · · · ·                                                                                                             | 0.470  |       | 0.470  |        |

|                               | FSTP input bias current                                                   | V <sub>ESTP</sub> =12V                                                                                                                            | 95     | 100   | 105    | ^      |

| I <sub>FSTP</sub>             | FSTF IIIput bias current                                                  | 1.41                                                                                                                                              | 18     |       |        | μΑ     |

| V                             | For a taking the souls and                                                | $R_{FSTP} = 200 \Omega$ , $V_{SNS}$ when $V_{HGATE} \downarrow$                                                                                   |        | 20    | 22     | \/     |

| V <sub>FASTRIP</sub>          | Fast trip threshold                                                       | $R_{FSTP} = 1 \text{ k}\Omega, V_{SNS} \text{ when } V_{HGATE} \downarrow$                                                                        | 95     | 100   | 105    | mV     |

| OUDDENT C'                    | MMINO NODE (IMON)                                                         | $R_{FSTP} = 4 \text{ k}\Omega, V_{SNS} \text{ when } V_{HGATE} \downarrow$                                                                        | 380    | 400   | 420    |        |

|                               | MMING NODE (IMON)                                                         | W. Author I. starts and                                                                                                                           | 000    | 075   | 202    |        |

| V <sub>IMON,CL</sub>          | Slow trip threshold at summing node                                       | V <sub>IMON</sub> ↑, when I <sub>TFLT</sub> starts sourcing                                                                                       | 660    | 675   | 690    | mV     |

| IMON-LKG                      | IMON leakage current                                                      | $V_{ENHS} = 0V$ , $V_{IMON} = 1.5V$                                                                                                               | -200   |       | 200    | nA     |

|                               | ONITOR (IMONBUF)                                                          |                                                                                                                                                   |        |       |        |        |

| V <sub>OS_IMONBUF</sub>       | Buffer offset                                                             | V <sub>IMON</sub> = 50mV to 675mV, Input referred                                                                                                 | -3     | 0     | 3      | mV     |

| GAIN <sub>IMONBUF</sub>       | Buffer voltage gain                                                       | $\Delta V_{\text{IMONBUF}} / \Delta V_{\text{IMON}}$                                                                                              | 2.97   | 2.99  | 3.01   | V      |

| BW <sub>IMONBUF</sub>         | Buffer closed loop bandwidth                                              | C <sub>IMONBUF</sub> = 75pF                                                                                                                       |        | 1     |        | MHz    |

| Hot Swap GA                   | TE DRIVER (HGATE)                                                         |                                                                                                                                                   |        |       |        |        |

|                               |                                                                           | $5 \le V_{VDD} \le 16V$ ; measure $V_{HGATE-OUTH}$                                                                                                | 12     | 13.6  | 15.5   | V      |

| V <sub>HGATE</sub>            | HGATE output voltage                                                      | 2.5V <v<sub>VDD &lt; 5V;<br/>16V <v<sub>VDD &lt; 20V measure V<sub>HGATE-OUTH</sub></v<sub></v<sub>                                               | 7      | 7.95  | 15     | ٧      |

| $V_{HGATEmax}$                | Clamp voltage                                                             | Inject 10µA into HGATE, measure V <sub>(HGATE - OUTH)</sub>                                                                                       | 12     | 13.9  | 15.5   | V      |

| I <sub>HGATEsrc</sub>         | Sourcing current                                                          | V <sub>HGAT-OUTH</sub> = 2V-10V                                                                                                                   | 44     | 55    | 66     | μΑ     |

| I <sub>HGATEfastSink</sub>    | Sinking current for fast trip                                             | V <sub>HGATE-OUTH</sub> = 2V–15V; V <sub>(FSTP – SENM)</sub> = 20mV                                                                               | 0.45   | 1     | 1.6    | Α      |

| I <sub>HGATEsustSink</sub>    | Sustained sinking current                                                 | Sustained, V <sub>HGATE-OUTH</sub> = 2V - 15V; V <sub>ENHS</sub> = 0                                                                              | 30     | 44    | 60     | mA     |

| INRUSH TIME                   | R (TINR)                                                                  |                                                                                                                                                   |        |       |        |        |

| I <sub>TINRsrc</sub>          | Sourcing current                                                          | V <sub>TINR</sub> = 0V, In power limit or current limit                                                                                           | 8      | 10.25 | 12.5   | μΑ     |

| I <sub>TINRsink</sub>         | Sinking current                                                           | V <sub>TINR</sub> = 2V, In regular operation                                                                                                      | 1.5    | 2     | 2.5    | μА     |

| V <sub>TINRup</sub>           | Upper threshold voltage                                                   | Raise V <sub>TINR</sub> until HGATE starts sinking                                                                                                | 1.3    | 1.35  | 1.4    | ·V     |

| V <sub>TINRIr</sub>           | Lower threshold voltage                                                   | Raise V <sub>TINR</sub> to 2V. Reduce V <sub>TINR</sub> until I <sub>TINR</sub> is sourcing.                                                      | 0.33   | 0.35  | 0.37   | V      |

| R <sub>TINR</sub>             | Bleed down resistance                                                     | $V_{VDD} = 0V$ , $V_{TINR} = 2V$                                                                                                                  | 70     | 104   | 130    | kΩ     |

| I <sub>TINR-PD</sub>          | Pulldown current                                                          | $V_{TINR} = 2V$ , when $V_{ENHS} = 0V$                                                                                                            | 2      | 4.2   | 7      | mA     |

| RETRY <sub>CYCLE</sub>        | Cycle number                                                              | # of timer cycles before retry (TPS24771 only)                                                                                                    | 64     | 64    | 64     | .11/ 3 |

| GYGLE                         | e, a.o. namboi                                                            | TFLT and TINR connected (TPS24771 only)                                                                                                           | 0-7    | 0.70% | 0.7    |        |

| $RETRY_DUTY$                  | Retry duty cycle                                                          | TFLT and TINR not connected (TPS24771 only)                                                                                                       |        | 0.75% |        |        |

| V <sub>IMON,TINR</sub>        | See Using Soft Start - I <sub>HGATE</sub> and TINR Considerations         | R <sub>PLIM</sub> = 52kΩ, V <sub>SENM</sub> = 12V, V <sub>OUTH</sub> = 0 V. Raise IMON voltage and record IMON when TINR starts sourcing current. | 47.75  | 90    | 132.25 | mV     |

| V <sub>IMON,PL</sub>          | See Using Soft Start - I <sub>HGATE</sub> and TINR Considerations         | $R_{PLIM} = 52k\Omega$ , $V_{SENM-OUTH} = 12V$ , Raise IMON voltage and record IMON when I <sub>HGATE</sub> starts sinking current.               | 114.75 | 135   | 155.25 | mV     |

| $\Delta V_{\text{IMON,TINR}}$ | See Using Soft Start - I <sub>HGATE</sub> and TINR Considerations         | $\Delta V_{IMON,TINR} = V_{IMON,PL} - V_{IMON,TINR}$                                                                                              | 23     | 45    | 67     | mV     |

|                               |                                                                           |                                                                                                                                                   |        |       |        |        |

<sup>(1)</sup> Specified by characterization.

**NSTRUMENTS**

## **Electrical Characteristics (continued)**

Unless otherwise noted these limits apply to the following: -40°C <  $T_J$ <125°C; 2.5V <  $V_{VDD}$ ,  $V_{OUT}$  < 18V;  $V_{ENHS}$  = 2 V;  $V_{OV}$  = 0 V;  $V_{HGATE}$ ,  $V_{PGHS}$ ,  $V_{FLTB}$ , and  $V_{IMONBUF}$  are floating;  $C_{INR}$  = 1nF;  $C_{FLT}$  = 1nF;  $R_{SET}$  = 44.2  $\Omega$ ;  $R_{IMON}$  = 2.98k  $\Omega$ ;  $R_{FSTP}$  = 200  $\Omega$ ;  $R_{PLIM}$  = 52 k $\Omega$ .

|                         | PARAMETER                                                | TEST CONDITION                                                          | MIN | TYP   | MAX  | UNIT |

|-------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|-----|-------|------|------|

| FAULT TIMER             | FAULT TIMER (TFLT)                                       |                                                                         |     |       |      |      |

| I <sub>TFLTsrc</sub>    | Sourcing current                                         | V <sub>TFLT</sub> = 0V, PGHS is high and in overcurrent                 | 8   | 10.25 | 12.5 | μΑ   |

| I <sub>TFLTsink</sub>   | Sinking current                                          | V <sub>TFLT</sub> = 2V, Not in overcurrent                              | 1.5 | 2     | 2.5  | μΑ   |

| $V_{TFLTup}$            | Upper threshold voltage                                  | Raise V <sub>TFLT</sub> until HGATE starts sinking                      | 1.3 | 1.35  | 1.4  | V    |

| R <sub>TFLT</sub>       | Bleed down resistance                                    | V <sub>ENHS</sub> = 0V, V <sub>TFLT</sub> = 2V                          | 70  | 104   | 130  | kΩ   |

| I <sub>TFLT-PD</sub>    | Pulldown current                                         | V <sub>TFLT</sub> = 2V, when V <sub>ENHS</sub> = 0V                     | 2   | 5.6   | 7    | mA   |

| HOT SWAP O              | UTPUT (OUTH)                                             |                                                                         |     |       |      |      |

| I <sub>OUTH, BIAS</sub> | Input bias current                                       | V <sub>OUTH</sub> = 12V                                                 |     | 30    | 70   | μΑ   |

| FAULT INDICATOR (FLTb)  |                                                          |                                                                         |     |       |      |      |

| V <sub>OL_FLTb</sub>    | Output low voltage                                       | Sinking 2 mA                                                            |     | 0.11  | 0.25 | V    |

| I <sub>FLTb</sub>       | Input leakage current                                    | V <sub>FLTb</sub> = 0V, 30V                                             | -1  | 0     | 1    | μΑ   |

| V <sub>HSFLT_IMON</sub> | V <sub>IMON</sub> threshold to detect Hot Swap FET short | V <sub>ENHS</sub> = 0V, Measured V <sub>IMON</sub> ↑ to GND when FLTb ↓ | 88  | 101   | 115  | mV   |

| V <sub>HSFL_hyst</sub>  | Hysteresis                                               |                                                                         |     | 25    |      | mV   |

|                         | OWER GOOD OUTPUT (PGHS)                                  |                                                                         |     |       |      |      |

| $V_{PGHSth}$            | PGHS Threshold                                           | Measure V <sub>SENM-OUTH</sub> ↓ when PGHS↑                             | 170 | 270   | 375  | mV   |

| V <sub>PGHShyst</sub>   | PGHS hysteresis                                          | V <sub>SENM-OUTH</sub> ↑                                                |     | 80    |      | mV   |

| V <sub>OL_PGHS</sub>    | PGHS Output low voltage                                  | Sinking 2mA                                                             |     | 0.11  | 0.25 | V    |

| I <sub>PGHS</sub>       | PHGS Input leakage current                               | V <sub>PGHS</sub> =0V to 30V                                            | -1  | 0     | 1    | μΑ   |

| THERMAL SHUTDOWN (OTSD) |                                                          |                                                                         |     |       |      |      |

| T <sub>OTSD</sub>       | Thermal shutdown threshold                               | Temperature rising                                                      |     | 140   |      | °C   |

| T <sub>OTSD,HYST</sub>  | Hysteresis                                               |                                                                         |     | 10    |      | °C   |

## 8.6 Timing Requirements

|                                        | PARAMETER                          | TEST CONDITION                                         | MIN   | TYP | MAX | UNIT |

|----------------------------------------|------------------------------------|--------------------------------------------------------|-------|-----|-----|------|

| INPUT SUPP                             | LY (VDD)                           |                                                        |       |     |     |      |

| DEGL <sub>UVLO</sub>                   | UVLO deglitch                      | Both rising and falling                                |       | 14  |     | μs   |

| HOT SWAP F                             | ET ENABLE (ENHS)                   |                                                        |       |     |     |      |

| DEGL <sub>ENHS</sub>                   | Deglitch time                      | Both rising and falling                                | 2.2   | 3.8 | 5.5 | μs   |

| OVER VOLTA                             | AGE (OV)                           |                                                        |       |     |     |      |

| DEGLOV                                 | Deglitch time                      | Both rising and falling                                | 2.2   | 3.9 | 5.7 | μs   |

| FAST TRIP (F                           | FSTP)                              |                                                        |       |     |     |      |

| t <sub>FastOffDly</sub>                | Fast turn-off delay                | $V_{(FSTP - SENM)}$ : -5mV to 5mV, $C_{HGATE} = 0$ pF  | 600   |     |     |      |

|                                        |                                    | $V_{(FSTP - SENM)}$ : -20mV to 20mV $C_{HGATE} = 0$ pF |       | 300 | ns  |      |

| t <sub>FastOffDur</sub>                | Strong pull down current duration  |                                                        | 53    | 63  | 73  | μs   |

| INRUSH TIME                            | ER (TINR)                          |                                                        |       |     |     |      |

| N <sub>RETRY</sub>                     | Number of TINR cycles before retry | TPS24741 only                                          |       | 64  |     |      |

|                                        | Datus distriction                  | T <sub>INR</sub> not connected to T <sub>FLT</sub>     | 0.35% |     |     |      |

| RETRY <sub>DUTY</sub> Retry duty cycle |                                    | T <sub>INR</sub> connected to T <sub>FLT</sub>         | 0.7%  |     |     |      |

| FAULT INDIC                            | ATOR (FLTb)                        |                                                        | -     |     |     |      |

| t <sub>FLT_degl</sub>                  | Fault deglitch                     | Both rising and falling                                | 2.2   | 3.9 | 5.3 | ms   |

|                                        | POWER GOOD OUTPUT (PGHS)           |                                                        |       |     |     |      |

| t <sub>PGHSdegl</sub>                  | PGHS deglitch time                 | Rising                                                 | 0.7   | 1   | 1.3 |      |

|                                        |                                    | Falling                                                | 7     | 8   | 9   | ms   |

Product Folder Links: TPS24772 TPS24771 TPS24770

## TEXAS INSTRUMENTS

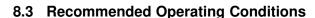

## 8.7 Typical Characteristics

Unless otherwise noted these cureves apply to the following:  $-40^{\circ}\text{C} < T_J < 125^{\circ}\text{C}$ ;  $2.5\text{V} < V_{VDD}$ ,  $V_{OUT} < 18\text{V}$ ;  $V_{ENHS} = 2\text{ V}$ ;  $V_{OV} = 0\text{ v}$ ;  $V_{HGATE}$ ,  $V_{PGHS}$ ,  $V_{FLTB}$ , and  $V_{IMONBUF}$  are floating;  $C_{INR} = 1\text{nF}$ ;  $C_{FLT} = 1\text{nF}$ ;  $R_{SET} = 44.2\ \Omega$ ;  $R_{IMON} = 2.98\text{k}\ \Omega$ ;  $R_{FSTP} = 200\ \Omega$ ;  $R_{PLIM} = 52\ \text{k}\Omega$ .

www.ti.com

## **Typical Characteristics (continued)**

Unless otherwise noted these cureves apply to the following: -40°C <  $T_J$ <125°C; 2.5V <  $V_{VDD}$ ,  $V_{OUT}$  < 18V;  $V_{ENHS}$  = 2 V;  $V_{OV}$  = 0 v;  $V_{HGATE}$ ,  $V_{PGHS}$ ,  $V_{FLTB}$ , and  $V_{IMONBUF}$  are floating;  $C_{INR}$  = 1nF;  $C_{FLT}$  = 1nF;  $R_{SET}$  = 44.2  $\Omega$ ;  $R_{IMON}$  = 2.98k  $\Omega$ ;  $R_{FSTP}$  = 200  $\Omega$ ;  $R_{PLIM}$  = 52 k $\Omega$ .

# TEXAS INSTRUMENTS

## 9 Detailed Description

#### 9.1 Overview

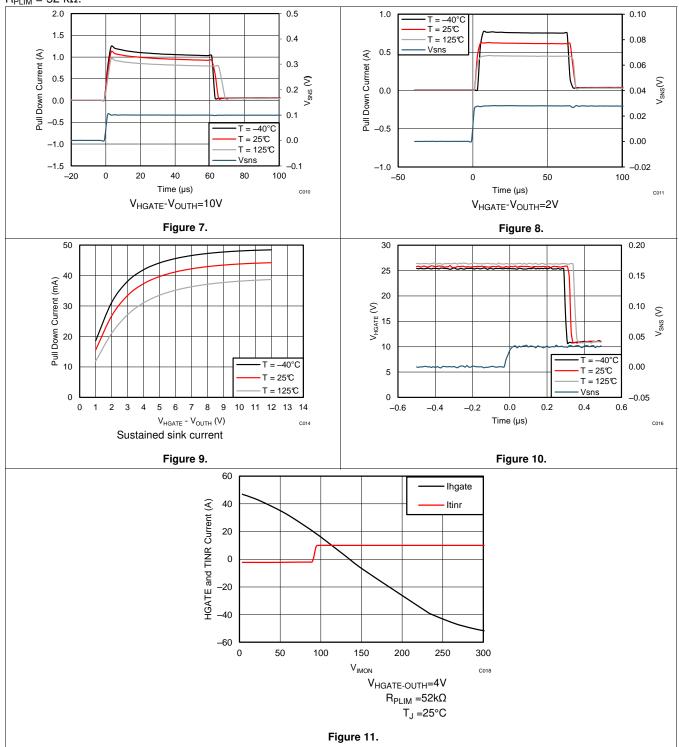

The TPS2477x Hot Swap features a programmable current limit, power limit, and fast trip threshold. It also has dual timers: one for inrush and one during over current faults. Finally it features an analog current monitor that can be used to provide current information to a microcontroller.

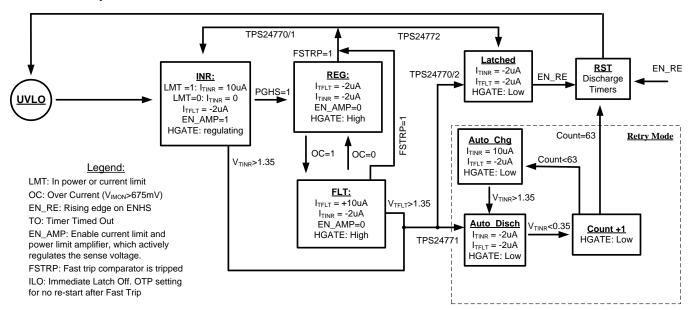

## 9.2 Functional Block Diagram

#### 9.3 Feature Description

## 9.3.1 Enable and Over-voltage Protection

The part is enabled when the ENHS pin voltage exceeds 1.35V and is disabled when the pin voltage falls under 1.3V providing 50mV of hysteresis. A resistor divider can be connected to these pins to turn on the TPS2477x at a certain bus voltage. The part will turn off if the OV pin exceeds 1.35V.

#### 9.3.2 Current Limit and Power Limit during Start-up

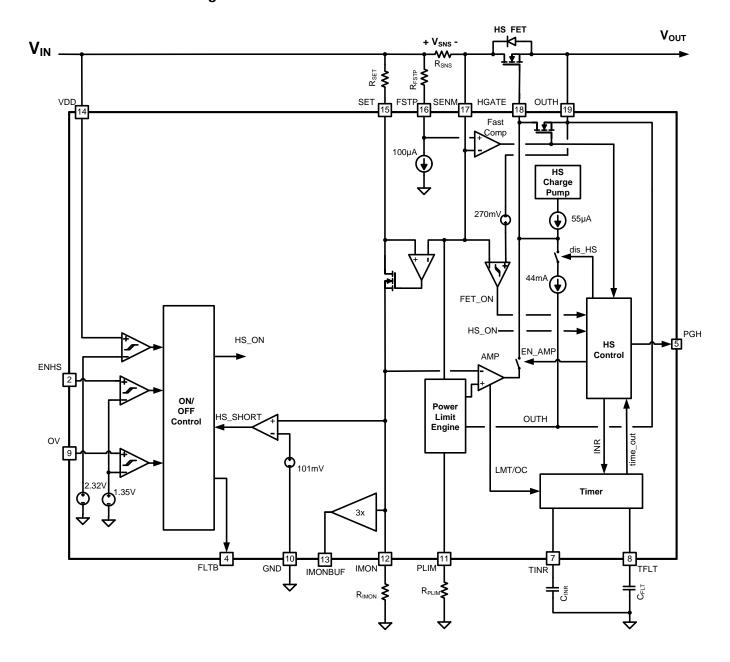

The current limit and power limit of the TPS2477x are programmable to protect the load, power supply, and the Hot Swap MOSFET. During start-up the active control loop will regulate the gate to ensure that the current through the MOSFET and the power dissipation of the MOSFET is below their respective pre-programmed thresholds. The maximum current allowed through the MOSFET ( $I_{LIM}$ ) is determined with the equation below.  $I_{LIM,CL}$  is the programmed current limit,  $P_{LIM}$  is the programmed power limit, and  $V_{DS}$  is the drain to source voltage across the Hot Swap MOSFET.

$$I_{LIM} = MIN \left( I_{LIM,CL}, \frac{P_{LIM}}{V_{DS}} \right)$$

(1)

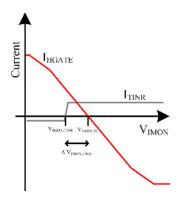

This results in an IV curve shown in Figure 12.  $I_{LIM,PL}$  denotes the maximum allowed MOSFET current ( $I_{DS}$ ) when the part is in power limit. As  $V_{DS}$  increases,  $I_{LIM,PL}$  decreases and  $I_{LIM,PL,MIN}$  denotes the lowest  $I_{LIM,PL}$ , which occurs at the largest  $V_{DS}$  ( $V_{DS,MAX}$ ). The TPS2477x enforce this by regulating the voltage across  $R_{SNS}$  ( $V_{SNS}$ ).  $V_{SNS,PL}$  decreases as  $V_{SNS}$  when power limiting is active. Similarly to  $I_{LIM,PL}$ ,  $V_{SNS,PL}$  decreases as  $V_{DS}$  increases and  $V_{SNS,PL,MIN}$  corresponds to the lowest  $V_{SNS,PL}$ , which occurs at  $V_{DS,MAX}$ .  $V_{SNS,CL}$  is a current limiting sense voltage, which is programmable in the TPS2477x.

Figure 12. Current vs V<sub>DS</sub> and V<sub>SNS</sub> vs V<sub>DS</sub> Programmed by Power Limit Engine.

The current and power limit can be programmed using the equations below.

$$V_{SNS,CL} = \frac{0.675 \times R_{SET}}{R_{IMON}}$$

(2)

$$I_{LIM,CL} = \frac{V_{SNS,CL}}{R_{SNS}} = \frac{0.675 \times R_{SET}}{R_{SNS}}$$

(3)

$$P_{LIM} = \frac{84375 \times R_{SET}}{R_{PLIM} \times R_{SNS} \times R_{IMON}}$$

(4)

# TEXAS INSTRUMENTS

### **Feature Description (continued)**

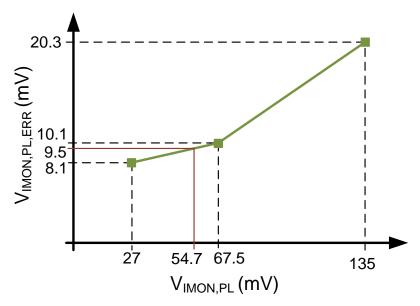

Note, that the error is largest at  $V_{SNS,PL,MIN}$  due to offset of the internal amplifier. Also the operation at  $V_{DS,MAX}$  is most critical because it corresponds to the short circuit condition and has the biggest impact on start time. Thus it is critical to consider  $V_{SNS,PL,MIN}$  during design. Equation 5 shows the relationship of  $V_{SNS,PL,MIN}$  as a function of  $P_{LIM}$ ,  $I_{LIM,CL}$ ,  $V_{SNS,CL}$ , and  $V_{DS,MAX}$ . Note that  $I_{LIM,CL}$  and  $V_{DS,MAX}$  are usually determined by the system requirements. The designer will have control over  $P_{LIM}$  and  $V_{SNS,CL}$ . In general, there will be a desire to reduce the power limit to allow for smaller MOSFETs and to reduce the  $V_{SNS,CL}$  to improve efficiency (lower  $R_{SNS}$ ). However, this will also reduce  $V_{SNS,PL,MIN}$  and the designer should ensure that it's above the minimum recommended value of 1.5mV.

$$V_{SNS,PL,MIN} = \frac{P_{LIM} \times V_{SNS,CL}}{V_{DS,MAX} \times I_{LIM,CL}}$$

(5)

#### 9.3.3 Two Level Protection During Regular Operation

After the TPS2477x has gone through start-up it will no longer actively control the gate. Instead it will run the timer when the current is between the current limit and the fast trip threshold. Once the timer has expired the gate will be pulled down. If the current ever exceeds the fast trip threshold, the gate will be pulled down immediately.

#### 9.3.4 Dual Timer (TFLT and TINR)

TPS2477x has two timer pins to allow the user to customize the protection. The TINR pin will source 10.25  $\mu$ A when the device is in start-up mode and is actively regulating the gate to limit the MOSFET power or current. It will sink 2  $\mu$ A otherwise. The TFLT pin will source 10.25  $\mu$ A when the device is in regular operation and the FET current exceeds the current limit. It will sink 2  $\mu$ A otherwise. If either of the timer pins exceeds 1.35, the TPS2477x will time out. The TPS24770 and TPS24772 will latch off. The TPS24771 will go through 64 cycles of TINR and attempt to start-up again.

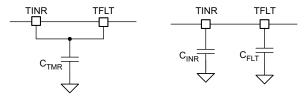

Since the TINR usually runs when the MOSFET is being stressed, TINR should be sized to maintain the FET within its SOA. In general TFLT runs when the load is drawing more current than expected, which can stress the load and the power supply. Thus TFLT should be programmed to have the right protection settings for the power supply and the load. In some systems the load is allowed to draw current above the current limit for 250ms or 1s. In that case a large TFLT is required, but a short TINR may still be desired to minimize the worst case FET stress. In other applications a long TINR may be required to due to large downstream capacitances, but drawing excessive current from the power supply for more than 5ms is not desired. In that case a short TFLT and a long TINR should be used. Finally, many applications can use the same TINR and TFLT setting, in which case the pins can be tied together and a single capacitor can be used. The two different options are shown in Figure 13.

Figure 13. Timer Configurations

If two separate timer capacitors are used their values can be computed with the equations below:

$$C_{INR} = 7.59 \ \mu F / s \times T_{INR} \tag{6}$$

$$C_{FLT} = 7.59 \ \mu F / s \times T_{FLT} \tag{7}$$

If a single capacitor is used C<sub>TMR</sub> can be computed with Equation 8.

12

#### **Feature Description (continued)**

$$C_{TMR} = 6.11 \,\mu\text{F} / \,\text{s} \times \text{T}_{TMR} \tag{8}$$

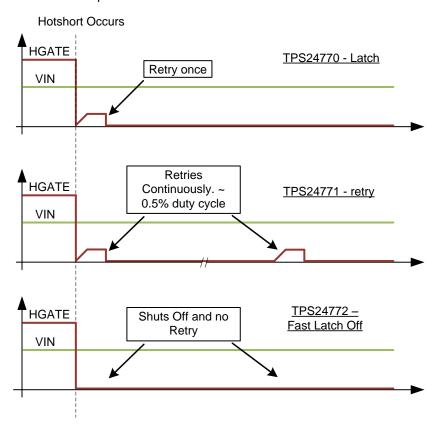

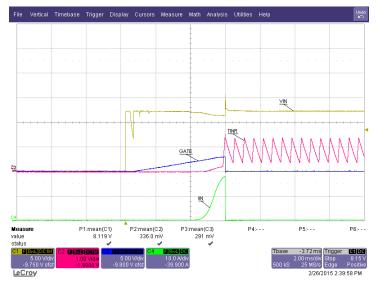

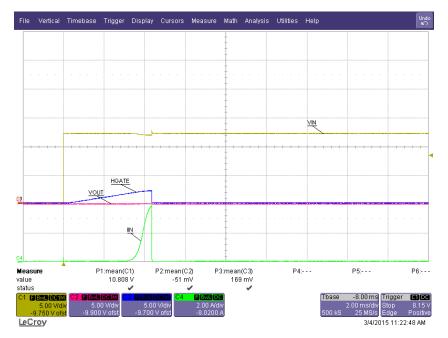

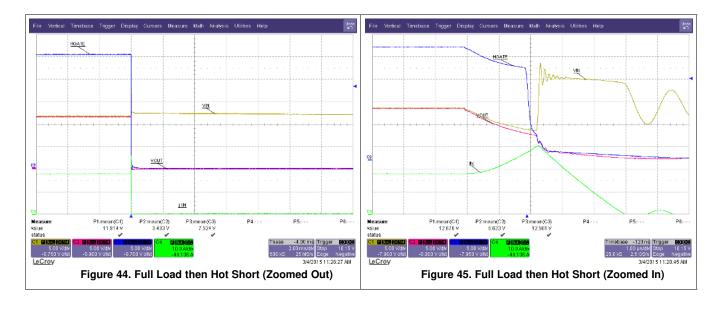

### 9.3.5 3 Options for Response to a Fast Trip

The TPS24770, TPS24771, and TPS24772 have difference responses to a fast trip event to accommodate different design requirements. When the current exceeds the fast trip threshold, the gate is quickly pulled down to minimize damage that can be caused due to a short circuit. Figure 14 shows the response of the variout devices options to a hot short on the output. The TPS24770 (latch) will attempt to re-start once after the hot-short is observed and then stay off, the TPS24771 will continuously retry with a duty cycle of  $\sim 0.5\%$  (0.7% if  $T_{FLT}$  and  $T_{INR}$  are connected, 0.35% if  $T_{FLT}$  and  $T_{INR}$  are not connected), and the TPS24772 (fast latch off) will shut off and never retry again. In general the TPS24772 will place the least amount of stress on the MOSFET, but is the least likely to recover from a nuissance trip.

Figure 14. TPS24770/1/2 Response to a Short Circuit

## 9.3.6 Using Soft Start - I<sub>HGATE</sub> and TINR Considerations

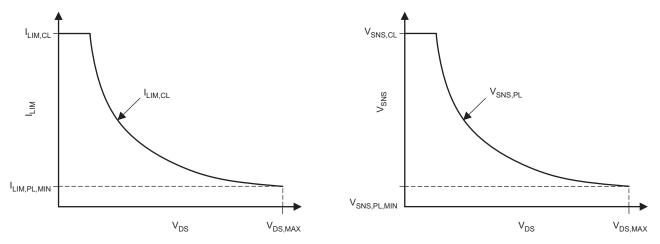

During start-up the TPS2477x regulates the HGATE to keep the FET power dissipation within  $P_{LIM}$ . This is accomplished by an amplifier that monitors the IMON voltage and an internal reference voltage. The TPS2477x will source current into HGATE if VIMON is lower than the reference voltage and will sink current into HGATE if VIMON is above the reference voltage. In steady state, the  $V_{IMON}$  will be regulated to the  $V_{IMON,PL}$  point, where  $I_{HGATE}$  equals zero. Note that  $V_{IMON,PL}$  is a determined by  $I_{PLIM}$  and  $I_{SENM}$  and  $I_{SENM}$  and  $I_{SENM}$  are  $I_{COUTH}$ .

The same amplifier feeds into the inrush timer circuitry to run the timer when the part is in power limit. The  $V_{IMON}$  threshold at which the timer starts to source current is denoted as  $V_{IMON}$ ,  $T_{INR}$ . Note that  $V_{IMON,TINR}$  is lower than  $V_{IMON,PL}$  to account for tolerances and ensure that the timer is always active when the device is in power limit. The difference between the two thresholds is defined as  $\Delta V_{IMON,TINR}$ . Refer to Figure 11 for a typical  $I_{HGATE}$  and  $I_{TINR}$  vs  $V_{IMON}$  curve.

# INSTRUMENTS

### **Feature Description (continued)**

Figure 15.  $I_{TINR}$  and  $I_{HGATE}$  vs  $V_{IMON}$  ( $V_{DS}$  = 12V,  $R_{PLIM}$  = 52k $\Omega$ )

It is critical to consider  $\Delta V_{IMON,\ TINR}$  and Figure 15 if a soft start circuit is used. Typically, the soft start is implemented by limiting the gate dv/dt with a capacitor, which in turn limits the inrush current to the output capacitor. Often times, the inrush current is kept below  $I_{LIM,PL}$  to keep the timer from running. Note that the  $I_{LIM,PL}$  is based on the  $V_{IMON,PL}$  threshold and thus  $T_{INR}$  can be activated even if the inrush current is below  $I_{LIM,PL}$ . To prevent the timer from running unintentionally, the  $P_{LIM}$  should be chosen above  $P_{LIM,MIN,SS}$ , which can be computed as shown below. As an example consider the usage case where the maximum inrush current ( $I_{INR,MAX}$ ) is 2A, the maximum input voltage ( $V_{IN,MAX}$ ) is 13V and  $R_{SET}$ ,  $R_{IMON}$ , and  $R_{SNS}$  are 100 $\Omega$ , 2.7k $\Omega$ , and 1m $\Omega$  respectively. For that case the power limit should be set to at least 58.3 W +  $P_{LIM}$  tolerance to ensure that the inrush timer doesn't run.

$$\begin{split} P_{\text{LIM,MIN,SS}} = & \left( I_{\text{INR,MAX}} + \Delta V_{\text{IMON,TINR,MAX}} \times \frac{R_{\text{SET}}}{R_{\text{IMON}} \times R_{\text{SNS}}} \right) \times V_{\text{IN,MAX}} \\ = & \left( 2A + 67 \text{mV} \times \frac{100\Omega}{2.7 \text{k}\Omega \times 1 \text{m}\Omega} \right) \times 13 \text{V} = 58.3 \text{W} \end{split} \tag{9}$$

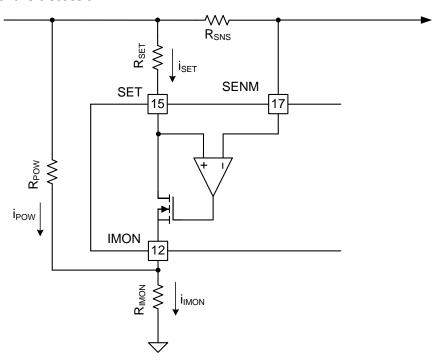

#### 9.3.7 Analog Current Monitor

The TPS2477x also features two analog current monitoring outputs: IMON and IMONBUF. Each has their own advantages and disadvantages. The IMON is more accurate, because it doesn't have the error added from the second stage. However it is a high impedance output and leakage current on that node would result in monitoring error. In addition it can only support 30pF of capacitance and its full scale range is 675mV (this is where current limit kicks in). The IMONBUF takes the IMON signal and buffers it 3x. This introduces more error, but the output is low impedance, has a larger full scale range, and can drive up to 100pF of capacitance.

Submit Documentation Feedback

### **Feature Description (continued)**

Figure 16. Current Monitoring Circuitry

#### 9.3.8 Power Good Flag

The TPS2477x has a power good flag, which should be used to turn on downstream DC/DC converters. This reduces the stress on the Hot Swap MOSFET during start-up. The PGHS pin of the TPS2477x is asserted (with 1 ms deglitch) when both:

- Hot Swap is enabled and

- V<sub>DS</sub> of Hot Swap MOSFET is below 240 mV.

PGHS is de-asserted (with 8 ms deglitch) when either:

- Hot Swap is disabled.

- VDS of Hot Swap MOSFET is above 310 mV

- In an overcurrent condition that causes the timer to time out and latch off.

## 9.3.9 Fault Reporting

TPS2477x will assert a fault by pulling down on the FLTb pin if any of the following occur:

- Hot Swap MOSFET Shorted Fault (ENHS = LO, but VIMON > 101 mV)

- · Hot Swap timer times out.

- Over Temperature Shut Down (OTSD)

# INSTRUMENTS

#### 9.4 Device Functional Modes

#### 9.4.1 Hot Swap Functional Modes

The state machine for the Hot Swap section is shown in Figure 17. After a POR / UVLO event the Hot Swap enters the Inrush up. Once operational the Hot Swap has the following functional modes:

- Inrush Mode (INR): In this state the Hot Swap controller is actively regulating the HGATE to meet the current limit and power limit settings. The inrush timer is running if the controller is in power or current limiting. If the inrush timer times out the gate will be pulled down. The TPS24770 and TPS24772 will go to latched mode and TPS24771 will go into retry mode.

- Regular Operation Mode (REG): In this mode everything is operating properly so both the timers are discharged and the HGATE is high. If there is an overcurrent condition (V<sub>SNS</sub> > V<sub>SNS,CL</sub>), the device will go into fault mode. If there is a fast trip condition (V<sub>SNS</sub> > V<sub>FSTP</sub>), the gate will be pulled down with a 1A / 63 µs pulse. The TPS24772 will go to the latched state and the TPS24770 and TPS24771 will go back to inrush for a retry.

- Fault Mode (FLT): In this mode the TPS2477x runs the fault timer. Once the timer expires the TPS24770 and TPS24772 will go to latch mode while TPS24771 will go to retry mode. If the overcurrent condition is removed the controller will go back to the regular operation mode.

- Latched Mode (Latched): In the latched mode the HGATE is low, the timer is being discharged, and the FLTb is asserted. If there is a rising edge on ENHS the part will discharge the timers and go to the inrush mode.

- Retry Mode (Retry): Here the part will charge and discharge the inrush timer 64 times before attempting another retry.

Figure 17. Hot Swap State Machine

6 Submit Documentation Feedback

## 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 10.1 Application Information

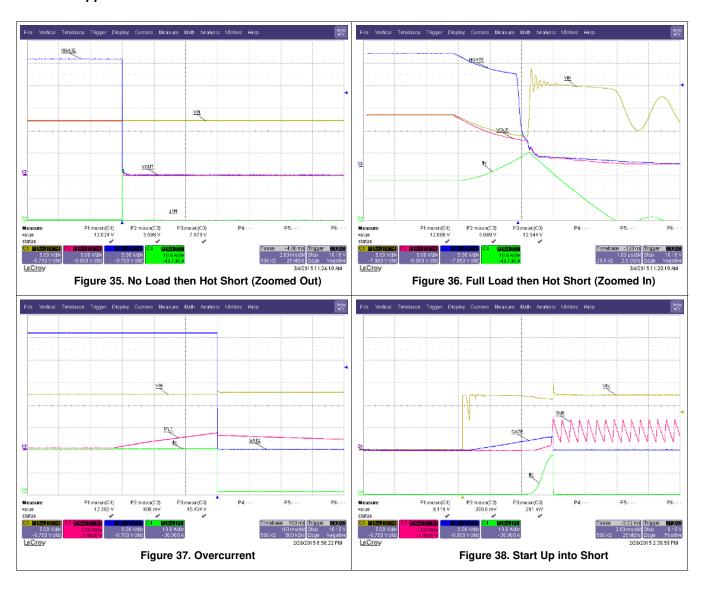

The TPS2477x is a highly configurable Hot Swap controller that can be fine-tuned for the application requirement. When designing a Hot Swap 3 key scenarios should be considered:

- Start-up.

- Output of a Hot Swap is shorted to ground when the Hot Swap is on. This is often referred to as a "Hot-Short".

- Powering up a board when the output and ground are shorted. This is usually called a "start into short".

All of these scenarios place a lot of stress on the Hot Swap MOSFET and special care must be taken when designing the Hot Swap circuit to keep the MOSFET within its Safe Operating Area (SOA). Note that the component selection can often be iteratively and it's recommended to use the publically available excel calculators to crunch the numbers. See the TPS24770 Design Calculator in the Tools & Software link on the Product folder.

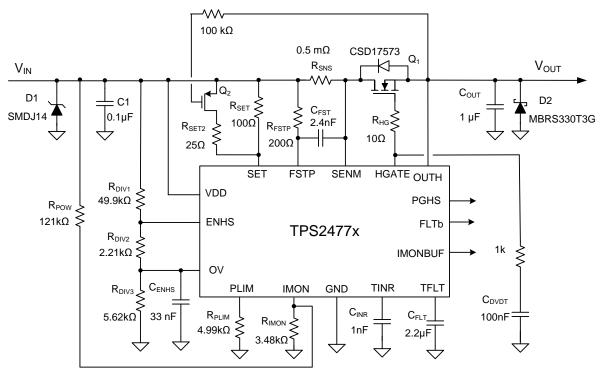

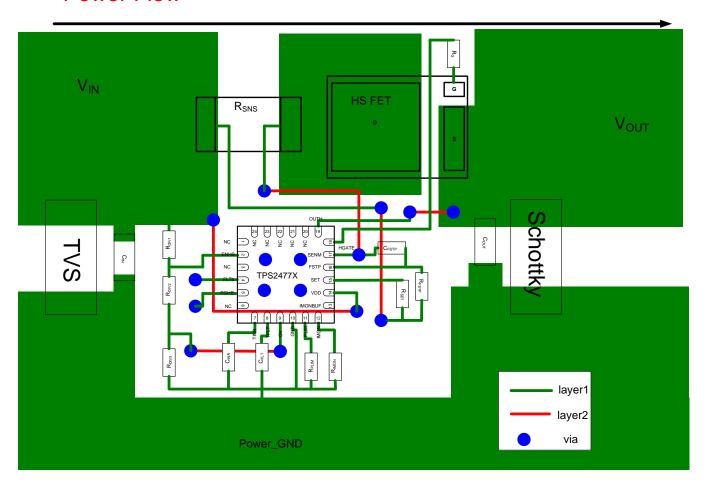

## 10.2 Typical Application

Three application examples are provided. The first one is for a 100A Hot Swap with 5,500  $\mu$ F of output capacitance that uses standard power limited based start-up. Then there are two examples of designing for the 240 VA design requirment. One uses the CSD16415Q5B, which is an older generation MOFSET with great SOA. The second one uses the CSD17573Q5B, which has lower SOA, but is more cost effective (price vs  $R_{DSON}$ ).

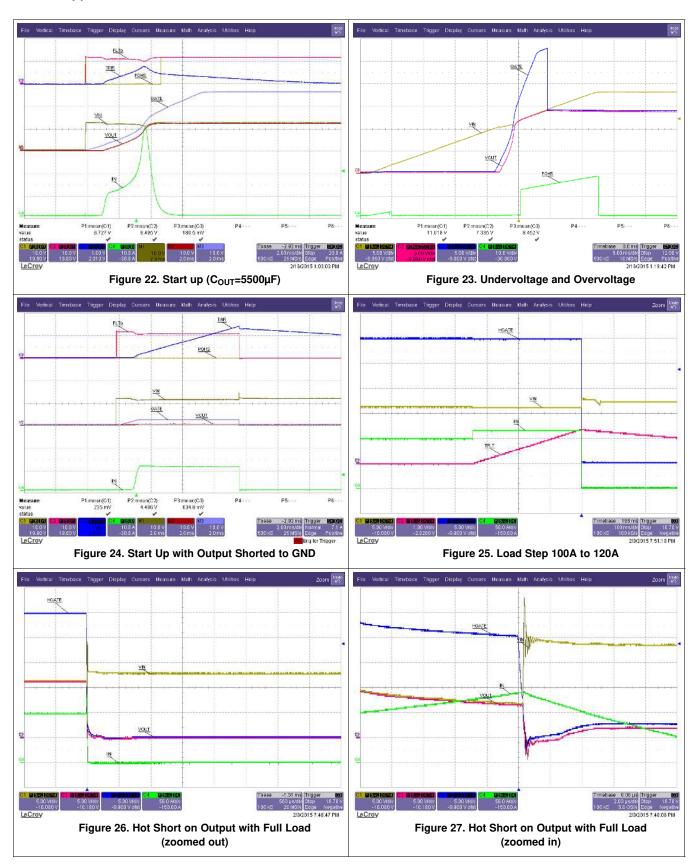

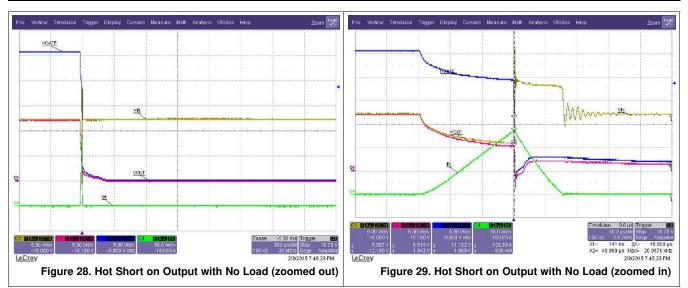

### 10.2.1 12 V, 100 A, 5,500 μF Analog Hot Swap Design

The diagram below shows the application schematic for this design example.

Figure 18. Application Schematic for 100 A Hot Swap

# Typical Application (continued)

#### 10.2.2 Design Requirements

Table 1 summarizes the design parameters that must be known before designing a Hot Swap circuit. When charging the output capacitor through the Hot Swap MOSFET, the FET's total energy dissipation equals the total energy stored in the output capacitor ( $1/2CV^2$ ). Thus both the input voltage and output capacitance will determine the stress experienced by the MOSFET. The maximum load current will drive the current limit and sense resistor selection. In addition, the maximum load current, maximum ambient temperature, and the thermal properties of the PCB ( $R_{\theta CA}$ ) will drive the selection of the MOSFET  $R_{DSON}$  and the number of MOSFETs used.  $R_{\theta CA}$  is a strong function of the layout and the amount of copper that is connected to the drain of the MOSFET. Air cooling will also reduce  $R_{\theta CA}$ . It's also important to know if there are any transient load requirements. Finally, whether current monitoring is needed and its accuracy requirement will drive the selection of  $R_{SNS}$ ,  $R_{IMON}$ , and  $R_{SET}$ .

Table 1. Design Requirements for a 12V, 100A, 5500µF Hot Swap Design

| DESIGN PARAMETER                               | EXAMPLE VALUE   |  |

|------------------------------------------------|-----------------|--|

| Input voltage range                            | 11 V – 13 V     |  |

| Maximum DC load current                        | 100A            |  |

| Maximum Output Capacitance of the Hot Swap     | 5500 μF         |  |

| Maximum Ambient Temperature                    | 55°C            |  |

| MOSFET R <sub>0CA</sub> (function of layout)   | 50°C/W          |  |

| Transient load requirement                     | 130A for 250 ms |  |

| Pass "Hot-Short" on Output?                    | Yes             |  |

| Pass a "Start into short"?                     | Yes             |  |

| Is the load off until PG asserted?             | Yes             |  |

| Can a Hot Board be plugged in or Power Cycled? | No              |  |

| IC used                                        | TPS24772        |  |

| Analog Current Monitor Used                    | No              |  |

#### 10.2.3 Detailed Design Procedure

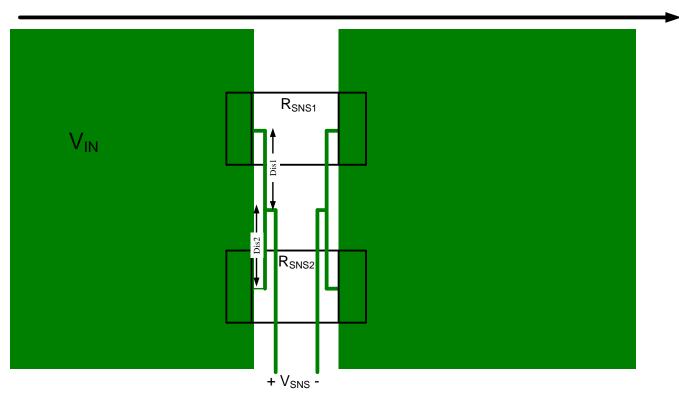

#### 10.2.3.1 Select R<sub>SNS</sub> and V<sub>SNS.CL</sub> Setting

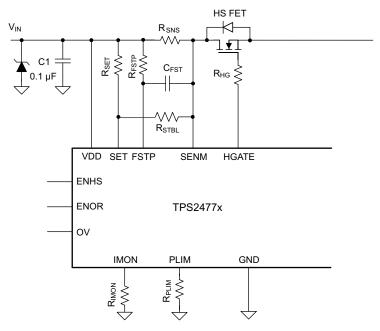

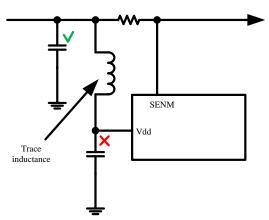

TPS2477x has a programmable  $V_{SNS,CL}$  with a recommended range of 10 mV to 67.5 mV. It can be used with a  $V_{SNS,CL}$  up to 200 mV, but that requires a resistor between SET and SENM to ensure stability of an internal loop. This is shown in Figure 19.  $R_{STBL}$  can be computed using the equation below.

$$R_{STBL} = \frac{R_{IMON} \times R_{SET}}{10 \times R_{SET} - R_{IMON}}$$

(10)

For high power applications a lower  $V_{SNS,CL}$  leads to better efficiency so 20 mV is targeted for this design. Targeting a current limit of 110A to allow margin for the load, the sense resistor can be calculated as follows:

$$R_{SNS,CLC} = \frac{V_{SNS,TGT}}{I_{LIM}} = \frac{20 \text{ mV}}{110 \text{ A}} = 0.18 \text{ m}\Omega$$

$$\tag{11}$$

Since 0.18 m $\Omega$  resistors aren't available, the closest standard resistor should be chosen. To have better efficiency, three 0.5m $\Omega$  resistors are used in parallel. Next the  $V_{SNS,CL}$  should be computed based on the actual  $R_{SNS}$  and then used to compute  $R_{SET}$  and  $R_{IMON}$ .  $R_{SET}$  is chosen to target 250  $\mu A$  of current through SET and IMON pins during current limit.

$$V_{SNS,CL} = I_{LIM} \times R_{SNS} = 110 \text{ A} \times 0.1667 \text{ m}\Omega = 18.37 \text{ mV}$$

(12)

$$R_{SET,CLC} = \frac{V_{SNS,CL}}{250 \ \mu A} = 73.3 \ \Omega \tag{13}$$

Chose  $R_{SET}$  to equal 73.2  $\Omega$ , which is the closest available standard resistor. Next obtain the calculated  $R_{IMON}$  ( $R_{IMON,CLC}$ ) as follows:

$$R_{\text{IMON,CLC}} = \frac{R_{\text{SET}} \times 675 \text{ mV}}{V_{\text{SNS,CL}}} = \frac{73.2 \ \Omega \times 675 \text{ mV}}{18.37 \text{ mV}} = 2.69 \text{ k}\Omega$$

(14)

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

**STRUMENTS**

Choose  $2.67k\Omega$  resistor for  $R_{IMON}$ , which is the closest available standard resistor. Since accurate current monitoring is not needed a 2512 2 terminal sense resistor can be used.

Finally, compute the actual current limit ( $I_{LIM,CL}$ ) and the analog current monitoring scaling factor  $V_{IMON,GAIN}$  ( $V_{IMON}$  vs  $I_{LOAD}$ )

$$I_{LIM,CL} = \frac{0.675 \text{ V} \times R_{SET}}{R_{IMON} \times R_{SENSE}} = \frac{0.675 \text{ V} \times 73.2 \Omega}{2.67 \text{ k}\Omega \times 0.1667 \text{ m}\Omega} = 111 \text{ A}$$

(15)

$$V_{IMON,GAIN} = \frac{R_{IMON} \times R_{SNS}}{R_{SET}} = \frac{0.1667 \text{ m}\Omega \times 2.67 \text{ k}\Omega}{73.2\Omega} = 6.08 \text{ mV / A}$$

$$(16)$$

Figure 19. Adding  $R_{STBL}$  for  $V_{SNS,CL} > 67.5 mV$

#### 10.2.3.2 Selecting the Fast Trip Threshold and Filtering

The TPS2477x allows the user to program the fast trip threshold. When this threshold is exceeded the gate is quickly pulled down ( $<1\mu$ s). In addition  $C_{FSTP}$  can be added to include some filtering into the comparator. The selection of the fast trip threshold and filtering is influenced by the systems environment and requirements. In general, picking a larger threshold and larger filtering time will result in more immunity to nuisance trips, but also a slower response (possibly inadequate) to real fault conditions. It's best to fine tune these threshold after testing the real system. As a starting point it is recommended to set the fast trip threshold at least 1.25x larger than then current limit. For this design example a 150A fast trip threshold along with a 500ns filtering time constant were targeted to ensure that the transient requirement will be passed. The value for  $R_{FSTP}$  and  $C_{FSTP}$  can be computed as shown below:

$$R_{FSTP} = \frac{I_{FSTP} \times R_{SNS}}{100 \ \mu A} = \frac{150 \ A \times 0.1667 \ m\Omega}{100 \ \mu A} = 250 \ \Omega \tag{17}$$

$$C_{FSTP} = \frac{t_{FSTP}}{R_{FSTP}} = \frac{500 \text{ ns}}{250 \Omega} = 2 \text{ nF}$$

(18)

The next closest standard resistor and capacitor values should be chosen. In this case  $R_{\text{FSTP}}$  = 249 $\Omega$  and  $C_{\text{FSTP}}$ =2nF

#### IEXAS INSTRUMENTS

#### 10.2.3.3 Selecting the Hot Swap FET(s)

It is critical to select the correct MOSFET for a Hot Swap design. The device must meet the following requirements:

- The V<sub>DS</sub> rating should be sufficient to handle the maximum system voltage along with any ringing caused by transients. For most 12V systems a 25 V or 30V FET is a good choice.

- The SOA of the FET should be sufficient to handle all usage cases: start-up, hot-short, start into short.

- R<sub>DSON</sub> should be sufficiently low to maintain the junction and case temperature below the maximum rating of the FET. In fact, it is recommended to keep the steady state FET temperature below 125°C to allow margin to handle transients.

- Maximum continuous current rating should be above the maximum load current and the pulsed drain current

must be greater than the current threshold of the circuit breaker. Most MOSFETs that pass the first three

requirements will also pass these two.

- A  $V_{GS}$  rating of +16 V is required, because the TPS2477x can pull up the gate as high as 15.5 V above source.

For this design the CSD16415Q5B was selected for its low  $R_{DSON}$  and superior SOA. After selecting the MOSFET, the maximum steady state case temperature can be computed as follows:

$$T_{C,MAX} = T_{A,MAX} + R_{\theta CA} \times I_{LOAD,MAX}^2 \times \frac{R_{DSON}(T_J)}{n^2}$$

(19)

In the equation above n is the number of FETs used in parallel. For this example 4 FETS are used in parallel to prevent over- heating and improve efficiency. Note that the  $R_{DSON}$  is a strong function of junction temperature, which for most MOSFETS will be very close to the case temperature. A few iterations of the above equations may be necessary to converge on the final  $R_{DSON}$  and  $T_{C,MAX}$  value. According to the CSD16415Q5B datasheet, its  $R_{DSON}$  is about 1.3x greater at 100°C compared to room temperature . The equation below uses this  $R_{DSON}$  value to compute the  $T_{C,MAX}$ . Note that the computed  $T_{C,MAX}$  is close to the junction temperature assumed for  $R_{DSON}$ . Thus no further iterations are necessary. For this example an  $R_{\theta CA}$  of 50°C/W was used since there are 4 FETs close together and it's expected that they will heat each other up. It's highly recommended to test the board at full load and double check the thermals with the calculations.

$$T_{C,MAX} = 55^{\circ}C + 50^{\circ} \frac{C}{W} \times (100A)^{2} \times \frac{(1.3 \times 1 \text{ m}\Omega)}{4^{2}} = 95.6^{\circ}C$$

(20)

#### 10.2.3.4 Select Power Limit

In general, a lower power limit setting is preferred to reduce the stress on the MOSFET. However, at low power limit levels both the  $V_{SNS}$  and  $V_{IMON}$  become very low, which results in more error caused by offsets. It is recommended to keep  $V_{SNS}$  above 1.5mV and  $V_{IMON}$  above 27mV to ensure reasonable accuracy of the power limit engine. Based on these requirements the minimum power limit can be computed as shown below.

$$\begin{split} P_{\text{LIM,MIN}} &= \frac{V_{\text{IN,MAX}}}{R_{\text{SNS}}} \times \text{MIN} \left( V_{\text{SNS,MIN}}, \frac{V_{\text{IMON,MIN}} \times R_{\text{SET}}}{R_{\text{IMON}}} \right) \\ &= \frac{13 \text{ V}}{0.1667 \text{ m}\Omega} \times \text{MIN} \left( 1.5 \text{ mV}, \frac{27 \text{ mV} \times 73.2 \Omega}{2.67 \text{ k}\Omega} \right) = 117 \text{ W} \end{split}$$

In most applications the power limit can be set to  $P_{\text{LIM},\text{MIN}}$  using the equation below. Here  $R_{\text{SNS}}$  and  $R_{\text{PWR}}$  are in  $\Omega s$  and  $P_{\text{LIM}}$  is in Watts.

$$R_{PLIM} = \frac{84375 \times R_{SET}}{R_{SNS} \times R_{IMON} \times P_{LIM}} = \frac{84375 \times 73.2 \ \Omega}{0.1.667 \ m\Omega \times 2.67 \ k\Omega \times 117 \ W} = 118.6 \ k\Omega \tag{22}$$

The closest available resistor should be selected. In this case it is a 118 k $\Omega$ .

SLVSC73 - MARCH 2015

#### 10.2.3.5 Set Fault Timer

The inrush timer runs when the Hot Swap is in power limit or current limit, which is the case during start-up. Thus the timer has to be sized large enough to prevent a time-out during start-up. If the part starts directly into current limit ( $I_{LIM} \times V_{DS} < P_{LIM}$ ) the maximum start time can be computed with the equation below:

$$t_{\text{start,max}} = \frac{C_{\text{OUT}} \times V_{\text{IN,MAX}}}{I_{\text{LIM,CL}}}$$

(23)

For most designs (including this example)  $I_{LIM,CL} \times V_{DS} > P_{LIM}$  so the Hot Swap will start in power limit and transition into current limit. In that case the maximum start time can be computed as follows:

$$t_{\text{start,max}} = \frac{C_{\text{OUT}}}{2} \times \left[ \frac{V_{\text{IN,MAX}}^2}{P_{\text{LIM}}} + \frac{P_{\text{LIM}}}{I_{\text{LIM,CL}}^2} \right] = \frac{5500 \ \mu\text{F}}{2} \times \left[ \frac{(13 \ \text{V})^2}{117 \ \text{W}} + \frac{117 \ \text{W}}{(110 \ \text{A})^2} \right] = 4.0 \ \text{ms}$$

(24)

Note that the above start-time is based on typical current limit and power limit values. To ensure that the timer never times out during start-up it is recommended to set the fault time (TINR) to be 1.5x t<sub>start,max</sub> or 6 ms. This will account for the variation in power limit, timer current, and timer capacitance.

Next the designer should decide if having equal TINR and TFLT is acceptable. Note that to pass the load transient the fault timer needs to be longer than 200 ms. If the inrush time is this long, it will place too much stress on the MOSFET during a start into short. For this reason, it's ideal to have two separate timers. To ensure proper start up and to pass the load transient a target inrush time (TINR.TGT) of 6 ms and a target fault time  $(T_{FLT,TGT})$  of 250ms is used.  $C_{INR,CLC}$  and  $C_{FLT,CLC}$  is computed as follows:  $C_{INR,CLC} = 7.59 \ \mu F / s \times T_{INR,TGT} = 7.59 \ \mu F / s \times 6 \ ms = 45.6 \ nF$

$$C_{INR,CLC} = 7.59 \ \mu F / s \times T_{INR,TGT} = 7.59 \ \mu F / s \times 6 \ ms = 45.6 \ nF$$

(25)

$$C_{FLT,CLC} = 7.59 \ \mu F / s \times T_{FLT,TGT} = 7.59 \ \mu F / s \times 250 \ ms = 1898 \ nF$$

(26)

The next largest available C<sub>INR</sub> is chosen as 47 nF and the next largest available C<sub>FLT</sub> is chosen as 2.2μF

Next, the actual  $T_{\text{INR}}$  and  $T_{\text{FLT}}$  can be computed as shown below: Once the  $C_{\text{TMR}}$  is chosen the actual programmed time out can be computed as follows.

$$T_{TMR} = \frac{C_{INR}}{7.59 \ \mu F/s} = \frac{47 \ nF}{7.59 \ \mu F/s} = 6.2 \ ms \tag{27}$$

$$T_{FLT} = \frac{C_{FLT}}{7.59 \ \mu\text{F/s}} = \frac{2.2 \ \mu\text{F}}{7.59 \ \mu\text{F/s}} = 290 \ \text{ms} \tag{28}$$

## 10.2.3.6 Check MOSFET SOA

Once the power limit and fault timer are chosen, it's critical to check that the FET will stay within its SOA during all test conditions. For this design example the TPS24772 is used, which does not retry during a hot-short. Thus the worst condition is a start-up into a short circuit. In this case the TPS24772 will start into a power limit and regulate at that point for 6.2 ms (T<sub>INB</sub>). Based on the SOA of the CSD16415Q5B, it can handle 13 V, 15 A for 10 ms and it can handle 13 V, 100 A for 1 ms. The SOA for 6.2 ms can be extrapolated by approximating SOA vs time as a power function as shown below:

$$I_{SOA}(t) = a \times t^{m}$$

$$m = \frac{\ln(I_{SOA}(t_1)/I_{SOA}(t_2))}{\ln(t_1/t_2)} = \frac{\ln(\frac{100 \text{ A}}{15 \text{ A}})}{\ln(\frac{1 \text{ ms}}{10 \text{ ms}})} = -0.82$$

$$a = \frac{I_{SOA}(t_1)}{t_1^m} = \frac{100 \text{ A}}{(1 \text{ ms})^{-0.82}} = 100 \text{ A} \times (\text{ms})^{0.82}$$

$$I_{SOA}$$

(6.2 ms) = 100 A×(ms)<sup>0.82</sup> ×(6.2 ms)<sup>-0.82</sup> = 22.4 A (29)

Note that the SOA of a MOSFET is specified at a case temperature of 25°C, while the case temperature can be hotter during a start into a short. It is important to understand the hottest temperature that a MOSFET can be during a start-up ( $T_{C, MAX, START}$ ). If a board has been off for a while and then it's turned on  $T_{A, MAX}$  is a good estimate for  $T_{C,MAX, START}$ . However, if a board is on and then gets power cycled or a hot board is unplugged and plugged back in  $T_{C,MAX}$  should be used for  $T_{C,MAX,STAR}$ . This will depend on system requirements. For this design example it's assumed that the board can only be plugged in cold and  $T_{A,MAX}$  is used to estimate  $T_{C,MAX,START}$ .

$$I_{SOA}\left(6.2 \text{ ms}, T_{C,MAX,START}\right) = I_{SOA}\left(6.2 \text{ ms}, 25^{\circ}C\right) \times \frac{T_{J,ABSMAX} - T_{A,MAX}}{T_{J,ABSMAX} - 25^{\circ}C} = 22.4 \text{ A} \times \frac{150^{\circ}C - 55^{\circ}C}{150^{\circ}C - 25^{\circ}C} = 17 \text{ A} \tag{30}$$

Based on this calculation the MOSFET can handle 17 A, 13 V for 6.2 ms at 55°C elevated case temperature, but is only required to handle 9A during a start into short. Thus there is good margin and this will be a robust design. In general, it is recommended that the MOSFET can handle 1.3x more than what is required during a hot-short. This provides margin to cover the variance of the power limit and fault time.

#### 10.2.3.7 Choose Under Voltage and Over Voltage Settings

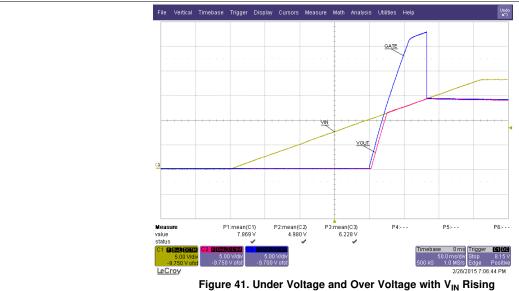

The TPS2477x has comparators with 1.35V threshold on the ENHS, ENOR, and OV pins. A resistor divider can be used to set Undervoltage and Overvoltage thresholds for the bus. For this design example 10V and 14V were chosen as the limits to allow some margin for the 11V to 13V input bus. Once these limits are known,  $R_{\text{DIV}2}$  and  $R_{\text{DIV}3}$  can be computed using the equations below.  $R_{\text{DIV}1}$  was set to 49.9 k $\Omega$ , which keeps the power consumption reasonable low without being too susceptible to leakage currents.

$$R_{DIV2,3} = R_{DIV2} + R_{DIV3} = \frac{R_{DIV1} \times 1.35 \text{ V}}{V_{UV} - 1.35 \text{ V}} = \frac{49.9 \text{ k}\Omega \times 1.35 \text{ V}}{10 \text{ V} - 1.35 \text{ V}} = 7.79 \text{ k}\Omega$$

(31)

$$R_{DIV3} = \frac{\left(R_{DIV1} + R_{DIV2,3}\right) \times 1.35 \text{ V}}{V_{OV}} = \frac{\left(49.9 \text{ k}\Omega + 7.79 \text{ k}\Omega\right) \times 1.35 \text{ V}}{14 \text{ V}} = 5.56 \text{ k}\Omega$$

(32)

$$R_{\text{DIV2}} = R_{\text{DIV2,3}} - R_{\text{DIV1}} = 7.79 \text{ k}\Omega - 5.56 \text{ k}\Omega = 2.23 \text{ k}\Omega \tag{33}$$

Choose closest available resistors standard 1% resistors:  $R_{DIV2}$  = 2.21 k $\Omega$  and  $R_{DIV3}$  = 5.62 k $\Omega$ . The actual Under Voltage and Over Voltage settings can be computed for the chosen resistors as follows:

$$V_{UV\_act} = 1.35 \text{V} \times \frac{R_{DIV1} + R_{DIV2} + R_{DIV3}}{R_{DIV2} + R_{DIV3}} = 1.35 \text{ V} \times \frac{2.21 \text{ k}\Omega + 5.62 \text{ k}\Omega + 49.9 \text{ k}\Omega}{2.21 \text{ k}\Omega + 5.62 \text{ k}\Omega} = 9.95 \text{ V}$$

(34)

$$V_{OV\_act} = 1.35 \text{ V} \times \frac{R_{DIV1} + R_{DIV2} + R_{DIV3}}{R_{DIV3}} = 1.35 \text{ V} \times \frac{2.21 \text{ k}\Omega + 5.62 \text{ k}\Omega + 49.9 \text{ k}\Omega}{5.62 \text{ k}\Omega} = 13.87 \text{ V}$$

(35)

#### 10.2.3.8 Selecting C<sub>1</sub> and C<sub>OUT</sub>

It is recommended to add ceramic bypass capacitors to help stabilize the voltages on the input and output. Since  $C_{IN}$  will be charged directly on hot-plug, its value should be kept small.  $0.1\mu F$  is a good target. Since  $C_{OUT}$  doesn't get charged during hot-plug, a larger value such as  $1~\mu F$  could be used.

#### 10.2.3.9 Adding C<sub>FNHS</sub>

When the ENHS pin is pulled below its threshold and raised back up the IC will reset. Note that during a hot short the input voltage can easily droop below the UV threshold and cycle the ENHS pin. For the TPS24770 and TPS24771 ICs this will not change the behavior. However, when using the TPS24772 the cycling of the ENHS will result in the IC attempting to restart, which is undesired (this is the main reason why someone would use the TPS24772). To avoid this behavior a capacitor should be added to the ENHS to provide filtering. 33 nF was chosen for this example.

2

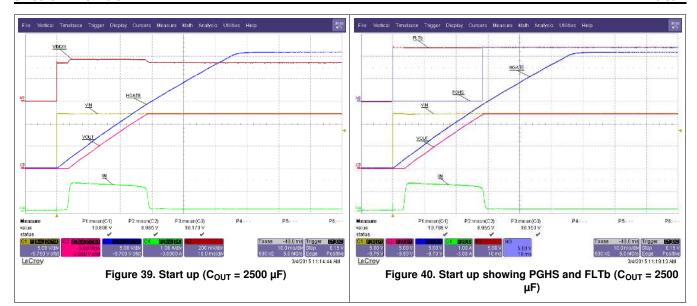

#### 10.2.3.10 Selecting D1 and D2