SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

| • | Step-Down DC-DC Converter                        | C                | B PAC  | CKAGE              |

|---|--------------------------------------------------|------------------|--------|--------------------|

| • | Three Operation-Modes                            |                  | (TOP ) | VIEW)              |

|   | – Heavy Load:                                    |                  |        | <b></b>            |

|   | <ul> <li>Fixed Frequency PWM</li> </ul>          | SOFTSTART [      | $ _1$  | 20 LH              |

|   | <ul> <li>Hysteretic (User Selectable)</li> </ul> | INV              | 2      | 19 🛛 OUT_u         |

|   | – Light Load:                                    | FB [             | 3      | 18 🛛 LL            |

|   | <ul> <li>Skip Mode</li> </ul>                    | Ст[              | 4      | 17 🛛 OUT_d         |

| ٠ | 4.5-V to 25-V Input Voltage Range                | R <sub>T</sub> [ | 5      | 16 OUTGND          |

| • | Adjustable Output Voltage Down to 1.2 V          | GND [            | 6      | 15 🛛 TRIP          |

|   | 95% Efficiency                                   | REF [            | 7      | 14 VCC_SENSE       |

|   | -                                                | COMP             | 8      | 13 V <sub>CC</sub> |

| • | Standby Control                                  | PWM/SKIP         | 9      | 12 VREF5           |

| ٠ | Overcurrent Protection                           | STBY [           | 10     | 11 VREG5V_IN       |

|   | UVI O for Informal 5 V Degulation                |                  |        |                    |

- UVLO for Internal 5-V Regulation

- Low-Standby Current . . . 0.5 mA Typical

# • $T_A = -40^{\circ}C$ to $85^{\circ}C$

#### description

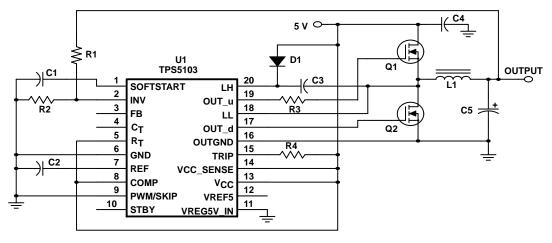

The TPS5103 is a synchronous buck dc/dc controller, designed for notebook PC system power. The controller has three user-selectable operation modes available: hysteretic mode, fixed-frequency PWM control, or SKIP control.

In high-current applications, where fast transient response is advantageous for reducing bulk capacitance, the hysteretic mode is selected by connecting the  $R_T$  pin to VREF5. Selecting the PWM/SKIP modes for less demanding transient applications is ideal for conserving notebook battery life under light load conditions. The device includes high-side and low-side MOSFET drivers capable of driving low  $r_{ds(on)}$  N-channel MOSFETs.

The user-selectable overcurrent protection (OCP) threshold is set by an external TRIP-pin resistor in order to protect the system. The TPS5103 is configured so that a current-sense resistor is not required, improving the operating efficiency.

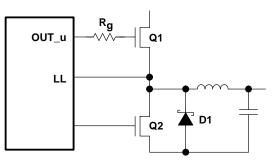

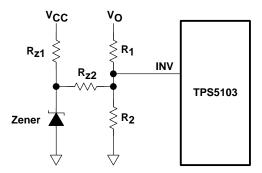

Figure 1. Typical Design

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2001, Texas Instruments Incorporated

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

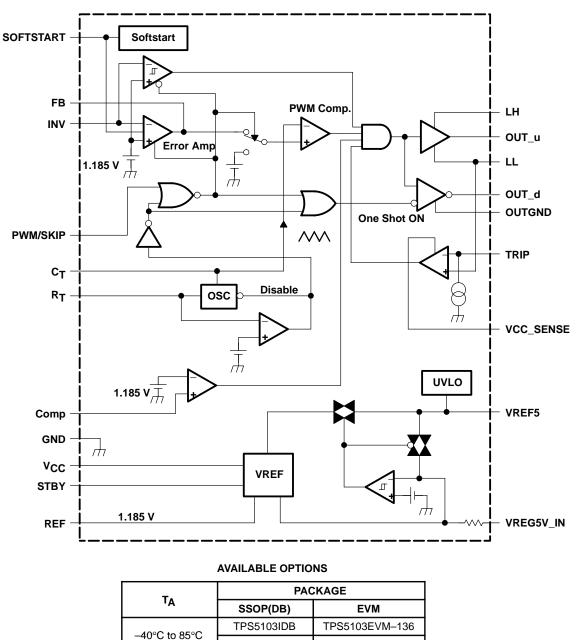

## functional block diagram

TPS5103IDBR

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# **Terminal Functions**

| TERMIN          | AL  | 10  | DESCRIPTION                                                                                                                                                                |

|-----------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | 1/0 | DESCRIPTION                                                                                                                                                                |

| COMP            | 8   | Ι   | Comparator input for voltage monitor                                                                                                                                       |

| CT              | 4   | I/O | External capacitor from $C_T$ to GND for adjusting the triangle oscillator and decreasing the current-limiting voltage                                                     |

| FB              | 3   | 0   | Feedback output of error amp                                                                                                                                               |

| GND             | 6   |     | Control GND                                                                                                                                                                |

| INV             | 2   | I   | Inverting input of both error amp and hysteretic comparator                                                                                                                |

| LH              | 20  | I/O | Bootstrap. Connect a 1 $\mu$ F, low-ESR capacitor from LH to LL.                                                                                                           |

| LL              | 18  | I/O | Bootstrap low. High-side gate driving return and output-current protection. Connect to the junction of the high-side and low-side FETs for a floating drive configuration. |

| OUT_d           | 17  | I/O | Gate-drive output for low-side power switching FETs                                                                                                                        |

| OUTGND          | 16  |     | Ground for FET drivers                                                                                                                                                     |

| OUT_u           | 19  | 0   | Gate-drive output for high-side power switching FETs                                                                                                                       |

| PWM/SKIP        | 9   | I   | PWM/SKIP mode select<br>L:PWM mode<br>H:SKIP mode                                                                                                                          |

| REF             | 7   | 0   | 1.185-V reference voltage output                                                                                                                                           |

| RT              | 5   | I/O | External resistor connection for adjusting the triangle oscillator.                                                                                                        |

| SOFTSTART       | 1   | I   | External capacitor from SOFTSTART to GND for soft-start control                                                                                                            |

| STBY            | 10  | Ι   | Standby control                                                                                                                                                            |

| TRIP            | 15  | Ι   | External resistor connection for output-current control                                                                                                                    |

| V <sub>CC</sub> | 13  | Ι   | Supply-voltage input                                                                                                                                                       |

| VCC_SENSE       | 14  | Ι   | Supply voltage sense for current protection                                                                                                                                |

| VREF5           | 12  | 0   | 5-V internal regulator output                                                                                                                                              |

| VREG5V_IN       | 11  | Ι   | External 5-V input (input voltage range = 4.5 V to 25 V)                                                                                                                   |

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

## detailed description

### REF

The reference voltage is used for the output voltage setting and the voltage protection(COMP). The tolerance is 1.5% typically.

#### VREF5

An internal linear voltage regulator is used for the high-side driver bootstrap voltage. Since the input voltage range is from 4.5 V to 25 V, this voltage offers a fixed voltage for the bootstrap voltage so that the design for the bootstrap is much easier. The tolerance is 6%.

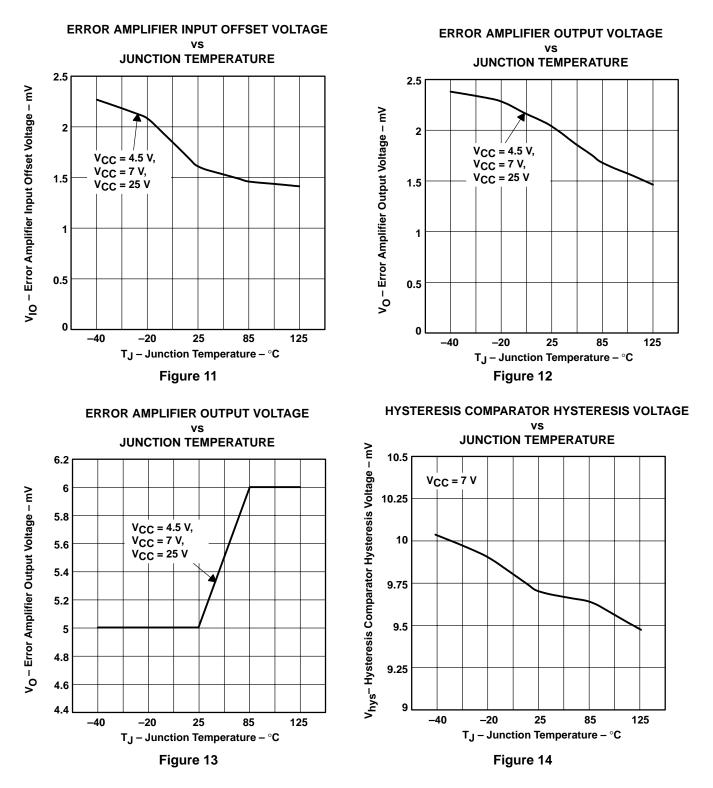

#### hysteretic comparator

The hysteretic comparator is used to regulate the output voltage of the synchronous-buck converter. The hysteresis is set internally and is typically 9.7 mV. The total delay time from the comparator input to the driver output is typically 400 ns for going both high and low.

#### error amplifier

The error amplifier is used to sense the output voltage of the synchronous buck converter. The negative input of the error amplifier is connected to the VREF (1.185 V) with a resistive divider network. The output of the error amplifier is brought out to the FB terminal to be used for loop-gain compensation.

#### low-side driver

The low-side driver is designed to drive low- $r_{ds(on)}$  n-channel MOSFETs. The maximum drive voltage is 5 V from VREF5. The current rating of the driver is typically 1.2 A at sink current, and -1.5 A at source current.

#### high-side driver

The high-side driver is designed to drive low- $r_{ds(on)}$  n-channel MOSFETs. The current rating of the driver is 1.2 A at sink current, and –1.7 A at source current. When configured as a floating driver, the bias voltage to the driver is developed from VREF5, limiting the maximum drive voltage between OUT\_u and LL to 5 V. The maximum voltage that can be applied between LH and OUTGND is 30 V.

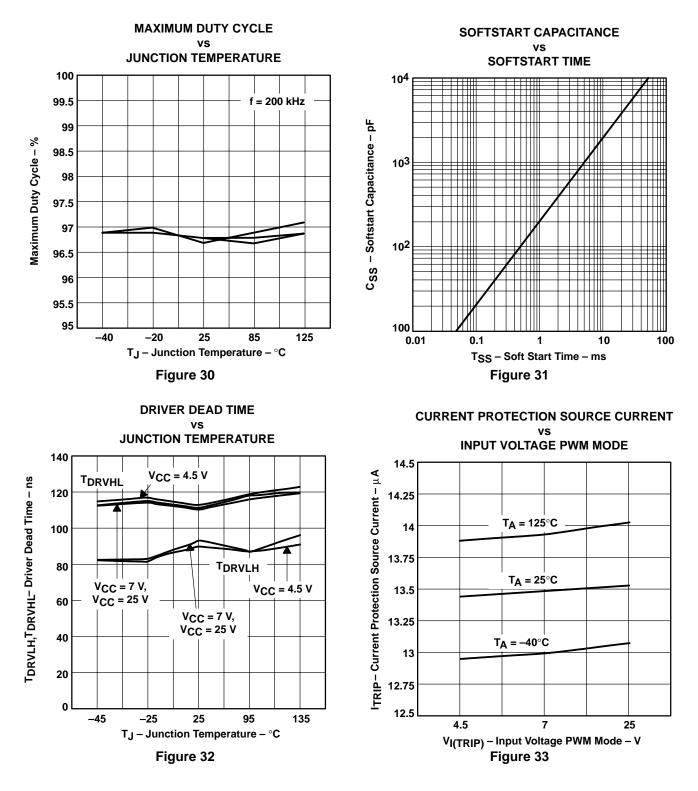

#### driver deadtime control

The deadtime control prevents shoot-through current from flowing through the main power FETs. During switching transitions the deadtime control actively controls the turnon time of the MOSFET drivers. The typical deadtime from the low-side-driver-off to the high-side-driver-on is 90 ns, and 110 ns from high-side-driver-off to low-side-driver-on.

#### COMP

COMP is designed for use with a regulation-output monitor. COMP also functions as an internal comparator used for any voltage protection such as the input under voltage protection. If the input voltage is lower than the setpoint, the comparator turns off and prevents external parts from being damaged. The investing terminal of the comparator is internally connected to REF (1.185 V).

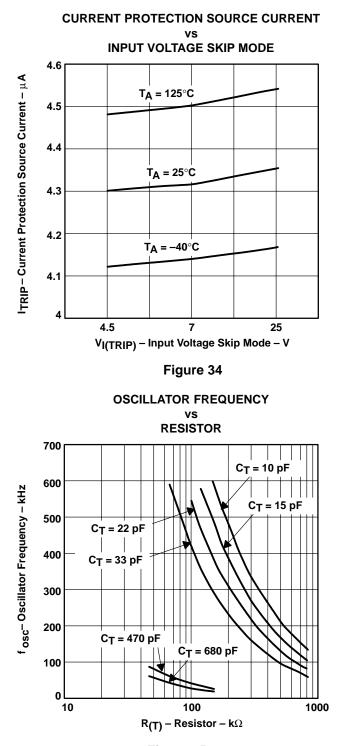

#### current protection

Current protection is achieved by sensing the high-side power MOSFET drain-to-source voltage drop during on-time through VCC\_SENSE and LL terminals. An external resistor between VREG5V\_IN and TRIP, with the an internal current source connected to the current comparator negative input, adjusts the current limit. The typical internal current source value is 15  $\mu$ A in PWM mode, and 5  $\mu$ A in SKIP mode. When the voltage on the positive terminal is lower than the negative terminal, the current comparator turns on the trigger, and then activates the oscillator. This oscillator repeatedly resets the trigger until the overcurrent condition is removed. The capacitor on the C<sub>T</sub> terminal can be open or added to adjust the reset frequency.

## detailed description (continued)

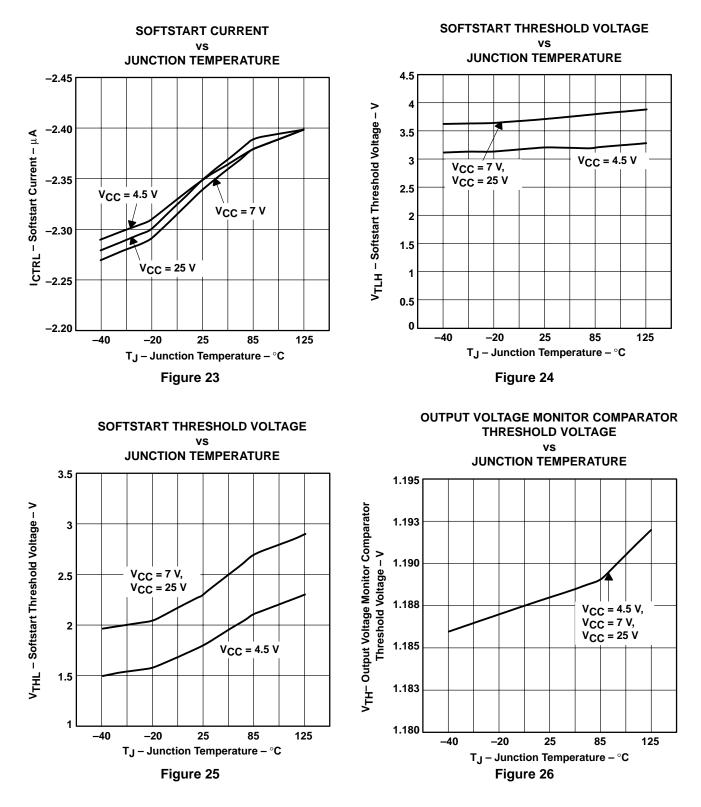

#### softstart

SOFTSTART sets the sequencing of the output for any possibility. The capacitor value for a start-up time can be calculated by the following equation:

$C = 2 \times T (\mu F)$

Where C is the external capacitor value, and T is the required start-up time in (ms).

#### standby

The controller can be switched into the standby mode by grounding the STBY terminal. When it is in standby mode, the quiescent current is less than 1.0  $\mu$ A.

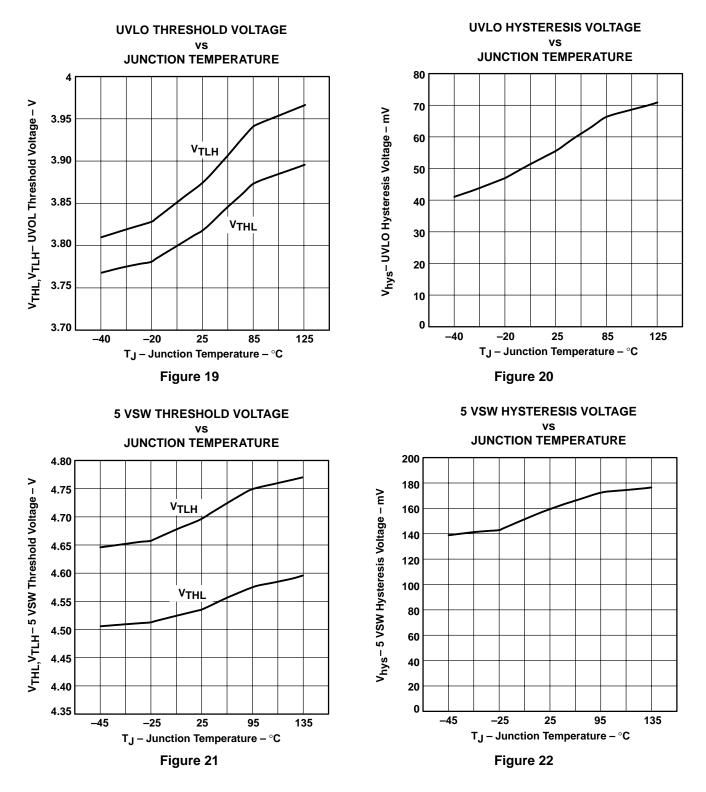

#### UVLO

The under-voltage lockout (ULVO) threshold is approximately 3.8 V. The typical hysteresis is 55 mV.

#### 5-V switch

If the internal 5-V switch senses a 5-V input from REG5V, the internal 5-V linear regulator will be disconnected from the MOSFET drivers. The external 5 V will be used for both the low-side driver and the high-side bootstrap, thus, increasing the efficiency.

#### **PWM/SKIP** switch

The PWM/SKIP switch selects the output operating mode. This controller has three operational modes, PWM, SKIP, and hysteretic. The PWM and SKIP mode control should be used for slower-transient applications.

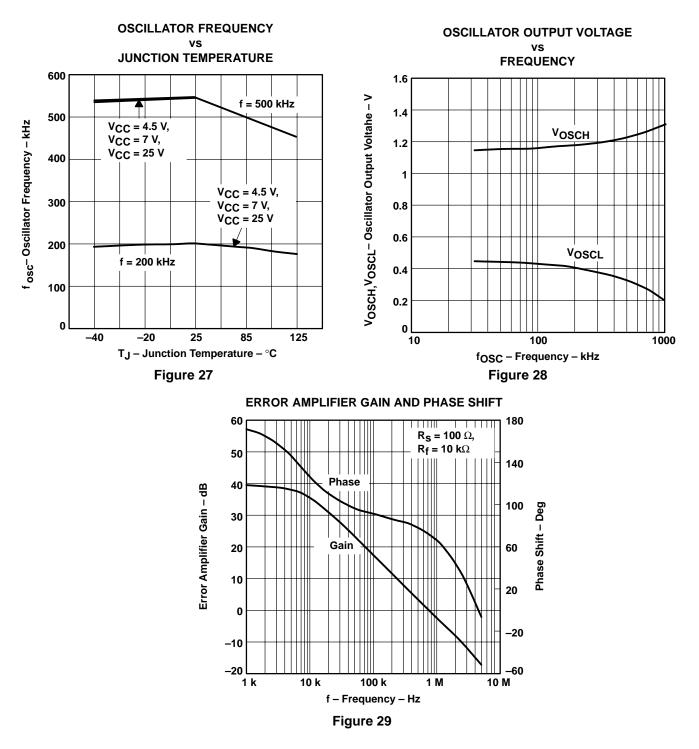

#### oscillator

The oscillator gives a triangle wave by connecting an external resistor to  $R_T$  and an external capacitor to  $C_T$ . The voltage amplitude is 0.43 V ~ 1.17 V. This wave is connected to the noninverting input of the PWM comparator.

| MODE                   | PWM    | HYSTERETIC |

|------------------------|--------|------------|

| Frequency              | Fixed  | Not fixed  |

| Transient response     | Normal | Very fast  |

| Feed back compensation | Need   | Needless   |

## Table 1. Comparison Table Between PWM Mode and Hysteretic Mode

#### SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage, $V_{CC}$ (see Note 1)<br>Input voltage, $V_I$ , INV, $C_T$ , $R_T$ , PWM/SKIP, SOFTSTART, COMP<br>Input voltage, VREG5V_IN<br>Input voltage, STBY<br>Input voltage, TRIP, VCC_SENSE<br>Output current, $I_O$<br>Low-level output voltage, $V_{OL}$<br>High-level output voltage, $V_{OH}$<br>Reference voltage, $V_{ref}$<br>Operating free-air temperature range, $T_A$<br>Operating virtual input in temperature range, $T_A$ | -0.3 V to 7 V<br>-0.3 V to 6 V<br>-0.3 V to 15 V<br>-0.3 V to 27 V<br>3 A<br>-0.3 V to 27 V<br>-0.3 V to 32 V<br>-0.3 V to 3 V<br>-0.3 V to 3 V |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

| Operating virtual junction temperature range, T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to the network ground terminal.

2. See Dissipation Rating Table for free-air temperature range above 25°C.

#### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          |

| DB      | 801 mW                | 6.408mW/°C                  | 416 mW                |

## recommended operating conditions

|                  |                       |                                        | MIN | NOM | MAX | UNIT |

|------------------|-----------------------|----------------------------------------|-----|-----|-----|------|

| VCC              | Supply voltage        |                                        | 4.5 |     | 25  | V    |

| VI               | Input voltage         | INV, CT, RT, COMP, PWM/SKIP, SOFTSTART |     |     | 6   |      |

|                  |                       | VREG5V_IN                              |     |     | 5.5 | V    |

|                  |                       | STBY                                   |     |     | 12  | v    |

|                  |                       | TRIP, VCC_SENSE                        |     |     | 25  |      |

| R <sub>(T)</sub> |                       | Timing register                        |     | 82  |     | kΩ   |

| C <sub>(T)</sub> | Oscillator frequency  | Timing capacitor                       |     | 100 |     | pF   |

| f                | 1                     | Frequency                              |     | 200 |     | kHz  |

| TA               | Operating temperature | range                                  | -40 |     | 85  | °C   |

# electrical characteristics over recommended operating free-air temperature range, $V_{CC}$ = 7 V (unless otherwise noted)

## reference voltage

|                    | PARAMETER         | TEST C                    | ONDITIONS               | MIN   | TYP   | MAX   | UNIT |

|--------------------|-------------------|---------------------------|-------------------------|-------|-------|-------|------|

|                    | Reference voltage | T <sub>A</sub> = 25°C,    | $I_{vref} = 50 \ \mu A$ | 1.167 | 1.185 | 1.203 | V    |

| V <sub>ref</sub>   |                   | I <sub>vref</sub> = 50 μA |                         | 1.155 |       | 1.215 | v    |

| Regin <sup>†</sup> | Line regulation   | $V_{CC}$ = 4.5 V to 25 V, | I = 50 μA               |       | 0.2   | 12    | mV   |

| Regl <sup>†</sup>  | Load regulation   | I = 1 μA to 1 mA          |                         |       | 0.5   | 10    | mV   |

<sup>†</sup>Not a JEDEC symbol.

#### oscillator

|                  | PARAMETER                              | TEST CONDITIONS                                 | MIN | TYP  | MAX | UNIT |

|------------------|----------------------------------------|-------------------------------------------------|-----|------|-----|------|

| f                | Frequency                              | PWM mode                                        |     |      | 500 | kHz  |

| R <sub>(T)</sub> | Timing resistor                        |                                                 | 47  |      |     | kΩ   |

| fdv†             |                                        | $V_{CC}$ = 4.5 V to 25 V                        |     | 0.1% |     |      |

| fdt <sup>†</sup> | Frequency change                       | $T_A = -40^{\circ}C$ to $85^{\circ}C$           |     | 2%   |     |      |

|                  | High-level output voltage <sup>∓</sup> | DC includes internal comparator error           | 1   | 1.1  | 1.2 | V    |

| VOH              |                                        | f = 200 kHz, includes internal comparator error |     | 1.17 |     | V    |

| Vei              |                                        | DC includes internal comparator error           | 0.4 | 0.5  | 0.6 | V    |

| VOL              | Low-level output voltage‡              | f = 200 kHz, includes internal comparator error |     | 0.43 |     | V    |

<sup>†</sup>Not a JEDEC symbol.

<sup>‡</sup> The output voltages of oscillator (f = 200 kHz) are ensured by design.

#### error amp

|                | PARAMETER              | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |

|----------------|------------------------|----------------------|-----|-----|-----|------|

| VIO            | Input offset voltage   | $T_A = 25^{\circ}C$  |     | 2   | 10  | mV   |

| Av†            | Open-loop voltage gain |                      | 50  |     |     | dB   |

| GB†            | Unity-gain bandwidth   |                      |     | 0.8 |     | MHz  |

| IO             | Output sink current    | $V_{O} = 0.4 V$      | 30  | 45  |     | μA   |

| ۱ <sub>S</sub> | Output source current  | V <sub>O</sub> = 1 V |     | 300 |     | μΑ   |

<sup>†</sup>Not a JEDEC symbol.

## hysteresis comparator§

|                  | PARAMETER                           | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------|-------------------------------------------|-----|-----|-----|------|

| V <sub>hys</sub> | Hysteresis window                   | Hysteretic mode                           | 6   | 9.7 | 13  | mV   |

| Vp-VS            | Offset voltage                      |                                           |     | 2   |     | mV   |

| Ι                | Bias current                        |                                           |     | 10  |     | pА   |

| <sup>t</sup> PHL | Propagation delay from INV to OUT_U | TTL input signal                          |     | 230 |     | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high | 10-mV overdrive on hysteresis band signal |     | 400 |     | ns   |

§ The numbers in the table include the driver delay. All numbers are ensured by design.

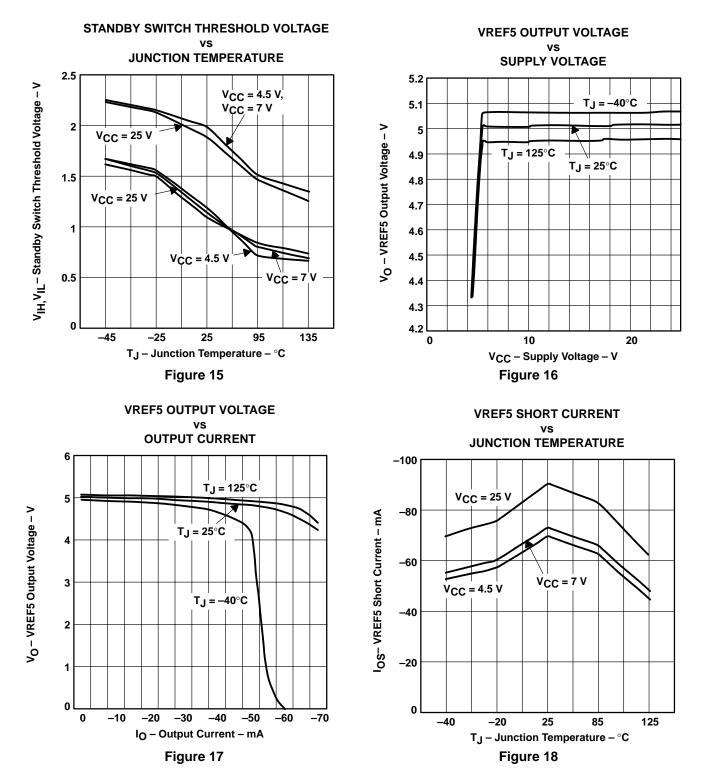

#### control

|      | PARAMETER                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------|--------------------------|-----------------|-----|-----|-----|------|

| VIHA | High-level input voltage | STBY            | 2.5 |     |     | V    |

|      |                          | PWM/SKIP        | 2   |     |     | v    |

| VILA | Low-level input voltage  | STBY            |     |     | 0.5 | V    |

|      |                          | PWM/SKIP        |     |     | 0.5 | v    |

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# electrical characteristics over recommended operating free-air temperature range, $V_{CC} = 7 V$ (unless otherwise noted) (continued)

#### 5-V regulator

|                    | PARAMETER                    | TEST CONDITIONS                                                     | MIN | TYP | MAX | UNIT |

|--------------------|------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| Vo                 | Output voltage               | I = 10 mA                                                           | 4.7 |     | 5.3 | V    |

| Regin <sup>†</sup> | Line regulation              | $V_{CC} = 5.5 \text{ V to } 25 \text{ V}, \qquad I = 10 \text{ mA}$ |     |     | 20  | mV   |

| Regl <sup>†</sup>  | Load regulation              | $I = 1 \text{ mA to } 10 \text{ mA}, \qquad V_{CC} = 5.5 \text{ V}$ |     |     | 40  | mV   |

| los                | Short-circuit output current | V <sub>ref</sub> = 0 V                                              |     | 70  |     | mA   |

<sup>†</sup>Not a JEDEC symbol.

#### 5-V switch

|                  | PARAMETER            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------|----------------------|-----------------|-----|-----|-----|------|

| VIT(high)        | h) Threshold voltage |                 | 4.2 |     | 4.9 | V    |

| VIT(low)         | Threshold voltage    |                 | 4.1 |     | 4.8 | v    |

| V <sub>hys</sub> | Hysteresis           |                 | 50  | 150 | 250 | mV   |

#### UVLO

|                  | PARAMETER         | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|------------------|-------------------|-----------------|-----|---------|------|

| VIT(high)        | Throphold voltage |                 | 3.6 | 4.2     | V    |

| VIT(low)         | Threshold voltage |                 | 3.5 | 4.1     | v    |

| V <sub>hys</sub> | Hysteresis        |                 | 10  | 150     | mV   |

#### output

|                | PARAMETER               | TEST CONDITIONS                                | MIN | TYP  | MAX | UNIT |

|----------------|-------------------------|------------------------------------------------|-----|------|-----|------|

| IO             | OUT_u sink current      | $V_{O} = 3 V$                                  | 0.5 | 1.2  |     | А    |

| IS             | OUT_u source current    | $V_{O} = 2 V$                                  | -1  | -1.7 |     | А    |

| IO             | OUT_d sink current      | $V_{O} = 3 V$                                  | 0.5 | 1.2  |     | А    |

| IS             | OUT_d source current    | $V_{O} = 2 V$                                  | -1  | -1.5 |     | А    |

|                |                         | PWM mode, $V(TRIP) = 7 V$                      | 10  | 15   | 20  | A    |

| I              | I TRIP terminal current | SKIP mode, V(TRIP) = 7 V                       | 3   | 5    | 7   | μA   |

|                |                         | High-side driver is GND referenced.            |     |      |     |      |

|                |                         | Input: $INV = 0 - 3V$                          |     |      |     |      |

| tr             | Rise time               | $t_r/t_f = 10 \text{ ns},$ Frequency = 200 kHz |     |      |     | ns   |

|                |                         | C <sub>L</sub> = 2200 pF                       |     | 28   |     |      |

|                |                         | C <sub>L</sub> = 3300 pF                       |     | 39   |     |      |

|                |                         | High-side driver is GND referenced.            |     |      |     |      |

|                |                         | Input: $INV = 0 - 3 V$                         |     |      |     |      |

| t <sub>f</sub> | Fall time               | $t_r/t_f = 10 \text{ ns},$ Frequency = 200 kHz |     |      |     | ns   |

|                |                         | C <sub>L</sub> = 2200 pF                       |     | 30   |     |      |

|                |                         | C <sub>L</sub> = 3300 pF                       |     | 38   |     |      |

# electrical characteristics over recommended operating free-air temperature range, $V_{CC}$ = 7 V (unless otherwise noted) (continued)

#### softstart

|           | PARAMETER                     | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------|-------------------------------|-----------------|-----|-----|-----|------|

| I(CTRL)   | Softstart current             |                 | 1.9 | 2.5 | 3   | μA   |

| VIT(high) |                               |                 |     | 3.9 |     | V    |

| VIT(low)  | Threshold voltage (SKIP mode) |                 |     | 2.6 |     | v    |

#### output voltage monitor

|     | PARAMETER         | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|-----|-------------------|-----------------|------|------|------|------|

| VIT | Threshold voltage |                 | 1.08 | 1.18 | 1.28 | V    |

#### driver deadtime section

|          | PARAMETER             | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------|-----------------------|-----------------|-----|-----|-----|------|

| T(DRVLH) | Low side to high side |                 |     | 90  |     | ns   |

| T(DRVHL) | High side to low side |                 |     | 110 |     | ns   |

#### whole device

|                    | PARAMETER        | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

|--------------------|------------------|-----------------|-----|------|-----|------|

| ICC                | Supply current   |                 |     | 0.5  | 1.2 | mA   |

| I <sub>O(sd)</sub> | Shutdown current | STBY = 0 V      |     | 0.01 | 10  | μΑ   |

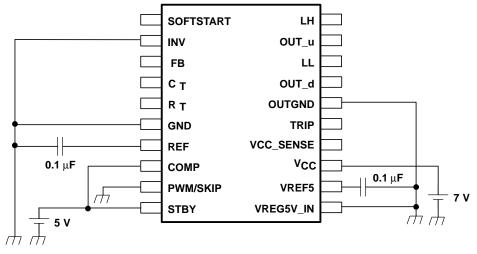

Figure 2. Test Circuit

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

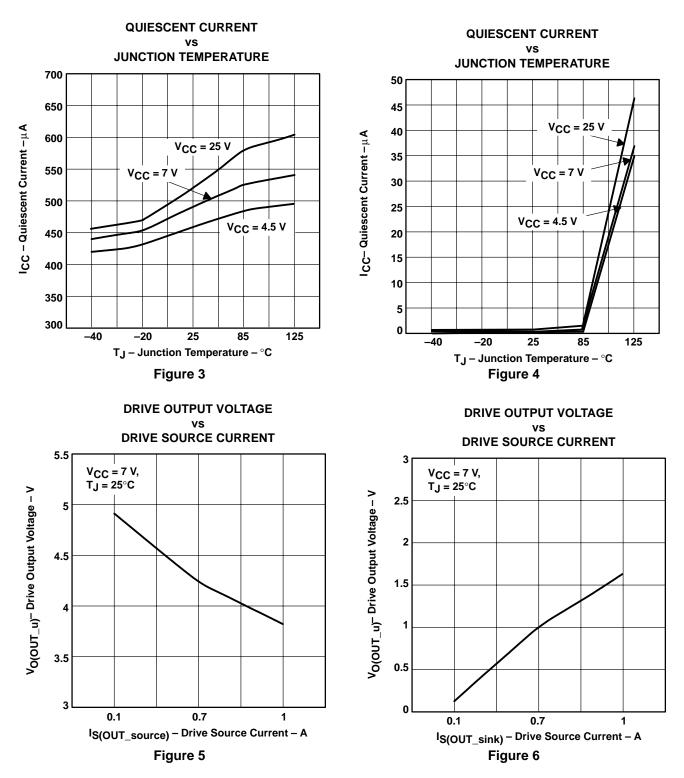

#### DRIVE OUTPUT VOLTAGE DRIVE OUTPUT VOLTAGE vs vs **DRIVE SOURCE CURRENT DRIVE SOURCE CURRENT** 4.5 6 TJ = 25°C T\_J = 25°C 4 V<sub>O</sub>(OUT\_d)<sup>–</sup> Drive Output Voltage – V V<sub>O</sub>(OUT\_d)<sup>–</sup> Drive Output Voltage – V 5 3.5 3 4 2.5 3 2 1.5 2 1 1 0.5 0 0 0.1 0.7 1 0.1 0.7 1 IS(OUT\_sink) - Drive Source Current - A IS(OUT\_source) - Drive Source Current - A Figure 7 Figure 8 **OSCILLATOR OUTPUT VOLTAGE OSCILLATOR OUTPUT VOLTAGE** vs vs JUNCTION TEMPERATURE JUNCTION TEMPERATURE 1.125 500 V<sub>O(osch</sub>)- Oscillator Output Voltage - V V<sub>O</sub>(osch)- Oscillator Output Voltage - V 1.115 495 1.105 490 $V_{CC} = 4.5 V,$ $V_{CC} = 7 V,$ $V_{CC} = 25 V$ 1.095 $V_{CC} = 4.5 V,$ $V_{CC} = 7 V$ , $V_{CC} = 25 V$ 485 1.085 480 1.075 -40 -20 25 85 125 -40 -20 25 85 125 T<sub>J</sub> – Junction Temperature – °C T<sub>J</sub> – Junction Temperature – °C Figure 9 Figure 10

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

**TYPICAL CHARACTERISTICS**

## Figure 35

# **APPLICATION INFORMATION**

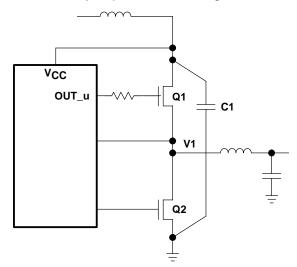

## overshoot of output rectangle wave

The drivers in the TPS5103 controller are fast and can produce high transients on V<sub>CC</sub> or the junction of Q1 and Q2 (shown below). Care must be taken to insure that these transients do not exceed the absolute maximum rating for the device or associated external component. A low-ESR capacitor connected directly from Q1 drain to Q2 source can greatly reduce transient pulses on V<sub>CC</sub>. Also, Q1 turnon speed can be reduced by adding a resistor (5 – 15  $\Omega$ ) in series with OUT\_u. Poor layout of the switching node (V1 in Figure 36) can result in the requirement for additional snubber circuitry required from V1 to ground.

Figure 36. Output Rectangle Wave

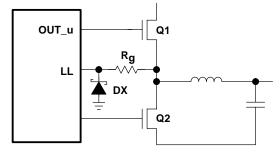

The high-current Schottky diode (D1) can be removed provided an alternate way of preventing negative voltages on LL ( $\geq 0.5$  V) is used (refer to Figure 38).

Figure 37. High-Current Schottky Diode

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# **APPLICATION INFORMATION**

Resistor (R<sub>g</sub>) is moved from the gate of the top FET and placed in series with LL. This allows for a smaller Schottky diode (DX) to be used.

Figure 38. High-Current Schottky Diode Removed

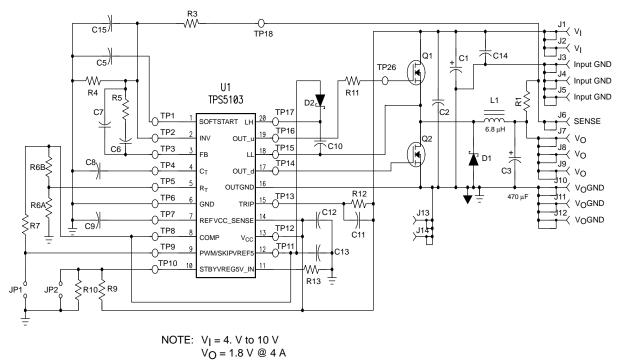

## application for general power

The design shown in this data sheet is a reference design for a general power supply application. An evaluation module (EVM), TPS5103EVM-136 (SLVP136), is available for customer testing and evaluation. The intent is to allow a customer to fully evaluate the given design using the plug-in EVM supply shown here. For subsequent customer board revisions, the EVM design can be copied onto the users PCB to shorten design cycle time, component count, and board cost.

To help the customers design the power supply using the TPS5103, some key design procedures are shown in Figure 39.

# **APPLICATION INFORMATION**

### output voltage setpoint calculation

The output voltage is set by the reference voltage and the voltage divider. In the TPS5102, the reference voltage is 1.185 V, and the divider is composed of two resistors in the EVM design that are R4 and R5, or R14 and R15. The equation for the setpoint is shown below.

$$R2 = \frac{R1 \times V_{ref}}{V_{O} - V_{ref}}$$

Where R1 (> 10 k $\Omega$ ) is the top resistor R2 is the bottom resistor (k $\Omega$ ), V<sub>O</sub> is the required output voltage, and V<sub>ref</sub> is the reference voltage (1.185 V in TPS5103).

Example: R1 = 1 k $\Omega$ ; V<sub>ref</sub> = 1.185 V; V<sub>O</sub> = 1.8 V, then R2 = 1.9 k $\Omega$ .

Some of the most popular output voltage setpoints are calculated in Table 2.

Table 2. Output Voltage Setpoints

| ٧ <sub>0</sub>  | 1.3 V | 1.5 V | 1.8 V | 2.5 V | 3.3 V | 5.0 V |

|-----------------|-------|-------|-------|-------|-------|-------|

| R1 (kΩ)         | 10    | 10    | 10    | 10    | 10    | 10    |

| <b>R2 (k</b> Ω) | 100   | 37    | 19    | 9     | 5.6   | 3.1   |

If higher precision resistor is used, the output voltage setpoint can be more accurate.

In some applications, the output voltage is required to be lower than the reference voltage. With a few extra components, this lower voltage can be easily achieved. Figure 40 shows the method for accomplishing this.

Figure 40. Application With Extra Components for Lower Output Voltage

In the schematic,  $R_{z1}$ ,  $R_{z2}$ , and the Zener are the extra components.  $R_{z1}$  is used to give the Zener enough current to build up the Zener voltage. The Zener voltage is added to INV through  $R_{z2}$ . Therefore, the voltage on INV is still equal to the IC internal voltage (1.185 V), even if the output voltage is regulated at a lower setpoint. The equation for setting up the output voltage is shown below:

$$\mathsf{R}_{\mathsf{Z2}} = \frac{\left(\mathsf{V}_{(\mathsf{Z})}^{-}\mathsf{V}_{\mathsf{ref}}\right)}{\frac{\left(\mathsf{V}_{\mathsf{ref}}^{-}\mathsf{V}_{\mathsf{O}}\right)}{\mathsf{R1}} + \frac{\mathsf{V}_{\mathsf{ref}}}{\mathsf{R2}}}$$

Where  $R_{z2}$  is the adjusting resistor for low-output voltage,  $V_{(z)}$  is the Zener voltage,  $V_{ref}$  is the internal reference voltage, R1 is the top resistor of the voltage sensing network, R2 is the bottom resistor of the sensing network, and  $V_{\Omega}$  is the required output voltage setpoint.

Example: Assuming the required output voltage setpoint is  $V_0 = 0.8 \text{ V}$ ,  $V_{(z)} = 5 \text{ V}$ ,  $R1 = 1 \text{ k}\Omega$ ;  $R2 = 1 \text{ k}\Omega$ , then the  $R_{z2} = 2.43 \text{ k}\Omega$ .

# **APPLICATION INFORMATION**

# switching frequency

With hysteretic control, the switching frequency is a function of the following:

- input voltage

- output voltage

- hysteresis window

- delay of the hysteresis comparator and the driver

- output inductance

- resistance in the output inductor

- output capacitance

- ESR and ESL in the output capacitor

- output current

- turnon resistance of the high-side and the low-side MOSFET

This is a very complex equation if everything is included. To make it more useful to the designers, a simplified equation only considers the most influential factors. The tolerance of this equation is about 30%.

$$fs = \frac{V_{O} \times (V_{I} - V_{O}) \times (ESR - (10 \times 10^{-7} + Td)/C_{O})}{V_{I} \times (V_{I} \times ESR \times (10 \times 10^{-7} + Td) + 0.0097 \times L_{(O)} - ESL \times V_{I})}$$

Where fs is the switching frequency (Hz),  $V_O$  is the output voltage,  $V_I$  is the input voltage,  $C_O$  is the output capacitance, ESR is the equivalent series resistance in the output capacitor ( $\Omega$ ), ESL is the equivalent series inductance in the output capacitor (H),  $L_{(O)}$  is the output inductance (H), and Td is the output feedback RC filter time constant (s).

For example:  $V_I = 5 V$ ,  $V_O = 1.8 V$ ,  $C_O = 680 \mu$ F; ESR = 40 m $\Omega$ ; ESL = 3 nH;  $L_{(O)} = 6 \mu$ H; Td = 0.5  $\mu$ s.

Then, the frequency (fs) = 122 kHz.

# output inductor ripple current

The output inductor current ripple can affect not only the efficiency and the inductor saturation, but also the output voltage capacitor selection. The equation is exhibited as below:

$$I_{\text{(ripple)}} = \frac{V_{I} - V_{O} - I_{O}(r_{ds(on)} + RL)}{L_{O}} \times D \times Ts$$

Where  $I_{(ripple)}$  is the peak-to-peak ripple current (A) through inductor;  $V_I$  is the input voltage,  $V_O$  is the output voltage,  $I_O$  is the output current,  $r_{ds(on)}$  is the on-time resistance of MOSFET ( $\Omega$ ), D is the duty cycle, and Ts is the switching cycle (S). From the equation, it can be seen that the current ripple can be adjusted by changing the output inductor value.

Example:  $V_I = 5 V$ ,  $V_O = 1.8 V$ ,  $I_O = 5 A$ ,  $r_{ds(on)} = 10 m\Omega$ ,  $RL = 5 m\Omega$ , D = 0.36,  $Ts = 10 \mu s$ ,  $L_{(O)} = 6 \mu H$

Then, the  $I_{(ripple)} = 2 A$ .

# output capacitor RMS current

Assuming the inductor ripple current totally goes through the output capacitor to the ground, the RMS current in the output capacitor can be calculated as:

$$I_{O(rms)} = \frac{\Delta I}{\sqrt{12}}$$

## **APPLICATION INFORMATION**

#### output capacitor RMS current

Where  $I_{O(rms)}$  is the maximum RMS current in the output capacitor (A), and  $\Delta I$  is the peak-to-peak inductor ripple current (A).

Example:  $\Delta I = 2 \text{ A}$ , so  $I_{O(\text{rms})} = 0.58 \text{ A}$

#### input capacitor RMS current

Assuming the input ripple current totally goes into the input capacitor to the power ground, the RMS current in the input capacitor can be calculated as:

$$I_{\text{I(rms)}} = \sqrt{I_0^2 \times D \times (1 - D) + \frac{1}{12} \times D \times \text{Iripple}^2}$$

Where I<sub>I(rms)</sub> is the input RMS current in the input capacitor (A), I<sub>O</sub> is the output current (A), and D is the duty cycle. From the equation, it can be seen that the highest input RMS current usually occurs at the lowest input voltage, so it is the worst case design for the input capacitor ripple current.

Example:  $I_0 = 5 A$ ; D = 0.36

Then, I<sub>I(rms)</sub>= 3.36 A

#### softstart

The softstart timing can be adjusted by selecting the soft-start capacitor value. The equation is shown below.

$C_{(soft)} = 2 \times T_{(soft)}$

Where  $C_{(soft)}$  is the softstart capacitance ( $\mu$ F),  $T_{(soft)}$  is the start-up time on the softstart terminal (s).

Example:  $T_{(soft)} = 5 \text{ ms}$ , so,  $C_{(soft)} = 0.01 \mu F$ .

#### current protection

The current protection in the TPS5103 is set using an internal current source and an external resistor to set up the current limit. The sensed, high-side MOSFET drain-to-source voltage drop is compared to the set point, if the voltage drop exceeds the limit, the internal oscillator is activated, and continuously resets the current limit until the over-current condition is removed. The equation below should be used for calculating the external resistor value for current protection:

PWM or HYS mode

$$Rcl = \frac{r_{ds(on)} \times (l_{(trip)} + lind(p-p)/2)}{0.000015}$$

SKIP mode $Rcl = \frac{r_{ds(on)} \times l_{(trip)} + lind(p-p)/2}{0.000005}$

Where, Rcl is the external current limit resistor (R10, R11),  $r_{ds(on)}$  is the high side MOSFET on-time resistance,  $I_{(trip)}$  is the required current limit, and lind(p-p) is the peak-to-peak output inductor current.

Example: PWM mode or HYS mode

$$r_{ds(on)} = 10 \text{ m}\Omega$$

,  $I_{(trip)} = 5 \text{ A}$ ,  $Iind(p-p) = 2 \text{ A}$ , so  $RcI = 4 \text{ k}\Omega$

Example: SKIP mode

$r_{ds(on)} = 10 \text{ m}\Omega$ ,  $I_{(trip)} = 2 \text{ A}$ , Iind(p-p) = 1 A, so  $RcI = 5 \text{ k}\Omega$

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# APPLICATION INFORMATION

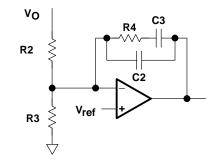

## loop-gain compensation

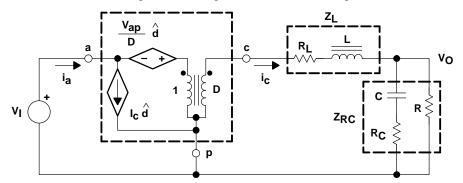

Voltage mode control is used in this controller for the output voltage regulation. To achieve fast, stabilized control, two parts are discussed in this section: the power stage small signal modeling and the compensation circuit design.

For the buck converter, the small-signal modeling circuit is shown in Figure 41.

Figure 41. Small-Signal Modeling Circuit

From this equivalent circuit, several control transfer functions can be derived: input-to-output, output impedance, and control-to-output. Typically, the control-to-output transfer function is used for the feedback control design.

Assuming R<sub>C</sub> and R<sub>L</sub> are much smaller than R, the simplified small signal control-to-output transfer function equation is shown below.

$$\frac{\hat{V}_{od}}{\hat{d}} = \frac{(1 + sCRc)}{1 + s\left[C \times \left(Rc + R_{L}\right) + \frac{L}{R}\right] + s^{2}LC}$$

Where C is the output capacitance, Rc is the equivalent serial resistance (ESR) in the output capacitor, L is the output inductor, RL is the equivalent serial resistance (ESR) in the output inductor, and R is the load resistance.

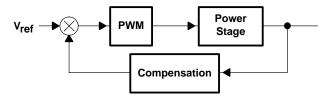

To achieve the fast transient response and the better output voltage regulation, a compensation circuit is added to improve the feedback control. The whole system is shown in Figure 42.

Figure 42. Loop-Gain Compensation

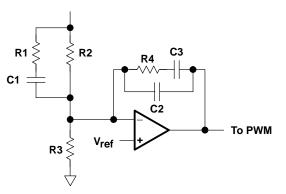

The typical compensation circuit used as an option in the EVM design is a part of the output feedback circuit. The circuitry is shown in Figure 43.

# **APPLICATION INFORMATION**

# loop-gain compensation (continued)

Figure 43. Typical Compensation Circuit

This circuit is composed of one integrator, two poles, and two zeros.

Assuming R1 << R2 and C2 << C3, the equation is:

$$Comp = \frac{(1 + sC3R4) \times (1 + sC2R2)}{sC3R2(1 + sC2R4)(1 + sC1R1)}$$

Therefore,

Pole 1 =

$$\frac{1}{2\pi C1R1}$$

Pole 2 =  $\frac{1}{2\pi C2R4}$

Zero 2 =  $\frac{1}{2\pi C3R4}$  Zero 1 =  $\frac{1}{2\pi C2R2}$

Integrator =  $\frac{1}{2\pi fC3R2}$

A simplified version used in the EVM design is shown in Figure 44.

Assuming C2 << C3, the equation is:

$$Comp = \frac{(1 + sC3R4)}{sC3R2(1 + sC2R4)}$$

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# **APPLICATION INFORMATION**

## loop-gain compensation (continued)

There is one pole, one zero, and one integrator.

Zero =

$$\frac{1}{2\pi C3R4}$$

Pole =  $\frac{1}{2\pi C2R4}$  Integrator =  $\frac{1}{2\pi fC3R2}$

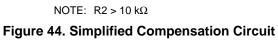

The loop-gain concept is used to design a stable and fast feedback control. The loop-gain equation is derived by the control-to-output transfer function times the compensation. The equation is shown below.

Loop - gain = Vod X Comp

By using a bode plot, the amplitude and the phase of this equation can be drawn with software such as MathCad. In turn, the stability can be easily designed by adjusting the compensation perimeters. The sample bode plot shown in Figure 45 explains the phase margin, gain margin, and the crossover frequency.

The gain is drawn as 20 log (loop-gain), and the phase is in degrees. To explain them clearer, 180 degrees is added to the phase, so that the gain and phase share the same zero.

Where the gain curve touches the zero is the crossover frequency. The higher this frequency is, the faster the transient response is, since the transient recovery time is 1/(crossover frequency). The phase to the zero is the phase margin at the crossover frequency. The phase margin should be at least 60 degrees to cover all the condition changes, such as temperature. The gain margin is the gap between the gain curve and the zero when the phase curve touches the zero. This margin should be at least 20 dB to assure the stability over all conditions.

Figure 45. Sample Bode Plot (not the EVM)

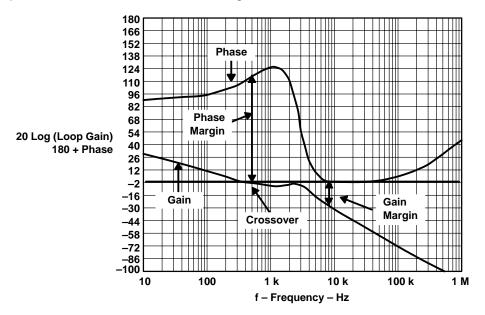

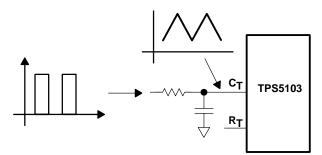

## synchronization

Some applications require switching-clock synchronization. The following two methods are used for synchronization.

• Triangle-wave synchronization

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# **APPLICATION INFORMATION**

# synchronization (continued)

Figure 46. Triangle-Wave Synchronization

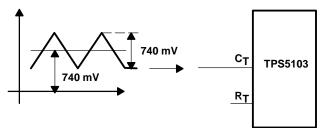

Square-wave synchronization

It can be seen that  $R_T$  and  $C_T$  are removed from the circuit. Therefore, two components are saved. This method is good for the synchronization between two controllers. If the controller needs to be synchronized with a digital circuit such as a DSP, usually the square-type clock signal is used. The configuration shown in Figure 47 is for this type of application.

Figure 47. Square-Wave Synchronization

An external resistor is added into the circuit, but  $R_T$  is still removed.  $C_T$  is kept to be a part of the RC circuit generating the triangle waveform for the controller. Assuming the peak value of the square is known, the resistor and the capacitor can be adjusted to achieve the correct peak-to-peak value and the offset value.

## layout guidelines

Good power supply results will only occur when care is given to proper design and layout. Layout will affect noise pickup and generation, and can cause a good design to perform with less than expected results. With a range of currents from milliamps to tens or even hundreds of amps, good power-supply layout is much more difficult than most general PCB designs. The general design should proceed from the switching node to the output, then back to the driver section and, finally, place the low-level components. Below are several specific points to consider before layout of a TPS5103 design begins.

- All sensitive analog components should be referenced to ANAGND. These include components connected to VREF5, Vref, INV, LH, and COMP.

- Analog ground and drive ground should be isolated as much as possible. Ideally, analog ground will connect to the ground side of the bulk storage capacitors on V<sub>O</sub>, and drive ground will connect to the main ground plane close to the source of the low-side FET.

- Connections from the drivers to the gate of the power FETs should be as short and wide as possible to reduce stray inductance. This becomes more critical if external gate resistors are not being used.

- The bypass capacitor for V<sub>CC</sub> should be placed close to the TPS5103.

# APPLICATION INFORMATION

# layout guidelines (continued)

- When configuring the high-side driver as a floating driver, the connection from LL to the power FETs should be as short and as wide as possible.

- When configuring the high-side driver as a floating driver, the bootstrap capacitor (connected from LH to LL) should be placed close to the TPS5103.

- When configuring the high-side driver as a ground-referenced driver, LL should be connected to DRVGND.

- The bulk-storage capacitors across V<sub>I</sub> should be placed close to the power FETS. High-frequency bypass capacitors should be placed in parallel with the bulk capacitors and connected close to the drain of the high-side FET and to the source of the low-side FET.

- High-frequency bypass capacitors should be placed across the bulk-storage capacitors on V<sub>O</sub>.

- LH and LL should be connected very close to the drain and source, respectively, of the high-side FET. LH and LL should be routed very close to each other to minimize differential-mode noise coupling to these traces. Ceramic-decoupling capacitors should be placed close to where V<sub>CC</sub> connects to V<sub>I</sub>, to reduce high-frequency noise coupling on V<sub>CC</sub>.

- The output-voltage sensing trace should be isolated by either ground trace or V<sub>CC</sub> trace.

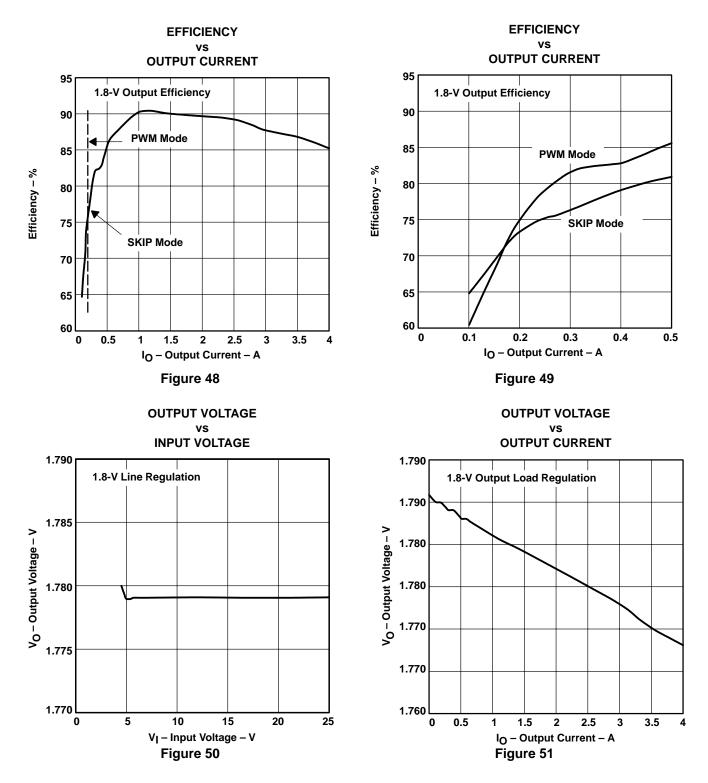

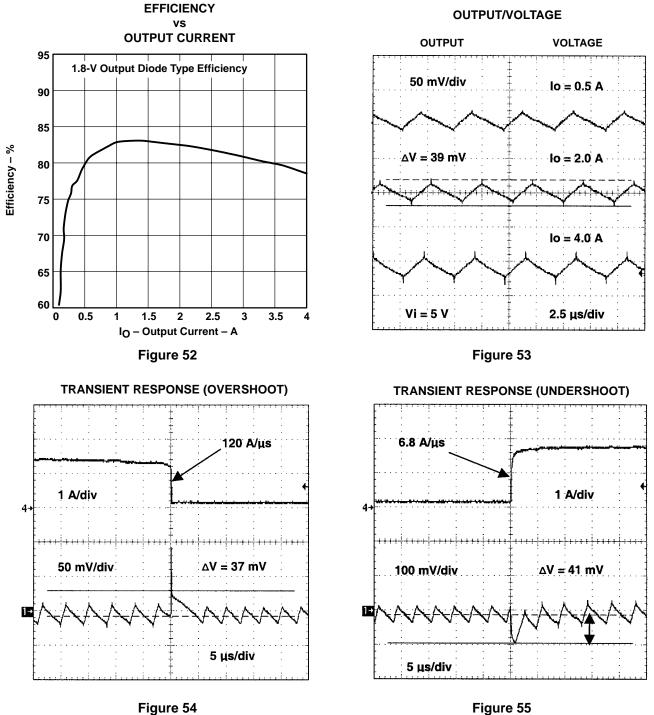

## test results

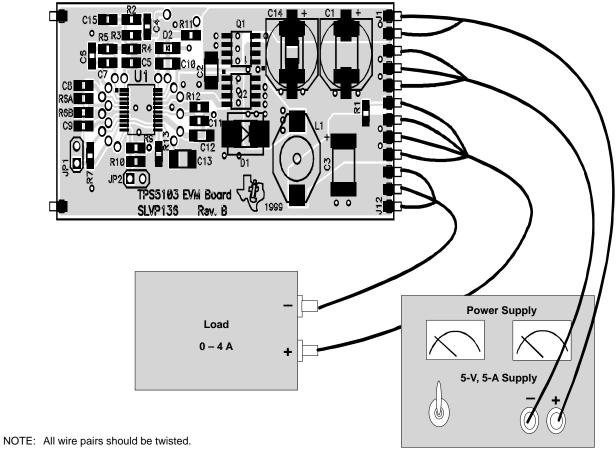

The tests are conducted at  $T_A = 25^{\circ}C$ , the point voltage is 5 V.

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

## **APPLICATION INFORMATION**

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# **APPLICATION INFORMATION**

Figure 55

# **APPLICATION INFORMATION**

#### Table 3. Bill of Materials (see Note 3)

| REF                  | PN              | DESCRIPTION                                                  | MFG           | SIZE                      |

|----------------------|-----------------|--------------------------------------------------------------|---------------|---------------------------|

| C1opt                | 10TPB220M       | Capacitor, POSCAP, 220 μF, 10 V                              | Sanyo         | 7,3 x 4,3 mm              |

| C1                   | RV-35V221MH10-R | Capacitor, electrolytic, 220 μF, 35 V                        | ELNA          | 10 x 10 mm                |

| C2                   | GMK325F106ZH    | Capacitor, ceramic, 10 μF, 35 V                              | Taiyo Yuden   | 1210                      |

| C3                   | 4TPB470M        | Capacitor, POSCAP, 470 μF, 4 V                               | Sanyo         | 7,3 x 4,3 mm              |

| C4†                  | std             | Open, capacitor, ceramic, 2.2 μF, 16 V                       |               | 805                       |

| C5                   | std             | Capacitor, ceramic, 1 μF, 16 V                               |               | 805                       |

| C6                   | std             | Capacitor, ceramic, 0.01 μF, 16 V                            |               | 805                       |

| C7                   | std             | Capacitor, ceramic, 220 pF, 16 V                             |               | 805                       |

| C8                   | std             | Capacitor, ceramic, 100 pF, 16 V                             |               | 805                       |

| C9                   | std             | Capacitor, ceramic, 1 μF, 16 V                               |               | 805                       |

| C10                  | GMK316F225ZG    | Capacitor, ceramic, 2.2 μF, 35 V                             | Taiyo Yuden   | 1206                      |

| C11 <sup>†</sup>     | std             | Open                                                         |               | 805                       |

| C12                  | GMK316F225ZG    | Capacitor, ceramic, 2.2 μF, 35 V                             | Taiyo Yuden   | 1206                      |

| C13                  | GMK325F106ZH    | Capacitor, ceramic, 10 μF, 35 V                              | Taiyo Yuden   | 1210                      |

| C14                  |                 | Open                                                         |               | 1                         |

| C14 <sup>†</sup> opt |                 | Open                                                         |               | 10 x 10 mm                |

| C15 <sup>†</sup>     | std             | Open, capacitor, ceramic, 1000 pF, 16 V                      |               | 805                       |

| D1                   | MBRS340T3       | Diode, Schottky, 40 V, 3 A                                   | Motorola      | SMC                       |

| D1opt                | MBRS130LT3      | Diode, Schottky, 30 V, 1 A                                   | Motorola      | SMB                       |

| D2                   | SD103-AWDICT-ND | Diode, Schottky, 40 V, 200 mA, 400 mW                        | DigiKey       | 3,5 x 1,5 mm              |

| L1                   | DO3316P-682     | Inductor, 6.8 uH, 4.4 A                                      | Coilcraft     | 0.5 x 0.37 in             |

| J1–J14               | CA26DA-D36W-0FC | Edge connector, surface-mount, 0.040" board, 0.090" standoff | NAS Interplex | 0.040"                    |

| JP1                  | S1132-2-ND      | Header, straight, 2-pin, 0.1 ctrs, 0.3" pins                 | Sullins       | Digi-Key<br>#S1132-2-ND   |

| JP1 Shunt            | 929950-00-ND    | Shunt, jumper, 0.1"                                          | ЗМ            | Digi-Key<br>#929950-00-NE |

| JP2                  | S1132-2-ND      | Header, straight, 2-pin, 0.1 ctrs, 0.3" pins                 | Sullins       | Digi-Key<br>#S1132-2-ND   |

| R1                   | std             | Resistor, 5.1 kΩ, 5 %                                        |               | 805                       |

| R2†                  | std             | Open, resistor, 1 kΩ, 5%                                     |               | 805                       |

| R3                   | std             | Resistor, 910 Ω, 1%                                          |               | 805                       |

| R4                   | std             | Resistor, 1.74 kΩ, 1%                                        |               | 805                       |

| R5                   | std             | Resistor, 5.1 kΩ, 5%                                         |               | 805                       |

| R6A                  | std             | Resistor, 82 kΩ, 5%                                          |               | 805                       |

| R6B†                 | std             | Open, 0 Ω, 5%                                                |               | 805                       |

| R7                   | std             | Resistor, 1 kΩ, 5%                                           |               | 805                       |

| R9                   | std             | Resistor, 1 kΩ, 5%                                           |               | 805                       |

| R10                  | std             | Resistor, 1 kΩ, 5%                                           |               | 805                       |

| R11                  | std             | Resistor, 10 Ω, 5%                                           |               | 805                       |

| R12                  | std             | Resistor, 51 kΩ, 5%                                          |               | 805                       |

| R13 <sup>†</sup>     | std             | Open                                                         |               | 805                       |

| Q1                   | Si4410DY        | Transistor, MOSFET, n-ch, 30-V, 10-A, 13-mΩ                  | Siliconix     | SO-8                      |

| Q2                   | Si4410DY        | Transistor, MOSFET, n-ch, 30-V, 10-A, 13-mΩ                  | Siliconix     | SO-8                      |

| U1                   | TPS5103         | IC, controller                                               | TI            | SSOP-20                   |

<sup>†</sup> Components for optional mode test only.

NOTE 3: This operation mode is PWM mode only.  $V_I = 4.5$  V to 10 V,  $V_O = 1.8$  V, and  $I_O = 4$  A (see Table 8 for other applications.)

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

**APPLICATION INFORMATION**

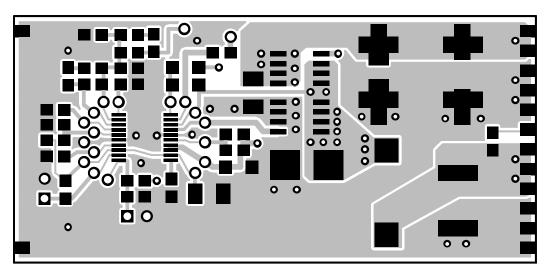

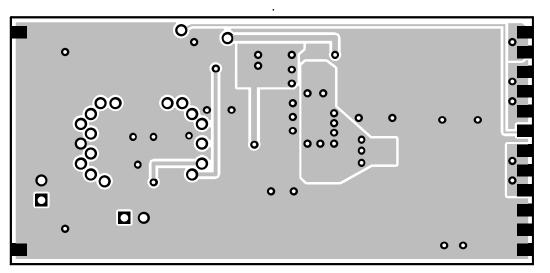

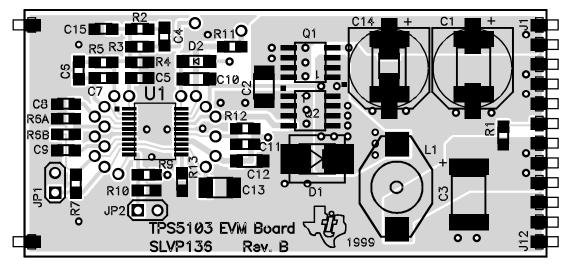

Figure 56. Top Layer

Figure 57. Bottom Layer (Top View)

SLVS240A – SEPTEMBER 1999 – REVISED MAY 2001

## **APPLICATION INFORMATION**

Figure 58. Top Assembly

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

# **APPLICATION INFORMATION**

### **Table 4. Test Specifications**

| PARAMETER                | CONDITIONS                                 | MIN | TYP | MAX | UNITS |

|--------------------------|--------------------------------------------|-----|-----|-----|-------|

| Input voltage range, VI  |                                            | 5   |     | 25  | V     |

| Output voltage range, VO | $V_I = 5 - 25 V$ , $I_O = 0 - 4 A$         | 1.7 | 1.8 | 1.9 | V     |

| Output current range, IO | $V_{I} = 5 - 10 V$                         | 0   |     | 4   | А     |

| Output current limit     | $V_{I} = 5 V$                              | 4.3 |     |     | А     |

| Output ripple            | V <sub>I</sub> = 5 V, I <sub>O</sub> = 4 A |     |     | 50  | mVp–p |

| Operating frequency, f   | I <sub>O</sub> = 4 A                       | 150 |     | 250 | kHz   |

| Efficiency               | VI = 5 V, VO = 1.8 V, IO = 4 A             |     | 90  |     | %     |

#### **Table 5. EVM Operating Specifications**

| SKIP MODE        | HYS MODE                                         |

|------------------|--------------------------------------------------|

| Remove JP1 shunt | Remove R5, C6, and C7                            |

|                  | Remove R6A                                       |

|                  | Add R6B                                          |

|                  | Add C15                                          |

|                  | If it needs the loop compensation, add R2 and C4 |

This EVM is designed to cover as many applications as possible. For more specific applications, the circuit can be simpler. Table 6 gives some recommendations.

#### **Table 6. EVM Application Recommendations**

| 5-V INPUT VOLTAGE                                                                                                   | <3-A OUTPUT CURRENT                                                 | DIODE VERSION                |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------|

| Change C1 to low-profile capacitor Sanyo 10TPB220M (220 $\mu\text{F},$ 10 V) or 6TPB330M (330 $\mu\text{F},$ 6.3 V) | Change Q1 and Q2 to dual-pack MOSFET,<br>IRF7311 to reduce the cost | Remove Q2 to reduce the cost |

| Remove R10                                                                                                          |                                                                     |                              |

### Table 7. Vendor and Source Information

| MATERIAL                                   | SOURCE        | PART NUMBER                                   | DISTRIBUTORS                      |  |  |

|--------------------------------------------|---------------|-----------------------------------------------|-----------------------------------|--|--|

|                                            | In EVM design | Si4410                                        | Local distributor                 |  |  |

| MOSFETS (Q1–Q2)                            | Second source | IRF7811 (International Rectifier)             | Local distributor                 |  |  |

| Input consoitors (C1)                      | In EVM design | RV-35V221MH10-R (ELNA)                        | Bell Microproducts 972-783-4191   |  |  |

| Input capacitors (C1)                      | Second source | 35CV330AX/GX (Sanyo)                          | 870–633–5030                      |  |  |

|                                            |               | UUR1V221MNR1GS (Nichicon)                     | Future Electronics (Local Office) |  |  |

| Main diodes (D1)                           | In EVM design | MBRS340T3 (Motorola)                          | Local distributors                |  |  |

|                                            | Second source | U3FWJ44N (Toshiba)                            | Local distributors                |  |  |

| Inductors (L1)                             | In EVM design | DO3316P-682 (Coilcraft)                       | 972–458–2645                      |  |  |

|                                            | Second source | CTDO3316P-682<br>(Inductor Warehouse)         | 800–533–8295                      |  |  |

| Ceramic capacitors<br>(C2, C14) (C12, C10) | In EVM design | GMK325F106ZH<br>GMK316F225ZG<br>(Taiyo Yuden) | SMEC<br>512–331–1877              |  |  |

|                                            | Taiyo Yuden   |                                               | email: mike@millsales.com         |  |  |

# **APPLICATION INFORMATION**

High-current applications are described in Table 8. The values are recommendations based on actual test circuits. Many variations are possible based on the requirements of the user. Performance of the circuit is dependent upon the layout rather than on the specific components, if the device parameters are not exceeded. The power stage, having the highest current levels and greatest dv/dt rates, should be given the most attention, as both the supply and load can be severely affected by the power levels and edge rates.

| REFERENCE<br>DESIGNATIONS | Operational<br>Conditions                    | FUNCTION                | 8-A OUTPUT                                    | 12-A OUTPUT                                   | 16-A OUTPUT                                            |  |  |

|---------------------------|----------------------------------------------|-------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------------|--|--|

| C1                        |                                              | Input-bulk capacitor    | 2x ELNA<br>RV-35V221MH10-R<br>220 μF, 35 V    | 3x ELNA<br>RV-35V221MH10-R<br>220 μF, 35 V    | 4x ELNA<br>RV-35V221MH10-R<br>220 μF, 35 V             |  |  |

| C2                        |                                              | Input-bypass capacitor  | 2x Taiyo Yuden<br>GMK325F106ZH<br>10 μF, 35 V | 3x Taiyo Yuden<br>GMK325F106ZH<br>10 μF, 35 V | 4x Taiyo Yuden<br>GMK325F106ZH<br>10 μF, 35 V          |  |  |

| C6                        | 0.01 μΩ at<br>V <sub>I</sub> = 4.5 V to 10 V |                         |                                               |                                               |                                                        |  |  |

| L1                        |                                              | Output-filter indicator | Coiltronics UP3B-2R2<br>2.2 µH, 9.2 A         | Coiltronics UP4B-1R5<br>1.5 µH, 13.4 A        | MicorMetals T68-8/90<br>Core w/7T, #16<br>1.0 μH, 25 A |  |  |

| C3                        |                                              | Output-filter capacitor | 2x Sanyo 4TPB470M<br>470 μF, 4 V              | 3x Sanyo 4TPB470M<br>470 μF, 4 V              | 4x Sanyo 4TPB470M<br>470 μF, 4 V                       |  |  |

| Q1                        |                                              | Power switch            | 2x Siliconix Si4410DY<br>30 V, 10 A, 13 mΩ    | 3x Siliconix Si4410DY<br>30 V, 10 A, 13 mΩ    | 4x Siliconix Si4410DY<br>30 V, 10 A, 13 mΩ             |  |  |

| Q2                        |                                              | Power switch            | 2x Siliconix Si4410DY<br>30 V, 10 A, 13 mΩ    | 3x Siliconix Si4410DY<br>30 V, 10 A, 13 mΩ    | 4x Siliconix Si4410DY<br>30 V, 10 A, 13 mΩ             |  |  |

| R3                        | 910 kΩ at<br>V <sub>I</sub> = 4.5 V to 10 V  |                         |                                               |                                               |                                                        |  |  |

| кэ                        | 10 kΩ at<br>V <sub>I</sub> = 10 V to 25 V    |                         |                                               |                                               |                                                        |  |  |

| R4                        | 1.74 kΩ at<br>V <sub>I</sub> = 4.5 V to 10 V |                         |                                               |                                               |                                                        |  |  |

| K4                        | 19 kΩ at<br>V <sub>I</sub> = 10 V to 25 V    |                         |                                               |                                               |                                                        |  |  |

| R5                        | 5.1 kΩ at<br>V <sub>I</sub> = 4.5 V to 25 V  |                         |                                               |                                               |                                                        |  |  |

| R11                       |                                              | Gate-drive resistor     | 7 Ω                                           | 5Ω                                            | 4Ω                                                     |  |  |

| R12                       |                                              | Current-limit resistor  | 10 kΩ                                         | 15 kΩ                                         | 20 kΩ                                                  |  |  |

| Switching<br>frequency    |                                              |                         | 200 kHz                                       | 150 kHz                                       | 100 kHz                                                |  |  |

## **Table 8. High-Current Applications**

SLVS240A - SEPTEMBER 1999 - REVISED MAY 2001

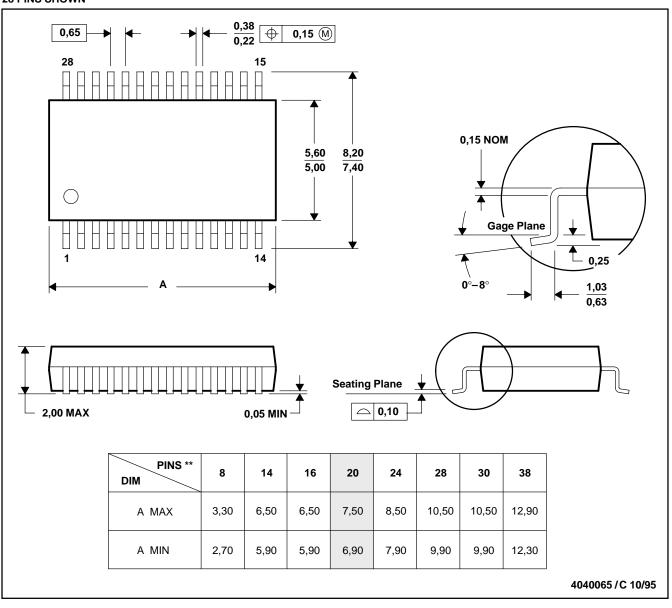

**MECHANICAL DATA**

PLASTIC SMALL-OUTLINE PACKAGE

## DB (R-PDSO-G\*\*) 28 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-150

10-Dec-2020

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TPS5103IDB       | ACTIVE        | SSOP         | DB                 | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | PU5103                  | Samples |

| TPS5103IDBR      | ACTIVE        | SSOP         | DB                 | 20   | 2000           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | PU5103                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

10-Dec-2020

Texas

www.ti.com

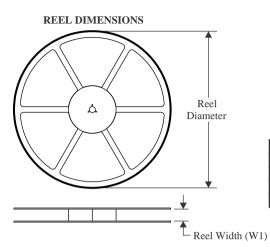

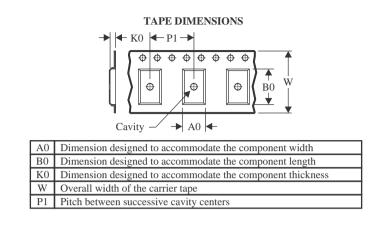

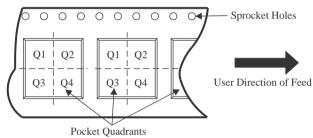

# TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nomir | nal |          |  |

|---------------------------|-----|----------|--|

|                           |     | <u> </u> |  |

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS5103IDBR | SSOP            | DB                 | 20 | 2000 | 330.0                    | 16.4                     | 8.2        | 7.5        | 2.5        | 12.0       | 16.0      | Q1               |

www.ti.com

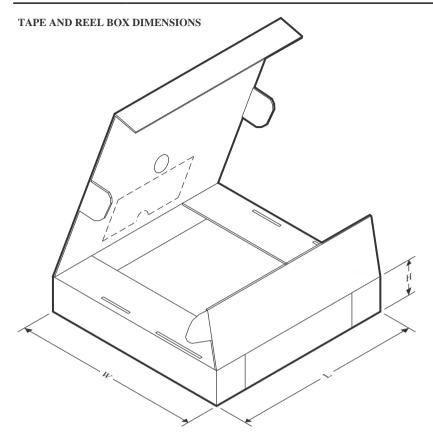

# PACKAGE MATERIALS INFORMATION

3-Jun-2022

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS5103IDBR | SSOP         | DB              | 20   | 2000 | 356.0       | 356.0      | 35.0        |

# TEXAS INSTRUMENTS

www.ti.com

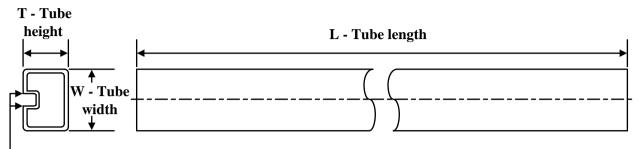

3-Jun-2022

# TUBE

# - B - Alignment groove width

\*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPS5103IDB | DB           | SSOP         | 20   | 70  | 530    | 10.5   | 4000   | 4.1    |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated