#### **Brief Description**

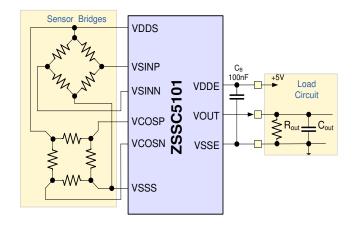

The ZSSC5101 is a CMOS integrated circuit for converting sine and cosine signals obtained from magnetoresistive bridge sensors into a ratiometric analog voltage with a user-programmable range of travel and clamping levels.

The ZSSC5101 accepts sensor bridge arrangements for both rotational as well as linear movement. Depending on the type of sensor bridge, a full-scale travel range of up to 360 mechanical degrees can be obtained.

Programming of the device is performed through the output pin, allowing in-line programming of fully assembled 3-wire sensors. Programming parameters are stored in an EEPROM and can be re-programmed multiple times.

The ZSSC5101 is fully automotive-qualified with an ambient temperature range up to 160°C.

#### **Features**

- Ratiometric analog output

- Up to 4608 analog steps

- Step size as small as 0.022°

- Programming through output pin via one-wire interface

- Offset calibration of the bridge input signals

- Programmable linear transfer characteristic:

- Zero position

- Angular range

- Upper and lower clamping levels

- Rising or falling slope

- Loss of magnet indication with programmable threshold level

- Accepts anisotropic, giant, and tunnel magnetoresistive bridge sensors (AMR, GMR and TMR)

- Programmable 32-bit user ID

- CRC, error detection, and error correction on EEPROM data

- Diagnostics: broken-wire detection

- Automotive-qualified to AEC-Q100, grade 0

#### **Benefits**

- No external trimming components required

- PC-controlled configuration and single-pass calibration via one-wire interface allows programming of fully assembled sensors

- Can be used with low-cost ferrite magnets

- Allows large air gaps between sensors and magnets

- Optimized for automotive environments with extended temperature range and special protection circuitry with excellent electromagnetic compatibility

- · Power supply monitoring

- Sensor monitoring

- Detection of EEPROM memory failure

- · Connection failure management

- High accuracy: ± 0.15° integral nonlinearity (INL) after calibration

#### **Available Support**

- Evaluation Kit

- Application Notes

#### **Physical Characteristics**

- Wide operation temperature: -40 C to +160 C (die)

- Supply voltage: 4.5V to 5.5V

- SSOP-14 package, bare die, or unsawn wafer

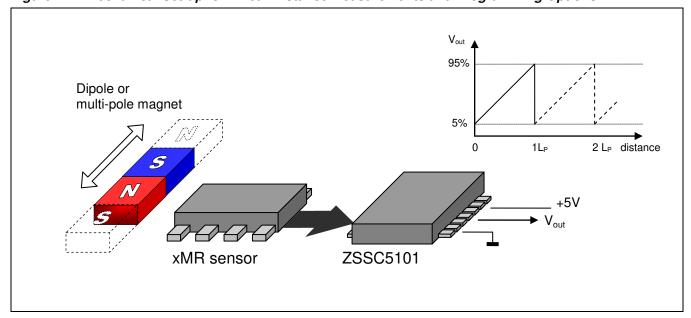

#### ZSSC5101 Typical Application Circuit

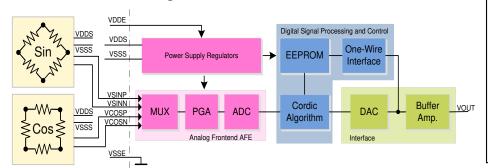

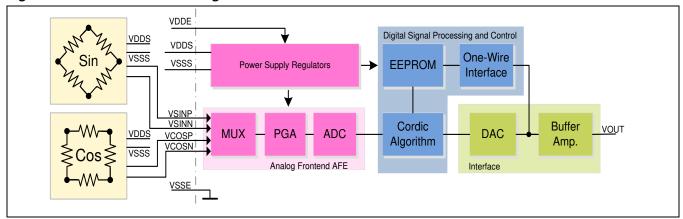

## **ZSSC5101 Block Diagram**

#### **Applications**

- Absolute Rotary Position Sensor

- Steering Wheel Position Sensor

- Pedal Position Sensor

- Throttle Position Sensor

- Float-Level Sensor

- Ride Height Position Sensor

- Non-Contacting Potentiometer

- Rotary Dial

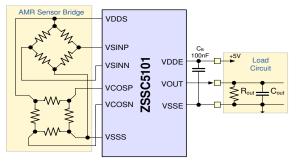

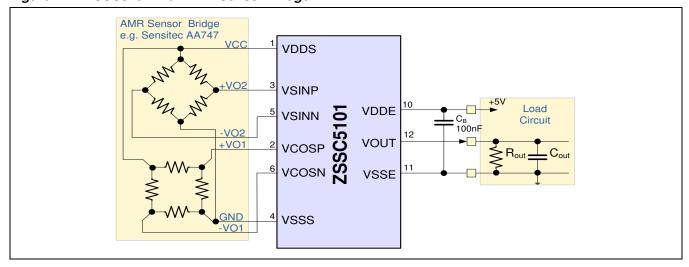

#### **Application Circuit for AMR Sensors**

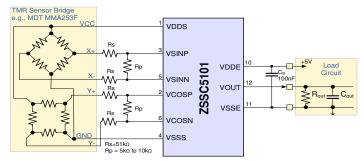

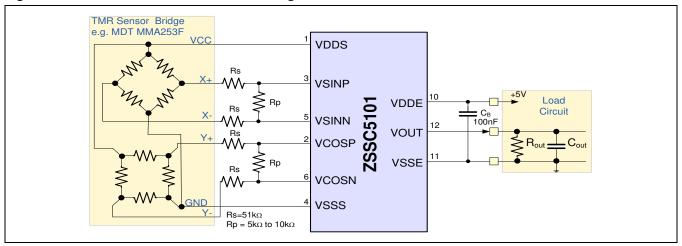

#### **Application Circuit for TMR Sensors**

#### **Ordering Information**

| Sales Code   | Description                                                                                                 | Delivery Package                                      |  |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|--|

| ZSSC5101BE1B | ZSSC5101 Die – Temperature range: -40°C to +160°C                                                           | 8" tested wafer, unsawn, thickness = 390 ±15μm        |  |  |  |  |  |  |  |

| ZSSC5101BE2B | ZSSC5101 Die – Temperature range: -40°C to +160°C                                                           | 8" tested wafer, unsawn, thickness = 725 ±15μm        |  |  |  |  |  |  |  |

| ZSSC5101BE3B | ZSSC5101 Die – Temperature range: -40°C to +160°C                                                           | 8" tested wafer, unsawn, thickness = 250 ±15μm        |  |  |  |  |  |  |  |

| ZSSC5101BE1C | ZSSC5101 Die – Temperature range: -40°C to +160°C                                                           | 8" tested wafer, sawn on frame, thickness = 390 ±15μm |  |  |  |  |  |  |  |

| ZSSC5101BE4R | ZSSC5101 SSOP-14 – Temperature range: -40°C to +150°C                                                       | 13" tape and reel                                     |  |  |  |  |  |  |  |

| ZSSC5101BE4T | ZSSC5101 SSOP-14 – Temperature range: -40°C to +150°C                                                       | Tube                                                  |  |  |  |  |  |  |  |

| ZSSC5101 KIT | Evaluation Kit: USB Communication Board, ZSSC5101 AMR board, adapters. Software is downloaded (see data she |                                                       |  |  |  |  |  |  |  |

## **Contents**

| 1 | IC Cha  | aracteristics                                                       | 5  |

|---|---------|---------------------------------------------------------------------|----|

|   | 1.1. Ak | osolute Maximum Ratings                                             | 5  |

|   | 1.2. O  | perating Conditions                                                 | 5  |

|   | 1.3. El | ectrical Parameters                                                 | 6  |

|   | 1.3.1.  | ZSSC5101 Characteristics                                            | 6  |

|   | 1.3.2.  | Input Stage Characteristics                                         |    |

|   | 1.3.3.  | Digital Calculation Characteristics                                 |    |

|   | 1.3.4.  | Analog Output Stage Characteristics (Digital to VOUT)               | 9  |

|   | 1.3.5.  | Analog Input to Analog Output Characteristics (Full Path)           |    |

|   | 1.3.6.  | Digital Interface Characteristics (CMOS compatible)                 |    |

|   | 1.3.7.  | Supervision Circuits                                                |    |

|   | 1.3.8.  | Power Loss Circuit                                                  |    |

| 2 | Circuit | Description                                                         | 12 |

|   |         | verview                                                             |    |

|   |         | ınctional Description                                               |    |

|   |         | ne-Wire Interface and Command Mode (CM)                             |    |

|   |         | ower-Up/Power-Down Characteristics                                  |    |

|   |         | ower Loss / GND Loss                                                |    |

|   | 2.5.1.  | •                                                                   |    |

|   | 2.5.2.  |                                                                     |    |

|   |         | agnostics Mode (DM)                                                 |    |

| 3 |         | OM                                                                  |    |

|   |         | ser Programmable Parameters in EEPROM                               |    |

|   |         | RC Algorithm                                                        |    |

|   |         | OC Algorithm                                                        |    |

| 4 |         | ation Circuit Examples                                              |    |

|   | -       | rpical Application Circuit for AMR Double Wheatstone Sensor Bridges |    |

|   | -       | pical Application Circuit for TMR Sensor Bridges                    |    |

|   |         | echanical Set-up for Absolute Angle Measurements                    |    |

|   |         | echanical Set-up for Linear Distance Measurements                   |    |

|   |         | put-to-Output Characteristics Calculation Examples                  |    |

| 5 |         | nd Latch-up Protection                                              |    |

|   |         | uman Body Model                                                     |    |

|   |         | achine Model                                                        |    |

|   |         | narged Device Model                                                 |    |

| _ |         | atch-Up                                                             |    |

| b | Pin Co  | onfiguration and Package Dimensions                                 | 23 |

| 6.1. Pa    | ckage Drawing – SSOP-14                                                    | 24 |

|------------|----------------------------------------------------------------------------|----|

| 6.2. Die   | e Dimensions and Pad Coordinates                                           | 25 |

| 7 Layout   | Requirements                                                               | 25 |

| 8 Reliabi  | lity and RoHS Conformity                                                   | 25 |

| 9 Orderir  | ng Information                                                             | 26 |

| 10 Related | d Documents                                                                | 26 |

|            | ry                                                                         |    |

| 12 Docum   | ent Revision History                                                       | 28 |

| List of F  | Figures                                                                    |    |

| Figure 2.1 | ZSSC5101 Block Diagram                                                     | 12 |

| Figure 4.1 | ZSSC5101 with AMR Sensor Bridge                                            | 17 |

| Figure 4.2 | ZSSC5101 with TMR Sensor Bridge                                            | 18 |

| Figure 4.3 | Mechanical Set-up for Rotational Measurements and Programming Options      | 19 |

| Figure 4.4 | Mechanical Set-up for Linear Distance Measurements and Programming Options | 20 |

| Figure 4.5 | Input-to-Output Characteristics with Parameters                            | 21 |

| Figure 6.1 | Package Dimensions – SSOP-14                                               | 24 |

| Figure 6.2 | Pin Map and Pad Position of the ZSSC5101 SSOP-14 Package                   | 25 |

| List of 7  | ables                                                                      |    |

| Table 1.1  | Absolute Maximum Ratings                                                   | 5  |

| Table 1.2  | Operating Conditions                                                       | 5  |

| Table 1.3  | Electrical Characteristics                                                 | 6  |

| Table 1.4  | Input Stage Characteristics                                                | 7  |

| Table 1.5  | Digital Calculation Characteristics                                        | 8  |

| Table 1.6  | Analog Output Stage Characteristics                                        |    |

| Table 1.7  | Full Analog Path Characteristics                                           |    |

| Table 1.8  | Digital Interface Characteristics                                          |    |

| Table 1.9  | Supervision Circuits                                                       |    |

| Table 1.10 | Power Loss Circuit                                                         |    |

| Table 2.1  | Output Modes during Power-Up and Power-Down                                |    |

| Table 2.2  | Power Loss Behavior                                                        |    |

| Table 2.3  | Diagnostics Mode                                                           |    |

| Table 3.1  | EEPROM — User Area                                                         |    |

| Table 6.1  | Pin Configuration                                                          | 23 |

## 1 IC Characteristics

## 1.1. Absolute Maximum Ratings

Table 1.1 Absolute Maximum Ratings

|          | Parameter                                      |                  | Min  | Тур. | Max                   | Unit |

|----------|------------------------------------------------|------------------|------|------|-----------------------|------|

| 1.1.1.1. | Supply voltage at VDDE pin                     | $V_{DDE}$        | -0.3 |      | 5.7                   | V    |

| 1.1.1.2. | Voltage at VDDS pin                            | $V_{DDS}$        | -0.3 |      | V <sub>DDE</sub> +0.3 | V    |

| 1.1.1.3. | Voltage at VSINP, VSINN, VCOSP, and VCOSN pins |                  | -0.3 |      | V <sub>DDS</sub>      | V    |

| 1.1.1.4. | Voltage at VOUT pin                            | V <sub>OUT</sub> | -0.3 |      | V <sub>DDE</sub> +0.3 | V    |

| 1.1.1.5. | Storage temperature                            | Ts               | -60  |      | 160                   | °C   |

## 1.2. Operating Conditions

#### Table 1.2 Operating Conditions

Note: See important notes at the end of the table.

|           | Parameter                                                                                                           | Symbol                   | Min | Тур. | Max  | Unit     |

|-----------|---------------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|------|----------|

| 1.2.1.1.  | Supply voltage for normal operation                                                                                 | $V_{DDE}$                | 4.5 | 5.0  | 5.7  | V        |

| 1.2.1.2.  | Operating ambient temperature range, bare die 1)                                                                    | T <sub>A</sub>           | -40 |      | 160  | °C       |

| 1.2.1.3.  | Extended ambient temperature range, bare die 1), 2)                                                                 | T <sub>A</sub>           | -60 |      | 160  | °C       |

| 1.2.1.4.  | Operating ambient temperature range, SSOP-14                                                                        | T <sub>A</sub>           | -40 |      | 150  | °C       |

| 1.2.1.5.  | Temperature range – EEPROM programming                                                                              | T <sub>A-EEP</sub>       | 10  |      | 150  | °C       |

| 1.2.1.6.  | Blocking capacitance between VDDE and VSSE pins                                                                     | Св                       | 75  | 100  |      | nF       |

| 1.2.1.7.  | Sensor bridge current (sine and cosine)                                                                             | I <sub>BRIDGE</sub>      |     |      | 4.0  | mA       |

| 1.2.1.8.  | Capacitive load at outputs                                                                                          | Соит                     |     |      | 20   | nF       |

| 1.2.1.9.  | Output pull-up or pull-down load                                                                                    | R <sub>LOAD</sub>        | 5   |      |      | kΩ       |

| 1.2.1.10. | Angular rate (mechanical)                                                                                           |                          |     |      | 1000 | °/s      |

| 1.2.1.11. | EEPROM programming time for a single address (condition: f <sub>DIGITAL</sub> is within specification; see 1.3.1.7) | tprog                    | 20  |      |      | ms       |

| 1.2.1.12. | Data retention time of memory over lifetime at maximum average temperature 50°C                                     | t <sub>RET</sub>         | 17  |      |      | years    |

| 1.2.1.13. | EEPROM endurance                                                                                                    |                          | 200 |      |      | cycles   |

| 1.2.1.14. | Range of differential input voltage (range of differential sensor output signal)                                    | V <sub>IN-RANGE</sub>    |     |      | ±23  | mV/V     |

| 1.2.1.15. | Range of offset voltage at input that can be digitally compensated                                                  | V <sub>OFFSET-COMP</sub> | -4  |      | +4   | mV/V     |

| 1.2.1.16. | Range of offset temperature compensation at input that can be digitally compensated                                 | T <sub>COEFF-RANGE</sub> | -4  |      | +4   | (μV/V)/K |

|                                                                | Parameter                              | Symbol    | Min | Тур. | Max | Unit      |

|----------------------------------------------------------------|----------------------------------------|-----------|-----|------|-----|-----------|

| 1.2.1.17.                                                      | Common mode input voltage range        | CMR       | 30% |      | 70% | $V_{DDE}$ |

| 1.2.1.18. Waiting time after enabling EEPROM charge pump clock |                                        | tvpp-rise | 1   |      |     | ms        |

| ,                                                              | = 160 K/W assumed. educed performance. |           |     |      |     |           |

#### 1.3. Electrical Parameters

The following electrical specifications are valid for the operating conditions as specified in table 1.2 ( $T_A = -40$ °C to 160°C).

#### 1.3.1. ZSSC5101 Characteristics

Table 1.3 Electrical Characteristics

|          | Parameter                                                   | Symbol                    | Min | Тур. | Max | Unit |

|----------|-------------------------------------------------------------|---------------------------|-----|------|-----|------|

| 1.3.1.1. | Leakage current at VSINP, VSINN, VCOSP, and VCOSN pins      | I <sub>IN-LEAK</sub>      |     |      | 1   | μΑ   |

| 1.3.1.2. | Leakage current at VOUT in high-impedance state             | I <sub>OUT-LEAK</sub>     | -12 |      | +12 | μΑ   |

| 1.3.1.3. | Leakage current difference Vsinp/n, Vcosp/n 1)              | I <sub>IN-DIFF-LEAK</sub> |     |      | 35  | nA   |

| 1.3.1.4. | Current consumption                                         | I <sub>SUPPLY</sub>       |     |      | 7   | mA   |

| 1.3.1.5. | Peak current consumption at startup 1) 2)                   | I <sub>PEAK</sub>         |     |      | 10  | mA   |

| 1.3.1.6. | Sensor supply voltage                                       | $V_{DDS}$                 | 3.8 | 4    | 4.2 | V    |

| 1.3.1.7. | Internal digital master clock frequency (after calibration) | f <sub>DIGITAL</sub>      | 1.5 | 1.6  | 1.8 | MHz  |

<sup>1)</sup> Maximum characterized on samples, not measured in production.

<sup>2)</sup> ZSSC5101 can start with such a peak current for ramps of the power supply with a rise-up time  $> 100 \ \mu s$ .

## 1.3.2. Input Stage Characteristics

Table 1.4 Input Stage Characteristics

|             | Parameter                               | Symbol                     | Conditions                                                                                | Min  | Тур. | Max  | Unit               |

|-------------|-----------------------------------------|----------------------------|-------------------------------------------------------------------------------------------|------|------|------|--------------------|

| 1.3.2.1.    | Common mode rejection ratio             | CMRR                       | Input frequency < 100Hz                                                                   | 60   |      |      | dB                 |

| 1.3.2.2.    | Input preamp offset voltage drift       | TC <sub>VD-IN-OFFSET</sub> | With chopped amplifier                                                                    |      |      | 5    | μV/K               |

| 1.3.2.3.    | Input stage offset                      | INP <sub>OFFSET</sub>      | Referenced to ADCaverage register                                                         |      |      | ±32  | LSB <sub>ADC</sub> |

| 1.3.2.4.    | Input differential nonlinearity         | DNL <sub>ADC</sub>         | ±2 LSB at 12-bit ADC (guaranteed monotony) 1)                                             |      |      | ±500 | ppm                |

| 1.3.2.5.    | Input integral nonlinearity             | INL <sub>INPUT</sub>       | Half input range<br>±2 LSB at 12-bit ADC                                                  |      |      | ±500 | ppm                |

| 1.3.2.6.    | Output referred noise                   |                            | Full range input Referenced to ADC steps after average (16-bit ADCaverageSin register) 1) |      |      | 16   | LSB eff            |

| 1.3.2.7.    | Gain low (programmable)                 |                            |                                                                                           | 17.8 | 18   | 18.2 |                    |

| 1.3.2.8.    | Gain high<br>(programmable)             |                            |                                                                                           | 35.6 | 36   | 36.4 |                    |

| 1.3.2.9.    | Gain matching between high and low gain |                            |                                                                                           |      |      | 0.6  | %                  |

| 1.3.2.10.   | Input noise voltage density             |                            | At bandwidth < 5kHz                                                                       |      |      | 100  | nV/sqrt(Hz)        |

| 1) Refer to | o the ZSSC5101 Application Note -       | Programming.               | •                                                                                         |      |      | •    | •                  |

## 1.3.3. Digital Calculation Characteristics

Table 1.5 Digital Calculation Characteristics

|           | Parameter                                                      | Symbol                | Condition                                                            | Min   | Тур.  | Max  | Unit                 |

|-----------|----------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|-------|-------|------|----------------------|

| 1.3.3.1.  | Input stage resolution                                         | RESINPUT              |                                                                      |       | 12    |      | bit                  |

| 1.3.3.2.  | Resolution at offset measurement                               | RES <sub>OFFSET</sub> |                                                                      |       | 14    |      | bit                  |

| 1.3.3.3.  | CORDIC calculation length                                      |                       |                                                                      |       | 16    |      | bit                  |

| 1.3.3.4.  | CORDIC accuracy for angle value                                |                       |                                                                      | 13    |       |      | bit                  |

| 1.3.3.5.  | CORDIC accuracy for magnitude value                            |                       |                                                                      | 10    |       |      | bit                  |

| 1.3.3.6.  | Channel switching                                              | f <sub>ADC</sub>      |                                                                      |       | 1/16  |      | f <sub>DIGITAL</sub> |

|           | frequency (i.e., the ADC conversion time)                      |                       | With average16not8 bit field in eep_ctrl_manu register 1) set to '0' |       | 1/32  |      | fdigital             |

| 1.3.3.7.  | Update rate of VOUT                                            | f <sub>UPDATE</sub>   |                                                                      | 2     | 3.125 |      | kHz                  |

| 1.3.3.8.  | Channel time skew between sampling of sine and cosine channels | tskew                 |                                                                      |       | 1     |      | 1/f <sub>ADC</sub>   |

| 1.3.3.9.  | Digitally programmable                                         | амах                  | AMR sensors                                                          | 5     |       | 180  | ° mech               |

|           | output angular range                                           |                       | GMR, TMR                                                             | 10    |       | 360  | ° mech               |

| 1.3.3.10. | Angular resolution                                             |                       | AMR sensors Vout = 5 to 95% VDDE                                     | 0.022 |       | 0.04 | ° mech               |

|           |                                                                |                       | GMR, TMR<br>Vout = 5 to 95% VDDE                                     | 0.044 |       | 0.08 | ° mech               |

| 1.3.3.11. | Zero point adjustment                                          |                       | AMR sensors                                                          | 0     |       | 180  | ° mech               |

|           | range<br>(digitally programmable)                              |                       | GMR, TMR                                                             | 0     |       | 360  | ° mech               |

|             | Parameter                                              | Symbol                  | Condition                                                                            | Min | Тур.                                       | Max  | Unit              |

|-------------|--------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------|-----|--------------------------------------------|------|-------------------|

| 1.3.3.12.   | Upper output clamping level                            | V <sub>CLAMP-HIGH</sub> | Max. digital DAC value<br>4864, fixed resolution (see<br>RES <sub>CLAMP</sub> below) | 40  |                                            | 95   | %V <sub>DDE</sub> |

| 1.3.3.13.   | Lower output clamping level                            | V <sub>CLAMP-LOW</sub>  | Min. digital DAC value 256, fixed resolution (see RES <sub>CLAMP</sub> )             | 5   |                                            | 30.5 | %V <sub>DDE</sub> |

| 1.3.3.14.   | Resolution of clamping levels (digitally programmable) | RES <sub>CLAMP</sub>    |                                                                                      |     | 1 / 5120<br>(1/4608<br>of output<br>range) |      | V <sub>DDE</sub>  |

| 1.3.3.15.   | DAC resolution                                         | RES <sub>DAC</sub>      |                                                                                      |     | 1 / 5120<br>(0.02% of<br>VDDE)             |      | $V_{DDE}$         |

| 1) Refer to | the ZSSC5101 Application Note –                        | <br>Programming.        |                                                                                      |     | 1 (002)                                    |      |                   |

## 1.3.4. Analog Output Stage Characteristics (Digital to VOUT)

Table 1.6 Analog Output Stage Characteristics

|          | Parameter                                  | Symbol                 | Condition                                                     | Min   | Тур. | Max  | Unit               |

|----------|--------------------------------------------|------------------------|---------------------------------------------------------------|-------|------|------|--------------------|

| 1.3.4.1. | Output voltage range                       | V <sub>OUT</sub>       | At full supply working range 4.5 V < V <sub>DDE</sub> < 5.7 V | 5     |      | 95   | %V <sub>DDE</sub>  |

| 1.3.4.2. | Error of upper and lower clamping level 1) |                        |                                                               | -0.18 |      | 0.18 | %V <sub>DDE</sub>  |

| 1.3.4.3. | Output offset                              |                        | Chopped output                                                |       |      | ±5   | LSB <sub>DAC</sub> |

| 1.3.4.4. | Differential nonlinearity of DAC           | DNL <sub>DAC</sub>     | Guaranteed monotony                                           |       |      | ±2   | LSB <sub>DAC</sub> |

| 1.3.4.5. | Integral nonlinearity of DAC               | INL <sub>DAC</sub>     |                                                               |       |      | ±3.9 | LSB <sub>DAC</sub> |

| 1.3.4.6. | Output current                             | I <sub>OUT</sub>       | Analog output in Normal<br>Operating Mode                     |       |      | 3    | mA                 |

| 1.3.4.7. | Output current limit 2)                    | I <sub>OUT-LIMIT</sub> | Analog output                                                 |       |      | 20   | mA                 |

<sup>1)</sup> Can be digitally compensated during calibration.

<sup>2)</sup> Overwrite-able for entering the Command Mode. See section 2.3.

## 1.3.5. Analog Input to Analog Output Characteristics (Full Path)

Table 1.7 Full Analog Path Characteristics

|          | Parameter                                               | Symbol                      | Condition                                                                                                                      | Min | Тур. | Max   | Unit                   |

|----------|---------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------------------|

| 1.3.5.1. | Output voltage temperature drift                        | V <sub>OUT-TEMP-DRIFT</sub> | For full angular range including complete function                                                                             |     |      | 1.6   | mV                     |

| 1.3.5.2. | Overall linearity error                                 | INL <sub>ALL</sub>          | Full mechanical input range <sup>1)</sup> 5% to 95% VDDE output range 8.2 LSB of DAC, orthogonal analog input to analog output |     |      | ±0.18 | % V <sub>DDE</sub>     |

| 1.3.5.3. | Output voltage noise                                    | V <sub>NOISE-OUT</sub>      | With external low pass filter $f_C = 0.7 kHz$                                                                                  |     |      | 1.3   | mVeff                  |

| 1.3.5.4. | Propagation delay<br>time to 90% output<br>level change | tprop-delay                 | 45°mech step for AMR,<br>90°mech step for GMR;TMR                                                                              |     |      | 1.8   | ms                     |

| 1.3.5.5. | Power-on time                                           | t <sub>ON</sub>             | Time until first valid data on                                                                                                 | 256 |      |       | 1/f <sub>DIGITAL</sub> |

|          |                                                         |                             | VOUT after V <sub>DDE</sub> > V <sub>PW-ON</sub> (see specification 1.3.7.2)                                                   |     |      | 5     | ms                     |

| 1) Corre | esponds to 180° mechanical ra                           | nge for AMR sensors         | or 360° for GMR, TMR sensors.                                                                                                  | I   |      |       |                        |

<sup>1.3.6.</sup> Digital Interface Characteristics (CMOS compatible)

Table 1.8 gives the digital signal levels during one-wire interface (OWI) communication.

Table 1.8 Digital Interface Characteristics

| Parameter |                                            | Symbol                   | Condition                           | Min | Тур. | Max | Unit              |

|-----------|--------------------------------------------|--------------------------|-------------------------------------|-----|------|-----|-------------------|

| 1.3.6.1.  | Input HIGH level                           | V <sub>IN-HIGH</sub>     |                                     | 75% |      |     | $V_{DDE}$         |

| 1.3.6.2.  | Input LOW level                            | V <sub>IN-LOW</sub>      |                                     |     |      | 25% | $V_{DDE}$         |

| 1.3.6.3.  | Output HIGH level                          | V <sub>OUT-HIGH</sub>    | I <sub>OUT-HIGH</sub> = 2mA         | 90% |      |     | $V_{DDE}$         |

| 1.3.6.4.  | Output LOW level                           | V <sub>OUT-LOW</sub>     | I <sub>OUT-LOW</sub> = 2mA          |     |      | 10% | $V_{DDE}$         |

| 1.3.6.5.  | Switching level                            | V <sub>SWITCH</sub>      |                                     |     | 50%  |     | $V_{DDE}$         |

| 1.3.6.6.  | Hysteresis of Schmitt-triggers on VOUT pin | V <sub>OUT-ST-HYST</sub> | Centered around V <sub>SWITCH</sub> | 10  |      | 16  | %V <sub>DDE</sub> |

#### 1.3.7. Supervision Circuits

See section 2.4 for details for specifications in Table 1.9 that are related to power-up/power-down characteristics.

Table 1.9 Supervision Circuits

|          | Parameter                     |                        | Condition                                                    | Min  | Тур. | Max  | Unit                   |

|----------|-------------------------------|------------------------|--------------------------------------------------------------|------|------|------|------------------------|

| 1.3.7.1. | Time to enter Command Mode 1) | tcode                  | Start-up sequence                                            | 16   | 20   | 26   | ms                     |

| 1.3.7.2. | Power watch on-level 2)       | V <sub>PW-ON</sub>     |                                                              | 4.05 | 4.30 | 4.45 | V                      |

| 1.3.7.3. | Power watch off-level 3)      | V <sub>PW-OFF</sub>    |                                                              | 3.9  | 4.2  | 4.3  | V                      |

| 1.3.7.4. | Hysteresis on/off             | V <sub>HYST</sub>      | V <sub>HYST</sub> = V <sub>PW-ON</sub> - V <sub>PW-OFF</sub> | 100  |      | 350  | mV                     |

| 1.3.7.5. | Power-on level 4)             | V <sub>ON</sub>        |                                                              | 2.4  | 2.7  | 3.3  | V                      |

| 1.3.7.6. | Lower diagnostic range        | $V_{DIAG-LOW}$         | Fixed as DAC value 96                                        |      |      | 4%   | V <sub>DDE</sub> (min) |

| 1.3.7.7. | Upper diagnostic range        | V <sub>DIAG-HIGH</sub> | Fixed as DAC value 5024                                      | 96%  |      |      | V <sub>DDE</sub> (min) |

<sup>1)</sup> After power-on, device checks for correct signature until  $t_{\text{CODE}}$  expires.

#### 1.3.8. Power Loss Circuit

Table 1.10 Power Loss Circuit

| Parameter |                                         | Symbol              | Condition                                                                                | Min | Тур. | Max | Unit |

|-----------|-----------------------------------------|---------------------|------------------------------------------------------------------------------------------|-----|------|-----|------|

| 1.3.8.1.  | Output impedance at VOUT for power loss | R <sub>P-LOSS</sub> | VDDE – VSSE < 0.7V<br>Corresponds to<br>diagnostics range for<br>pull-up/pull-down ≥ 5kΩ |     |      | 200 | Ω    |

<sup>2)</sup> If  $V_{\text{DDE}}$  is above this level, VOUT is on in Normal Operating Mode.

<sup>3)</sup> If  $V_{\text{DDE}}$  is below this level, VOUT is set to the defined Diagnostics Mode.

<sup>4)</sup> If V<sub>DDE</sub> is equal to or below this level, VOUT is in reset state or diagnostics LOW state (see Table 2.1).

## 2 Circuit Description

#### 2.1. Overview

The ZSSC5101 is a sensor signal conditioner and encoder for magnetoresistive sensor bridges. In a typical setup for rotational or linear motion, the sensor bridges provide two sinusoidal signals, which are phase-shifted by 90° (Vsin and Vcos). The ZSSC5101 converts these two signals into a linear voltage ramp, proportional to the rotation angle or linear distance by means of a CORDIC (Coordinate Rotation Digital Computer) algorithm.

The output voltage V<sub>OUT</sub> (see specification 1.3.4.1) is ratiometric to V<sub>DDE</sub>; the typical supply voltage is 5V ±10%.

Using the ZSSC5101's one-wire interface (OWI), a sensor assembly containing an xMR sensor bridge and the ZSSC5101 can be connected to a host controller by means of just three wires:

- V<sub>DDE</sub> (4.5 to 5.5V)

- VOUT (sensor output and programming input)

- V<sub>SSE</sub> (ground)

The VOUT pin is used for sensor output, programming, and diagnostics for the ZSSC5101 through the OWI (see section 2.3). All parameters are stored in a nonvolatile memory (EEPROM) and can be read and re-programmed by the user.

By using the output pin for programming, no additional wires are required to calibrate the sensor. This facilitates in-line programming and re-programming of fully assembled sensor modules.

The ZSSC5101 also provides failure mode detection, such as broken supply or broken ground detection. In Normal Operating Mode, the output voltage ranges from  $\geq$ 5%  $V_{DDE}$  to  $\leq$ 95%  $V_{DDE}$ . Both clamping levels are programmable (see specifications 1.3.3.12 and 1.3.3.13).

In the case of failure detection, the output voltage will be outside the normal operating range ( $<4\%V_{DDE}$  and  $>96\%V_{DDE}$ ).

#### 2.2. Functional Description

Figure 2.1 provides the block diagram for the ZSSC5101. See section 11 for the definitions of the abbreviations.

Figure 2.1 ZSSC5101 Block Diagram

The ZSSC5101 is supplied by a single supply voltage  $V_{DDE}$  of 5V  $\pm 10\%$ . Internal low-dropout linear voltage regulators (LDOs) generate the required analog and digital supply voltages as well as the supply voltage for the sensor bridge, VDDS.

The ZSSC5101 accepts fully differential signals from both sine and cosine sensor bridges. These signals are connected to the VSINP, VSINN pins and the VCOSP, VCOSN pins, respectively.

Both sine and cosine signals are then multiplexed, sequentially pre-amplified, and sampled by a 12-bit ADC. The xMR COS/SIN-bridge circuitry is alternately sampled at a frequency of ~200kHz to ensure an identical signal conversion in both sine and cosine paths.

Following data conversion, the digital sine and cosine values representing X and Y rectangular coordinates are converted into their respective polar coordinates, phase, and magnitude by means of coordinate transformation using a CORDIC algorithm.

**Phase information** ranges from 0 to  $2\pi$ , which is equivalent to one full wave of the input signal. This information is further used to calculate the analog output voltage, depending on the user-programmable settings, such as zero position or angle range. See section 4.3 for further details.

The **magnitude information** is equivalent to the strength of the input signal (Vpeak). This information is further used to determine a "magnet loss" error state. See section 2.6 for further details.

Based on the calculated phase information and the user-programmed zero, slope, and clamping parameters, the corresponding output values are calculated and routed to the DAC input. The DAC output is driven by a buffer amplifier and routed to the output pin VOUT.

#### 2.3. One-Wire Interface and Command Mode (CM)

In Normal Operating Mode (NOM), the VOUT pin is a buffered, analog output, providing an output voltage equivalent to the sensor input signals.

Because the same pin is used for programming via the OWI, a specific sequence is required to put the ZSSC5101 into command / programming mode (CM):

- After power-on, the circuit starts in NOM and provides a valid output signal after t\_on.

- In parallel, the ZSSC5101 monitors the VOUT pin for a valid signature command from the programming system to enable the Command Mode (authorization). Therefore, the programming system must be able to overdrive the output buffer with a driver strength greater than I<sub>OUT-LIMIT</sub> (see 1.3.4.7).

- The ZSSC5101 can only be unlocked by receiving a predefined user-programmable signature. This signature is stored in the EEPROM in a write-only register.

- If CM is active, the output buffer is switched to high impedance and communication over the one-wire interface is enabled.

- The time frame to enter CM with a valid signature command is limited to t<sub>CODE</sub>, but it is always open in Diagnostics Mode (see section 2.6).

- Digital data transmission over the one-wire-interface bus is accomplished using PWM-coded signals. For further information on the OWI protocol, please contact IDT technical support (see contact information on page 28).

#### 2.4. Power-Up/Power-Down Characteristics

Table 2.1 describes the behavior of the ZSSC5101 during ramp-up and ramp-down of the power supply voltage  $V_{DDE}$ . See Table 1.7 and Table 1.9 for the timing and voltage specifications. In each condition, the ZSSC5101 is in a defined state, which is a substantial feature for safety-critical applications.

Table 2.1 Output Modes during Power-Up and Power-Down

| V <sub>DDE</sub> Voltage<br>Range [V] | Description                                                                                                                                                                                                                                                             | Behavior at VOUT                                             |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 0.0 to 1.5                            | The ZSSC5101 is in reset state.                                                                                                                                                                                                                                         | Active driven output to a voltage level between 0 and VDDE/2 |

| 1.5 to 2.5                            | VOUT is driven to LOW state.                                                                                                                                                                                                                                            | Diagnostics LOW level                                        |

| 2.5 to 4.2                            | If $V_{\text{DDE}} > V_{\text{ON}}$ , the power-on reset is released and all modules are activated.                                                                                                                                                                     | Diagnostics Mode (see section 2.6)                           |

| 4.2 to 4.5                            | If $V_{\text{DDE}}$ > $V_{\text{PW-ON}}$ , VOUT is turned on after $t_{\text{ON}}$ and drives the last calculated angle value from the DAC. If $V_{\text{DDE}}$ < $V_{\text{PW-OFF}}$ , the ZSSC5101 enters Diagnostics Mode; however, brief voltage drops are ignored. | Analog output with reduced accuracy                          |

| 4.5 to 5.7                            | Normal operation range.                                                                                                                                                                                                                                                 | Normal Operation Mode Analog output with specified accuracy  |

#### 2.5. Power Loss / GND Loss

#### 2.5.1. Purpose

In NOM, the output voltage of the ZSSC5101 is within the range of 5%VDDE ≤ VOUT ≤ 95% VDDE.

In the event of a loss of VDDE or VSSE, for example due to a broken supply wire, the output voltage VOUT will be driven into the diagnostics range, which is a voltage level outside of the normal operating range. This makes a power loss easily identifiable by the host controller.

The diagnostic levels are defined as

• Diagnostics LOW level: VOUT <= 4% VDDE; see specification 1.3.7.6

• Diagnostics HIGH level: VOUT >= 96% VDDE; see specification 1.3.7.7

#### 2.5.2. Power Loss Behavior

In order to ensure that the output can be safely driven to the Diagnostics Mode levels, a pull-up or pull-down resistor  $\geq 5k\Omega$  must be connected at the receiving side of the VOUT signal.

Table 2.2 Power Loss Behavior

| External Resistor | VDDE Loss              | VSSE Loss                |  |  |

|-------------------|------------------------|--------------------------|--|--|

| Pull-Up ≥ 5kΩ     | Diagnostics   OW lovel | Diagnostics IIICII level |  |  |

| Pull-Down ≥ 5kΩ   | Diagnostics LOW level  | Diagnostics HIGH level   |  |  |

#### 2.6. Diagnostics Mode (DM)

In addition to the power loss indication described above, the ZSSC5101 also indicates other error states by switching the output VOUT into Diagnostics Mode. These errors are described in Table 2.3.

Table 2.3 Diagnostics Mode

| Error Source         | Error Condition                                                                              | Error De-activation                                   |

|----------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Loss of input signal | Loss of magnet; magnitude is below a pre-programmed threshold                                | Magnitude must be above the threshold; power-on reset |

| EEPROM               | CRC error                                                                                    | Power-on reset                                        |

| EEPROM               | EEPROM read failure                                                                          | Power-on reset                                        |

| DAC                  | No valid DAC values                                                                          | Valid DAC values are available                        |

| Supply voltage       | Low V <sub>DDE</sub> ; V <sub>DDE</sub> < V <sub>PW-OFF</sub> ;<br>see specification 1.3.7.3 | VDDE > V <sub>PW-ON</sub> ; see specification 1.3.7.2 |

The state of the Diagnostics Mode is programmable in the EEPROM, it has the following options:

- · Diagnostics LOW level

- · Diagnostics HIGH level

- High impedance (in this setting, external pull-up or pull-down resistors must be connected to VOUT)

#### 3 EEPROM

The ZSSC5101 contains a non-volatile EEPROM memory for storing manufacturer codes and calibration values as well as user-programmable data. Access to the EEPROM is available over the output pin VOUT by using IDT's one-wire interface (see section 2.3).

#### 3.1. User Programmable Parameters in EEPROM

Table 3.1 shows the user accessible settings of the EEPROM. These settings are used to adjust the analog output VOUT to the mechanical movement range and provide space for a user-selectable identification number.

Table 3.1 EEPROM — User Area

| Function            | Description                                                                                                                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Zero angle          | Mechanical zero position                                                                                                       |

| Magnet loss         | Threshold that defines when the magnet loss error diagnostic state is turned on/off                                            |

| Angular range slope | Multiplication factor for determining the slope of the analog output                                                           |

| Clamp low and high  | Upper and lower clamping levels when the mechanical angle is at the minimum, maximum, or outside of the normal operation range |

| User ID             | 32-bit user-selectable identification number                                                                                   |

| Clamp switch angle  | Angle position at which the output changes the clamping level state                                                            |

| Slope direction     | Rising or falling slope of output voltage vs. rotation; clockwise or counterclockwise operation                                |

| PGA gain            | Input preamplifier gain: low/high                                                                                              |

| Diagnostics Mode    | VOUT state in Diagnostics Mode: LOW, HIGH, or high impedance                                                                   |

For detailed information about EEPROM programming and register settings, refer to the *ZSSC5101 Application Note – Programming*.

#### 3.2. CRC Algorithm

EEPROM data is verified by implementing an 8-bit cyclic redundancy check (CRC).

#### 3.3. EDC Algorithm

The EEPROM is protected against bit errors through an error detection and correction (EDC) algorithm. The protection logic corrects any single-bit error in a data word and can detect all double-bit errors. A single-bit error is corrected, and the ZSSC5101 continues in Normal Operating Mode. On detection of a double-bit error, the ZSSC5101 enters the Diagnostics Mode.

## 4 Application Circuit Examples

#### 4.1. Typical Application Circuit for AMR Double Wheatstone Sensor Bridges

Figure 4.1 ZSSC5101 with AMR Sensor Bridge

The circuit diagram in Figure 4.1 shows a typical application for the ZSSC5101 with an AMR double Wheatstone sensor bridge. Due to the nature of AMR sensors, the periodicity of these sensor signals is 180 mechanical degrees.

The sensor bridges are mechanically rotated by 45° from each other, providing differential output signals that are 90 electrical degrees apart. The ZSSC5101 converts these sine and cosine signals into a linear output voltage with a programmable full-scale angle range from 0° to 5° up to 0° to 180° with a resolution of 0.022° to 0.04° per step (see specification 1.3.3.10). The ZSSC5101 accepts sensor signals with a sensitivity up to ±23mV/V (see specification 1.2.1.14), which is sufficient for a typical AMR sensor bridge. No external components are required at the sensor inputs.

#### 4.2. Typical Application Circuit for TMR Sensor Bridges

Figure 4.2 ZSSC5101 with TMR Sensor Bridge

The circuit diagram in Figure 4.2 shows a typical application for the ZSSC5101 with two TMR sensor bridges. TMR and GMR sensors have a periodicity of 360 mechanical degrees; therefore this configuration can be used to measure the absolute angle of a full mechanical turn.

The sensor bridges are mechanically rotated by 90° from each other, providing differential output signals that are 90 electrical degrees apart. The ZSSC5101 converts these sine and cosine signals into a linear output voltage with a programmable full-scale angle range from 0° to 10° up to 0° to 360° with a resolution of 0.044° to 0.08° per step (see specification 1.3.3.10). As a TMR sensor bridge has a much higher sensitivity than an AMR Sensor (up to 2 orders of magnitude), a resistive divider consisting of 2x Rs and Rp is added to each sensor input channel (sin, cos) of the ZSSC5101 to match the sensor bridge with the ZSSC5101 inputs.

For best temperature compensation, Rs and Rp should have the same temperature coefficient TC and routed close together on the same printed circuit board (PCB).

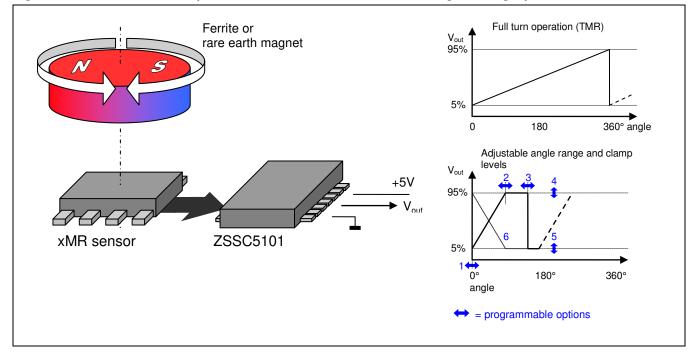

#### 4.3. Mechanical Set-up for Absolute Angle Measurements

Figure 4.3 shows a typical set-up for an absolute rotation angle measurement. A diametrically magnetized magnet is mounted at the end of a rotating shaft with a specific gap. The rotation axis of the magnet is centered over the xMR sensor (see sensor manufacturer's data sheet for exact location). Depending on the maximum angle to be measured, the sensor can be either an AMR sensor with a maximum absolute angle of 180° or a TMR/GMR sensor with a maximum absolute angle of 360° (see 4.1 and 4.2 for further details).

The ZSSC5101 converts the sine and cosine signals generated by the xMR sensor bridge into a linear ramp that is proportional to the rotation angle.

The gap between magnet and sensor is determined by the strength of the magnet and the type of sensor. Stronger magnets allow larger air gaps, and due to their higher sensitivity, TMR sensors allow larger air gaps than AMR sensors. The air gap should be chosen such that the sensor output signal remains undistorted and sinusoidal.

In order to adjust the linear ramp to the mechanical angle range, the ZSSC5101 provides several programmable parameters. These parameters are stored in an on-chip EEPROM and can be re-programmed by the user (see Figure 4.3):

- Zero angle position: aligns the mechanical zero position to the electrical zero position

- Maximum angle position: matches the full stroke of the ramp to the mechanical angular range

- Clamp switch angle: defines the angle position where the output voltage returns from V<sub>out,max</sub> to V<sub>out,min</sub>

- Maximum output voltage, upper clamping level Vout,max

- Minimum output voltage, lower clamping level Vout.min

- · Ramp direction: rising or falling ramp

Figure 4.3 Mechanical Set-up for Rotational Measurements and Programming Options

#### 4.4. Mechanical Set-up for Linear Distance Measurements

Figure 4.4 shows a typical set-up for a linear distance measurement. The xMR sensor provides a sinusoidal signal that is proportional to the length of a magnetic pole (AMR) or to the length of a magnetic pole pair (TMR). The graph shown below shows a setup for an AMR sensor (e.g., Sensitec AA700 family; <a href="https://www.sensitec.com">www.sensitec.com</a>, Measurement Specialties KMT series, <a href="https://www.meas-spec.com">www.meas-spec.com</a>).

As the magnet is moving on a linear path, one output ramp is generated with each pole; hence an absolute linear distance measurement is possible within the length of one pole:

absolute

$$\_$$

position =  $L_P * \frac{V_{out} - V_{out,min}}{V_{out,max} - V_{out,min}}$

where:  $L_P =$  pole length of the sensor magnet

$V_{OUT} =$  output voltage of the ZSSC5101

$V_{OUT,max}$  = maximum output clamping voltage of ZSSC5101 (programmable; e.g. 95% VDD)

V<sub>OUT</sub>,<sub>min</sub> = minimum output clamping voltage of ZSSC5101 (programmable; e.g. 5% VDD)

Longer linear distances can be measured by using multi-pole magnetic strips and by counting the number of ramps from a defined home position. Each full ramp  $(V_{OUT,min}$  to  $V_{OUT,max})$  corresponds to the length of one magnetic pole.

Figure 4.4 Mechanical Set-up for Linear Distance Measurements and Programming Options

#### 4.5. Input-to-Output Characteristics Calculation Examples

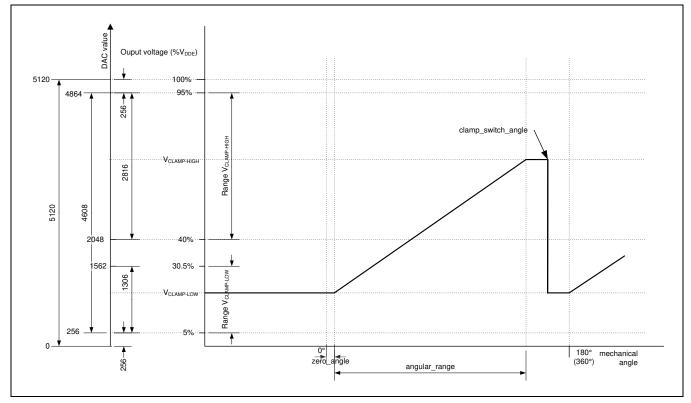

Figure 4.5 shows a detailed view of the possible settings for clamping levels, zero position, ramp slope, and clamp switch angle.

The total output range VOUT from 0 to 100% VDDE is 5120 DAC steps.

In the normal operating range (5 to 95% VDDE), the DAC output can range from 256 to 4864, allowing 4608 steps (12.17bit) for the analog output voltage.

The full-scale angular range is 180° for AMR sensors and 360° for GMR and TMR sensors. Consequently, the full-scale angular step resolution is

180°/4608 = 0.039 mechanical degrees for AMR sensors and

360°/4608 = 0.078 mechanical degrees for GMR and TMR sensors

Smaller angular ranges result in a finer angular step resolution. The smallest angle step is 0.022° (= 180°/8192). For example, a total stroke of 30° (e.g., in a pedal application) will yield the following results:

$30^{\circ}/0.022^{\circ} = 1365$  steps (using an AMR sensor)

Figure 4.5 Input-to-Output Characteristics with Parameters

## 5 ESD and Latch-up Protection

#### 5.1. Human Body Model

The ZSSC5101 conforms to standard MIL-STD-883D Method 3015.7, rated at 4000V, 100pF,  $1.5k\Omega$  according to the Human Body Model. This protection is ensured at all external pins (VOUT) including the device supply (VDDE, VSSE). ESD protection on all other pins (VDDS, VSSS, VSINP, VSINN, VCOSP, VCOSN) is up to 2000V.

#### 5.2. Machine Model

The ZSSC5101 conforms to standard EIA/JESD22-A115-A, rated at 400V, 200pF, and  $0k\Omega$  according to the machine model. This protection is ensured at all external pins (VOUT) including device supply (VDDE, VSSE). ESD protection on all other pins (VDDS, VSSS, VSINP, VSINN, VCOSP, VCOSN) is up to 200V.

#### 5.3. Charged Device Model

The ZSSC5101 conforms to standard AEC Q100 (Rev. F) and EIA/JESD22/C101, rated at 750V for corner pins and 500V for all other pins (class C3B) according to the Charge Device Model. This protection is ensured at all external pins,

#### 5.4. Latch-Up

The ZSSC5101 conforms to EIA/JEDEC Standard No. 78.

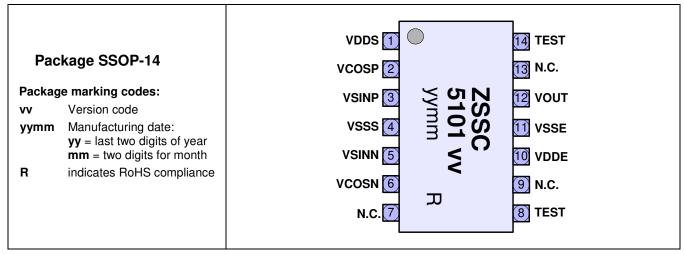

## **6** Pin Configuration and Package Dimensions

The ZSSC5101 is available in a SSOP14 green package or as bare die.

Table 6.1 Pin Configuration

| Pin No<br>Die | Pin No<br>SSOP-14 | Pin<br>Name | Description                                 | Notes                                        |

|---------------|-------------------|-------------|---------------------------------------------|----------------------------------------------|

| 1             | 10                | VDDE        | Positive analog supply voltage              | Positive supply voltage, 5V ±10%             |

| 2             | 11                | VSSE        | Negative analog supply voltage              | Negative supply voltage, must connect to GND |

| 3             | 12                | VOUT        | Analog output/one-wire interface (OWI)      |                                              |

| 4             | 1                 | VDDS        | Positive sensor supply voltage              |                                              |

| 5             | 2                 | VCOSP       | Positive sensor signal cosine channel input |                                              |

| 6             | 3                 | VSINP       | Positive sensor signal sine channel input   |                                              |

| 7             | 4                 | VSSS        | Negative sensor supply voltage              |                                              |

| 8             | 5                 | VSINN       | Negative sensor signal sine channel input   |                                              |

| 9             | 6                 | VCOSN       | Negative sensor signal cosine channel input |                                              |

|               | 7                 | N.C.        | Unconnected pin                             | Must be left open                            |

|               | 8                 | TEST        | Factory test pin                            | Must be left open                            |

|               | 9                 | N.C.        | Unconnected pin                             | Must be left open                            |

|               | 13                | N.C.        | Unconnected pin                             | Must be left open                            |

|               | 14                | TEST        | Factory test pin                            | Must be left open                            |

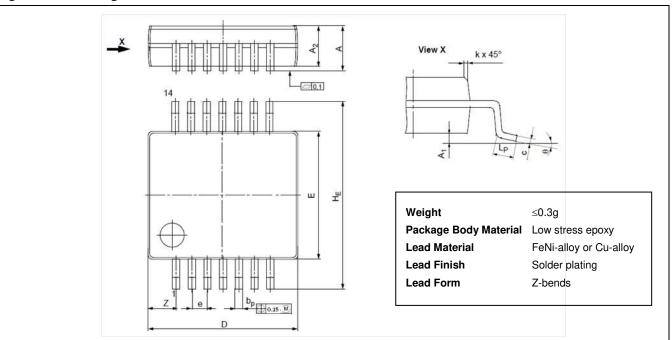

## 6.1. Package Drawing – SSOP-14

The SSOP-14 package is a delivery option for the ZSSC5101. The package dimensions based on the JEDEC JEP95: MO-150 standard illustrated in Figure 6.1.

Figure 6.1 Package Dimensions - SSOP-14

| Dimension            | Minimum      | Maximum |  |  |  |

|----------------------|--------------|---------|--|--|--|

| Α                    | 1.73         | 1.99    |  |  |  |

| A <sub>1</sub>       | 0.05         | 0.21    |  |  |  |

| A <sub>2</sub>       | 1.68         | 1.78    |  |  |  |

| b <sub>P</sub>       | 0.25         | 0.38    |  |  |  |

| С                    | 0.09         | 0.20    |  |  |  |

| D*                   | 6.07         | 6.33    |  |  |  |

| е                    | 0.65 nominal |         |  |  |  |

| E*                   | 5.20         | 5.38    |  |  |  |

| HE                   | 7.65         | 7.90    |  |  |  |

| k                    | 0.25         |         |  |  |  |

| L <sub>P</sub>       | 0.63         |         |  |  |  |

| θ                    | 0°           | 10°     |  |  |  |

| * Without mold-flash |              |         |  |  |  |

Figure 6.2 Pin Map and Pad Position of the ZSSC5101 SSOP-14 Package

#### 6.2. Die Dimensions and Pad Coordinates

Die dimensions and pad coordinates are available on request in a separate document. See section 10.

## 7 Layout Requirements

**Recommendation:** Keep the traces between the xMR sensor and the ZSSC5101 (VDDS, VSSS, VSINP, VSINN, VCOSP, and VCOSN pins) as short as possible. Additional resistors for using TMR sensors (see Figure 4.2) should have the same temperature coefficient TC and be routed close together on the same PCB.

## 8 Reliability and RoHS Conformity

The ZSSC5101 is qualified according to the AEC-Q100 standard, operating temperature grade 0.

The ZSSC5101 complies with the RoHS directive and does not contain hazardous substances.

The complete RoHS declaration update can be downloaded at www.IDT.com.

## 9 Ordering Information

| Sales Code   | Description                                                                                                                                                                                                                                                                                                             | Delivery Package                                      |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| ZSSC5101BE1B | ZSSC5101 Die - Temperature range: -40°C to +160°C                                                                                                                                                                                                                                                                       | 8" tested wafer, unsawn, thickness = 390 ±15μm        |  |  |  |

| ZSSC5101BE2B | ZSSC5101 Die - Temperature range: -40°C to +160°C                                                                                                                                                                                                                                                                       | 8" tested wafer, unsawn, thickness = 725 ±15μm        |  |  |  |

| ZSSC5101BE3B | ZSSC5101 Die – Temperature range: -40°C to +160°C                                                                                                                                                                                                                                                                       | 8" tested wafer, unsawn, thickness = 250 ±15μm        |  |  |  |

| ZSSC5101BE1C | ZSSC5101 Die - Temperature range: -40°C to +160°C                                                                                                                                                                                                                                                                       | 8" tested wafer, sawn on frame, thickness = 390 ±15μm |  |  |  |

| ZSSC5101BE4R | ZSSC5101 SSOP-14 – Temperature range: -40°C to +150°C                                                                                                                                                                                                                                                                   | 13" tape and reel                                     |  |  |  |

| ZSSC5101BE4T | ZSSC5101 SSOP-14 – Temperature range: -40°C to +150°C                                                                                                                                                                                                                                                                   | Tube                                                  |  |  |  |

| ZSSC5101 KIT | ZSSC5101 Evaluation Kit including USB Communication Board, ZSSC5101 AMR board, adapters. Software can be downloaded from <a href="https://www.lDT.com/ZSSC5101">www.lDT.com/ZSSC5101</a> after free customer login, which is described in section 10 (see the ZSSC5101 Evaluation Kit and GUI Description for details). |                                                       |  |  |  |

## 10 Related Documents

| Document                                      |

|-----------------------------------------------|

| ZSSC5101 Feature Sheet                        |

| ZSSC5101 Evaluation Kit and GUI Description * |

| ZSSC5101 Technical Note – Die Dimensions **   |

| ZSSC5101 Application Note – Programming **    |

Visit the ZSSC5101 product page <a href="https://www.IDT.com/ZSSC5101">www.IDT.com/ZSSC5101</a> or contact your local sales office for the latest version of these documents.

- \* Note: Documents marked with an asterisk (\*) require a free customer login account.

- \*\* Note: Documents marked with two asterisks (\*\*) are available only on request.

# 11 Glossary

| Term   | Description                            |

|--------|----------------------------------------|

| AFE    | Analog Frontend                        |

| AMR    | Anisotropic Magnetoresistance          |

| СМ     | Command Mode                           |

| CORDIC | Coordinate Rotation Digital Computer   |

| DAC    | Digital-to-Analog Converter            |

| DM     | Diagnostic Mode                        |

| EDC    | Error Detection and Correction         |

| GMR    | Giant Magnetoresistance                |

| INL    | Integral Nonlinearity                  |

| LDO    | Low-Dropout Linear Voltage Regulators  |

| MUX    | Multiplexer                            |

| NOM    | Normal Operating Mode                  |

| OWI    | One-Wire Interface                     |

| РСВ    | Printed Circuit Board                  |

| THJA   | Junction to Ambient Thermal Resistance |

| TMR    | Tunnel Magnetoresistance               |

# 12 Document Revision History

| Revision | Date               | Description                                                                                                                                                                                                                                                                                    |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00     | August 25, 2014    | First release document                                                                                                                                                                                                                                                                         |

| 1.10     | September 10, 2014 | Add package drawing                                                                                                                                                                                                                                                                            |

| 1.20     | April 13, 2015     | Updates for INL <sub>DAC</sub> , TMR application schematic, pin names. Addition of package marking codes in Figure 6.2. Removal of references to half-bridge applications. Corrections for step number in section 4.5 and Figure 4.5. Update for contact information. Minor edits for clarity. |

| 1.21     | April 17, 2015     | Correction for maximum temperature for SSOP-14.                                                                                                                                                                                                                                                |

| 1.22     | April 29, 2015     | Removal of reference to amplitude calibration on page 1.                                                                                                                                                                                                                                       |

|          | January 22,2016    | Changed to IDT branding.                                                                                                                                                                                                                                                                       |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/