#### Very Low Power 2-Output PCIe Clock Generator With On-chip Termination

#### **Features**

- → 1.8V supply voltage

- → Crystal/CMOS input: 25 MHz

- → 2 differential low power HCSL outputs with on-chip termination

- → Individual output enable

- → Reference CMOS output

- → Programmable Slew rate and output amplitute for each output

- → Differential outputs blocked until PLL is locked

- → Selectable 0%, -0.25% or -0.5% spread on differential outputs

- → Strapping pins or SMBus for configuration;

- → 3.3V tolerant SMBus interface support

- → Very low jitter outputs

- → Differential cycle-to-cycle jitter <50ps

- → Differential output-to-output skew <50ps

- → PCIe Gen1/Gen2/Gen3/Gen4 compliant

- → CMOS REFOUT phase jitter is < 1.5ps RMS

- → Packaging (Pb-free & Green): 24-lead 4×4mm TQFN

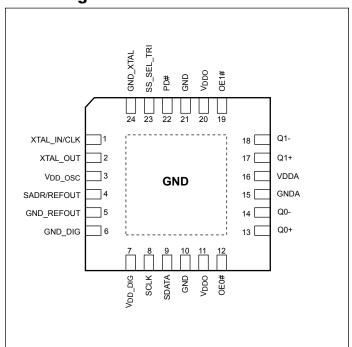

## **Pin Configuration**

### **Description**

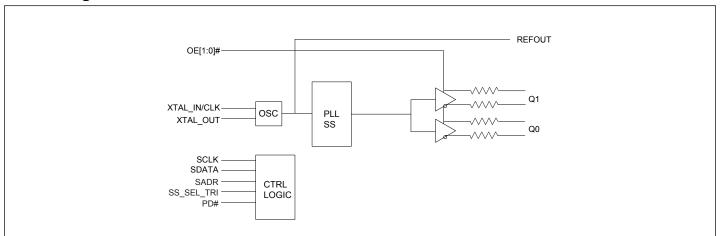

The PI6CG18201 is an 2-output very low power PCIe Gen1/Gen2/Gen3/Gen4 clock generator. It uses 25MHz crystal or CMOS reference as an input to generate the 100MHz low power differential HCSL outputs with on-chip terminations. The on-chip termination can save 8 external resistors and make layout easier. An additional buffered reference output is provided to serve as a low noise reference for other circuitry.

It uses Diodes' proprietary PLL design to achieve very low jitter that meets PCIe Gen1/Gen2/Gen3/Gen4 requirements. It also provides various options such as different slew rate and amplitude through strapping pins or SMBUS so that users can configure the device easily to get the optimized performance for their individual boards. The device also supports selectable spread-spectrum options to reduce EMI for various applications.

## **Block Diagram**

2

## **Pin Description**

| Pin#   | Pin Name             | Ту               | ре        | Description                                                                                                                                                                                               |

|--------|----------------------|------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | XTAL_IN/CLK          | Input            |           | Crystal input or CMOS reference input                                                                                                                                                                     |

| 2      | XTAL_OUT             | Output           |           | Crystal output                                                                                                                                                                                            |

| 3      | V <sub>DD</sub> _OSC | Power            |           | Power supply for oscillator circuitry, nominal 1.8V                                                                                                                                                       |

| 4      | SADR/REFOUT          | Input/<br>Output | CMOS      | Latch to select SMBus Address or 1.8V LVCMOS REFOUT. This pin has an internal pull-down.                                                                                                                  |

| 5      | GND_REFOUT           | Power            |           | Ground for REFOUT                                                                                                                                                                                         |

| 6      | GND_DIG              | Power            |           | Ground for digital circuitry                                                                                                                                                                              |

| 7      | V <sub>DD</sub> _DIG | Power            |           | Power supply for digital circuitry, nominal 1.8V                                                                                                                                                          |

| 8      | SCLK                 | Input            | CMOS      | SMBUS clock input, 3.3V tolerant                                                                                                                                                                          |

| 9      | SDATA                | Input/<br>Output | CMOS      | SMBUS Data line, 3.3V tolerant                                                                                                                                                                            |

| 10, 21 | GND                  | Power            |           | Ground                                                                                                                                                                                                    |

| 11, 20 | $V_{\mathrm{DDO}}$   | Power            |           | Power supply for differential outputs                                                                                                                                                                     |

| 12     | OE0#                 | Input            | CMOS      | Active low input for enabling Q0 pair. This pin has an internal pull-down. 1 = disable outputs, 0 = enable outputs                                                                                        |

| 13     | Q0+                  | Output           | HCSL      | Differential true clock output                                                                                                                                                                            |

| 14     | Q0-                  | Output           | HCSL      | Differential complementary clock output                                                                                                                                                                   |

| 15     | GNDA                 | Power            |           | Ground for analog circuitry                                                                                                                                                                               |

| 16     | $V_{\mathrm{DDA}}$   | Power            |           | Power supply for analog circuitry                                                                                                                                                                         |

| 17     | Q1+                  | Output           | HCSL      | Differential true clock output                                                                                                                                                                            |

| 18     | Q1-                  | Output           | HCSL      | Differential complementary clock output                                                                                                                                                                   |

| 19     | OE1#                 | Input            | CMOS      | Active low input for enabling Q1 pair. This pin has an internal pull-down. 1 = disable outputs, 0 = enable outputs                                                                                        |

| 22     | PD#                  | Input            | CMOS      | Input notifies device to sample latched inputs and start up on first high assertion. Low enters Power Down Mode, subsequent high assertions exit Power Down Mode. This pin has internal pull-up resistor. |

| 23     | SS_SEL_TRI           | Input            | Tri-level | Latched select input to select spread spectrum amount at initial power up $1 = -0.5\%$ spread, $M = -0.25\%$ , $0 = Spread Off$                                                                           |

| 24     | GND_XTAL             | Power            |           | Ground for oscillator circuit                                                                                                                                                                             |

### **SMBus Address Selection Table**

|                                           | SADR | Address | +Read/Write Bit |

|-------------------------------------------|------|---------|-----------------|

| State of SADB on first application of BD# | 0    | 1101000 | X               |

| State of SADR on first application of PD# | 1    | 1101010 | X               |

## **Power Management Table**

| PD# | SMBus OE bit | OEn# | Qn+     | Qn-     | REFOUT  |

|-----|--------------|------|---------|---------|---------|

| 0   | X            | X    | Low     | Low     | HiZ     |

| 1   | 1            | 0    | Running | Running | Running |

| 1   | 1            | 1    | Low     | Low     | Low     |

| 1   | 0            | X    | Low     | Low     | Low     |

## **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                                    | 65°C to +150°C          |

|--------------------------------------------------------|-------------------------|

| Junction Temperature                                   | up to +125°C            |

| Supply Voltage to Ground Potential, ${ m V}_{ m DDxx}$ |                         |

| Input Voltage –0.5V to V <sub>DI</sub>                 | D+0.5V, not exceed 2.5V |

| SMBus, Input High Voltage                              | 3.6V                    |

| ESD Protection (HBM)                                   | 2000 V                  |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Operating Conditions**

Temperature = T<sub>A</sub>; Supply voltages per normal operation conditions; See test circuits for the load conditions

| Symbol                                                | Parameters                                       | Conditions                                                 | Min. | Тур. | Max. | Units |

|-------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------|------|------|------|-------|

| $V_{DDO}$ , $V_{DDA}$ , $V_{DD\_OSC}$ , $V_{DD\_DIG}$ | Power Supply Voltage                             |                                                            | 1.7  | 1.8  | 1.9  | V     |

| $I_{DDA}$                                             | Analog Power Supply Current                      | All outputs active @100MHz                                 |      | 7    | 8    | mA    |

| $I_{DD}$                                              | Power Supply Current                             | All $V_{DD}$ , except $V_{DDA}$ All outputs active @100MHz |      | 15   | 18   | mA    |

| I <sub>DD_WL</sub>                                    | Power Supply Wake-on-LAN <sup>1</sup><br>Current | All $V_{DD}$ , $Q$ outputs off, REF output running         |      | 1.5  | 2    | mA    |

| I <sub>DD_PD</sub>                                    | Power Supply Power Down <sup>2</sup> Current     | All outputs off                                            |      | 0.6  | 1    | mA    |

| $T_{A}$                                               | Ambient Temperature                              | Industrial grade                                           | -40  |      | 85   | °C    |

#### Note:

<sup>1.</sup> Wake-on-LAN mode: PD# = '0' Byte 3, bit 5 = '1'

<sup>2.</sup> Power down mode: PD# = '0' Byte 3, bit 5 = '0'

Nov 2017

## **Input Electrical Characteristics**

| Symbol           | Parameters                                  | Conditions | Min. | Тур. | Max. | Units |

|------------------|---------------------------------------------|------------|------|------|------|-------|

| R <sub>pu</sub>  | Internal pull up resistance                 |            |      | 120  |      | ΚΩ    |

| R <sub>dn</sub>  | Internal pull down resistance               |            |      | 120  |      | ΚΩ    |

| $C_{XTAL}$       | Internal capacitance on X_IN and X_OUT pins |            |      | 5    |      | pF    |

| L <sub>PIN</sub> | Pin inductance                              |            |      |      | 7    | nН    |

### **Crystal Characteristic**

| Parameters       | Description                  | Min. | Тур       | Max. | Units |

|------------------|------------------------------|------|-----------|------|-------|

| OSCmode          | Mode of Oscillation          | F    | undamenta | al   |       |

| FREQ             | Frequency                    |      | 25        |      | MHz   |

| ESR <sup>1</sup> | Equivalent Series Resistance |      |           | 50   | Ω     |

| Cload            | Load Capacitance             |      | 8         |      | pF    |

| Cshunt           | Shunt Capacitance            |      |           | 7    | pF    |

|                  | Drive Level                  |      |           | 300  | uW    |

#### Note:

### **SMBus Electrical Characteristics**

Temperature = T<sub>A</sub>; Supply voltages per normal operation conditions; See test circuits for the load conditions

| Symbol               | Parameters                | Conditions                                     | Min.                       | Тур. | Max. | Units |

|----------------------|---------------------------|------------------------------------------------|----------------------------|------|------|-------|

| V <sub>DDSMB</sub>   | Nominal bus voltage       |                                                | 1.7                        |      | 3.6  | V     |

|                      |                           | SMBus, $V_{DDSMB} = 3.3V$                      | 2.1                        |      | 3.6  |       |

| V <sub>IHSMB</sub>   | SMBus Input High Voltage  | SMBus, $V_{DDSMB} < 3.3V$                      | 0.65<br>V <sub>DDSMB</sub> |      |      | V     |

| 17                   | SMBus Input Low Voltage   | SMBus, V <sub>DDSMB</sub> = 3.3V               |                            |      | 0.6  | V     |

| V <sub>ILSMB</sub>   |                           | SMBus, V <sub>DDSMB</sub> < 3.3V               |                            |      | 0.6  | V     |

| I <sub>SMBSINK</sub> | SMBus sink current        | SMBus, at V <sub>OLSMB</sub>                   | 4                          |      |      | mA    |

| V <sub>OLSMB</sub>   | SMBus Output Low Voltage  | SMBus, at I <sub>SMBSINK</sub>                 |                            |      | 0.4  | V     |

| $f_{MAXSMB}$         | SMBus operating frequency | Maximum frequency                              |                            |      | 400  | kHz   |

| t <sub>RMSB</sub>    | SMBus rise time           | (Max $V_{IL}$ - 0.15) to (Min $V_{IH}$ + 0.15) |                            |      | 1000 | ns    |

| t <sub>FMSB</sub>    | SMBus fall time           | (Min $V_{IH}$ + 0.15) to (Max $V_{IL}$ - 0.15) |                            |      | 300  | ns    |

## **Spread Spectrum Characteristic**

Temperature = T<sub>A</sub>; Supply voltages per normal operation conditions; See test circuits for the load conditions

| Symbol    | Parameters              | Conditions            | Min. | Тур. | Max. | Units |

|-----------|-------------------------|-----------------------|------|------|------|-------|

| $f_{MOD}$ | SS Modulation Frequency | Triangular modulation | 30   | 31.6 | 33   | kHz   |

<sup>1.</sup> ESR value is dependent upon frequency of oscillation

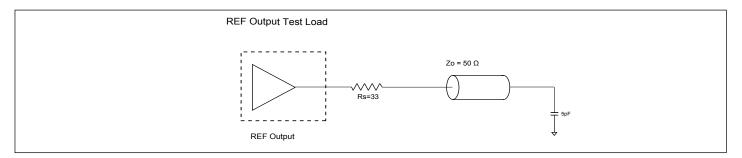

### **LVCMOS DC Electrical Characteristics**

Temperature = T<sub>A</sub>; Supply voltages per normal operation conditions; See test circuits for the load conditions

| Symbol           | Parameters            | Conditions                                                                         | Min.                     | Тур.           | Max.                    | Units |

|------------------|-----------------------|------------------------------------------------------------------------------------|--------------------------|----------------|-------------------------|-------|

| V <sub>IH</sub>  | Input High Voltage    | Single-ended inputs, except SMBus                                                  | 0.75<br>V <sub>DD</sub>  |                | V <sub>DD</sub><br>+0.3 | V     |

| $V_{IM}$         | Input Mid Voltage     | SS_SEL_TRI                                                                         | 0.4V <sub>DD</sub>       | $0.5V_{ m DD}$ | $0.6V_{\mathrm{DD}}$    | V     |

| $V_{\rm IL}$     | Input Low Voltage     | Single-ended inputs, except SMBus                                                  | -0.3                     |                | 0.25<br>V <sub>DD</sub> | V     |

| I <sub>IH</sub>  | Input High Current    | Single-ended inputs, $V_{IN} = V_{DD}$                                             |                          |                | 20                      | μА    |

| I <sub>IL</sub>  | Input Low Current     | Single-ended inputs, $V_{IN} = 0V$                                                 | -20                      |                |                         | μА    |

| I <sub>IH</sub>  | Input High Current    | Single-ended inputs with pull up / pull down resistor, $V_{\rm IN}$ = $V_{\rm DD}$ |                          |                | 220                     | μА    |

| I <sub>IL</sub>  | Input Low Current     | Single-ended inputs with pull up / pull down resistor, $V_{\rm IN} = 0V$           | -220                     |                |                         | μА    |

| V <sub>OH</sub>  | Output High Voltage   | REFOUT, except SMBus; I <sub>OH</sub> = -2mA                                       | V <sub>DD</sub><br>-0.45 |                |                         | V     |

| V <sub>OL</sub>  | Output Low Voltage    | REFOUT, except SMBus; I <sub>OH</sub> = 2mA                                        |                          |                | 0.45                    | V     |

| R <sub>OUT</sub> | CMOS Output impedance |                                                                                    |                          | 20             |                         | Ω     |

| C <sub>IN</sub>  | Input Capacitance     |                                                                                    | 1.5                      |                | 5                       | pF    |

### **LVCMOS AC Characteristics**

Temperature = T<sub>A</sub>; Supply voltages per normal operation conditions; See test circuits for the load conditions

| Symbol              | Parameters                     | Conditions                                                                            | Min. | Typ. | Max. | Units  |

|---------------------|--------------------------------|---------------------------------------------------------------------------------------|------|------|------|--------|

| f <sub>INPUT</sub>  | Input Frequency                | XTAL_IN/CLK                                                                           | 23   | 25   | 27   | MHz    |

| t <sub>RIN</sub>    | Input rise time                | Single-ended inputs                                                                   |      |      | 5    | ns     |

| t <sub>FIN</sub>    | Input fall time                | Single-ended inputs                                                                   |      |      | 5    | ns     |

| t <sub>STAB</sub>   | Clock stablization             | From Power-Up and after input clock stabilization or de-assertion of PD# to 1st clock |      | 0.6  | 1.8  | ms     |

| t <sub>OELAT</sub>  | Output enable latency          | Q start after OE# assertion Q stop after OE# deassertion                              | 1    |      | 3    | clocks |

| t <sub>PDLAT</sub>  | PD# de-assertion               | Differential outputs enable after PD# deassertion                                     |      |      | 300  | us     |

| t <sub>PERIOD</sub> | REFOUT clock period            | REFOUT, assume input is at 25MHz                                                      |      | 40   |      | ns     |

| $f_{ACC}$           | REFOUT frequency accuracy 1    | REFOUT, long term accuracy to input                                                   |      | 0    |      | ppm    |

|                     |                                | Byte 3 = 1F, 20% to 80% of V <sub>DDREF</sub>                                         |      | 1    | 2.5  | V/ns   |

|                     | REFOUT slew rate <sup>1</sup>  | Byte 3 = 5F, 20% to 80% of V <sub>DDREF</sub>                                         |      | 1.6  | 2.5  | V/ns   |

| $t_{\rm SLEW}$      | KEFOUT SIEW rate               | Byte 3 = 9F, 20% to 80% of V <sub>DDREF</sub>                                         |      | 2.0  | 2.5  | V/ns   |

|                     |                                | Byte 3 = DF, 20% to 80% of V <sub>DDREF</sub>                                         |      | 2.1  | 2.5  | V/ns   |

| $t_{DC}$            | REFOUT Duty Cycle <sup>1</sup> | $V_T = V_{\rm DD}$ /2 V, driven by a Xtal                                             | 45   | 50   | 55   | %      |

### **LVCMOS AC Characteristics (Cont.)**

| Symbol             | Parameters                   | Condition                                         | Min. | Тур. | Max. | Units |

|--------------------|------------------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>DCDIS</sub> | REFOUT Duty Cycle Distortion | $V_T = V_{DD}$ /2 V, driven by an external source | 0    | 2    | 4    | %     |

| t <sub>JITCC</sub> | REFOUT cycle-cycle jitter    | $V_T = V_{DD} / 2 V$ , driven by a Xtal           |      | 20   | 250  | ps    |

| t <sub>JITPH</sub> | REFOUT phase jitter          | 12kHz to 5MHz, RMS, driven by a Xtal              |      | 0.68 | 1.5  | ps    |

| 4                  | Noise floor                  | 1kHz offset, driven by a Xtal                     |      | -130 | -105 | dBc   |

| tJITN              |                              | 10kHz offset to Nyquist, driven by a Xtal         |      | -140 | -120 | dBc   |

#### Note:

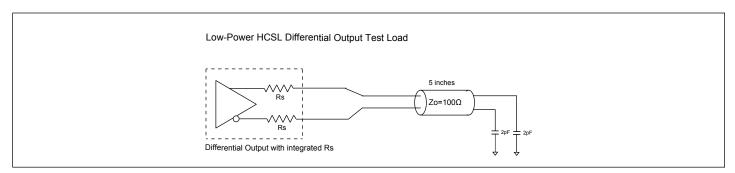

### **HCSL Output Characteristics**

Temperature = T<sub>A</sub>; Supply voltages per normal operation conditions; See test circuits for the load conditions

| Symbol            | Parameters                                        | Condition                                | Min. | Тур. | Max. | Units |

|-------------------|---------------------------------------------------|------------------------------------------|------|------|------|-------|

| V <sub>OH</sub>   | Output Voltage High <sup>1</sup>                  | Statistical measurement on single-ended  | 660  | 784  |      | mV    |

| V <sub>OL</sub>   | Output Voltage Low <sup>1</sup>                   | signal using oscilloscope math function  | -150 |      | 150  | mV    |

| V <sub>OMAX</sub> | Output Voltage Maximum <sup>1</sup>               | Measurement on single ended signal using |      | 816  | 1150 | mV    |

| V <sub>OMIN</sub> | Output Voltage Minimum <sup>1</sup>               | absolute value                           | -300 | -15  |      | mV    |

| Voswing           | Output Swing Voltage 1,2,3                        | Scope averaging off                      | 300  | 1551 |      | mV    |

| V <sub>OC</sub>   | Output Cross Voltage 1,2,4                        |                                          | 250  | 400  | 550  | mV    |

| DV <sub>OC</sub>  | V <sub>OC</sub> Magnitude Change <sup>1,2,5</sup> |                                          |      | 14   | 140  | mV    |

#### Note:

- 1. At default SMBUS amplitude settings

- 2. Guaranteed by design and characterization, not 100% tested in production

- 3. Measured from differential waveform

- 4. This one is defined as voltage where Q+ = Q- measured on a component test board and only applied to the differential rising edge

- 5. The total variation of all Vcross measurements in any particular system. This is a subset of Vcross\_min/max allowed.

### **HCSL Output AC Characteristics**

Temperature = T<sub>A</sub>; Supply voltages per normal operation conditions; See test circuits for the load conditions

| Symbol               | Parameters                           | Condition                         | Min. | Тур. | Max. | Units |

|----------------------|--------------------------------------|-----------------------------------|------|------|------|-------|

| f <sub>OUT</sub>     | Output Frequency                     |                                   |      | 100  |      | MHz   |

| <b>t</b>             | Slew rate <sup>1,2,3</sup>           | Scope averaging on fast setting   | 2.9  | 3.1  | 5.7  | V/ns  |

| $t_{RF}$             | Siew rate                            | Scope averaging on slow setting   | 1.1  | 2.0  | 3.0  | V/ns  |

| Dt <sub>RF</sub>     | Slew rate matching 1,2,4             | Scope averaging on                |      | 3    |      | %     |

| t <sub>DC</sub>      | Duty Cycle <sup>1,2</sup>            | Measured differentially, PLL Mode | 45   | 50   | 55   | %     |

| t <sub>SKEW</sub>    | Output Skew <sup>1,2</sup>           | Averaging on, $V_T = 50\%$        |      | 34   | 50   | ps    |

| tj <sub>c-c</sub>    | Cycle to cycle jitter <sup>1,2</sup> |                                   |      | 14   | 55   | ps    |

| t <sub>STARTUP</sub> | Start up time                        |                                   |      |      | 10   | ms    |

| t <sub>LOCK</sub>    | PLL lock time                        |                                   |      |      | 20   | ms    |

<sup>1.</sup> Guaranteed by design and characterization, not 100% tested in production

### **HCSL Output AC Characteristics (continued)**

| Symbol              | Parameters                          | Condition                                                                  | Min. | Тур. | Max. | Units |

|---------------------|-------------------------------------|----------------------------------------------------------------------------|------|------|------|-------|

|                     |                                     | PCIe Gen 1                                                                 | 20   | 25   | 86   | ps    |

|                     |                                     | PCIe Gen 2 Low Band, 10kHz < f < 1.5MHz                                    | 0.8  | 0.9  | 3.0  | ps    |

| tj <sub>PHASE</sub> | Integrated phase jitter (RMS) 1,5,6 | PCIe Gen 2 High Band, 1.5MHz < f < Nyquist (50MHz)                         | 1.5  | 1.6  | 3.1  | ps    |

| GPHASE              |                                     | PCIe Gen 3 Common Clock Architecture (PLL BW of 2-4 or 2-5MHz, CDR =10MHz) | 0.4  | 0.5  | 1.0  | ps    |

|                     |                                     | PCIe Gen 4 (PLL BW of 2-4 or 2-5MHz,<br>CDR =10MHz)                        | 0.25 | 0.3  | 0.5  | ps    |

#### Note:

- 1. Guaranteed by design and characterization, not 100% tested in production

- 2. Measured from differential waveform

- $3. \ Slew\ rate\ is\ measured\ through\ the\ Vswing\ voltage\ range\ centered\ around\ differential\ 0V,\ within\ +/-150mV\ window$

- 4. It is measured using a +/-75mV window centered on the average cross point

- 5. See http://www.pcisig.com for complete specs

- 6. Sample size of at least 100k cycles. This can be extrapolated to 108ps pk-pk @ 1M cycles for a BER of  $10^{-12}\,$

# Differential Output Clock Periods - Spread Spectrum Disabled 1, 2

|              |                              |                                 | Meas                           | surement Wir               | ıdow                          |                                 |                              |       |

|--------------|------------------------------|---------------------------------|--------------------------------|----------------------------|-------------------------------|---------------------------------|------------------------------|-------|

| Center       | 1 clock                      | 1 us                            | 0.1 s                          | 0.1 s                      | 0.1 s                         | 1 us                            | 1 clock                      |       |

| Freq.<br>MHz | -c2c jitter<br>AbsPer<br>Min | - SSC<br>Short-term<br>Avg. Min | -ppm Long-<br>term Avg.<br>min | 0 ppm<br>Period<br>Nominal | +ppm<br>Long-term<br>Avg. max | + SSC<br>Short-term<br>Avg. Max | -c2c jitter<br>AbsPer<br>Max | Units |

| 100.00       | 9.94900                      |                                 | 9.99900                        | 10.00000                   | 10.00100                      |                                 | 10.05100                     | ns    |

# Differential Output Clock Periods - Spread Spectrum Enabled <sup>1, 2</sup>

|              |                              |                                 | Mea                            | surement Wir               | ndow                          |                                 |                              |       |

|--------------|------------------------------|---------------------------------|--------------------------------|----------------------------|-------------------------------|---------------------------------|------------------------------|-------|

| Center       | 1 clock                      | 1 us                            | 0.1 s                          | 0.1 s                      | 0.1 s                         | 1 us                            | 1 clock                      |       |

| Freq.<br>MHz | -c2c jitter<br>AbsPer<br>Min | - SSC<br>Short-term<br>Avg. Min | -ppm Long-<br>term Avg.<br>min | 0 ppm<br>Period<br>Nominal | +ppm<br>Long-term<br>Avg. max | + SSC<br>Short-term<br>Avg. Max | -c2c jitter<br>AbsPer<br>Max | Units |

| 99.75        | 9.94906                      | 9.99906                         | 10.02406                       | 10.02506                   | 10.02607                      | 10.05107                        | 10.10107                     | ns    |

#### Note:

- 1. Guaranteed by design and characterization, not 100% tested in production

- 2. All long term accuracy and clock period specifications are guaranteed assuming REF is trimmed to 25.00MHz

### **SMBus Serial Data Interface**

PI6CG18201 is a slave only device that supports block read and block write protocol using a single 7-bit address and read/write bit as shown below.

Read and write block transfers can be stopped after any complete byte transfer.

### **Address Assignment**

| A6 | A5 | A4 | A3 | A2 | A1   | A0 | R/W |

|----|----|----|----|----|------|----|-----|

| 1  | 1  | 0  | 1  | 0  | SADR | 0  | 1/0 |

Note: SMBus address is latched on SADR pin

#### **How to Write**

| 1 bit     | 7 bits | 1 bit | 1 bit | 8 bits                              | 1 bit | 8 bits                 | 1 bit | 8 bits                  | 1 bit | 8 bits                   | 1 bit | 1 bit    |

|-----------|--------|-------|-------|-------------------------------------|-------|------------------------|-------|-------------------------|-------|--------------------------|-------|----------|

| Start bit | Add.   | W(0)  | Ack   | Beginning<br>Byte loca-<br>tion = N | Ack   | Data Byte<br>count = X | Ack   | Beginning Data Byte (N) | Ack   | <br>Data Byte<br>(N+X-1) | Ack   | Stop bit |

### **How to Read**

| 1 bit     | 7 bits  | 1 bit | 1 bit | 8 bits                      | 1 bit | 1 bit               | 7 bits  | 1 bit | 1 bit | 8 bits                 | 1 bit | 8 bits                  | 1 bit |

|-----------|---------|-------|-------|-----------------------------|-------|---------------------|---------|-------|-------|------------------------|-------|-------------------------|-------|

| Start bit | Address | W(0)  | Ack   | Beginning Byte location = N | Ack   | Repeat<br>Start bit | Address | R(1)  | Ack   | Data Byte<br>count = X | Ack   | Beginning Data Byte (N) | Ack   |

| 8 bits    | 1 bit | 1 bit    |

|-----------|-------|----------|

| Data Byte | NAck  | Stop bit |

| (N+X-1)   | IVACK | Stop bit |

# Byte 0: Output Enable Register <sup>1</sup>

| Bit | <b>Control Function</b> | Description      | Туре | Power Up<br>Condition | 0       | 1       |

|-----|-------------------------|------------------|------|-----------------------|---------|---------|

| 7   | Reserved                |                  |      | 1                     |         |         |

| 6   | Reserved                |                  |      | 1                     |         |         |

| 5   | Reserved                |                  |      | 1                     |         |         |

| 4   | Reserved                |                  |      | 1                     |         |         |

| 3   | Reserved                |                  |      | 1                     |         |         |

| 2   | Q1_OE                   | Q1 output enable | RW   | 1                     | Low/Low | Enabled |

| 1   | Q0_OE                   | Q0 output enable | RW   | 1                     | Low/Low | Enabled |

| 0   | Reserved                |                  |      | 1                     |         |         |

#### Note:

## Byte 1: SS Readback and Control Register

| Bit | Control Function | Description               | Type            | Power Up<br>Condition | 0                                         | 1                                         |

|-----|------------------|---------------------------|-----------------|-----------------------|-------------------------------------------|-------------------------------------------|

| 7   | SSENRB1          | SS Enable Readback Bit1   | R               | Latch                 | '00' for SS_SEL_                          | _TRI = '0',                               |

| 6   | SSENRB0          | SS Enable Readback Bit0   | R               | Latch                 | '01' for SS_SEL_<br>'11' for SS_SEL_      | ,                                         |

| 5   | SSEN_SWCTR       | Enable SW control of SS   | RW              | 0                     | Values in<br>B1[7:6] control<br>SS amount | Values in<br>B1[4:3] control<br>SS amount |

| 4   | SSENSW1          | SS enable SW control Bit1 | RW <sup>1</sup> | 0                     | '00' = SS off, '01                        | ' = -0.25% SS,                            |

| 3   | SSENSW0          | SS enable SW control Bit0 | RW <sup>1</sup> | 0                     | '10' = Reserved,                          | '11' = -0.5% SS                           |

| 2   | Reserved         |                           |                 | 1                     |                                           |                                           |

| 1   | Amplitude1       | Control output applitude  | RW              | 1                     | '00' = 0.6V, '01' =                       | = 0.7V, '10' =                            |

| 0   | Amplitude0       | Control output applitude  | RW              | 0                     | 0.8V, '11' = 0.9V                         |                                           |

#### Note:

$1.\ B1[5]$  must be set to a 1 for these bits to have any effect on the part.

11

<sup>1.</sup> A low on these bits will override the OE# pins and force the differential outputs to Low/Low states

## Byte 2: Differential Output Slew Rate Control Register

| Bit | Control Function | Description             | Туре | Power Up<br>Condition | 0            | 1            |

|-----|------------------|-------------------------|------|-----------------------|--------------|--------------|

| 7   | Reserved         |                         |      | 1                     |              |              |

| 6   | Reserved         |                         |      | 1                     |              |              |

| 5   | Reserved         |                         |      | 1                     |              |              |

| 4   | Reserved         |                         |      | 1                     |              |              |

| 3   | Reserved         |                         |      | 1                     |              |              |

| 2   | SLEWRATECTR_Q1   | Control slew rate of Q1 | RW   | 1                     | Slow setting | Fast setting |

| 1   | SLEWRATECTR_Q0   | Control slew rate of Q0 | RW   | 1                     | Slow setting | Fast setting |

| 0   | Reserved         |                         |      | 1                     |              |              |

# **Byte 3: REF Control Register**

| Bit | Control Function | Description                | Туре | Power Up<br>Condition | 0                  | 1                  |

|-----|------------------|----------------------------|------|-----------------------|--------------------|--------------------|

| 7   | DEEGI EMIDATE    | Slew rate control for REF  | RW   | 0                     | '00' = 0.9V/ns '0  | 1' = 1.3V/ns,      |

| 6   | REFSLEWRATE      | Siew rate control for REF  | RW   | 1                     | '10' = 1.6V/ns, '1 | 1' = 1.8V/ns       |

| 5   | REF_PDSTATE      | Wake-on-Lan enable for REF | RW   | 0                     | REF = 'Low'        | REF = run-<br>ning |

| 4   | REF_OE           | Output enable for REF      | RW   | 1                     | REF = "Low'        | REF = run-<br>ning |

| 3   | Reserved         |                            |      | 1                     |                    |                    |

| 2   | Reserved         |                            |      | 1                     |                    |                    |

| 1   | Reserved         |                            |      | 1                     |                    |                    |

| 0   | Reserved         |                            |      | 1                     |                    |                    |

## **Byte 4: Reserved**

| Bit | Control Function | Description | Туре | Power Up<br>Condition | 0 | 1 |

|-----|------------------|-------------|------|-----------------------|---|---|

| 7:0 | Reserved         |             |      | 1                     |   |   |

## Byte 5: Revision and Vendor ID Register

| Bit | Control Function | Description  | Туре | Power Up<br>Condition | 0             | 1 |

|-----|------------------|--------------|------|-----------------------|---------------|---|

| 7   | RID3             |              | R    | 0                     | rev = 0000    |   |

| 6   | RID2             | n · · · · ID | R    | 0                     |               |   |

| 5   | RID1             | Revision ID  | R    | 0                     |               |   |

| 4   | RID0             |              | R    | 0                     |               |   |

| 3   | PVID3            | Vendor ID    | R    | 0                     |               |   |

| 2   | PVID3            |              | R    | 0                     | Diodes = 0011 |   |

| 1   | PVID3            |              | R    | 1                     | Diodes = 0011 |   |

| 0   | PVID3            |              | R    | 1                     |               |   |

## Byte 6: Device Type/Device ID Register

| Bit | Control Function | Description | Туре | Power Up<br>Condition | 0                          | 1     |

|-----|------------------|-------------|------|-----------------------|----------------------------|-------|

| 7   | DTYPE1           | Desire town | R    | 0                     | '00' = CG, '01' =          | ZDB,  |

| 6   | DTYPE0           | Device type | R    | 0                     | '10' = Reserve, '11' = ZDB |       |

| 5   | DID5             |             | R    | 0                     |                            |       |

| 4   | DID4             |             | R    | 0                     |                            |       |

| 3   | DID3             | Device ID   | R    | 0                     | 000010 binany              | 02How |

| 2   | DID2             | Device ID   | R    | 0                     | 000010 binary, 02Hex       |       |

| 1   | DID1             |             | R    | 1                     |                            |       |

| 0   | DID0             |             | R    | 0                     |                            |       |

## **Byte 7: Byte Count Register**

| Bit | Control Function | Description            | Туре | Power Up<br>Condition | 0                | 1                 |

|-----|------------------|------------------------|------|-----------------------|------------------|-------------------|

| 7   | Reserved         |                        |      | 0                     |                  |                   |

| 6   | Reserved         |                        |      | 0                     |                  |                   |

| 5   | Reserved         |                        |      | 0                     |                  |                   |

| 4   | BC4              |                        | RW   | 0                     |                  |                   |

| 3   | BC3              |                        | RW   | 1                     | Writing to this  | register will     |

| 2   | BC2              | Byte count programming | RW   | 0                     | configure how    | many bytes will   |

| 1   | BC1              |                        | RW   | 0                     | be read back, do | efault is 8 bytes |

| 0   | BC0              |                        | RW   | 0                     |                  |                   |

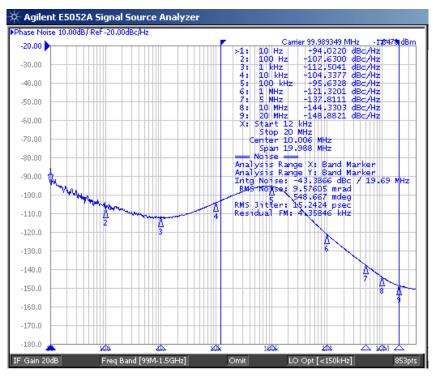

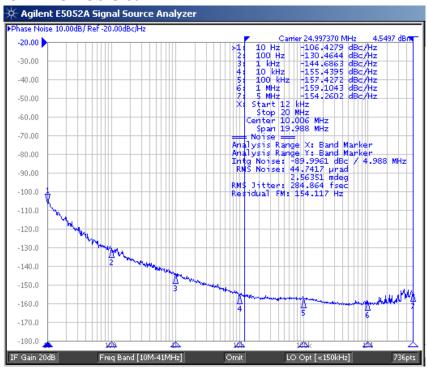

### Plots 100MHz HCSL Clock

#### 25MHz CMOS Clock

14

Figure 1. Low Power HCSL Test Circuit

Figure 2. CMOS REF Test Circuit

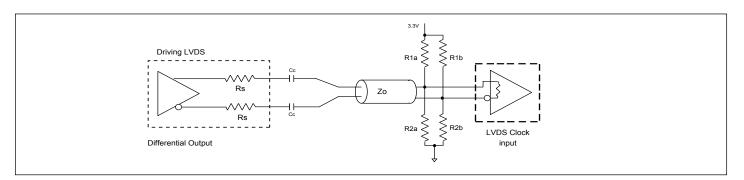

Figure 3. Differential Output driving LVDS

# **Alternate Differential Output Terminations**

| Component                         | Receiver with termination | Receiver without termination | Unit |

|-----------------------------------|---------------------------|------------------------------|------|

| R <sub>1a</sub> , R <sub>1b</sub> | 10,000                    | 140                          | Ω    |

| $R_{2a}, R_{2b}$                  | 5,600                     | 75                           | Ω    |

| C <sub>C</sub>                    | 0.1                       | 0.1                          | μF   |

| $V_{CM}$                          | 1.2                       | 1.2                          | V    |

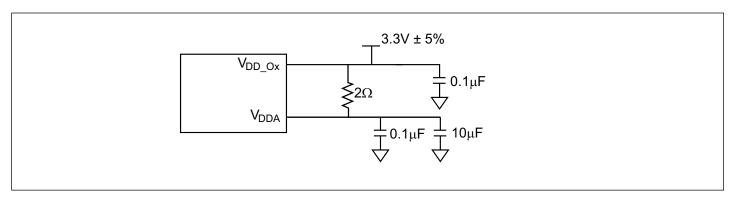

Figure 4. Power Supply Filter

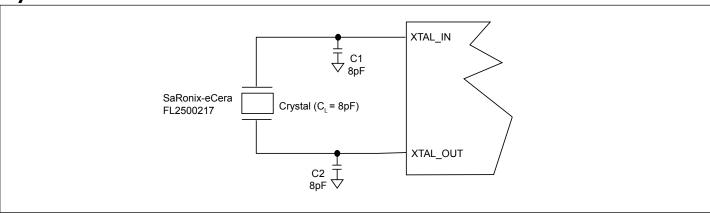

## **Crystal circuit connection**

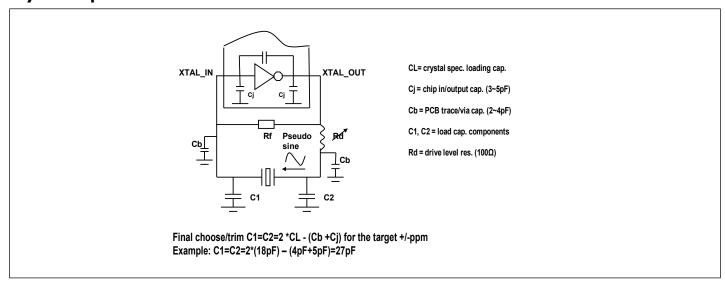

The following diagram shows PI6CG18201 crystal circuit connection with a parallel crystal. For the CL=8pF crystal, it is suggested to use C1=8pF, C2=8pF. C1 and C2 can be adjusted to fine tune to the target ppm of crystal oscillator according to different board layouts based on the following formular in the Crystal Capacitor Calculation diagram.

### **Crystal Oscillator Circuit**

### **Crystal Capacitor Calculation**

## **Recommended Crystal Specification**

#### **Diodes recommends:**

a) FL2500217, SMD 3.2x2.5(4P), 25MHz, CL=8pF, +/-20ppm, https://www.diodes.com/assets/Datasheets/FL.pdf

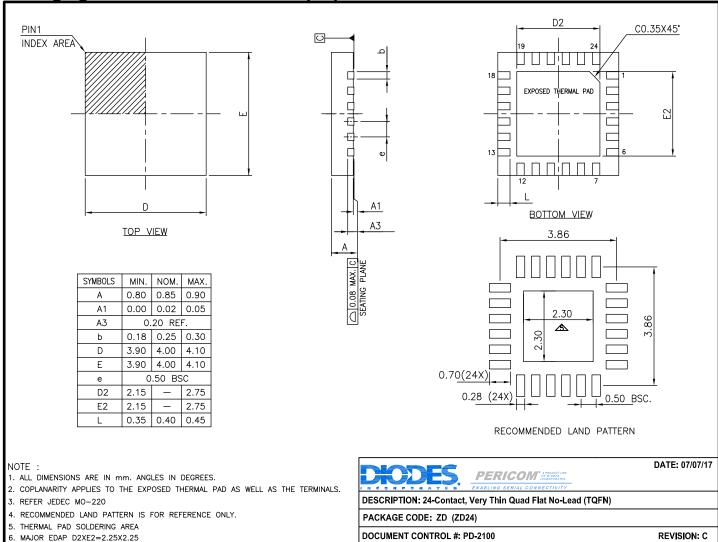

Packaging Mechanical: 24-Pin TQFN (ZD)

17-0533

$Note: For \ latest \ package \ info, \ please \ check: \ https://www.diodes.com/design/support/packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packaging/pericom-packa$

# Ordering Information<sup>(1-3)</sup>

| Ordering Code   | Package Code | Package Description                                               | Operating Temperature |

|-----------------|--------------|-------------------------------------------------------------------|-----------------------|

| PI6CG18201ZDIE  | ZD           | 24-contact, Thin Fine Pitch Quad Flat No-Lead (TQFN)              | Industrial            |

| PI6CG18201ZDIEX | ZD           | 24-contact, Thin Fine Pitch Quad Flat No-Lead (TQFN), Tape & Reel | Industrial            |

18

#### Notes

- 1. Thermal characteristics can be found on the company web site at https://www.diodes.com/design/support/packaging/pericom-packaging/

- 2. E = Pb-free and Green

- 3. Adding an X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com