# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# TCM2913, TCM2914, TCM2916, TCM2917 COMBINED SINGLE-CHIP PCM CODEC AND FILTER

D2765, SEPTEMBER 1983-REVISED JUNE 1988

11 CLKR/CLKX

#### NOT RECOMMENDED FOR NEW DESIGN

For New Design, Refer to TCM29C13, TCM29C14, TCM29C16, and TCM29C17

#### **FEATURE TABLE**

| FEATURE                  | 2913 | 2914 | 2916 | 2917 |

|--------------------------|------|------|------|------|

| Number of Pins:          |      |      |      |      |

| 24                       |      | X    |      |      |

| 20                       | Х    |      |      |      |

| 16                       |      |      | ×    | x    |

| μ-law/A-law Coding:      |      |      |      |      |

| μ-law                    | ×    | X    | ×    |      |

| A-law                    | x    | X    |      | х    |

| Data Timing Rates:       |      |      |      |      |

| Variable Mode            |      |      |      |      |

| 64 kHz to 2.048 MHz      | ×    | X    | ×    | X    |

| Fixed Mode               |      |      |      |      |

| 1.536 MHz                | X    | X    |      |      |

| 1.544 MHz                | X    | X    |      |      |

| 2.048 MHz                | X    | X    | ×    | x    |

| Loopback Test Capability |      | X    |      |      |

| 8th-Bit Signaling        |      | х    |      |      |

### description

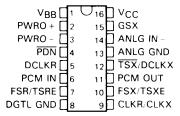

The TCM2913, TCM2914, TCM2916, and TCM2917 are single-chip pulse-code-modulated encoders and decoders (PCM codecs) and PCM line filters. These devices provide all the functions required to interface a full-duplex (4-wire) voice telephone circuit with a time-division-multiplexed (TDM) system. These

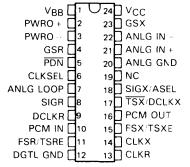

#### J PACKAGE (TOP VIEW) U20∏ V<sub>CC</sub> ∨<sub>BB</sub> ∏₁ PWRO + ∏2 19 GSX PWRO - [ 18 ANLG IN --GSR 14 17 ANLG IN + PDN | 5 16 ANLG GND CLKSEL T6 15 ASEL DCLKR [ 14 TSX/DCLKX PCM IN 8 13 PCM OUT FSR/TSRE ∏9 12 FSX/TSXE

TCM2913

### TCM2914 JW PACKAGE (TOP VIEW)

DGTL GND ☐10

### TCM2916, TCM2917 J PACKAGE (TOP VIEW)

Caution. These devices have limited built-in gate protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Texas Instruments

### description (continued)

devices are intended to replace the TCM2910A in tandem with the TCM2912C. Primary applications of the devices include:

- Line Interface for Digital Transmission and Switching of T1 Carrier, PABX, and Central Office Telephone Systems

- Subscriber Line Concentrators

- Digital Encryption Systems

- Digital Voice Band Data Storage Systems

- Digital Signal Processing

These devices are designed to perform the transmit encoding (A/D conversion) and receive decoding (D/A conversion) as well as the transmit and receive filtering functions in a pulse-code-modulated system. They are intended to be used at the analog termination of a PCM line or trunk.

The TCM2913, TCM2914, TCM2916, and TCM2917 provide the bandpass filtering of the analog signals prior to encoding and after decoding. These combination devices perform the encoding and decoding of voice and call progress tones as well as the signaling and supervision information.

The TCM2913, TCM2914, TCM2916, and TCM2917 are characterized for operation from 0°C to 70°C.

The TCM2913-3 version is identical to the standard version except that maximum encoder milliwatt response and digital milliwatt response are  $\pm 0.40$  dBm0.

### functional block diagram

# TCM2913, TCM2914, TCM2916, TCM2917 COMBINED SINGLE-CHIP PCM CODEC AND FILTER

|         | PIN     |                    |                 |                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|---------|--------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCM2913 | TCM2914 | TCM2916<br>TCM2917 | NAME            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

| 1       | 1       | 1                  | V <sub>BB</sub> | Most negative supply voltage; input is $-5 \text{ V } \pm 5\%$ .                                                                                                                                                                                                                                                                                                                                 |

| 2       | 2       | 2                  | PWRO+           | Noninverting output of power amplifier. Can drive transformer hybrids or high-impedance loads directly in either a differential or a single-ended configuration.                                                                                                                                                                                                                                 |

| 3       | 3       | 3                  | PWRO -          | Inverting output of power amplifier; functionally identical with and complementary to $\mbox{PWRO}+$ .                                                                                                                                                                                                                                                                                           |

| 4       | 4       |                    | GSR             | Input to the gain-setting network on the output power amplifier.  Transmission level can be adjusted over a 12-dB range depending upon the voltage at GSR.                                                                                                                                                                                                                                       |

| 5       | 5       | 4                  | PDN             | Power-down select. The device is inactive with a TTL low-level input to this pin and active with a TTL high-level input to the pin.                                                                                                                                                                                                                                                              |

| 6       | 6       |                    | CLKSEL          | Clock frequency selection. Input must be connected to $V_{BB}$ , $V_{CC}$ , or ground to reflect the master clock frequency. When tied to $V_{BB}$ , CLK is 2.048 MHz. When tied to ground, CLK is 1.544 MHz. When tied to $V_{CC}$ . CLK is 1.536 MHz.                                                                                                                                          |

|         | 7       |                    | ANLG LOOP       | Provides loopback test capability. When this input is TTL high, PWRO $\pm$ is internally connected to ANLG IN.                                                                                                                                                                                                                                                                                   |

|         | 8       |                    | SIGR            | Signaling bit output, receive channel; in a fixed-data-rate mode, outputs the logical state of the 8th bit (LSB) of the PCM word in the most recent signaling frame.                                                                                                                                                                                                                             |

| 7       | 9       | 5                  | DCLKR           | Selects fixed or variable data-rate operation. When this pin is connected to VBB, the device operates in the fixed-data-rate mode. When DCLKR is not connected to VBB, the device operates in the variable-data-rate mode, and DCLKR becomes the receive data clock, which operates at frequencies from 64 kHz to 2.048 MHz.                                                                     |

| 8       | 10      | 6                  | PCM IN          | Receive PCM input. PCM data is clocked in on this pin on eight consecutive negative transitions of the receive data clock, which is CLKR in fixed-data-rate timing and DCLKR in variable-data-rate timing.                                                                                                                                                                                       |

| 9       | 11      | 7                  | FSR/TSRE        | Frame synchronization clock input/time slot enable for receive channel. In the fixed-data-rate mode, FSR distinguishes between signaling and non-signaling frames by a double- or single-length pulse, respectively. In the variable-data-rate mode, this signal must remain high for the duration of the timeslot. The receive channel enters the standby state when FSR is TTL low for 300 ms. |

| 10      | 12      | 8                  | DGTL GND        | Digital ground for all internal logic circuits. Not internally connected to ANLG GND.                                                                                                                                                                                                                                                                                                            |

| 11      | 13      | 9                  | CLKR            | Receive master clock and data clock for the fixed-data-rate mode. Receive master clock only for variable-data-rate mode. CLKR and CLKX are internally connected together for TCM2913, TCM2916, and TCM2917.                                                                                                                                                                                      |

# TCM2913, TCM2914, TCM2916, TCM2917 COMBINED SINGLE-CHIP PCM CODEC AND FILTER

|          | PIN       |         |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----------|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T0140045 | T014004 : | TCM2916 | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TCM2913  | TCM2914   | TCM2917 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11       | 14        | 9       | CLKX      | Transmit master clock and data clock for the fixed-data-rate mode. Transmit master clock only for variable data rate mode. CLKR and CLKX are internally connected for the TCM2913, TCM2916, and TCM2917.                                                                                                                                                                                                                                                                                 |

| 12       | 15        | 10      | FSX/TSXE  | Frame synchronization clock input/time-slot enable for transmit channel.  Operates independently of, but in an analagous manner to, FSR/TSRE.  The transmit channel enters the standby state when FSX is TTL low for 300 ms.                                                                                                                                                                                                                                                             |

| 13       | 16        | 11      | PCM OUT   | Transmit PCM output. PCM data is clocked out on this output on eight consecutive positive transitions of the transmit data clock, which is CLKX in fixed-data-rate timing and DCLKX in variable-data-rate timing.                                                                                                                                                                                                                                                                        |

| 14       | 17        | 12      | TSX/DCLKX | Transmit channel time slot strobe (output) or data clock (input) for the transmit channel. In the fixed-data-rate mode, this pin is an open-drain output to be used as an enable signal for a three-state buffer. In the variable-data rate mode, DCLKX becomes the transmit data clock, which operates at TTL levels from 64 kHz to 2.048 MHz.                                                                                                                                          |

| 15       | 18        |         | SIGX/ASEL | Used to select between A-law and $\mu$ -law operation. When connected to V <sub>BB</sub> , A-law is selected. When connected to V <sub>CC</sub> or ground, $\mu$ -law is selected. When not connected to V <sub>BB</sub> , it is a TTL-level input that is transmitted as the eighth bit (LSB) of the PCM word during signaling frames on the PCM OUT pin (TCM2914 only). SIGX/ASEL is internally connected to provide $\mu$ -law operation for TCM2916 and A-law operation for TCM2917. |

| 16       | 20        | 13      | ANLG GND  | Analog ground return for all internal voice circuits. Not internally connected to DGTL GND.                                                                                                                                                                                                                                                                                                                                                                                              |

| 17       | 21        |         | ANLG IN+  | Noninverting analog input to uncommitted transmit operational amplifier. Internally connected to ANLG GND on TCM2916 and TCM2917.                                                                                                                                                                                                                                                                                                                                                        |

| 18       | 22        | 14      | ANLG IN - | Inverting analog input to uncommitted transmit operational amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19       | 23        | 15      | GSX       | Output terminal of internal uncommitted operational amplifier. Internally, this is the voice signal input to the transmit filter.                                                                                                                                                                                                                                                                                                                                                        |

| 20       | 24        | 16      | Vcc       | Most positive supply voltage; input is 5 V ± 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                                              | -0.3 V to 15 V   |

|-------------------------------------------------------------------------------|------------------|

| Output voltage, VO                                                            |                  |

|                                                                               |                  |

| Input voltage, V <sub>I</sub>                                                 | -0.3 V to 15 V   |

| Digital ground voltage                                                        | -0.3~V to 15 $V$ |

| Continuous total dissipation at (or below) 25 °C free-air temperature         | See Dissipation  |

| Commission total dissipation at (or below, 25 % not an temperature            | Rating Table     |

| Operating free-air temperature range (under bias)                             | -10°C to 80°C    |

| Storage temperature range                                                     | -65°C to 150°C   |

| Lead temperature 1.6 mm (1/16 inch) from case for 60 seconds: J or JW package | 300°C            |

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING<br>FACTOR | DERATE<br>ABOVE T <sub>A</sub> | TA = 80°C<br>POWER RATING |

|---------|---------------------------------------|--------------------|--------------------------------|---------------------------|

| J       | 1375 mW                               | 11.0 mW/°C         | 25 °C                          | 770 mW                    |

| JW      | 1375 mW                               | no derating        |                                | 1375 mW                   |

NOTE 1: Voltage values for maximum ratings are with respect to VBB.

# recommended operating conditions

|                 |                                                    |                          | MIN                  | NOM | MAX       | UNIT |

|-----------------|----------------------------------------------------|--------------------------|----------------------|-----|-----------|------|

| VCC             | Supply voltage (see Not                            | te 2)                    | 4.75                 | 5   | 5.25      | V    |

| V <sub>BB</sub> | Supply voltage                                     |                          | -4.75                | - 5 | - 5.25    | V    |

|                 | DGTL GND voltage with                              | respect to ANLG GND      |                      | 0   |           | V    |

| VIH             | High-level input voltage, all inputs except CLKSEL |                          | 2.2                  |     |           | V    |

| VIL             | Low-level input voltage,                           | all inputs except CLKSEL |                      |     | 0.8       | V    |

|                 | Clark and an                                       | For 2.048 MHz            | V <sub>BB</sub>      |     | VBB + 0.5 |      |

|                 | Clock select<br>input voltage                      | For 1.544 MHz            | 0                    |     | 0.5       | V    |

|                 |                                                    | For 1.536 MHz            | V <sub>CC</sub> -0.5 |     | Vcc       |      |

|                 |                                                    | At GSX                   | 10                   |     |           | kΩ   |

| RL              | Load resistance                                    | At PWRO + and/or PWRO -  | 300                  |     |           | Ω    |

| _               | L Load capacitance                                 | At GSX                   |                      |     | 50        |      |

| CL              |                                                    | At PWRO + and/or PWRO -  |                      |     | 100       | pF   |

| TA              | Operating free-air temper                          | erature                  | 0                    |     | 70        | °C   |

NOTE 2: Voltages at analog inputs and outputs, V<sub>CC</sub>, and V<sub>BB</sub> terminals are with respect to the ANLG GND terminal. All other voltages are referenced to the DGTL GND terminal unless otherwise noted.

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature supply current, fDCLK = 2.048 MHz, outputs not loaded

|                 | PARAMETER               |            | TEST CONDITIONS                         | MIN | TYP <sup>†</sup> | MAX  | UNIT |

|-----------------|-------------------------|------------|-----------------------------------------|-----|------------------|------|------|

|                 | Supply current          | Operating  |                                         |     | 14               | 19   |      |

| 1cc             | from VCC                | Standby    | FSX, FSR = V <sub>IL</sub> after 300 ms |     | 1.2              | 2.4  | mA   |

|                 | 110111 ACC              | Power-down | PDN = V <sub>IL</sub> after 10 μs       |     | 0.5              | 1    |      |

|                 | Supply current from VBB | Operating  |                                         |     | - 18             | - 24 |      |

| 1 <sub>BB</sub> |                         | Standby    | FSX, FSR = V <sub>IL</sub> after 300 ms |     | - 1.2            | -2.4 | mA   |

|                 |                         | Power-down | PDN = V <sub>IL</sub> after 10 μs       |     | -0.5             | - 1  |      |

|                 |                         | Operating  |                                         |     | 140              | 226  |      |

|                 | Power dissipation       | Standby    | FSX, FSR = V <sub>IL</sub> after 300 ms |     | 12               | 25   | mW   |

|                 |                         | Power down | PDN = V <sub>IL</sub> after 10 μs       |     | 5                | 10.5 |      |

### digital interface

|     | PARAMETER                                      |         | TEST CONDITIONS                 | MIN | TYP <sup>†</sup> | MAX | UNIT |

|-----|------------------------------------------------|---------|---------------------------------|-----|------------------|-----|------|

|     | High level extense veltege                     | PCM OUT | I <sub>OH</sub> = -9.6 mA       | 2.4 |                  |     | V    |

| ∨он | VOH High-level output voltage                  | SIGR    | I <sub>OH</sub> = -1.2 mA       | 2.4 |                  |     | V    |

| VOL | Low-level output voltage at PCM OUT, TSX, SIGR |         | IOL = 3.2 mA                    |     |                  | 0.4 | ٧    |

| ΙΗ  | High-level input current, any digital input    |         | $V_1 = 2.2 \text{ V to V}_{CC}$ |     |                  | 10  | μΑ   |

| IIL | Low-level input current, any digital input     |         | V <sub>I</sub> = 0 to 0.8 V     |     |                  | 10  | μΑ   |

| Ci  | C <sub>i</sub> Input capacitance               |         | •                               |     | 5                | 10  | pF   |

| Co  | Output capacitance                             |         |                                 |     | 5                |     | pF   |

# transmit amplifier input

| PARAMETER                                   | TEST CONDITIONS                              | MIN  | TYP <sup>†</sup> | MAX   | UNIT |

|---------------------------------------------|----------------------------------------------|------|------------------|-------|------|

| Input current at ANLG IN+, ANLG IN-         | $V_{j} = -2.17 \text{ V to } 2.17 \text{ V}$ |      |                  | ± 100 | nA   |

| Input offset voltage at ANLG IN+, ANLG IN-  | $V_{i} = -2.17 \text{ V to } 2.17 \text{ V}$ |      |                  | ± 25  | mV   |

| Common-mode rejection at ANLG IN+, ANLG IN- | $V_1 = -2.17 \text{ V to } 2.17 \text{ V}$   | 55   |                  |       | dB   |

| Open-loop voltage amplification at GSX      |                                              | 5000 |                  |       |      |

| Open-loop unity-gain bandwidth at GSX       |                                              |      | 1                |       | MHz  |

| Input resistance at ANLG IN+, ANLG IN-      |                                              | 10   |                  |       | МΩ   |

### receive filter output

| PARAMETER                                            | TEST CONDITIONS      | MIN TYPT MAX | UNIT |

|------------------------------------------------------|----------------------|--------------|------|

| Output offset voltage PWRO + , PWRO - (single-ended) | Relative to ANLG GND | 120          | mV   |

| Output resistance at PWRO + , PWRO -                 |                      | 1            | Ω    |

$<sup>^{\</sup>dagger}AII$  typical values are at VBB = -5 V, VCC = 5 V, and TA = 25 °C.

# gain and dynamic range, VCC = 5 V, VBB = -5 V, TA = 25 °C (unless otherwise noted) (see Notes 3, 4, and 5)

| PARAMETER                                            |                          | TEST CONDITION               | ONS               | MIN TYP | MAX    | UNIT  |

|------------------------------------------------------|--------------------------|------------------------------|-------------------|---------|--------|-------|

| Encoder milliwatt response (transmit gain tolerance) |                          | Simplify 1 064 V mg          | Standard versions | ± 0.08  | ±0.18  | 400   |

|                                                      |                          | Signal input = 1.064 V rms   | TCM2913-3         | ±0.18   | ±0.40  | dBm0  |

| Encoder milliwatt response varia                     | ation with               | $T_A = 0$ °C to 70°C,        |                   |         | . 0.07 | dB    |

| temperature and supplies                             |                          | Supplies = ±5%               |                   |         | ±0.07  | an an |

| Digital milliwatt response (receive                  | ve tolerance gain)       | Signal input per CCITT G.711 | Standard versions | ±0.08   | ±0.18  | 4D0   |

| relative to zero-transmission level point            |                          | Output signal = 1 kHz        | TCM2913-3         | ±0.18   | ±0.40  | dBm0  |

| Digital milliwatt response variation with            |                          | $T_A = 0$ °C to 70°C,        |                   |         | . 0.07 | dB    |

| temperature and supplies                             | temperature and supplies |                              |                   |         | ±0.07  | ab    |

| Zero-transmission-level                              | μ-law                    | $R_1 = 600 \Omega$           |                   | 2.76    |        |       |

|                                                      | A-law                    | HL = 800 11                  |                   | 2.79    |        | dBm   |

| point, transmit channel                              | μ-law                    | B. 900 0                     |                   | 1       |        | abm   |

| (0 dBm0)                                             | A-law                    | $R_L = 900 \Omega$           |                   | 1.03    |        |       |

| 7                                                    | μ-law                    | B 600.0                      |                   | 5.76    | )      |       |

| Zero-transmission-level point, receive channel       | A-law                    | R <sub>L</sub> = 600 Ω       |                   | 5.79    | ·      | 4D    |

|                                                      | μ-law                    | B 900 0                      |                   | 4       |        | dBm   |

| (0 dBm0)                                             | A-law                    | R <sub>L</sub> = 900 Ω       |                   | 4.03    |        |       |

- NOTES: 3. Unless otherwise noted, the analog input is a 0-dBm0, 1020-Hz sine wave, where 0 dBm0 is defined as the zero-reference point of the channel under test. This corresponds to an analog signal input of 1.064 V rms, or an output of 1.503 V rms.

- 4. The input amplifier is set for unity gain. The digital input is a PCM bit stream generated by passing a 0-dBm0, 1020-Hz sine wave through an ideal encoder.

- 5. Receive output is measured single-ended in the maximum-gain configuration. To set the output amplifier for maximum gain, GSR is connected to PWRO - and the output is taken at PWRO +. All output levels are (sin x)/x corrected.

### gain tracking over recommended ranges of supply voltage and operating free-air temperature, reference level = -10 dBm0

| PARAMETER                                      | TEST CONDITIONS     | MIN MAX | UNIT |

|------------------------------------------------|---------------------|---------|------|

|                                                | -3 to -40 dBm0      | ± 0.25  | l    |

| Transmit gain tracking error, sinusoidal input | -40 to -50 dBm0     | ±0.5    | dB   |

|                                                | -50 to −55 dBm0     | ±1.2    | 1    |

|                                                | -3 to -40 dBm0      | ±0.25   |      |

| Receive gain tracking error, sinusoidal input  | -40 to -50 dBm0     | ±0.5    | dB   |

|                                                | , – 50 to – 55 dBm0 | ± 1.2   | 1    |

# noise over recommended ranges of supply voltage and operating free-air temperature

| PARAMETER                                          | TEST CONDITIONS                            | MIN | MAX  | UNIT   |

|----------------------------------------------------|--------------------------------------------|-----|------|--------|

| Transmit noise, C-message weighted                 | ANLG IN + = ANLG GND,                      |     | 15   | dBrnC0 |

| Transmit hoise, C-message weighted                 | ANLG IN - = GSX                            |     |      | abrnco |

| Transmit noise, C-message weighted with eighth-bit | ANLG IN + = ANLG GND,                      |     |      |        |

| signaling (TCM2914 only)                           | $ANLG\ IN-=GSX,$                           |     | 18   | dBrnC0 |

| signaling (TCW2914 Only)                           | 6th frame signaling                        |     |      |        |

| Transmit noise, psophometrically weighted          | $ANLG\ IN + = ANLG\ GND,$                  |     | - 75 | dBm0p  |

| Transmit hoise, psophometrically weighted          | ANLG IN - = GSX                            |     | - /5 | автор  |

|                                                    | PCM IN = 111111111 (μ-law)                 |     |      |        |

| Receive noise, C-message weighted quiet code       | PCM IN = 10101010 (A-law)                  | 11  |      | dBrnC0 |

|                                                    | measured at PWRO +                         |     |      |        |

| Receive noise, C-message weighted sign             | Input to PCM IN is zero code with sign bit | 12  |      | dBrnCO |

| bit toggled                                        | toggled at 1-kHz rate                      |     |      | ubinco |

| Receive noise, psophometrically weighted           | PCM = lowest positive decode level         |     | - 79 | dBm0p  |

# power supply rejection and crosstalk attenuation over recommended ranges of supply voltage and operating free-air temperature

| PARA                                                             | METER                               | TEST CONDITIONS                                                                                        | MIN TYP† MAX | UNIT |

|------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------|--------------|------|

| V <sub>CC</sub> supply voltage rejection ratio, transmit channel | f = 0 to 30 kHz<br>f = 30 to 50 kHz | Idle channel, supply signal = 200 mV p-p, f measured at PCM OUT                                        | - 30<br>- 45 | dB   |

| VBB supply voltage rejection ratio, transmit channel             | f = 0 to 30 kHz<br>f = 30 to 50 kHz | Idle channel, supply signal = 200 mV p-p, f measured at PCM OUT                                        | - 30<br>- 55 | dB   |

| V <sub>CC</sub> supply voltage rejection ratio,                  | f = 0 to 30 kHz                     | ldle channel,<br>supply signal = 200 mV p-p,                                                           | - 20         | dB   |

| receive channel<br>(single-ended)                                | f = 30 to 50 kHz                    | narrow-band, f measured<br>at PWRO +                                                                   | 45           |      |

| VBB supply voltage rejection ratio,                              | f = 0 to 30 kHz                     | ldle channel,<br>supply signal = 200 mV p-p,                                                           | - 20         | dB   |

| receive channel<br>(single-ended)                                | f = 30 to 50 kHz                    | narrow-band, f measured<br>at PWRO +                                                                   | - 45         |      |

| Crosstalk attenuation, transmit-to-receive (single-ended)        |                                     | ANLG IN + = 0 dBm0,<br>f = 1.02 kHz, unity gain,<br>PCM IN = lowest decode level<br>measured at PWRO + | 71           | dB   |

| Crosstalk attenuation, receive-to-transmit (single-ended)        |                                     | PCM IN = 0 dBm0,<br>f = 1.02 kHz,<br>ANLG IN+ = ANLG GND,<br>measured at PCM OUT                       | 71           | dB   |

$<sup>^{\</sup>dagger}$ All typical values are at V<sub>BB</sub> = -5 V, V<sub>CC</sub> = 5 V, and T<sub>A</sub> = 25 °C.

# distortion over recommended ranges of supply voltage and operating free-air temperature

| PARAMETER                                       | TEST CONDITIONS                                | MIN  | TYP <sup>†</sup> | MAX    | UNIT |

|-------------------------------------------------|------------------------------------------------|------|------------------|--------|------|

| Transmit signal to distortion ratio, sinusoidal | ANLG IN + = 0 to -30 dBm0                      | 36   |                  |        |      |

| input (see Note 6)                              | ANLG IN $+ = -30$ to $-40$ dBm0                | 30   |                  |        | dB   |

| input (see Note 6)                              | ANLG IN $+ = -40$ to $-45$ dBm0                | 25   |                  |        |      |

| Receive signal to distortion ratio, sinusoidal  | ANLG IN + = 0 to -30 dBm0                      | 36   |                  |        |      |

| input (see Note 6)                              | ANLG IN $+ = -30$ to $-40$ dBm0                | 30   |                  |        | dB   |

| input (see Note 6)                              | ANLG IN + = -40 to -45 dBm0                    | 25   |                  |        |      |

| Transmit single-frequency distortion products   | AT&T Advisory #64 (3.8), Input signal = 0 dBm0 |      |                  | 46     | dBm0 |

| Receive single-frequency distortion products    | AT&T Advisory #64 (3.8), Input signal = 0 dBm0 |      |                  | 46     | dBm0 |

|                                                 | CCITT G.712 (7.1)                              |      |                  | 35     | dBm0 |

| Intermodulation distortion, end-to-end          | CCITT G.712 (7.2)                              |      |                  | - 49   | авто |

| Spurious out-of-band signals, end-to-end        | CCITT G.712 (6.1)                              |      |                  | 25     | dBm0 |

|                                                 | CCITT G.712 (9)                                | - 40 |                  | dbillo |      |

| Transmit shootists date; time to DCM OLIT       | Fixed data rate, CLKS = 2.048 MHz,             |      | 245              |        |      |

| Transmit absolute delay time to PCM OUT         | Input to ANLG IN + = 1.02 kHz at 0 dBm0        | 245  |                  |        | μS   |

|                                                 | f = 500 Hz to 600 Hz                           |      | 170              |        |      |

| Transmit differential envelope delay time       | f = 600 Hz to 1000 Hz                          |      | 95               |        |      |

| relative to transmit absolute delay time        | f = 1000 Hz to 2600 Hz                         |      | 45               |        | μS   |

|                                                 | f = 2600 Hz to 2800 Hz                         |      | 105              |        |      |

| S                                               | Fixed data rate, fCLKR = 2.048 MHz,            |      | 100              |        |      |

| Receive absolute delay time to PWRO+            | Digital input is DMW codes                     |      | 190              |        | μS   |

|                                                 | f = 500 Hz to 600 Hz                           |      | 45               |        |      |

| Receive differential envelope delay time        | f = 600 Hz to 1000 Hz                          |      | 35               |        | _    |

| relative to transmit absolute delay time        | f = 1000 Hz to 2600 Hz                         |      | 85               |        | μS   |

|                                                 | f = 2600 Hz to 2800 Hz                         |      | 110              |        |      |

$<sup>^{\</sup>dagger}All$  typical values are at VBB = -5 V, VCC = 5 V, and TA = 25 °C. NOTE 6. CCITT G.712 - Method 2.

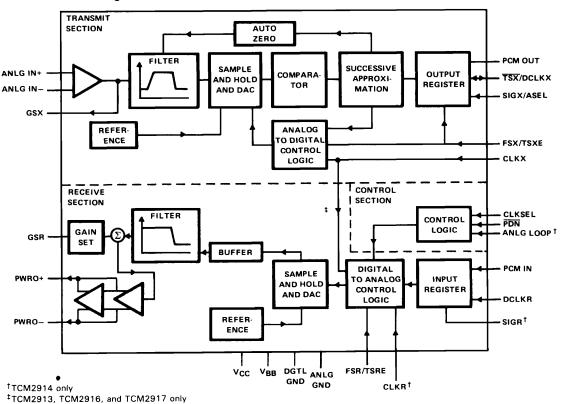

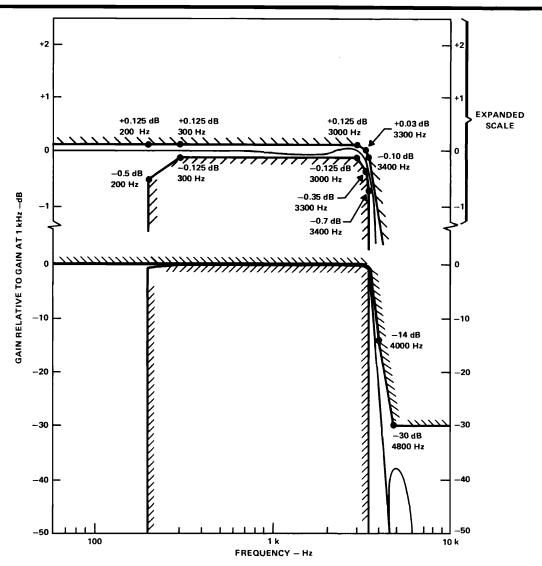

# transmit filter transfer over recommended ranges of supply voltage and operating free-air temperature (see Figure 1)

| PARAMETER             | TEST COND                                     | DITIONS           | MIN    | MAX   | UNIT |

|-----------------------|-----------------------------------------------|-------------------|--------|-------|------|

|                       |                                               | 16.67 Hz          |        | - 30  |      |

|                       |                                               | 50 Hz             |        | - 25  |      |

|                       | Input amplifier set for                       | 60 Hz             |        | - 23  |      |

|                       | unity gain, Noninverting maximum gain output, | 200 Hz            | -1.8   | 0.125 |      |

| Gain relative to gain |                                               | 300 Hz to 3 kHz   | -0.125 | 0.125 | dB   |

| at 1.02 kHz           | Input signal at ANLG IN                       | 3.3 kHz           | -0.35  | 0.03  |      |

|                       | is 0 dBm0                                     | 3.4 kHz           | -0.7   | -0.1  |      |

|                       |                                               | 4 kHz             |        | -14   |      |

|                       |                                               | 4.6 kHz and above |        | - 32  |      |

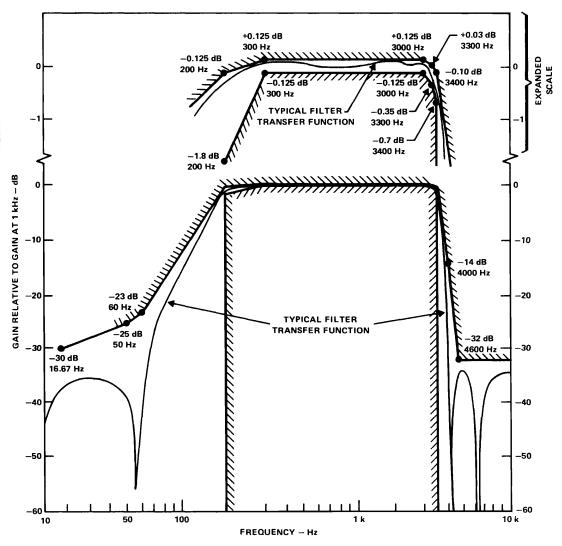

# receive filter transfer over recommended ranges of supply voltage and operating free-air temperature (see Figure 2)

| PARAMETER                         | TEST CONDITIONS                  |                   | MIN    | MAX   | UNIT |

|-----------------------------------|----------------------------------|-------------------|--------|-------|------|

|                                   |                                  | Below 200 Hz      |        | 0.125 |      |

| Gain relative to gain at 1.02 kHz |                                  | 200 Hz            | -0.5   | 0.125 | 1    |

|                                   | Input signal at PCM IN is 0 dBm0 | 300 Hz to 3 kHz   | -0.125 | 0.125 | dB   |

|                                   |                                  | 3.3 kHz           | -0.35  | 0.03  |      |

|                                   |                                  | 3.4 kHz           | -0.7   | - 0.1 | ĺ    |

|                                   |                                  | 4 kHz             |        | -14   | 1    |

|                                   | İ                                | 4.6 kHz and above |        | - 30  | 1    |

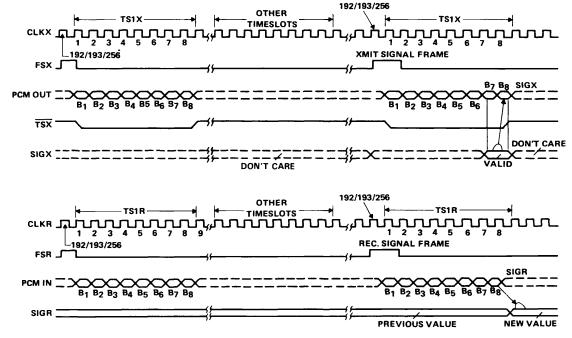

# clock timing requirements over recommended ranges of supply voltage and operating free-air temperature (see timing diagrams)

|                                 | PARAMETER                                                         | MIN | TYP <sup>†</sup> | MAX | UNIT |

|---------------------------------|-------------------------------------------------------------------|-----|------------------|-----|------|

| t <sub>c</sub> (CLK)            | Clock period for CLKX, CLKR (2.048-MHz systems)                   | 488 |                  |     | ns   |

| t <sub>r</sub> , t <sub>f</sub> | Rise and fall times for CLKX and CLKR                             | 5   |                  | 30  | ns   |

| tw(CLK)                         | Pulse duration for CLKX and CLKR (see Note 7)                     | 220 |                  |     | ns   |

| tw(DCLK)                        | Pulse duration for DCLK (fDCLK = 64 Hz to 2.048 MHz) (see Note 8) | 220 |                  |     | ns   |

| <u> </u>                        | Clock duty cycle [tw(CLK)/tc(CLK)] for CLKX and CLKR              | 45  | 50               | 55  | %    |

$<sup>^{\</sup>dagger}$  All typical values are at V<sub>BB</sub> = -5 V, V<sub>CC</sub> = 5 V, and T<sub>A</sub> = 25 °C.

# transmit timing requirements over recommended ranges of supply voltage and operating free-air temperature, fixed-data-rate mode (see timing diagrams)

| l                     | PARAMETER                                           | MIN | MAX                       | UNIT |

|-----------------------|-----------------------------------------------------|-----|---------------------------|------|

| td(FSX)               | Frame sync delay time                               | 100 | t <sub>c(CLK)</sub> - 100 | ns   |

| t <sub>su(SIGX)</sub> | Setup time before Bit 7 falling edge (TCM2914 only) | 0   |                           | ns   |

| th(SIGX)              | Hold time after Bit 8 falling edge (TCM2914 only)   | 0   |                           | ns   |

# propagation delay times over recommended ranges of operating conditions, fixed-data-rate mode (see timing diagrams)

|                  | PARAMETER                                                                                                            | TEST CONDITIONS              | MIN | MAX | UNIT |

|------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|-----|-----|------|

| <sup>t</sup> pd1 | From rising edge of transmit clock to Bit 1 data valid at PCM OUT (data enable time on time slot entry) (see Note 8) | C <sub>L</sub> = 0 to 100 pF | 0   | 145 | ns   |

| t <sub>pd2</sub> | From rising edge of transmit clock Bit n to Bit n + 1 data valid at PCM OUT (data valid time)                        | C <sub>L</sub> = 0 to 100 pF | 0   | 145 | ns   |

| t <sub>pd3</sub> | From falling edge of transmit clock Bit 8 to Bit 8 Hi-Z at PCM OUT (data float time on time slot exit) (see Note 8)  | C <sub>L</sub> = 0           | 60  | 215 | ns   |

| t <sub>pd4</sub> | From rising edge of transmit clock Bit 1 to TSX active (low) (time slot enable time)                                 | C <sub>L</sub> = 0 to 100 pF | 0   | 145 | ns   |

| t <sub>pd5</sub> | From falling edge of transmit clock Bit 8 to TSX inactive (high) (time slot disable time) (see Note 8)               | C <sub>L</sub> = 0           | 60  | 190 | ns   |

| t <sub>pd6</sub> | From rising edge of channel time slot to SIGR update (TCM2914 only)                                                  |                              | 0   | 2   | μς   |

NOTES: 7. FSX CLK must be phase locked with the CLKX, FSR CLK must be phase locked with CLKR.

<sup>8.</sup> Timing parameters  $t_{pd1}$ ,  $t_{pd3}$ , and  $t_{pd5}$  are referenced to the high-impedance state.

# receive timing requirements over recommended ranges of supply voltage and operating free-air temperature, fixed-data-rate mode (see timing diagrams)

|             | PARAMETER                                           | MIN | MAX                       | UNIT |

|-------------|-----------------------------------------------------|-----|---------------------------|------|

| td(FSR)     | Frame sync delay time                               | 100 | t <sub>c(CLK)</sub> - 100 | ns   |

| tsu(PCM IN) | Setup time before Bit 7 falling edge (TCM2914 only) | 10  |                           | ns   |

| th(PCM IN)  | Hold time after Bit 8 falling edge (TCM2914 only)   | 60  |                           | ns   |

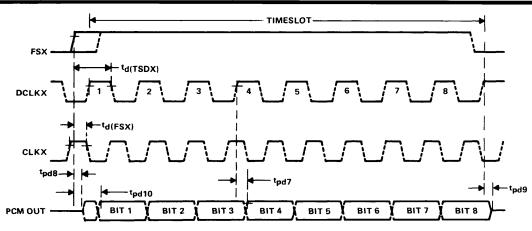

# transmit timing requirements over recommended ranges of supply voltage and operating free-air temperature, variable-data-rate mode (see timing diagrams)

|           | PARAMETER                                   | MIN | MAX                       | UNIT |

|-----------|---------------------------------------------|-----|---------------------------|------|

| td(TSDX)  | Timeslot delay time from DCLKX (see Note 9) | 140 | td(DCLKX) - 140           | ns   |

| td(FSX)   | Frame sync delay time                       | 100 | t <sub>c(CLK)</sub> - 100 | ns   |

| tc(DCLKX) | Clock period for DCLKX                      | 488 | 15620                     | ns   |

# propagation delay times over recommended ranges of operating conditions, variable-data-rate mode (see Note 10 and timing diagrams)

|                  | PARAMETER                                    | TEST CONDITIONS               | MIN | MAX | UNIT |

|------------------|----------------------------------------------|-------------------------------|-----|-----|------|

| tpd7             | Data delay time from DCLKX                   | $C_L = 0$ to 100 pF           | 0   | 100 | ns   |

| t <sub>pd8</sub> | Data delay from timeslot enable to PCM OUT   | $C_L = 0$ to 100 pF           | 0   | 50  | ns   |

| t <sub>pd9</sub> | Data delay from time slot disable to PCM OUT | C <sub>L</sub> = 0 to 100 pF  | 0   | 80  | ns   |

| tpd10            | Data delay time from FSX                     | t <sub>d</sub> (TSDX) = 80 ns | 0   | 140 | ns   |

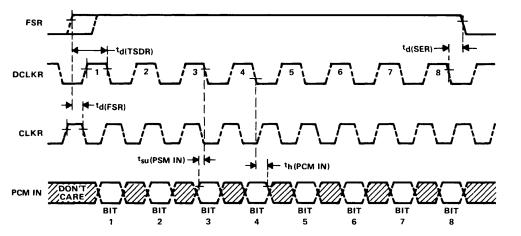

# receive timing requirements over recommended ranges of supply voltage and operating free-air temperature, variable-data-rate mode (see timing diagrams)

|                         | PARAMETER                                    | MI | N MAX                         | UNIT |

|-------------------------|----------------------------------------------|----|-------------------------------|------|

| td(TSDR)                | Timeslot delay time from DCLKR (see Note 11) | 14 | 0 t <sub>d(DCLKR)</sub> - 140 | ns   |

| td(FSR)                 | Frame sync delay time                        | 10 | 0 t <sub>c(CLK)</sub> - 100   | ns   |

| t <sub>su(PCM IN)</sub> | Setup time before Bit 7 falling edge         | 1  | 0                             | ns   |

| th(PCM IN)              | Hold time after Bit 8 falling edge           | 6  | 0                             | ns   |

| t <sub>c</sub> (DCLKR)  | Clock period for DCLKR                       | 48 | 8 15620                       | ns   |

| td(SER)                 | Timeslot end receive time                    |    | 0                             | ns   |

# 64-kilobit operation timing requirements over recommended ranges of supply voltage and operating free-air temperature, variable-data-rate mode

| PARAMETER |                                       | TEST CONDITIONS    | MIN  | MAX | UNIT |

|-----------|---------------------------------------|--------------------|------|-----|------|

| tFSLX     | Transmit frame sync minimum down time | FSX = TTL high for | 488  |     | ns   |

|           |                                       | remainder of frame |      |     |      |

| †FSLR     | Receive frame sync minimum down time  | FSR = TTL high for | 1952 |     | ns   |

|           |                                       | remainder of frame |      |     |      |

| †DCLK     | Pulse duration data clock             |                    |      | 10  | μS   |

NOTES: 9. tFSLX minimum requirement overrides the td(TSDX) maximum requirement for 64-kHz operation.

10. Timing parameters  $t_{\mbox{pd8}}$  and  $t_{\mbox{pd9}}$  are referenced to a high-impedance state.

11. tFSLR minimum requirement overrides the td(TSDR) maximum requirement for 64-kHz operation.

FIGURE 1. TRANSFER CHARACTERISTICS OF THE TRANSMIT FILTER

NOTE: This is a typical transfer function of the receiver filter component.

FIGURE 2. TRANSFER CHARACTERISTIC OF THE RECEIVE FILTER

# INPUT TIMING FIGURE 4. RECEIVE TIMING (FIXED-DATA-RATE)

NOTES: A. Inputs are driven from 0.45 V to 2.4 V. Time intervals are referenced to 2 V if the high level is indicated and 0.8 V if the low level is indicated.

B. BIT 1 = MSB = Sign Bit and is clocked in first on the PCM-IN pin or is clocked out first on the PCM-OUT pin.

BIT 8 = LSB = Least Significant Bit and is clocked in last on the PCM-IN pin or is clocked out last on the PCM-OUT pin.

VALID

VALID

SIGR OUTPUT

FIGURE 5. TRANSMIT TIMING (VARIABLE-DATA-RATE)

NOTES: B. BIT 1 = MSB = Sign Bit and is clocked in first on the PCM-IN or is clocked out first on the PCM-OUT pin. BIT 8 = LSB = Least Significant Bit and is clocked in last on the PCM-PIN or is clocked out last on the PCM-OUT pin.

C. All timing parameters referenced to VIH and VIL except tpd8 and tpd9, which are referenced to a high-impedance state.

FIGURE 6. RECEIVE TIMING (VARIABLE-DATA-RATE)

#### GENERAL OPERATION

### system reliability features

The TCM2913, TCM2914, TCM2916, or TCM2917 is powered up in four steps:

VCC and VBB supply voltages are applied.

All clocks are connected.

TTL high is applied to PDN.

FSX and/or FSR synchronization pulses are applied.

On the transmit channel, digital outputs PCM out and TSX are held in high-impedance state for approximately four frames (500  $\mu$ s) after power up or application of VBB or VCC. After this delay, PCM OUT, TSX, and signaling are functional and will occur in the proper timeslot. The analog circuits on the transmit side require approximately 60 ms to reach their equilibrium value due to the autozero circuit settling time. Thus valid digital information, such as for on/off hook detection, is available almost immediately, while analog information is available after some delay.

On the receive channel, the digital output SIGR is also held low for a maximum of four frames after power up or application of VRB or VCC. SIGR will remain low until it is updated by a signalling frame.

To further enhance system reliability, PCM OUT and  $\overline{TSX}$  will be placed in a high-impedance state approximately 20 µs after an interruption of CLKX. SIGR will be held low approximately 20 µs after an interruption of CLKR. These interruptions could possible occur with some kind of fault condition.

### power-down and standby operations

To minimize power consumption, a power-down mode and three standby modes are provided.

For power down, an external TTL low signal is applied to the PDN pin. It is not sufficient to remove the TTL high voltage to PDN. In the absence of a signal, the PDN pin floats to TTL high and the device remains active. In the power-down mode, the average power consumption is reduced to an average of 5 mW.

The standby modes give the user the option of putting the entire device on standby, putting only the transmit channel on standby, or putting only the receive channel on standby. To place the entire device on standby, both FSX and FSR are held at TTL low. For transmit-only operation, FSX is high and FSR is held low. For receive-only operation, FSR is high and FSX is held low. See Table 1 for power down and standby procedures.

The first TSX pulse that occurs after power-up or removal from standby mode may not be exactly 8 data bits long. In applications that require a valid first TSX, such as Digital Signal Processing, the TCM29C13, TCM29C14, TCM29C16, and TCM29C17 are recommended.

TABLE 1. POWER DOWN AND STANDBY PROCEDURES

| DEVICE<br>STATUS | PROCEDURE       | TYPICAL POWER CONSUMPTION             | DIGITAL OUTPUT STATUS                                |

|------------------|-----------------|---------------------------------------|------------------------------------------------------|

|                  | PDN = TTL low   | 5 mW                                  | TSX and PCM OUT are in a high-impedance state;       |

| Power down       |                 |                                       | SIGR goes to TTL low within 10 μs.                   |

| Entire device    | FSX and FSR     | 12 mW                                 | TSX and PCM OUT are in a high-impedance state;       |

| on standby       | are TTL low     |                                       | SIGR goes to TTL low within 300 ms.                  |

| Only transmit    | FSX is TTL low  | 70 mW                                 | TSX and PCM OUT are placed in a high-impedance state |

| on standby       | FSR is TTL high |                                       | within 300 ms.                                       |

| Only receive     | FSR is TTL low  | 110 mW                                | SIGR is placed in a high-impedance state             |

| on standby       | FSX is TTL high | I I I I I I I I I I I I I I I I I I I | within 300 ms.                                       |

# fixed-data-rate timing (see Figure 7)

Fixed-data-rate timing is selected by connecting DCLKR to VgB. It uses master clocks CLKX and CLKR, frame synchronizer clocks FSX and FSR, and output  $\overline{\text{TSX}}$ . FSX and FSR are 8-kHz inputs that set the sampling frequency and distinguish between signaling and nonsignaling frames by their pulse width. A frame synchronization pulse one master clock wide designates a nonsignaling frame, while a double width sync pulse enables the signaling function (TCM2914 only). Data is transmitted on the PCM OUT pin on the first eight positive transitions of CLKX following the rising edge of FSX. Data is received on the PCM IN pin on the first eight falling edges of CLKR following FSX. A digital-to-analog (D/A) conversion is performed on the received digital word and the resulting analog sample is held on an internal sample-and-hold capacitor until transferred to the receive filter.

The clock selection pin (CLKSEL) is used to select the frequency of CLKX and CLKR (TMC2913 and TCM2914 only). The TCM2913 and TCM2914 fixed data rate mode can operate with frequencies of 1.536 MHz, 1.544 MHz, or 2.048 MHz. The TCM2916 and TCM2917 fixed data rate mode operates at 2.048 MHz only.

FIGURE 7. SIGNALING TIMING (FIXED-DATA-RATE ONLY)

### variable data rate timing

Variable-data-rate timing is selected by connecting DCLKR to the bit clock for the receive PCM highway rather than to VBB. It uses master clocks CLKX and CLKR, bit clocks DCLKX and DCLKR, and frame synchronization clocks FSX and FSR.

Variable-data-rate timing allows for a flexible data frequency. The frequency of the bit clocks can be varied from 64 kHz to 2.048 MHz. The bit clocks can be asynchronous in the TCM2914, but must be synchronous in the TCM2913, TCM2916, and TCM2917. Master clocks in types TCM2913 and TCM2914 are restricted to frequencies of operation of 1.536 MHz, 1.544 MHz, or 2.048 MHz as in the fixed-data-rate timing mode. The master clock for the TCM2916 and TCM2917 is restricted to 2.048 MHz.

While FSX/TSXE input is high, PCM data is transmitted from PCM OUT onto the highway on the next eight consecutive positive transitions of DCLKX. Similarly, while the FSR/TSRE input is high, the PCM word is received from the highway by PCM IN on the next eight consecutive negative transitions of DCLKR.

The transmitted PCM word will be repeated in all remaining timeslots in the 125  $\mu$ s frame as long as DCLKX is pulsed and FSX is held high. This feature, which allows the PCM word to be transmitted to the PCM highway more than once per frame, if desired, is available only with variable-data-rate timing. Signaling is allowed only in the fixed-data-rate mode because the variable-data-rate mode provides no means with which to specify a signaling frame.

# signaling

The TCM2914 (only) provides 8th-bit signaling in the fixed-data-rate timing mode. Transmit and receive signaling frames are independent of each other and are selected by a double-width frame sync pulse on the appropriate channel. During a transmit signaling frame, the signal present on SIGX is substituted for the least significant bit (LSB) of the encoded PCM word. In a receive signaling frame, the codec will decode the seven most significant bits in accordance with CCITT G.733 recommendations, and output the logical state of the LSB on the SIGR pin until it is updated in the next signaling frame. Timing relationships for signaling operations are shown n Figure 9. The signaling path is used to transmit digital signaling information such as ring control, rotary dial pulses, and off-hook and disconnect supervision. The voice path is used to transmit prerecorded messages as well as the call progress tones; dial tone, ring-back tone, busy tone, and re-order tone.

### asynchronous operation

The TCM2914 can be operated with asynchronous clocks in either the fixed- or variable-data-rate modes. In order to avoid crosstalk problems associated with special interrupt circuits, the design of the TCM2913 and TCM2914 includes separate digital-to-analog converters and voltage references on the transmit and receive sides to allow completely independent operation of the two channels.

In either timing mode, the master clock, data clock, and timeslot strobe must be synchronized at the beginning of each frame. Specifically, in the variable-rate mode, the falling edge of CLKX must occur within td(FSX) and the falling edge of DCLKX must occur within tdTSDX as after the rise of FSX. CLKX and DCLKX are synchronized once per frame but may be of different frequencies. The receive channel operates in a similar manner and is completely independent of the transmit timing (see variable data rate timing diagrams). This approach requires the provision of two separate master clocks but avoids the use of a synchronizer, which can cause intermittent data conversion errors.

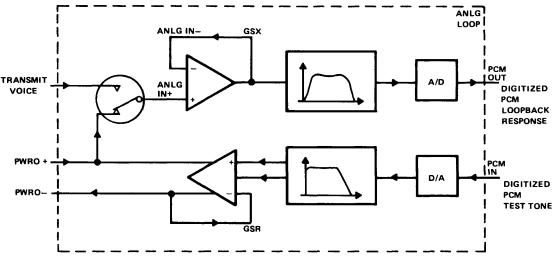

### analog loopback

A distinctive feature of the TCM2914 is its analog loopback capability. With this feature, the user can test the line circuit remotely by comparing the signals sent into the receive channel (PCM IN) with those generated on the transmit channel (PCM OUT). The test is accomplished by sending a control signal that internally connects the analog input and output ports. When ANLG LOOP is TTL high, the receive output (PWRO +) is internally connected to ANLG IN +, GSR is internally connected to PWRO –, and ANLG IN – is internally connected to GSX (see Figure 8).

FIGURE 8. TCM2914 ANALOG LOOPBACK CONFIGURATION

Due to the difference in the transmit and receive transmission levels, a 0 dBm0 code into PCM IN will emerge from PCM OUT as a 3-dBm0 code, an implicit gain of 3 dB. Because of this, the maximum signal that can be tested by analog loopback is 0 dBm0.

#### precision voltage references

No external components are required with the TCM2913, TCM2914, TCM2916, and TCM2917 to provide the voltage references. Voltage references that determine the gain and dynamic range characteristics of the device are generated internally. A difference in subsurface charge density between two suitably implanted MOS devices is used to derive a temperature- and bias-stable reference voltage. These references are calibrated during the manufacturing process. Separate references are supplied to the transmit and receive sections, and each is calibrated independently. Each reference value is then further trimmed in the gain setting operational amplifiers to a final precision value. Manufacturing tolerances can be achieved of typically  $\pm 0.04$  dB in absolute gain for each half channel, providing the user a significant margin to compensate for error in other board components.

#### conversion laws

The TCM2913 and TCM2914 provide pin-selectable  $\mu$ -law operation as specified by CCITT G.711 recommendation. A-law operation is selected when the ASEL pin is connected to VBB. Signaling is not allowed during A-law operation. The TCM2916 is  $\mu$ -law only. The TCM2917 is A-law only.

The  $\mu$ -law operation is effectively selected by not selecting A-law operation. If the ASEL pin is connected to VCC or GND, the device is in  $\mu$ -law operation. If  $\mu$ -law operation is selected, SIGX is a TTL-level input that can be used in the fixed data rate timing mode to modify the LSB of the PCM output in signaling frames.

# transmit operation

#### transmit filter

The input section provides gain adjustment in the passband by means of an on-chip uncommitted operational amplifier. The load impedance to ground (ANLG GND) at the amplifier output (GSX) must be greater than  $10 \text{ k}\Omega$  in parallel with less than 50 pF. The input signal on the ANLG IN + pin can be either ac or dc coupled. The input operational amplifier can also be used in the inverting mode or differential amplifier mode.

A low-pass antialiasing section is included on the device. This section provides 35-dB attenuation at the sampling frequency. No external components are required to provide the necessary antialiasing function for the switched capacitor section of the transmit filter.

The passband section provides flatness and stopband attenuation that fulfills the AT&T D3/D4 channel bank transmission specification and CCITT recommendation G.712. The TCM2913, TCM2914, TCM2916, and TCM2917 specifications meet or exceed digital class 5 central office switching systems requirements.

A high-pass section configuration was chosen to reject low-frequency noise from 50- and 60-Hz power lines, 17-Hz European electric railroads, ringing frequencies and their harmonics, and other low-frequency noise. Even with the high rejection at these frequencies, the sharpness of the band edge gives low attenuation at 200 Hz. This feature allows the use of low-cost transformer hybrids without external components.

### encoding

The encoder internally samples the output of the transmit filter and holds each sample on an internal sample and hold capacitor. The encoder performs an analog-to-digital conversion on a switched capacitor array. Digital data representing the sample is transmitted on the first eight data clocks bits of the next frame.

The autozero circuit corrects for dc offset on the input signal to the encoder. The autozero circuit uses the sign bit averaging technique. The sign bit from the encoder output is long-term averaged and subtracted from the input to the encoder. All dc offset is removed from the encoder input waveform.

# receive operation

### decoding

The serial PCM word is received at the PCM IN pin on the first eight data clock bits of the frame. Digital-toanalog conversion is performed and the corresponding analog sample is held on an internal sample-andhold capacitor. This sample is transferred to the receive filter.

#### receive filter

The receive section of the filter provides passband flatness and stopband rejection that fulfills both the AT&T D3/D4 specification and CCITT recommendation G.712. The filter contains the required compensation for the  $(\sin x)/x$  response of such decoders.

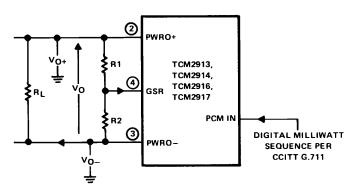

# receive output power amplifiers

A balanced output amplifier is provided to allow maximum flexibility in output configuration. Either of the two outputs can be used single-ended (i.e., referenced to ANLG GND) to drive single-ended loads. Alternatively, the differential output will directly drive a bridged load. The output stage is capable of driving loads as low as 300 ohms single-ended to a level of 12 dBm or 600 ohms differentially to a level of 15 dBm.

The receive channel transmission level may be adjusted between specified limits by manipulation of the GSR input. GSR is internally connected to an analog gain-setting network. When GSR is connected to PWRO –, the receive level is at maximum. When GSR is connected to PWRO +, the level is minimum. The output transmission level is adjusted between 0 and -12 dB as GSR is adjusted (with an adjustable resistor) between PWRO + and PWRO –.

Transmission levels are specified relative to the receive channel output under digital milliwatt conditions (i.e., when the digital input at PCM IN is the eight-code sequence specified in CCITT recommendation G.711).

#### TYPICAL APPLICATION DATA

### output gain set design considerations (see Figure 9)

PWRO + and PWRO - are low-impedance complementary outputs. The voltages at the nodes are:

VO+ at PWRO+

Vo - at PWRO -

$V_0 = V_{0+} - V_{0-}$  (total differential response)

R1 and R2 are a gain-setting resistor network with the center tap connected to the GSR input.

A value greater than 10 k $\Omega$  and less than 100 k $\Omega$  for R1 + R2 is recommended because of the following: The parallel combination of R1 + R2 and R<sub>I</sub> sets the total loading.

The total capacitance at the GSR input and the parallel combination of R1 and R2 define a time constant which has to be minimized to avoid inaccuracies.

VA represents the maximum available digital milliwatt output response (VA = 3.006 V rms).

$$V_O = A \cdot V_A$$

Where  $A = \frac{1 + (R1/R2)}{4 + (R1/R2)}$

FIGURE 9. GAIN-SETTING CONFIGURATION