# Octal Sample-and-Hold with Multiplexed Input

SMP08

# **FEATURES**

- Internal Hold Capacitors

- Low Droop Rate

- TTL/CMOS Compatible Logic Inputs

- Single or Dual Supply Operation

- Break-Before-Make Channel Addressing

- Compatible With CD4051 Pinout

- Low Cost

# **APPLICATIONS**

- Multiple Path Timing Deskew for A.T.E.

- Memory Programmers

- Mass Flow/Process Control Systems

- Multichannel Data Acquisition Systems

- Robotics and Control Systems

- Medical and Analytical Instrumentation

- Event Analysis

- Stage Lighting Control

# ORDERING INFORMATION 1

| PACKAGE:         | PACKAGE: 16-PIN DIP/SO |                                     |  |

|------------------|------------------------|-------------------------------------|--|

| CERDIP<br>16-PIN | PLASTIC<br>16-PIN      | . OPERATING<br>TEMPERATURE<br>RANGE |  |

| TBA*             | -                      | MIL                                 |  |

| SMP08FQ          | SMP08FP                | XIND                                |  |

| -                | SMP08FS                | XIND                                |  |

<sup>.</sup> Consult factory for 883 data sheet.

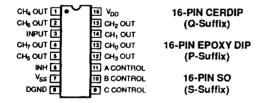

# **PIN CONNECTIONS**

# **GENERAL DESCRIPTION**

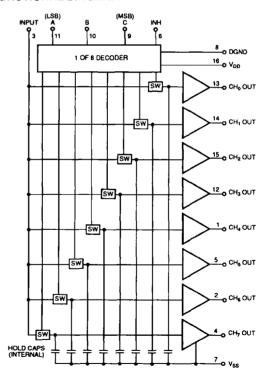

The SMP-08 is a monolithic octal sample-and-hold, it has eight internal buffer amplifiers, input multiplexer, and internal hold capacitors. It is manufactured in an advanced oxide isolated CMOS technology to obtain high accuracy, low droop rate, and

Manufactured under the following U.S. patent: 4,739,281

fast acquisition time. The SMP-08 has a typical linearity error of only 0.01% and can accurately acquire a 10-bit input signal to  $\pm 1/2$  LSB in less than seven microseconds. The SMP-08's output swing includes the negative supply in both single and dual supply operation.

The SMP-08 was specifically designed for systems that use a calibration cycle to adjust a multiple of system parameters. The low cost and high level of integration makes the SMP-08 ideal for calibration requirements that have previously required an ASIC, or high cost multiple D/A converters.

The SMP-08 is also ideally suited for a wide variety of sampleand-hold applications including amplifier offset or VCA gain adjustments. One or more SMP-08s can be used with single or multiple DACs to provide multiple set points within a system.

The SMP-08 offers significant cost and size reduction over discrete designs. It is available in a 16-pin hermetic or plastic DIP, or surface mount SOIC package.

## **FUNCTIONAL DIAGRAM**

This is an abridged data sheet. To obtain the most recent version or complete data sheet, call our fax retrieval system at 1-800-446-6212.

Burn-in is available on industrial temperature range parts in CerDIP and plastic DIP packages.

# SMP08

# **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| V <sub>DD</sub> to DGND     | –0.3V, 17V                        |

|-----------------------------|-----------------------------------|

| Von to Von                  | 0.3V, 17V                         |

| V to DGND                   | 0.3V, V <sub>pp</sub>             |

| V to DGND                   | V <sub>201</sub> V <sub>201</sub> |

| Value to DGND               | V <sub>ss</sub> , V <sub>pp</sub> |

| Analog Output Current       | ±20mA                             |

|                             | (Not short-circuit protected)     |

| Operating Temperature Range |                                   |

| ED EC                       | 40°C to 495°C                     |

| FP, F5                               | 40-0 10 +85-0  |

|--------------------------------------|----------------|

| Junction Temperature                 | +150°C         |

| Storage Temperature                  | 65°C to +150°C |

| Lead Temperature (Soldering, 60 sec) |                |

|                                      |                |

| PACKAGE TYPE            | ⊖ <sub>jA</sub> (Note 2) | Θ <sub>jc</sub> | UNITS |

|-------------------------|--------------------------|-----------------|-------|

| 16-Pin Hermetic DIP (Q) | 94                       | 12              | °C/W  |

| 16-Pin Plastic DIP (P)  | 76                       | 33              | °C/W  |

| 16-Pin SO (S)           | 92                       | 27              | °C/W  |

## NOTES:

- Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

- Θ<sub>IA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>IA</sub> is specified for device in socket for CerDIP and P-DIP packages; Θ<sub>IA</sub> is specified for device soldered to printed circuit board for SO package.

## CAUTION:

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to the above maximum rating conditions for extended periods may affect device reliability.

- Digital inputs and outputs are protected; however, permanent damage may occur on unprotected units from high-energy electrostatic fields. Keep units in conductive foam or packaging at all times until ready to use. Use proper antistatic handling procedures.

- 3. Remove power before inserting or removing units from their sockets.

**ELECTRICAL CHARACTERISTICS** at  $V_{DD} = +5V$ ,  $V_{SS} = -5V$ , DGND = 0V,  $R_L = No$  Load,  $T_A = -40$ °C to +85°C for SMP-08F, unless otherwise noted.

|                           |                      |                                                          | SMP-08F |            |          | -     |

|---------------------------|----------------------|----------------------------------------------------------|---------|------------|----------|-------|

| PARAMETER                 | SYMBOL               | CONDITIONS                                               | MIN     | TYP        | MAX      | UNITS |

| Linearity Error           |                      | -3V ≤ V <sub>IN</sub> ≤ +3V                              | _       | 0.01       | _        | %     |

| Buffer Offset Voltage     | v <sub>os</sub>      | T <sub>A</sub> = +25°C<br>-40°C ≤ T <sub>A</sub> ≤ +85°C | =       | 2.5<br>3.5 | 10<br>20 | mV    |

| Hold Step                 | V <sub>HS</sub>      | V <sub>IN</sub> = 0V                                     | _       | 1          | 4        | mV    |

| Droop Rate                | ΔV <sub>CH</sub> /Δt | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 0V             | _       | 2          | 20       | mV/s  |

| Output Source Current     | SOURCE               | V <sub>IN</sub> = 0V (Note 1)                            | 1.2     |            | _        | mA    |

| Output Sink Current       | Isink                | V <sub>IN</sub> = 0V (Note 1)                            | 0.5     | _          | _        | mA    |

| Output Voltage Range      |                      | R <sub>L</sub> = 20kΩ                                    | -3.0    | _          | +3.0     | ٧     |

| LOGIC CHARACTERISTICS     |                      |                                                          |         |            |          |       |

| Logic Input High Voltage  | V <sub>INH</sub>     | <del></del>                                              | 2.4     | _          | -        | ٧     |

| Logic Input Low voltage   | V <sub>INL</sub>     |                                                          | -       |            | 0.8      | ٧     |

| Logic Input Current       | 1 <sub>IN</sub>      | V <sub>IN</sub> = 2.4V                                   | _       | 0.5        | 1        | μА    |

| DYNAMIC PERFORMANCE       | (Note 2)             |                                                          |         |            |          |       |

| Acquisition Time          | t <sub>AQ</sub>      | T <sub>A</sub> = +25°C, -3V to +3V to 0.1%               | -       | 7          |          | μз    |

| Hold Mode Settling Time   | 14                   | To ± 1mV of Final Value                                  | _       | 1          | _        | μs    |

| Channel Select Time       | 1 <sub>CH</sub>      |                                                          | _       | 90         | _        | ns    |

| Channel Deselect Time     | t <sub>DCS</sub>     |                                                          | _       | 45         | _        | ns    |

| Inhibit Recovery Time     | t <sub>in</sub>      |                                                          | _       | 90         | _        | ns    |

| Slew Rate                 | SR                   |                                                          | _       | 3          |          | V/µs  |

| Capacitive Load Stability |                      | <30% Overshoot                                           |         | 500        | _        | pF    |

| Analog Crosstalk          |                      | -3V to +3V Step                                          | _       | -72        |          | dB    |

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +5V,  $V_{SS}$  = -5V, DGND = 0V,  $R_L$  = No Load,  $T_A$  = -40°C to +85°C for SMP-08F, unless otherwise noted. *Continued*

|                              | • •    | <u> </u>                       | SMP-08F |     |     |       |

|------------------------------|--------|--------------------------------|---------|-----|-----|-------|

| PARAMETER                    | SYMBOL | CONDITIONS                     | MIN     | TYP | MAX | UNITS |

| SUPPLY CHARACTERISTICS       |        |                                | -       |     |     |       |

| Power Supply Rejection Ratio | PSRR   | V <sub>s</sub> = ±5V to ±6V    | 60      | 75  | _   | dB    |

| Supply Current               |        | T <sub>4</sub> = +25°C         | _       | 5.5 | 7.5 |       |

|                              | םם '   | -40°C ≤ T <sub>A</sub> ≤ +85°C | _       | 7.5 | 9.5 | mA    |

#### NOTES

- Outputs are capable of sinking and sourcing over 20mA but offset is guaranteed at specified load levels.

- 2. All input control signals are specified with  $t_r$  =  $t_t$  = 5ns (10% to 90% of +5V) and timed from a voltage level of 1.6V.

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$  = +12V,  $V_{SS}$  = 0V, DGND = 0V,  $R_L$  = No Load,  $T_A$  = -40°C to +85°C for SMP-08F, unless otherwise noted.

|                              |                      |                                              |      | SMP-08F |      |       |

|------------------------------|----------------------|----------------------------------------------|------|---------|------|-------|

| PARAMETER                    | SYMBOL               | CONDITIONS                                   | MIN  | TYP     | MAX  | UNITS |

| Linearity Error              |                      | 60mV ≤ V <sub>IN</sub> ≤ 10V                 |      | 0.01    | -    | %     |

| Buffer Offset Voltage        | V <sub>os</sub>      | T <sub>A</sub> = +25°C                       | _    | 2.5     | 10   | mV    |

| Duller Onset voltage         | os                   | -40°C ≤ T <sub>A</sub> ≤ +85°C               |      | 3.5     | 20   |       |

| Hold Step                    | V <sub>HS</sub>      | V <sub>IN</sub> ≠ 6V                         | _    | 1       | 4    | m∨    |

| Droop Rate                   | ΔV <sub>CH</sub> /Δt | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 6V | _    | 2       | 20   | mV/s  |

| Output Source Current        | ISOURCE              | V <sub>IN</sub> = 6V (Note 1)                | 1.2  |         | _    | mA    |

| Output Sink Current          | Isink                | V <sub>IN</sub> = 6V (Note 1)                | 0.5  | _       | -    | mA    |

| Output Voltage Range         |                      | R <sub>L</sub> = 20kΩ                        | 0.06 |         | 10.0 |       |

| Output voitage hange         |                      | R = 10kΩ                                     | 0.06 |         | 9.5  |       |

| LOGIC CHARACTERISTICS        |                      |                                              |      |         |      |       |

| Logic Input High Voltage     | V <sub>INH</sub>     |                                              | 2.4  | _       | _    | ٧     |

| Logic Input Low voltage      | V <sub>INL</sub>     |                                              |      | _       | 0.8  | ٧     |

| Logic Input Current          | IIN                  | V <sub>IN</sub> = 2.4V                       | _    | 0.5     | 1    | μА    |

| DYNAMIC PERFORMANCE (        | Note 2)              |                                              |      |         |      |       |

| Acquisition Time             | t <sub>AO</sub>      | T <sub>A</sub> = +25°C, 0 to 10V to 0.1%     | -    | 9       | _    | μs    |

| Hold Mode Settling Time      | t <sub>H</sub>       | To ± 1mV of Final Value                      |      | 1       |      | μs    |

| Channel Select Time          | t <sub>CH</sub>      |                                              | _    | 90      | _    | ns    |

| Channel Deselect Time        | tocs                 |                                              | _    | 45      | _    | ns    |

| Inhibit Recovery Time        | t <sub>A</sub>       |                                              | _    | 90      | _    | ns    |

| Slew Rate                    | SR                   | R <sub>L</sub> = 20kΩ (Note 3)               | 3    | 4       | _    | V/µs  |

| Capacitive Load Stability    |                      | <30% Overshoot                               |      | 500     | _    | pF    |

| Analog Crosstalk             | <u></u>              | 0 to 10V Step                                | -    | -72     | _    | dB    |

| SUPPLY CHARACTERISTICS       |                      |                                              |      |         |      |       |

| Power Supply Rejection Ratio | PSRR                 | 10.8V ≤ V <sub>DD</sub> ≤ 13.2V              | 60   | 75      | _    | dB    |

| Supply Current               | 1                    | T <sub>A</sub> = +25°C                       | -    | 6.0     | 8.0  | mA    |

| Supply Current               | I <sub>DD</sub>      | -40°C ≤ T <sub>A</sub> ≤ +85°C               | _    | 8.0     | 10.0 |       |

# NOTES:

- Outputs are capable of sinking and sourcing over 20mA but offset is guaranteed at specified load levels.

- All input control signals are specified with t<sub>i</sub> = t<sub>i</sub> = 5ns (10% to 90% of +5V) and timed from a voltage level of 1.6V.

- Slew rate is measured in the sample mode with a 0 to 10V step from 20% to 80%.