TEXAS INSTRUMENTS

TPS25832-Q1, TPS25833-Q1 SLVSEH7D – JULY 2019 – REVISED MARCH 2022

# TPS2583x-Q1 Automotive USB Type-C<sup>®</sup> and BC1.2 5-V 3.5-A Output, 36-V Input Synchronous DC/DC Regulator with Cable Compensation

# 1 Features

- AEC-Q100 qualified for automotive applications:

- Temperature grade 1: –40°C to +125°C, T<sub>A</sub>

- HBM ESD classification level H2

- CDM ESD classification level C5

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- Synchronous buck DC/DC regulator

- Input voltage range: 4.5 V to 36 V

- Output current: 3.5 A

- 5.1-V output voltage with ±1% accuracy

- Current mode control

- Adjustable frequency: 300 kHz to 2.2 MHz

- Frequency synchronization to external clock

- FPWM with spread-spectrum dithering

- Internal compensation for ease of use

- Compliant to USB-IF standards

- USB Type-C<sup>®</sup> Rev 1.3

- CC logic, V<sub>CONN</sub> source and discharge

- USB cable polarity detection (POL)

- CDP/SDP Mode per USB BC1.2

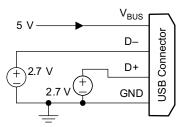

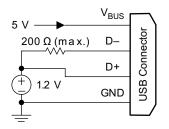

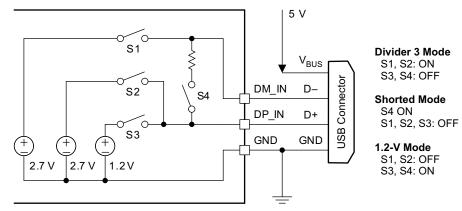

- Automatic DCP modes (TPS25833-Q1 only)

- DCP shorted mode and YD/T 1591-2009

- 2.7-V divider 3 mode

- 1.2-V mode

- Optimized for USB power and communication

- User-programmable USB current limit

- Cable droop compensation up to 1.5 V

- High bandwidth data switches on DP and DM (TPS25832-Q1 only)

- NTC input for intelligent thermal management (TPS25833-Q1 only)

- Integrated protection

- DP\_IN and DM\_IN Short-to-V<sub>BUS</sub> protection

- DP\_IN, DM\_IN, CCx IEC 61000-4-2 rated

- ±8-kV contact and ±15-kV air discharge

- Fault flag reports

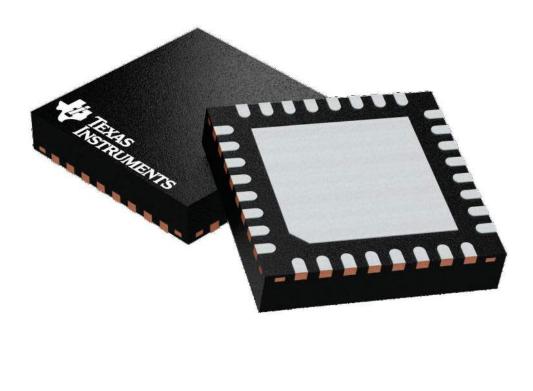

- 32-pin QFN package with wettable flank

#### 2 Applications

- Automotive infotainment

- USB media hubs

- USB charger ports

# **3 Description**

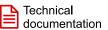

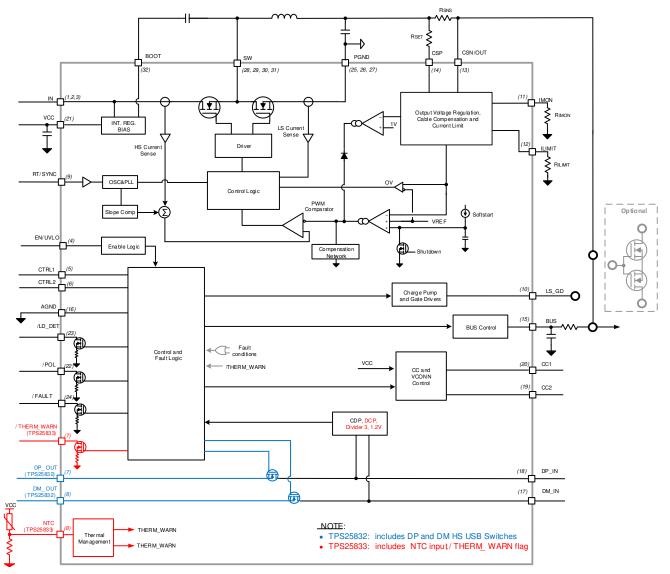

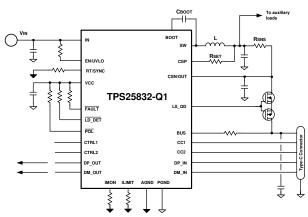

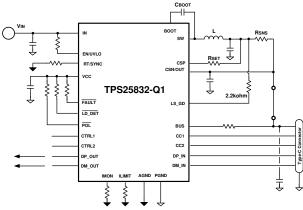

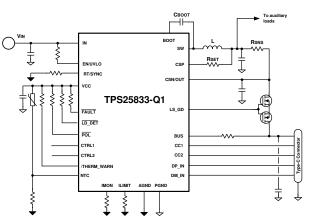

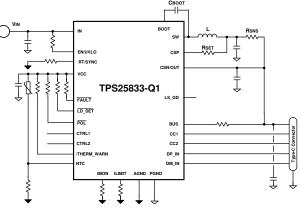

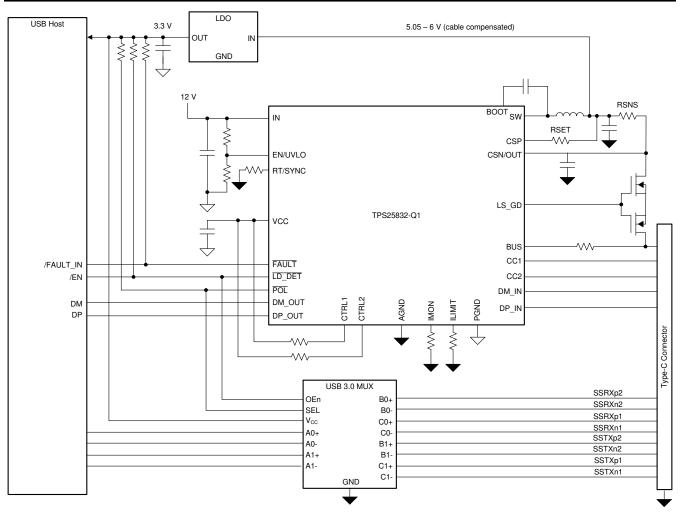

The TPS2583x-Q1 is a USB Type-C and BC1.2 charging port controller that includes a synchronous DC/DC converter. With cable droop compensation, the  $V_{BUS}$  voltage remains constant regardless of load current, ensuring connected portable devices charge at optimal current and voltage.

The TPS25832-Q1 includes high bandwidth analog switches for DP and DM pass-through, while the TPS25833-Q1 includes a thermistor input pin and thermal warning flag for user programmable thermal overload protection.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS25832-Q1 | VQFN (32) | 5.00 mm × 5.00 mm |

| TPS25833-Q1 | VQFN (32) | 5.00 mm × 5.00 mm |

(1) For detail part numbers for all available different options, see the orderable addendum at the end of the data sheet.

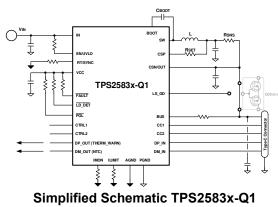

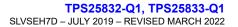

Efficiency vs Output Current fsw = 400 kHz

# **Table of Contents**

| 2 Applications13 Description14 Revision History25 Description (Continued)36 Device Comparison Table37 Pin Configuration and Functions48 Specifications68.1 Absolute Maximum Ratings68.2 ESD Ratings78.3 Recommended Operating Conditions78.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview2210.2 Functional Block Diagram23 | 1 Features                          | 1              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------|

| 4 Revision History25 Description (Continued)36 Device Comparison Table37 Pin Configuration and Functions48 Specifications68.1 Absolute Maximum Ratings68.2 ESD Ratings78.3 Recommended Operating Conditions78.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview22                                                             | 2 Applications                      | 1              |

| 4 Revision History25 Description (Continued)36 Device Comparison Table37 Pin Configuration and Functions48 Specifications68.1 Absolute Maximum Ratings68.2 ESD Ratings78.3 Recommended Operating Conditions78.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview22                                                             | 3 Description                       | 1              |

| 5 Description (Continued)36 Device Comparison Table37 Pin Configuration and Functions48 Specifications68.1 Absolute Maximum Ratings68.2 ESD Ratings78.3 Recommended Operating Conditions78.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview22                                                                                | 4 Revision History                  | 2              |

| 7 Pin Configuration and Functions48 Specifications68.1 Absolute Maximum Ratings68.2 ESD Ratings78.3 Recommended Operating Conditions78.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview22                                                                                                                                    | 5 Description (Continued)           | 3              |

| 8 Specifications68.1 Absolute Maximum Ratings68.2 ESD Ratings78.3 Recommended Operating Conditions78.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview22                                                                                                                                                                      | 6 Device Comparison Table           | 3              |

| 8.1 Absolute Maximum Ratings.68.2 ESD Ratings.78.3 Recommended Operating Conditions.78.4 Thermal Information.88.5 Electrical Characteristics.88.6 Timing Requirements.138.7 Switching Characteristics.138.8 Typical Characteristics.159 Parameter Measurement Information.2110 Detailed Description.2210.1 Overview.22                                                                                                                                                                            | 7 Pin Configuration and Functions   | 4              |

| 8.1 Absolute Maximum Ratings.68.2 ESD Ratings.78.3 Recommended Operating Conditions.78.4 Thermal Information.88.5 Electrical Characteristics.88.6 Timing Requirements.138.7 Switching Characteristics.138.8 Typical Characteristics.159 Parameter Measurement Information.2110 Detailed Description.2210.1 Overview.22                                                                                                                                                                            | 8 Specifications                    | 6              |

| 8.2 ESD Ratings78.3 Recommended Operating Conditions78.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview22                                                                                                                                                                                                                    |                                     |                |

| 8.4 Thermal Information88.5 Electrical Characteristics88.6 Timing Requirements138.7 Switching Characteristics138.8 Typical Characteristics159 Parameter Measurement Information2110 Detailed Description2210.1 Overview22                                                                                                                                                                                                                                                                         |                                     |                |

| 8.5 Electrical Characteristics.88.6 Timing Requirements.138.7 Switching Characteristics.138.8 Typical Characteristics.159 Parameter Measurement Information.2110 Detailed Description.2210.1 Overview.22                                                                                                                                                                                                                                                                                          |                                     |                |

| 8.6 Timing Requirements.138.7 Switching Characteristics.138.8 Typical Characteristics.159 Parameter Measurement Information.2110 Detailed Description.2210.1 Overview.22                                                                                                                                                                                                                                                                                                                          | 8.4 Thermal Information             | <mark>8</mark> |

| 8.7 Switching Characteristics.138.8 Typical Characteristics.159 Parameter Measurement Information.2110 Detailed Description.2210.1 Overview.22                                                                                                                                                                                                                                                                                                                                                    | 8.5 Electrical Characteristics      | <mark>8</mark> |

| 8.8 Typical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8.6 Timing Requirements             | 13             |

| 9 Parameter Measurement Information       21         10 Detailed Description       22         10.1 Overview       22                                                                                                                                                                                                                                                                                                                                                                              | 8.7 Switching Characteristics       | 13             |

| 10 Detailed Description         22           10.1 Overview         22                                                                                                                                                                                                                                                                                                                                                                                                                             | 8.8 Typical Characteristics         | 15             |

| 10.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9 Parameter Measurement Information | 21             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10 Detailed Description             | 22             |

| 10.2 Functional Block Diagram23                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10.1 Overview                       | 22             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10.2 Functional Block Diagram       | 23             |

| 10.3 Feature Description                              | .23  |

|-------------------------------------------------------|------|

| 10.4 Device Functional Modes                          | .47  |

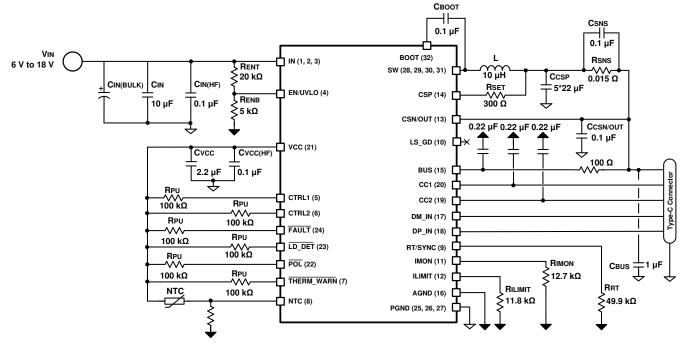

| 11 Application and Implementation                     |      |

| 11.1 Application Information                          |      |

| 11.2 Typical Application                              |      |

| 12 Power Supply Recommendations                       |      |

| 13 Layout                                             |      |

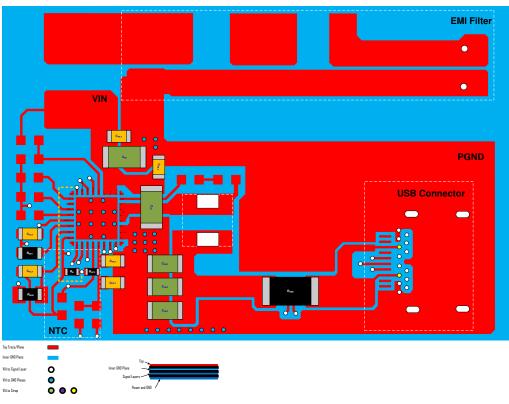

| 13.1 Layout Guidelines                                |      |

| 13.2 Ground Plane and Thermal Considerations          |      |

| 13.3 Layout Example                                   |      |

| 14 Device and Documentation Support                   |      |

| 14.1 Documentation Support                            |      |

| 14.2 Receiving Notification of Documentation Updates. |      |

| 14.3 Support Resources                                |      |

| 14.4 Trademarks                                       |      |

| 14.5 Electrostatic Discharge Caution                  |      |

| 14.6 Glossary                                         |      |

| 15 Mechanical, Packaging, and Orderable               |      |

| Information                                           | . 65 |

|                                                       |      |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision C (August 2020) to Revision D (March 2022) | Page |

|------------------------------------------------------------------|------|

| Added RHB0032AA package to the data sheet                        | 4    |

| Added the thermal information for RHB0032AA package              |      |

| Changes from Revision B (May 2020) to Revision C (August 2020)   | Page |

| С | hanges from Revision B (May 2020) to Revision C (August 2020)                                                                                                | Page |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | Updated the numbering format for tables, figures and cross-references throughout the document<br>Added functional safety link to the <i>Features</i> section |      |

| С | hanges from Revision A (September 2019) to Revision B (May 2020)                                                                                             | Page |

| Changed Layout descriptio | n for clarity              |                                        |                                        |                                        | . 62                                   |

|---------------------------|----------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

|                           |                            |                                        |                                        |                                        |                                        |

|                           | Changed Layout description | Changed Layout description for clarity |

# Changes from Revision \* (July 2019) to Revision A (September 2019)

| • | Changed TPS25832-Q1 to Production Data | 1 |

|---|----------------------------------------|---|

|   |                                        |   |

Page

# **5** Description (Continued)

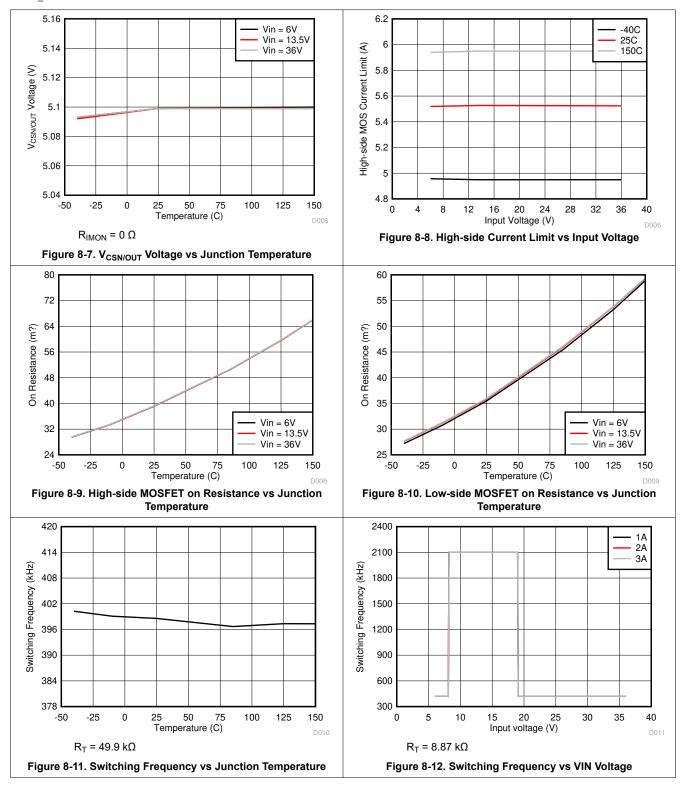

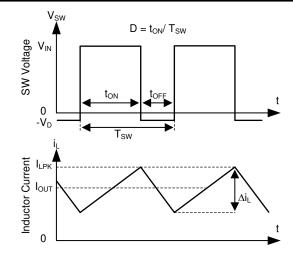

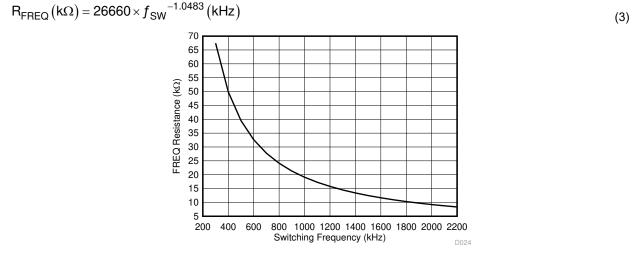

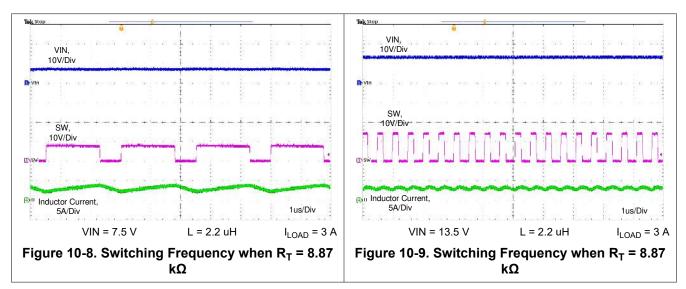

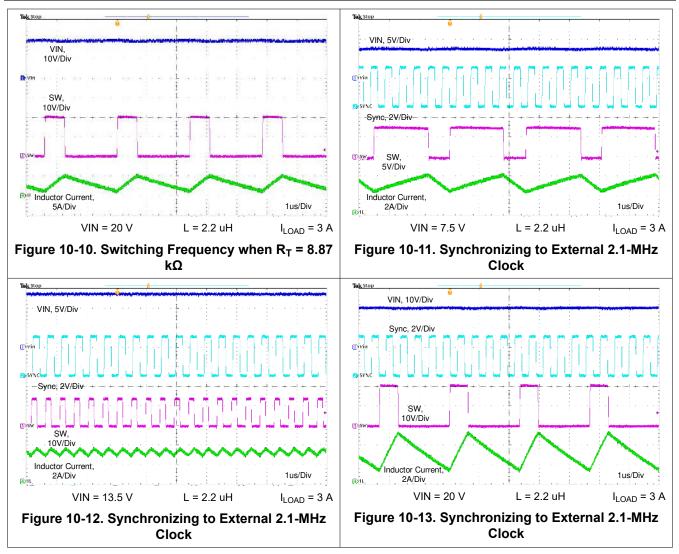

The synchronous buck regulator operates with current mode control and is internally compensated to simplify the design. A resistor on the RT pin sets the switching frequency between 300 kHz and 2.2 MHz. Operating below 400 kHz results in better system efficiency. Operation above 2.1 MHz avoids the AM radio bands and allows for use of a smaller inductor.

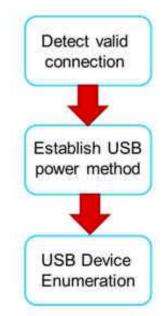

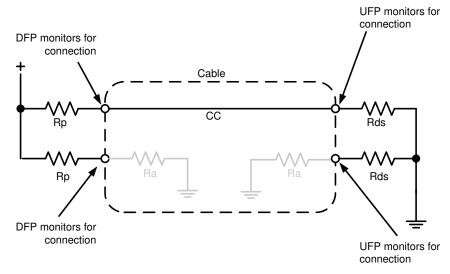

The TPS2583x-Q1 integrates standard USB Type-C port controller functionality including Configuration Channel (CC) logic for 3-A and 1.5-A current advertisement. Battery Charging (Rev. 1.2) integration provides the required electrical signatures necessary for non-Type-C, legacy USB devices that use USB data line signaling to determine USB port current sourcing capabilities.

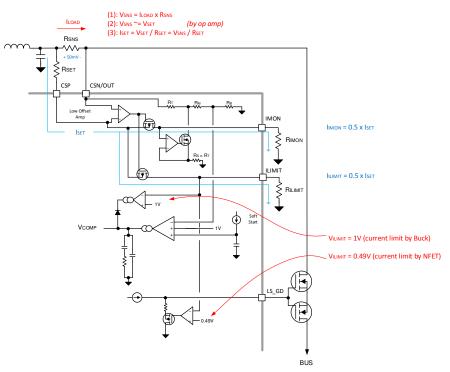

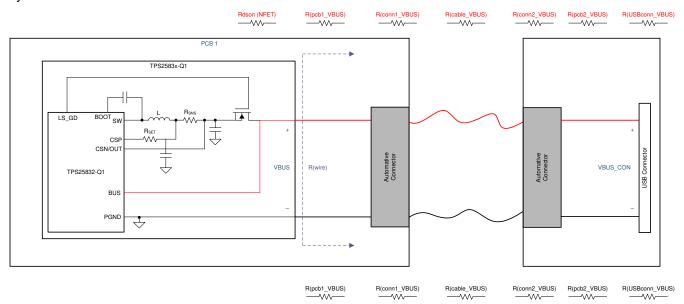

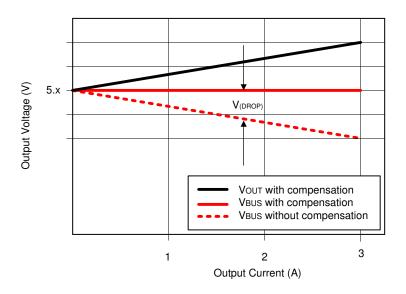

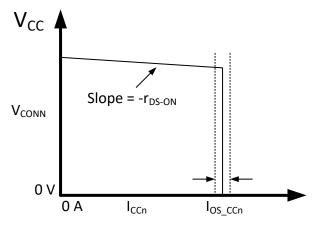

A precision current sense amplifier is included for user programmable cable droop compensation and current limit tuning. Cable compensation aids portable devices in charging at optimum current and voltage under heavy loads by changing the buck regulator output voltage linearly with load current to counteract the voltage drop due to wire resistance in automotive cabling. The  $V_{BUS}$  voltage measured at a connected portable device remains approximately constant, regardless of load current, allowing the portable device's battery charger to work optimally.

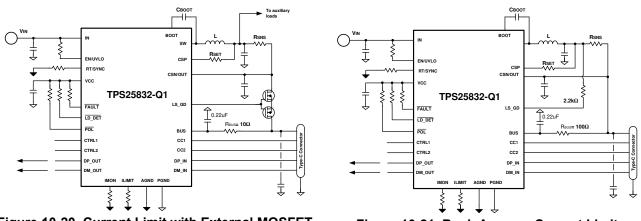

The USB specifications require current limiting of USB charging ports, but give system designers reasonable flexibility to choose overcurrent protection levels based on system requirements. The TPS2583x-Q1 uses a novel two-threshold current limit circuit allowing system designers to either program average current limit protection of the buck regulator, or optionally, current limit using an external NMOS between the CSN/OUT and BUS pins. The NFET implementation enables the TPS2583x-Q1 buck regulator to supply a 5-V output for other loads during an overcurrent fault condition on the USB port.

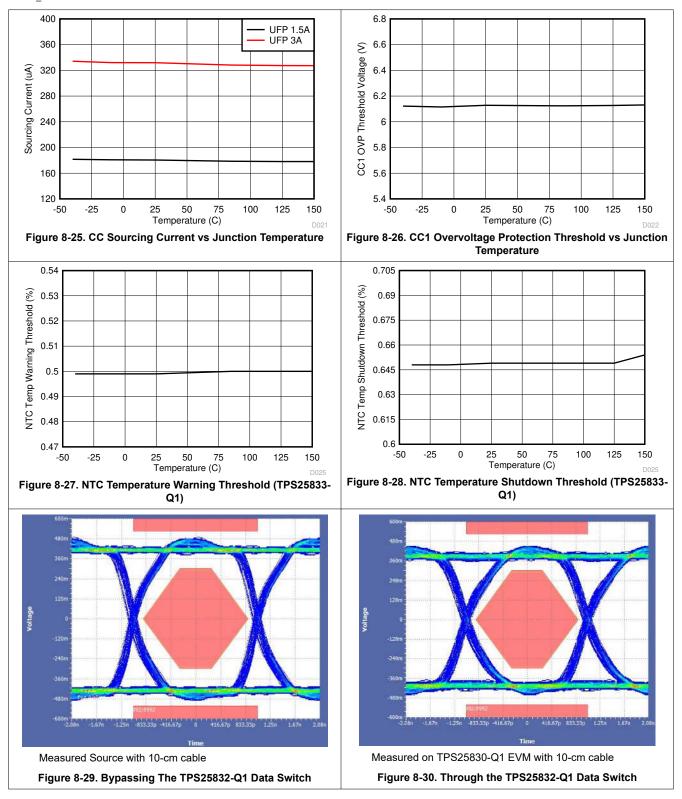

The TPS25832-Q1 includes high bandwidth analog switches for DP and DM pass-through. The TPS25833-Q1 includes a thermistor input pin and thermal warning flag for user programmable thermal overload protection.

Integrated protection features include cycle-by-cycle current limit, hiccup short-circuit protection, undervoltage lockout,  $V_{BUS}$  overvoltage and overcurrent, CC overvoltage and overcurrent, data line (D<sub>x</sub>) short-to-V<sub>BUS</sub> and die overtemperature protection.

| PART NUMBER | PACKAGE   | DCP AUTO | DP AND DM<br>SWITCHES | NTC INPUT | THERMAL<br>WARNING FLAG | DP/DM/CC SHORT<br>TO VBAT |

|-------------|-----------|----------|-----------------------|-----------|-------------------------|---------------------------|

| TPS25832-Q1 | VQFN (32) | No       | Yes                   | No        | No                      | No                        |

| TPS25833-Q1 | VQFN (32) | Yes      | No                    | Yes       | Yes                     | No                        |

# 6 Device Comparison Table

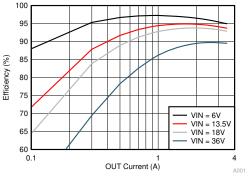

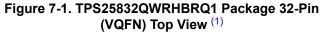

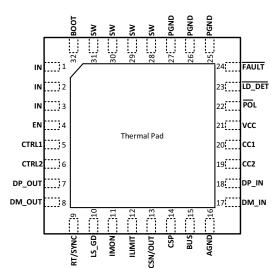

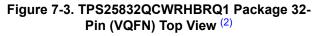

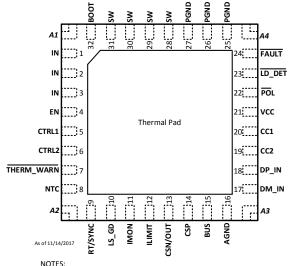

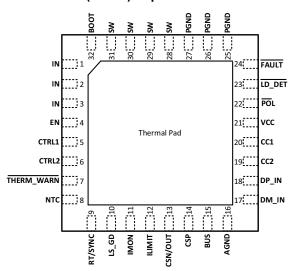

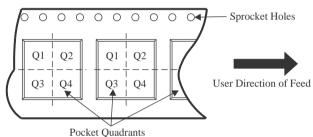

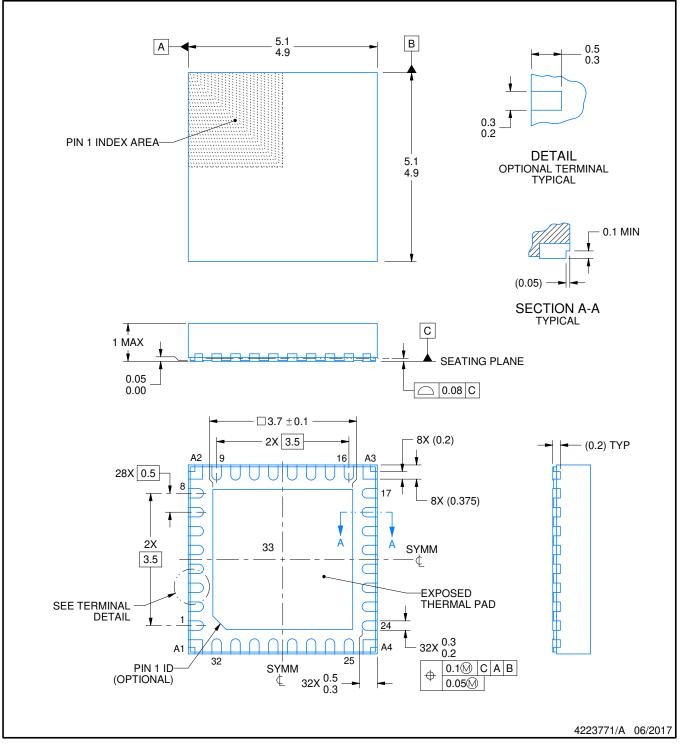

# 7 Pin Configuration and Functions

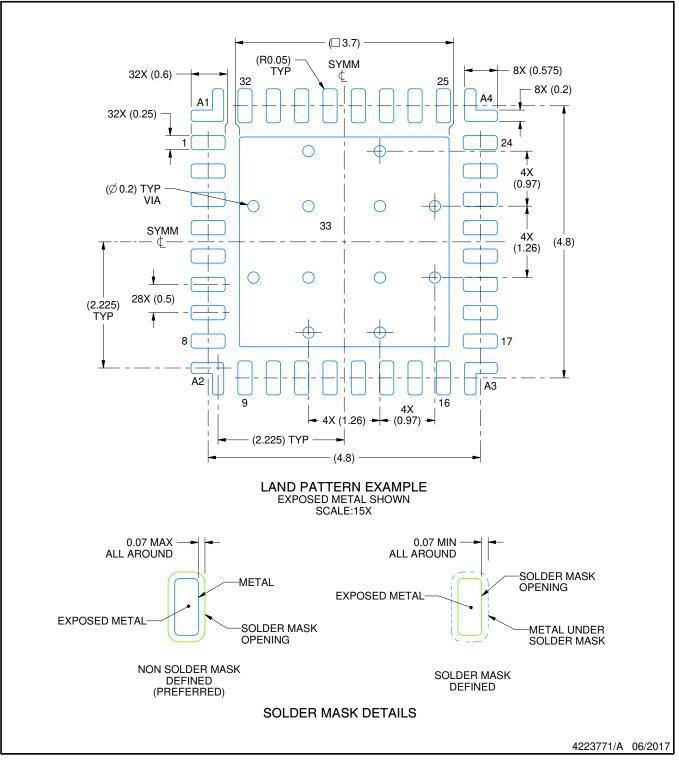

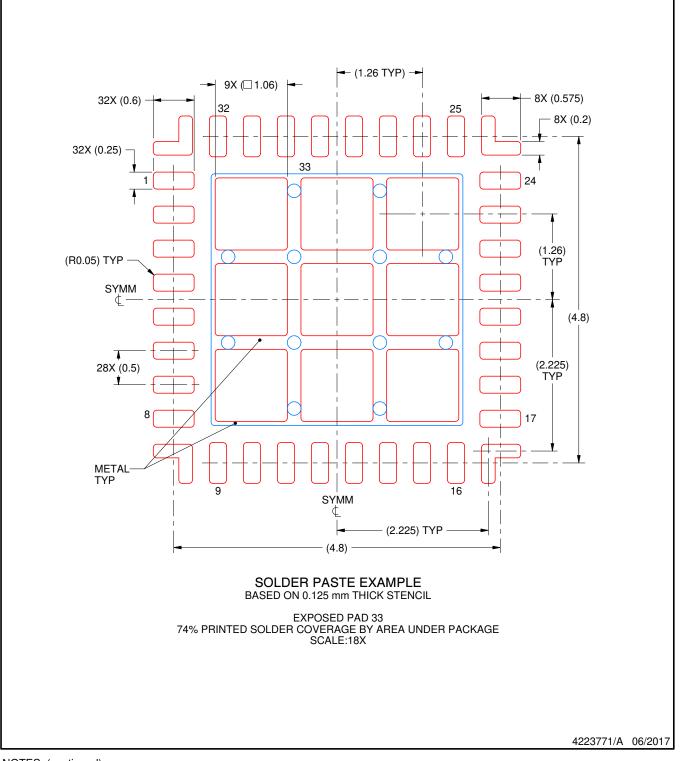

1) A1, A2, A3, and A4 are corner anchors for enhanced package stress performance.

2) A1, A2, A3, and A4 are electrically connected to the thermal pad. 3) A1, A2, A3, and A4 PCB lands should be electrically isolated or electrically connected to thermal pad and PGND.

1) A1, A2, A3, and A4 are corner anchors for enhanced package stress performance.

2) A1, A2, A3, and A4 are electrically connected to the thermal pad. 3) A1, A2, A3, and A4 PCB lands should be electrically isolated or electrically connected to thermal pad and PGND.

#### Figure 7-2. TPS25833QWRHBRQ1 Package 32-Pin (VQFN) Top View <sup>(1)</sup>

Figure 7-4. TPS25833QCWRHBRQ1 Package 32-Pin (VQFN) Top View (2)

|  | Table | 7-1. P | in Func | tions |

|--|-------|--------|---------|-------|

|--|-------|--------|---------|-------|

| NAME | 832-Q1<br>NO. | 833-Q1<br>NO. | <b>TYPE</b><br>(3) | I/O | DESCRIPTION                                                                                                                                                                   |  |

|------|---------------|---------------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AGND | 16            | 16            | G                  | _   | Analog ground terminal. Ground reference for internal references and logic. All electrical parameters are measured with respect to this pin. Connect to system ground on PCB. |  |

| BOOT | 32            | 32            | Р                  |     | Boot-strap capacitor connection for HS FET driver. Connect a high quality 100-nF capacitor from this pin to the SW pin.                                                       |  |

| BUS  | 15            | 15            | А                  | I   | VBUS discharge input. Connect to VBUS on USB Connector.                                                                                                                       |  |

| CC1  | 20            | 20            | А                  | I/O | Analog input/output. Connect to Type-C CC1 pin.                                                                                                                               |  |

#### Table 7-1. Pin Functions (continued)

| NAME           | 832-Q1<br>NO.     | 833-Q1<br>NO.     | TYPE<br>(3) | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------------|-------------------|-------------------|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CC2            | 19                | 19                | А           | I/O | Analog input/output. Connect to Type-C CC2 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CSN/OU<br>T    | 13                | 13                | А           | I   | Negative input of current sense amplifier, also buck output for internal voltage regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| CSP            | 14                | 14                | А           | I   | Positive input of current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| CTRL1          | 5                 | 5                 | А           | Ι   | Logic-level control inputs for device/system configuration (see Table 10-10).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CTRL2          | 6                 | 6                 | А           | I   | Logic-level control inputs for device/system configuration (see Table 10-10).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DM_IN          | 17                | 17                | А           |     | DM data line. Connect to USB connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DM_OU<br>T     | 8                 | -                 | А           |     | DM data line. Connect to USB host controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DP_IN          | 18                | 18                | А           |     | DP data line. Connect to USB connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DP_OU<br>T     | 7                 | -                 | А           |     | DP data line. Connect to USB host controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

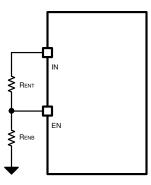

| EN/<br>UVLO    | 4                 | 4                 | А           |     | Enable pin. Do not float. High = on, Low = off. Can be tied to VIN. Precision enable input allows adjustable UVLO by external resistor divider.                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| FAULT          | 24                | 24                | А           | 0   | Active LOW open-drain output. Asserted during fault conditions (see Table 10-4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ILIMIT         | 12                | 12                | А           |     | External resistor used to set the current-limit threshold (see Table 10-2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| IMON           | 11                | 11                | А           |     | External resistor used to set the max cable comp voltage at full load current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| IN             | 1, 2, 3           | 1, 2, 3           | Ρ           | I   | Input Supply to regulator. Connect a high-quality bypass capacitor(s) directly to this pin and PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| LD_DET         | 23                | 23                | А           | 0   | Active LOW open-drain output. Asserted when a Type-C UFP is identified on the CC lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| LS_GD          | 10                | 10                | А           |     | External NMOS gate driver. For TPS25832-Q1, LS_GD pin must be pulled up through a 2.2-k $\Omega$ resistor under average current limit mode.(see <i>Current Limit Setting using R<sub>ILIMIT</sub></i> ).                                                                                                                                                                                                                                                                                                                                                |  |

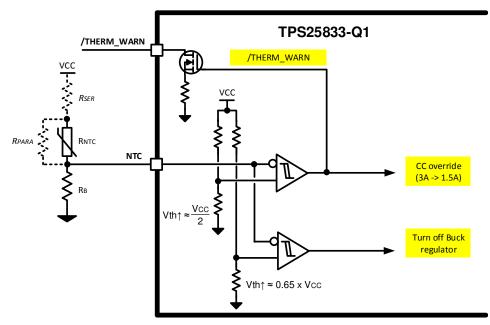

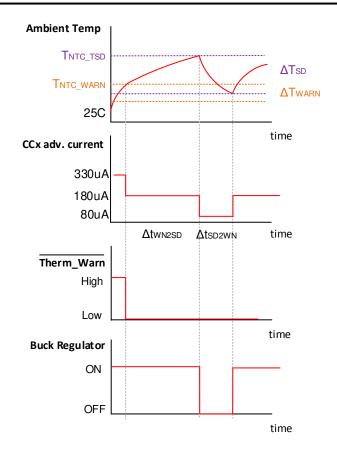

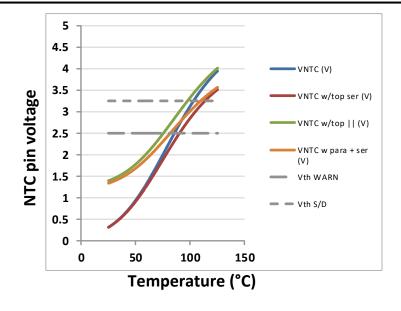

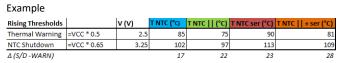

| NTC            | -                 | 8                 |             | I   | Input for negative temperature coefficient resistor divider. Use to monitor external PCB temperature (see <i>Thermal Sensing with NTC (TPS25833-Q1)</i> ).                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PGND           | 25, 26, 27        | 25, 26, 27        | G           | _   | Power ground terminal. Connect to system ground and AGND. Connect to bypass capacitor with short wide traces.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| POL            | 22                | 22                | А           | 0   | Active LOW open-drain output. Signals which Type-C CC pin is connected to the CC line. This gives cable orientation information needed to mux the super speed lines. Asserted when the CC2 pin is connected to the CC line in the cable.                                                                                                                                                                                                                                                                                                                |  |

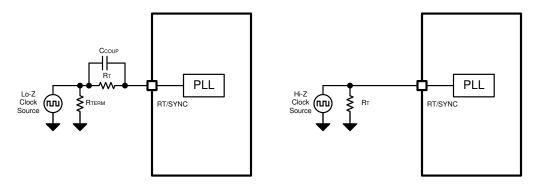

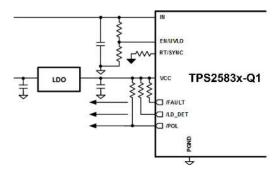

| RT/<br>SYNC    | 9                 | 9                 | A           |     | Resistor Timing or External Clock input. An internal amplifier holds this terminal at a fixed voltage when using an external resistor to ground to set the switching frequency. If the terminal is pulled above the PLL upper threshold, a mode change occurs and the terminal becomes a synchronization input. The internal amplifier is disabled and the terminal is a high impedance clock input to the internal PLL. If clocking edges stop, the internal amplifier is re-enabled and the operating mode returns to resistor frequency programming. |  |

| sw             | 28, 29,<br>30, 31 | 28, 29,<br>30, 31 | Р           |     | Switching output of the regulator. Internally connected to source of the HS FET and drain of the LS FET. Connect to power inductor.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| THERM<br>_WARN | -                 | 7                 | А           | 0   | Active LOW open-drain output. Asserted when voltage at the NTC pin increases above the thermal warning threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| VCC            | 21                | 21                | Р           |     | Output of internal bias supply. Used as supply to internal control circuits. Connect a high quality $2.2$ - $\mu$ F capacitor from this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                     |  |

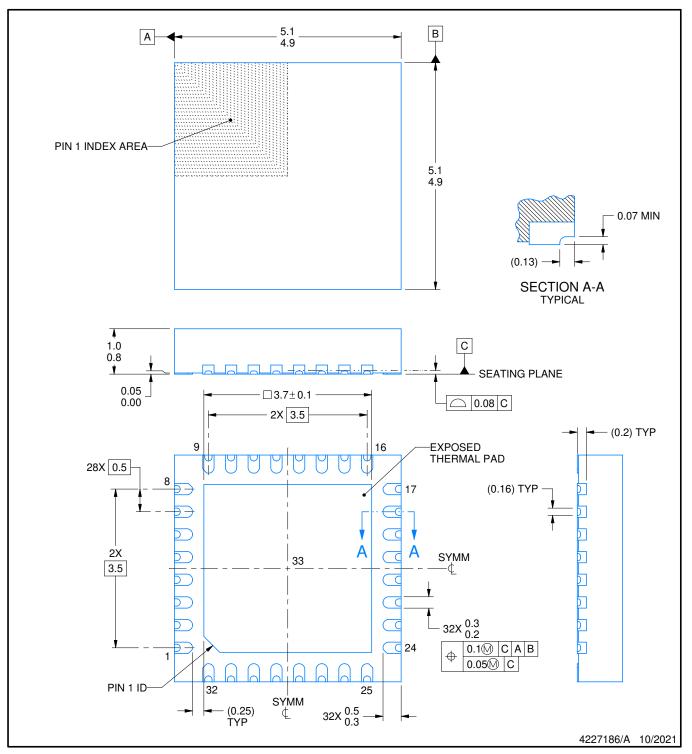

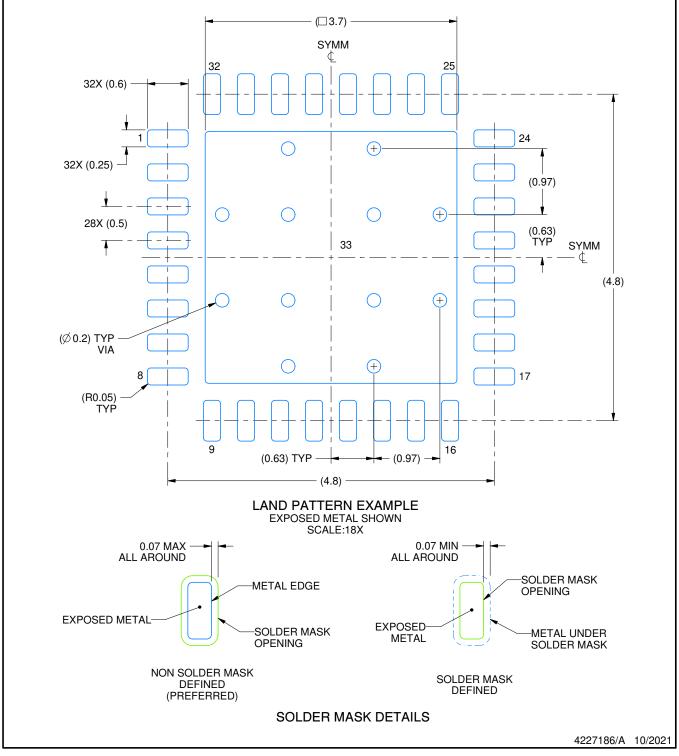

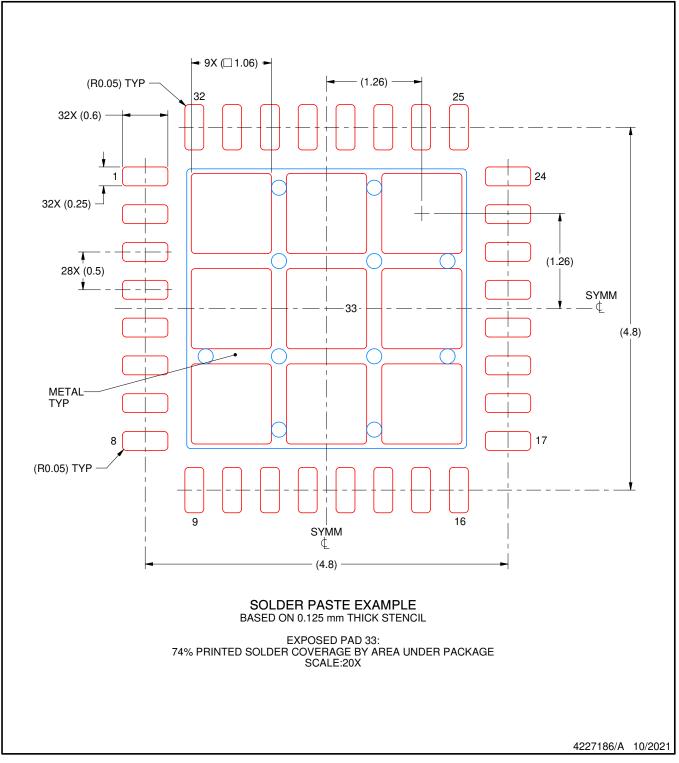

For the package drawing, please refer to RHB0032R at the end of the data sheet. (1)

(2) For the package drawing, please refer to RHB0032AA at the end of the data sheet.

(3) A = Analog, P = Power, G = Ground.

# 8 Specifications

# 8.1 Absolute Maximum Ratings

Voltages are with respect to GND (unless otherwise noted)<sup>(1)</sup>

|                                                  | PARAMETER                                                             | MIN  | MAX                   | UNIT |

|--------------------------------------------------|-----------------------------------------------------------------------|------|-----------------------|------|

|                                                  | IN to PGND                                                            | -0.3 | 40                    |      |

|                                                  | OUT to PGND                                                           | -0.3 | 20                    |      |

|                                                  | EN to AGND                                                            | -0.3 | VIN + 0.3             |      |

|                                                  | CSP to AGND                                                           | -0.3 | 20                    |      |

| Input voltage                                    | CSN to AGND                                                           | -0.3 | 20                    | V    |

|                                                  | BUS to AGND                                                           | -0.3 | 18                    |      |

|                                                  | RT/SYNC to AGND                                                       | -0.3 | 6                     |      |

|                                                  | CTRL1 or CTRL2 to AGND                                                | -0.3 | 6                     |      |

|                                                  | AGND to PGND                                                          | -0.3 | 0.3                   |      |

|                                                  | SW to PGND                                                            | -0.3 | VIN + 0.3             |      |

|                                                  | SW to PGND (less than 10 ns transients)                               | -3.5 | 40                    |      |

| Output voltage                                   | BOOT to SW                                                            | -0.3 | 6                     | V    |

|                                                  | VCC to AGND                                                           | -0.3 | 6                     |      |

|                                                  | LS_GD                                                                 | -0.3 | 18                    |      |

|                                                  | CC1 or CC2 to AGND                                                    | -0.3 | 7                     |      |

|                                                  | DP_IN, DM_IN to AGND                                                  | -0.3 | 7                     | V    |

| Voltago rango                                    | DP_OUT, DM_OUT to AGND (TPS25832-Q1 only)                             | -0.3 | 6                     |      |

| Voltage range                                    | FAULT, POL, LD_DET to AGND                                            | -0.3 | 6                     |      |

|                                                  | THERM_WARN, NTC to AGND (TPS25833-Q1 only)                            | -0.3 | 6                     |      |

|                                                  | ILIMIT or IMON to AGND                                                | -0.3 | 6                     |      |

| Pin positive source current, I <sub>VCC</sub>    | VCC Source Current                                                    |      | 5                     | mA   |

| Pin positive source current,<br>I <sub>SRC</sub> | CC1, CC2                                                              |      | Internally<br>Limited | А    |

| Pin positive sink current, I <sub>SNK</sub>      | CC1, CC2 (while applying VCONN)                                       |      | 1                     | А    |

| Pin positive sink current, I <sub>SNK</sub>      | FAULT, POL, LD_DET                                                    |      | Internally<br>Limited | •    |

|                                                  | THERM_WARN (TPS25833-Q1 only)                                         |      | Internally<br>Limited | A    |

| I/O current                                      | DP_IN to DP_OUT, or DM_IN to DM_OUT in SDP, CDP<br>(TPS25832-Q1 only) | -100 | 100                   | mA   |

|                                                  | DP_IN to DM_IN in DCP Auto Mode (TPS25833-Q1 only)                    | -35  | 35                    |      |

| TJ                                               | Junction temperature                                                  | -40  | 150                   | °C   |

| T <sub>stg</sub>                                 | Storage temperature                                                   | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 8.2 ESD Ratings

|                    |                                 |                                      |                                | VALUE                 | UNIT |

|--------------------|---------------------------------|--------------------------------------|--------------------------------|-----------------------|------|

|                    |                                 | Human body model (HBM), per AEC      | CQ100-002 <sup>(1)</sup>       | ±2000 <sup>(2)</sup>  |      |

|                    | Charged device model (CDM), per | Corner pins (1, 8, 9, 17, 25 and 32) | ±750 <sup>(3)</sup>            |                       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge         | AEC Q100-011                         | Other pins                     | ±750 <sup>(3)</sup>   | V    |

|                    |                                 | IEC 61000-4-2 contact discharge      | DP_IN, DM_IN, CC1 and CC2 pins | ±8000 <sup>(4)</sup>  |      |

|                    |                                 | IEC 61000-4-2 air-gap discharge      | DP_IN, DM_IN, CC1 and CC2 pins | ±15000 <sup>(4)</sup> |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

(2) The passing level per AEC-Q100 Classification H2.

(3) The passing level per AEC-Q100 Classification C5.

Surges per IEC61000-4-2, 1999 applied between DP\_IN, DM\_IN, CC1, CC2 and output ground of the TPS2583x-Q1 evaluation module. Addition 0.22u cap is needed on CCx pins.

#### 8.3 Recommended Operating Conditions

Voltages are with respect to GND (unless otherwise noted)

|                                 |                               |                                                                                      | MIN | NOM MAX            | UNIT |

|---------------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----|--------------------|------|

|                                 |                               | IN to PGND                                                                           | 4.5 | 36                 |      |

|                                 |                               | EN                                                                                   | 0   | VIN                |      |

|                                 |                               | VCC when driven from external regulator                                              | 0   | 5.5                |      |

| VI                              | Input voltage                 | DP_IN, DM_IN                                                                         | 0   | 3.6                |      |

| ٧I                              |                               | DP_OUT, DM_OUT (TPS25832-Q1 only)                                                    | 0   | 3.6                |      |

|                                 |                               | NTC (TPS25833-Q1 only)                                                               | 0   | VCC                | V    |

|                                 |                               | CTRL1, CTRL2                                                                         | 0   | VCC                |      |

|                                 |                               | RT/SYNC when driven by external clock                                                | 0   | VCC                |      |

| V <sub>PU</sub> Pull up voltage | Dull un velte re              | FAULT, LD_DET, POL                                                                   | 0   | VCC                |      |

|                                 | THERM_WARN (TPS25833-Q1 only) | 0                                                                                    | VCC |                    |      |

| Vo                              | Output voltage                | CSN/OUT                                                                              | 0   | 6.5                |      |

|                                 |                               | Buck regulator output current                                                        | 0   | 3.5                | А    |

| I <sub>O</sub>                  | Output current                | DP_IN to DP_OUT or DM_IN to DM_OUT Continuous current in SDP, CDP (TPS25832-Q1 only) | -30 | 30                 |      |

|                                 |                               | DP_IN to DM_IN Continuous current in BC1.2 DCP<br>Mode (TPS25833-Q1 only)            | -15 | 15                 | mA   |

| I <sub>SRC</sub>                | Source current                | CC1 or CC2 source current when supplying VCONN                                       |     | 250                |      |

|                                 | Sink current                  | FAULT, LD_DET, POL                                                                   |     | 10                 |      |

| I <sub>SNK</sub>                | Sink current                  | THERM_WARN (TPS25833-Q1 only)                                                        |     | 10                 |      |

| I <sub>I</sub>                  | Input current                 | Continuous current into the CSP pin                                                  |     | 200                | μA   |

| R <sub>EXT</sub>                | External resistnace           | R <sub>IMON</sub> , R <sub>ILIMIT</sub>                                              | 0   | 100                | kΩ   |

| TJ                              |                               | Operating junction temperature                                                       | -40 | 125 <sup>(1)</sup> | °C   |

(1) Operating at junction temperatures greater than 125°C is possible, however lifetime will be degraded.

#### 8.4 Thermal Information

|                               |                                              | TPS25           | TPS2583x-Q1      |      |  |  |

|-------------------------------|----------------------------------------------|-----------------|------------------|------|--|--|

| THERMAL METRIC <sup>(1)</sup> |                                              | RHB0032R (VQFN) | RHB0032AA (VQFN) | UNIT |  |  |

|                               |                                              | 32 PINS         | 32 PINS          |      |  |  |

| R <sub>0JA</sub>              | Junction-to-ambient thermal resistance       | 28.7            | 29.4             | °C/W |  |  |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 17.6            | 18.6             | °C/W |  |  |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 7.2             | 9.7              | °C/W |  |  |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.2             | 0.2              | °C/W |  |  |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 7.2             | 9.7              | °C/W |  |  |

| R <sub>0JC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 1               | 2.3              | °C/W |  |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **8.5 Electrical Characteristics**

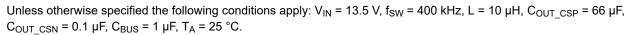

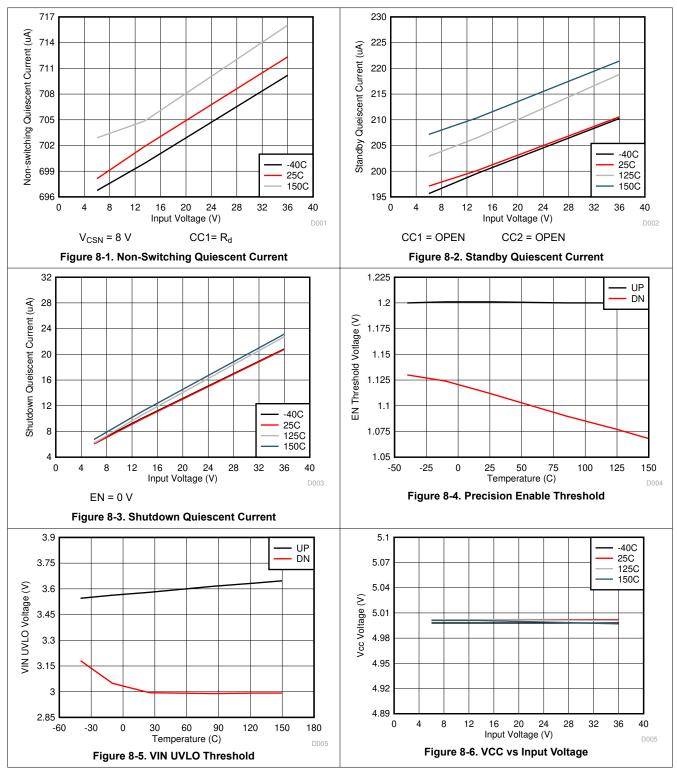

Limits apply over the junction temperature (T<sub>J</sub>) range of -40°C to +150°C;  $V_{IN}$  = 13.5 V,  $f_{SW}$  =400 kHz,  $C_{VCC}$  = 2.2 µF,  $R_{SNS}$  = 15 mΩ,  $R_{IMON}$  = 13 kΩ,  $R_{ILIMIT}$ = 13 kΩ,  $R_{SET}$ = 300 Ω unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only.

| PARAMETER                                  |                                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                     | MIN   | TYP   | MAX   | UNIT |

|--------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY VOLTATE                             | (IN PIN)                                              |                                                                                                                                                                                                                                                                                                                     |       |       |       |      |

| V <sub>IN</sub>                            | Operating input voltage range                         |                                                                                                                                                                                                                                                                                                                     | 4.5   |       | 36    | V    |

| I <sub>Q</sub>                             | Operating quiescent current (non switching)           | $V_{EN/UVLO} = V_{IN}$ , CTRL1 = CTRL2 =<br>$V_{CC}$ , $V_{CSN} = 8V$ , CC1 or CC2 = R <sub>D</sub> ,<br>CC2 or CC1 = open                                                                                                                                                                                          |       | 700   | 990   | μA   |

| I <sub>Q-SB</sub>                          | Standby quiescent current                             | V <sub>EN/UVLO</sub> = V <sub>IN</sub> , CTRL1 = CTRL2 =<br>V <sub>CC</sub> , CC1 and CC2 = open                                                                                                                                                                                                                    |       |       | 290   | μA   |

| I <sub>SD</sub>                            | Shutdown quiescent current;<br>measured at IN pin.    | EN= 0                                                                                                                                                                                                                                                                                                               |       | 10    | 16    | μA   |

| ENABLE and UVL                             | O (EN/UVLO PIN)                                       | 1                                                                                                                                                                                                                                                                                                                   | 1     |       | I     |      |

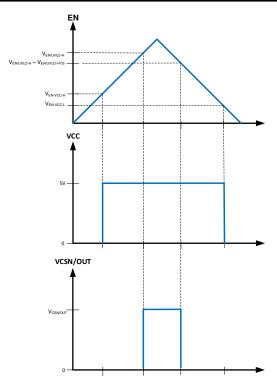

| V <sub>EN/UVLO_VCC_H</sub>                 | EN/UVLO input level required to turn on internal LDO  | V <sub>EN/UVLO</sub> rising threshold                                                                                                                                                                                                                                                                               |       |       | 1.14  | V    |

| V <sub>EN/UVLO_VCC_L</sub>                 | EN/UVLO input level required to turn off internal LDO | V <sub>EN/UVLO</sub> falling threshold                                                                                                                                                                                                                                                                              | 0.3   |       |       | V    |

| V <sub>EN/UVLO_H</sub>                     | EN/UVLO input level required to turn on state machine | V <sub>EN/UVLO</sub> rising threshold                                                                                                                                                                                                                                                                               | 1.140 | 1.200 | 1.260 | V    |

| V <sub>EN/UVLO_HYS</sub>                   | Hysteresis                                            | V <sub>EN/UVLO</sub> falling threshold                                                                                                                                                                                                                                                                              |       | 90    |       | mV   |

| ILKG_EN/UVLO                               | Enable input leakage current                          | V <sub>EN/UVLO</sub> = 3.3 V                                                                                                                                                                                                                                                                                        |       | 0.5   |       | uA   |

| INTERNAL LDO                               |                                                       |                                                                                                                                                                                                                                                                                                                     |       |       |       |      |

| V <sub>BOOT_UVLO</sub>                     | Bootstrap voltage UVLO threshold                      |                                                                                                                                                                                                                                                                                                                     |       | 2.2   |       | V    |

| V <sub>CC</sub>                            | Internal LDO output voltage appearing on VCC pin      | $6 \text{ V} \le \text{V}_{\text{IN}} \le 36 \text{ V}$                                                                                                                                                                                                                                                             | 4.75  | 5     | 5.25  | V    |

| V <sub>CC_UVLO_R</sub>                     | Rising UVLO threshold                                 |                                                                                                                                                                                                                                                                                                                     | 3.4   | 3.6   | 3.8   | V    |

| V <sub>CC_UVLO_HYS</sub>                   | Hysteresis                                            |                                                                                                                                                                                                                                                                                                                     |       | 600   |       | mV   |

| CURRENT LIMIT                              | OLTAGE (CSP - CSN/OUT PINS) TO A                      | CTIVATE BUCK AVG CURRENT LIMIT                                                                                                                                                                                                                                                                                      | ING   |       |       |      |

| (V <sub>CSP</sub> – V <sub>CSN/OUT</sub> ) | Current limit voltage buck regulator control loop     | $ \begin{array}{c} V_{CSN} = 5 \ V, \ R_{SET} = 300 \ \Omega, \ R_{ILIMIT} = \\ 13 \ k\Omega, \ R_{IMON} = 13 \ k\Omega, \ -40^{\circ}C \leq T_{J} \leq \\ 125^{\circ}C \end{array} \qquad $ |       | 46    | 48.5  | mV   |

| (V <sub>CSP</sub> – V <sub>CSN/OUT</sub> ) | Current limit voltage buck regulator control loop     | $V_{CSN} = 5 V, R_{SET} = 300 \Omega, R_{ILIMIT} = 13 k\Omega, R_{IMON} = 13 k\Omega, -40^{\circ}C \le T_{J} \le 150^{\circ}C$                                                                                                                                                                                      | 42.5  | 46    | 49.5  | mV   |

Limits apply over the junction temperature (T<sub>J</sub>) range of -40°C to +150°C;  $V_{IN}$  = 13.5 V,  $f_{SW}$  =400 kHz,  $C_{VCC}$  = 2.2 µF,  $R_{SNS}$  = 15 mΩ,  $R_{IMON}$  = 13 kΩ,  $R_{ILIMIT}$ = 13 kΩ,  $R_{SET}$ = 300 Ω unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only.

|                                            | PARAMETER                                                                | TEST CONDITIONS                                                                                                                                                                                                                           | MIN      | TYP  | MAX   | UNIT |

|--------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|------|

| (V <sub>CSP</sub> – V <sub>CSN/OUT</sub> ) | Current limit voltage buck regulator control loop                        | $ \begin{array}{l} V_{CSN} = 5 \; V, \; R_{SET} = 300 \; \Omega, \; R_{ILIMIT} = \\ 26.1 \; k\Omega, \; R_{IMON} = 13 \; k\Omega, \; \text{-}40^\circ C \leq T_J \leq \\ 125^\circ C \end{array} $                                        | 20       | 22.5 | 25    | mV   |

| (V <sub>CSP</sub> – V <sub>CSN/OUT</sub> ) | Current limit voltage buck regulator control loop                        | V <sub>CSN</sub> = 5 V, R <sub>SET</sub> = 300 Ω, R <sub>ILIMIT</sub> =<br>26.1 kΩ, R <sub>IMON</sub> = 13 kΩ, -40°C ≤ T <sub>J</sub> ≤<br>150°C                                                                                          | 19       | 22.5 | 26    | mV   |

| CURRENT LIMIT                              | OLTAGE (CSP - CSN/OUT PINS) TO A                                         | CTIVATE EXTERNAL NFET CURRENT                                                                                                                                                                                                             | LIMITING |      |       |      |

| (V <sub>CSP</sub> – V <sub>CSN/OUT</sub> ) | Current limit voltage NFET control loop                                  | $ \begin{array}{l} V_{CSN} = 5 \; V, \; R_{SET} = 300 \; \Omega, \; R_{ILIMIT} = \\ 6.8 \; k\Omega, \; R_{IMON} = 13 \; k\Omega, \; \text{-}40^\circ C \leq T_J \leq \\ 125^\circ C \end{array} $                                         | 40       | 43   | 46    | mV   |

| $(V_{CSP} - V_{CSN/OUT})$                  | Current limit voltage NFET control loop                                  |                                                                                                                                                                                                                                           | 38.5     | 43   | 47.5  | mV   |

| (V <sub>CSP</sub> – V <sub>CSN/OUT</sub> ) | Current limit voltage NFET control loop                                  | t limit voltage NFET control loop $V_{CSN} = 5 \text{ V}, \text{ R}_{SET} = 300 \Omega, \text{ R}_{ILIMIT} = 13.7 \text{ k}\Omega, \text{ R}_{IMON} = 13 \text{ k}\Omega, -40^{\circ}\text{C} \leq \text{T}_{J} \leq 125^{\circ}\text{C}$ |          |      |       | mV   |

| $(V_{CSP} - V_{CSN/OUT})$                  | Current limit voltage NFET control loop                                  | $ \begin{array}{l} V_{CSN} = 5 \; V, \; R_{SET} = 300 \; \Omega, \; R_{ILIMIT} = \\ 13.7 \; k\Omega, \; R_{IMON} = 13 \; k\Omega, \; \text{-}40^\circ C \leq T_J \leq \\ 150^\circ C \end{array} $                                        | 17       | 21   | 25    | mV   |

| CURRENT LIMIT -                            | BUCK REGULATOR PEAK CURRENT                                              | LIMIT                                                                                                                                                                                                                                     |          |      | •     |      |

| I <sub>L-SC-HS</sub>                       | High-side current limit                                                  |                                                                                                                                                                                                                                           | 4.6      | 5.4  | 6.2   | А    |

| I <sub>L-SC-LS</sub>                       | Low-side current limit                                                   |                                                                                                                                                                                                                                           | 3.5      | 4    | 4.5   | А    |

| I <sub>L-NEG-LS</sub>                      | Low-side negative current limit                                          |                                                                                                                                                                                                                                           | -3.1     | -2.1 | -1.3  | А    |

| CABLE COMPENS                              | SATION VOLTAGE                                                           | · · · ·                                                                                                                                                                                                                                   |          |      |       |      |

| V <sub>IMON</sub>                          | Cable compensation voltage                                               | $      (V_{CSP} - V_{CSN}) = 46 \text{ mV},  \text{R}_{\text{SET}} = 300  \Omega, \\ \text{R}_{\text{ILIMIT}} = 13  \text{k} \Omega,  \text{R}_{\text{IMON}} = 13  \text{k} \Omega $                                                      | 0.935    | 1    | 1.065 | V    |

| V <sub>IMON</sub>                          | Cable compensation voltage                                               | $      (V_{CSP} - V_{CSN}) = 23 \text{ mV},  \text{R}_{SET} = 300  \Omega, \\ \text{R}_{\text{ILIMIT}} = 13  \text{k}\Omega,  \text{R}_{\text{IMON}} = 13  \text{k}\Omega $                                                               | 0.435    | 0.5  | 0.565 | V    |

| V <sub>IMON</sub>                          | Cable compensation voltage (internal clamp)                              | $      (V_{CSP} - V_{CSN}) = 46 \text{ mV},  \text{R}_{\text{SET}} = 300  \Omega, \\ \text{R}_{\text{ILIMIT}} = 13  \text{k} \Omega,  \text{R}_{\text{IMON}} = \text{open} $                                                              |          | 1.8  |       | V    |

| BUCK OUTPUT V                              | OLTAGE (CSN/OUT PIN)                                                     | · · · · · ·                                                                                                                                                                                                                               |          |      |       |      |

| V <sub>CSN/OUT</sub>                       | Output voltage                                                           | CC1 or CC2 pulldown resistance = $R_d$ ,<br>$R_{IMON} = 0 \Omega$ , $R_{ILIMIT} = 0 \Omega$                                                                                                                                               | 5.05     | 5.10 | 5.15  | V    |

| V <sub>CSN/OUT</sub>                       | Output voltage accuracy                                                  | CC1 or CC2 pulldown resistance = $R_d$ ,<br>$R_{IMON} = 0 \Omega$ , $R_{ILIMIT} = 0 \Omega$                                                                                                                                               | -1       |      | 1     | %    |

| V <sub>CSN/OUT_OV</sub>                    | Overvoltage level on CSN/OUT pin<br>which buck regulator stops switching | V <sub>CSN/OUT</sub> rising                                                                                                                                                                                                               | 7.1      | 7.5  | 7.9   | V    |

| V <sub>CSN/OUT_OV_HYS</sub>                | Hysteresis                                                               |                                                                                                                                                                                                                                           |          | 500  |       | mV   |

| V <sub>HC</sub>                            | CSN / OUT pin voltage required to trigger short circuit hiccup mode      |                                                                                                                                                                                                                                           |          | 2    |       | V    |

| V <sub>DROP</sub>                          | Dropout voltage(V <sub>IN</sub> -V <sub>OUT</sub> )                      | $V_{IN} = V_{OUT} + V_{DROP}, V_{OUT} = 5.1V,$<br>$I_{OUT} = 3A$                                                                                                                                                                          |          | 150  |       | mV   |

| BUCK REGULATO                              | R INTERNAL RESISTANCE                                                    | · · · · ·                                                                                                                                                                                                                                 |          |      | I     |      |

| R <sub>DS-ON-HS</sub>                      | High-side MOSFET ON-resistance                                           | Load = 3 A, T <sub>J</sub> = 25°C                                                                                                                                                                                                         |          | 40   | 45    | mΩ   |

| R <sub>DS-ON-HS</sub>                      | High-side MOSFET ON-resistance                                           | Load = 3 A, -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                                                                                                                                |          | 40   | 68    | mΩ   |

| R <sub>DS-ON-HS</sub>                      | High-side MOSFET ON-resistance                                           | Load = 3 A, -40°C ≤ T <sub>J</sub> ≤ 150°C                                                                                                                                                                                                |          | 40   | 75    | mΩ   |

| R <sub>DS-ON-LS</sub>                      | Low-side MOSFET ON-resistance                                            | Load = 3 A, T <sub>J</sub> = 25C                                                                                                                                                                                                          |          | 35   | 41    | mΩ   |

| R <sub>DS-ON-LS</sub>                      | Low-side MOSFET ON-resistance                                            | Load = 3 A, -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                                                                                                                                                |          | 35   | 60    | mΩ   |

Copyright © 2022 Texas Instruments Incorporated

Limits apply over the junction temperature (T<sub>J</sub>) range of -40°C to +150°C;  $V_{IN}$  = 13.5 V,  $f_{SW}$  =400 kHz,  $C_{VCC}$  = 2.2 µF,  $R_{SNS}$  = 15 m $\Omega$ ,  $R_{IMON}$  = 13 k $\Omega$ ,  $R_{ILIMIT}$ = 13 k $\Omega$ ,  $R_{SET}$ = 300  $\Omega$  unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only.

|                             | PARAMETER                                                 | TEST CONDITIONS                                                                                                   | MIN  | TYP | MAX  | UNIT |

|-----------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| R <sub>DS-ON-LS</sub>       | Low-side MOSFET ON-resistance                             | Load = 3 A, -40°C ≤ T <sub>J</sub> ≤ 150°C                                                                        |      | 35  | 68   | mΩ   |

| NFET GATE DRIV              | E (LS_GD PIN)                                             | · · ·                                                                                                             |      |     |      |      |

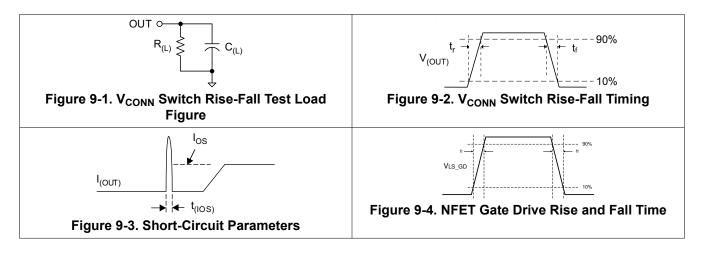

| V <sub>LS_GD</sub>          | NFET gate drive output voltage                            | $V_{CSN/OUT}$ = 5.1 V, $C_G$ = 1000 pF (see Figure 9-4)                                                           | 9.5  | 11  | 12.5 | V    |

| I <sub>LS_DR_SRC</sub>      | NFET gate drive output source current                     | V <sub>CSN/OUT</sub> = 5.1 V, C <sub>G</sub> = 1000 pF                                                            | 2    | 3   | 4    | μA   |

| ILS_DR_SNK                  | NFET gate drive output sink current                       | V <sub>CSN/OUT</sub> = 5.1 V, C <sub>G</sub> = 1000 pF                                                            | 20   | 35  | 50   | μA   |

| V <sub>LS_GD_UVLO_R</sub>   | V <sub>CSN/OUT</sub> rising threshold for LS_GD operation | V <sub>CSN/OUT</sub> rising                                                                                       | 2.85 | 3   | 3.15 | V    |

| V <sub>LS_GD_UVLO_HYS</sub> | Hysteresis                                                |                                                                                                                   |      | 80  |      | mV   |

| BUS DISCHARGE               | (BUS PIN)                                                 | · · · · ·                                                                                                         |      |     | I    |      |

| R <sub>BUS_DCHG</sub>       | BUS discharge resistance                                  | V <sub>BUS</sub> = 4 V                                                                                            | 250  | 320 | 550  | Ω    |

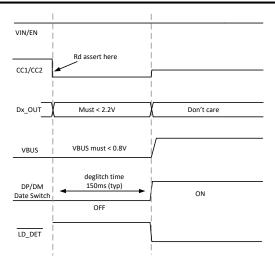

| V <sub>BUS_NO_DCHG</sub>    | Falling threshold for VBUS not discharged                 |                                                                                                                   |      |     | 0.8  | V    |

| R <sub>BUS_DCHG_BLEED</sub> | BUS bleed resistance                                      | $V_{BUS}$ = 4 V, No sink termination on CC lines, Time > t <sub>W_BUS_DCHG</sub>                                  | 100  | 130 | 200  | kΩ   |

| V <sub>BUS_OV</sub>         | Rising threshold for BUS pin<br>overvoltage protection    | V <sub>BUS</sub> rising                                                                                           | 6.6  | 7   | 7.3  | V    |

| V <sub>BUS_OV_HYS</sub>     | Hysteresis                                                |                                                                                                                   |      | 180 |      | mV   |

| R <sub>BUS_DCHG_18V</sub>   | Discharge resistance for BUS                              | V <sub>BUS</sub> = 18V, measure leakage current                                                                   |      | 29  |      | kΩ   |

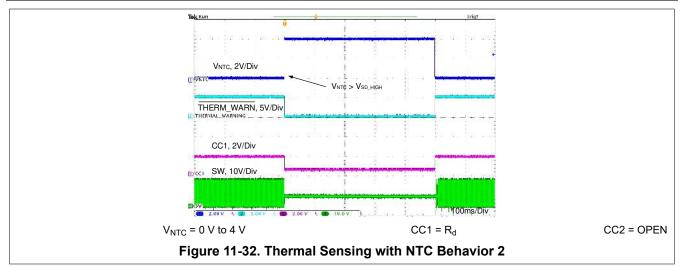

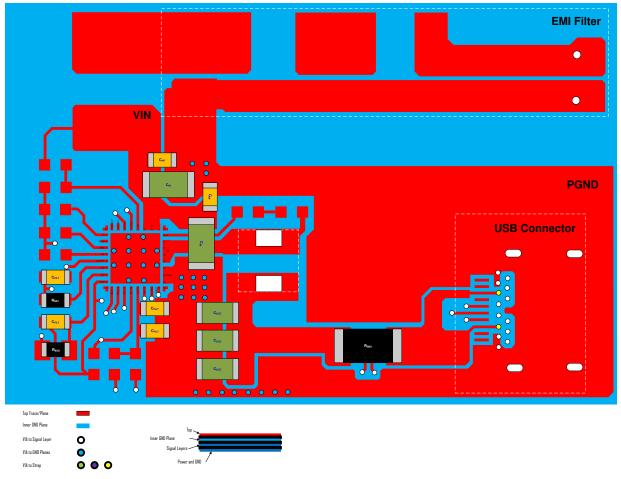

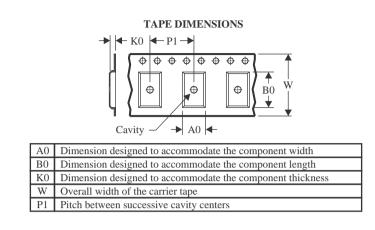

| R <sub>BUS_DCHG_8V</sub>    | Discharge resistance for BUS                              | V <sub>BUS</sub> = 8V, measure leakage current                                                                    |      | 35  |      | kΩ   |