Data Sheet September 1998 File Number 2924.4

## 250MHz Video Buffer

The HA-5033 is a unity gain monolithic IC designed for any application requiring a fast, wideband buffer. Featuring a bandwidth of 250MHz and outstanding differential phase/gain characteristics, this high performance voltage follower is an excellent choice for video circuit design. Other features, which include a minimum slew rate of 1000V/µs and high output drive capability, make the HA-5033 applicable for line driver and high speed data conversion circuits.

The high performance of this product is a result of the Intersil Dielectric Isolation process. A major feature of this process is that it produces both PNP and NPN high frequency transistors which makes wide bandwidth designs, such as the HA-5033, practical. Alternative process methods typically produce a lower AC performance.

# **Ordering Information**

| PART NUMBER<br>(BRAND) | TEMP.<br>RANGE (°C) | PACKAGE          | PKG.<br>NO. |

|------------------------|---------------------|------------------|-------------|

| HA2-5033-2             | -55 to 125          | 12 Pin Metal Can | T12.C       |

| HA2-5033-5             | 0 to 75             | 12 Pin Metal Can | T12.C       |

| HA3-5033-5             | 0 to 75             | 8 Ld PDIP        | E8.3        |

| HA4P5033-5             | 0 to 75             | 20 Ld PLCC       | N20.35      |

| HA9P5033-5<br>(H50335) | 0 to 60<br>(Note 3) | 8 Ld PSOP        | M8.15A      |

### **Features**

| Differential Phase Error 0.02 Degrees |

|---------------------------------------|

| Differential Gain Error               |

| • High Slew Rate                      |

| Wide Bandwidth (Small Signal)         |

| Wide Power Bandwidth DC to 17.5MHz    |

| • Fast Rise Time                      |

| • High Output Drive                   |

| Wide Power Supply Range ±5V to ±16V   |

| Replace Costly Hybrids                |

# **Applications**

- · Video Buffer

- · High Frequency Buffer

- · Isolation Buffer

- · High Speed Line Driver

- · Impedance Matching

- · Current Boosters

- High Speed A/D Input Buffers

- · Related Literature

- AN548, Designer's Guide for HA-5033

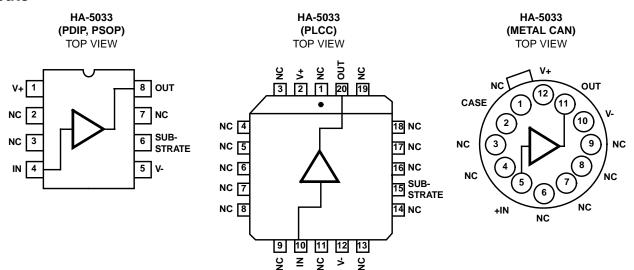

## **Pinouts**

### **Absolute Maximum Ratings**

| Voltage Between V+ and V- Pins               | 40V      |

|----------------------------------------------|----------|

| DC Input Voltage                             | V+ to V- |

| Output Current (Peak) (50ms On/1 Second Off) | ±200mA   |

| ESD Rating                                   |          |

| Library Destrict Medial (Destrict)           | 00001    |

#### Human Body Model (Per MIL-STD-883 Method 3015.7) . . . . 2000V

### **Operating Conditions**

| Temperature Ranges     |               |

|------------------------|---------------|

| HA-5033-2              | 55°C to 125°C |

| HA-5033-5 (Note 3)     |               |

| HA0P5033-5 (Notes 1 3) | -40°C to 60°C |

### **Thermal Information**

| Thermal Resistance (Typical, Note 2)                                    | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ ( $^{o}C/W$ ) |

|-------------------------------------------------------------------------|----------------------|-----------------------------|

| Metal Can Package                                                       | 65                   | 34                          |

| PDIP Package                                                            | 96                   | N/A                         |

| PSOP Package (Note 4)                                                   | 129                  | N/A                         |

| PLCC Package                                                            | 80                   | N/A                         |

| Maximum Junction Temperature (Note 1)                                   |                      | 175 <sup>0</sup> C          |

| Maximum Junction Temperature (Plastic P                                 | ackages)             | 150 <sup>0</sup> C          |

| Maximum Storage Temperature Range                                       | 65                   | 5°C to 150°C                |

| Maximum Lead Temperature (Soldering 10 (PSOP and PLCC - Lead Tips Only) | Os)                  | 300°C                       |

|                                                                         |                      |                             |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

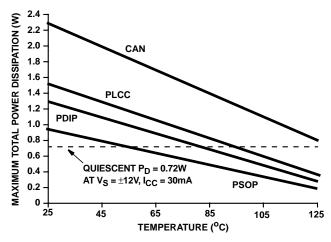

- Maximum power dissipation, including load conditions, must be designed to maintain the maximum junction temperature below 175°C for the metal can package, and below 150°C for the plastic packages (See Figure 5.).

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

- 3. Maximum operating temperature in the PSOP package is limited to 60°C, for V<sub>SUPPLY</sub> = ±12V to prevent the junction temperature from exceeding 150°C. The maximum operating temperature may have to be derated further, depending on the output load condition. The operating temperature may be increased if the HA9P5033 is operated at lower V<sub>SUPPLY</sub>. For example, the quiescent operating temperature may be increased to 75°C by operating at V<sub>SUPPLY</sub> ≤ ±9.7V. See Figure 5 for more information.

- Direct attach of the PSOP copper slug to copper area on the PCB can reduce the θ<sub>JA</sub> value to <100°C/W. Consult the Intersil Application Group for more information.

# **Electrical Specifications** $V_{SUPPLY} = \pm 12V$ , $R_S = 50\Omega$ , $R_L = 100\Omega$ , $C_L = 10pF$ , Unless Otherwise Specified

| PARAMETER                     | TEST<br>CONDITIONS                   | TEMP. | HA-5033-2 |      |     | HA-5033-5 |      |     |                    |

|-------------------------------|--------------------------------------|-------|-----------|------|-----|-----------|------|-----|--------------------|

|                               |                                      |       | MIN       | TYP  | MAX | MIN       | TYP  | MAX | UNITS              |

| INPUT CHARACTERISTICS         |                                      | •     |           | •    |     |           | •    |     |                    |

| Offset Voltage                |                                      | 25    | -         | 5    | 15  | -         | 5    | 15  | mV                 |

|                               |                                      | Full  | -         | 6    | 25  | -         | 6    | 25  | mV                 |

| Average Offset Voltage Drift  |                                      | Full  | -         | 33   | -   | -         | 33   | -   | μV/ <sup>o</sup> C |

| Bias Current                  |                                      | 25    | -         | 20   | 35  | -         | 20   | 35  | μА                 |

|                               |                                      | Full  | -         | 30   | 50  | -         | 30   | 50  | μА                 |

| Input Resistance              |                                      | 25    | -         | 3    | -   | -         | 3    | -   | ΜΩ                 |

| Input Capacitance             |                                      | 25    | -         | 1.6  | -   | -         | 1.6  | -   | pF                 |

| Input Noise Voltage           | 10Hz to 100MHz                       | 25    | -         | 20   | -   | -         | 20   | -   | μV <sub>P-P</sub>  |

| TRANSFER CHARACTERISTIC       | CS                                   |       |           | •    |     | ·         |      |     |                    |

| Voltage Gain                  | $R_L = 100\Omega$                    | 25    | 0.93      | -    | -   | 0.93      | -    | -   | V/V                |

|                               | $R_L = 1k\Omega$                     | 25    | 0.93      | 0.99 | -   | 0.93      | 0.99 | -   | V/V                |

|                               | $R_L = 100\Omega$                    | Full  | 0.92      | -    | -   | 0.92      | -    | -   | V/V                |

| -3dB Bandwidth                |                                      | 25    | -         | 250  | -   | -         | 250  | -   | MHz                |

| OUTPUT CHARACTERISTICS        |                                      |       |           | 1    |     |           | 1    |     | 1                  |

| Output Voltage Swing          | $R_L = 100\Omega$                    | Full  | ±8        | ±10  | -   | ±8        | ±10  | -   | V                  |

|                               | $R_L = 1k\Omega$ , $V_S = \pm 15V$   | Full  | ±11       | ±12  | -   | ±11       | ±12  | -   | V                  |

| Output Current                |                                      | 25    | ±80       | ±100 | -   | ±80       | ±100 | -   | mA                 |

| Output Resistance             |                                      | 25    | -         | 8    | -   | -         | 8    | -   | Ω                  |

| Full Power Bandwidth          | $V_{OUT} = 1V_{RMS}, R_L = 1k\Omega$ | 25    | -         | 146  | -   | -         | 146  | -   | MHz                |

| Full Power Bandwidth (Note 5) |                                      | 25    | 15.9      | 17.5 | -   | 15.9      | 17.5 | -   | MHz                |

| TRANSIENT RESPONSE            |                                      |       |           |      |     |           |      | -   |                    |

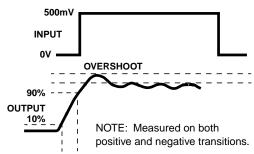

| Rise Time                     | V <sub>OUT</sub> = 500mV             | 25    | -         | 4.6  | -   | -         | 4.6  | -   | ns                 |

| Propagation Delay             |                                      | 25    | -         | 1    | -   | -         | 1    | -   | ns                 |

| Overshoot                     |                                      | 25    | -         | 3    | -   | -         | 3    | -   | %                  |

| Slew Rate (Note 5)            |                                      | 25    | 1         | 1.1  | -   | 1         | 1.1  | -   | V/ns               |

|                                   | TEST                                          | TEMP. | HA-5033-2 |      |     | HA-5033-5 |      |     |        |

|-----------------------------------|-----------------------------------------------|-------|-----------|------|-----|-----------|------|-----|--------|

| PARAMETER                         | CONDITIONS                                    | (°C)  | MIN       | TYP  | MAX | MIN       | TYP  | MAX | UNITS  |

| Settling Time to 0.1%             |                                               | 25    | -         | 50   | -   | -         | 50   | -   | ns     |

| Differential Phase Error (Note 6) |                                               | 25    | -         | 0.02 | -   | -         | 0.02 | -   | Degree |

| Differential Gain Error (Note 6)  |                                               | 25    | -         | 0.03 | -   | -         | 0.03 | -   | %      |

| POWER SUPPLY CHARACTERIS          | STICS                                         |       |           |      |     |           |      |     |        |

| Supply Current                    |                                               | 25    | -         | 21   | 25  | -         | 21   | 25  | mA     |

|                                   |                                               | Full  | -         | 21   | 30  | -         | 21   | 30  | mA     |

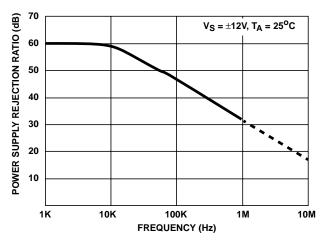

| Power Supply Rejection Ratio      |                                               | Full  | 54        | -    | -   | 54        | -    | -   | dB     |

| Harmonic Distortion               | V <sub>IN</sub> = 1V <sub>RMS</sub> at 100kHz | 25    | -         | <0.1 | -   | -         | <0.1 | -   | %      |

#### NOTES:

- 5.  $V_{SUPPLY} = \pm 15V$ ,  $V_{OUT} = \pm 10V$ ,  $R_L = 1k\Omega$ .

- 6. Differential gain and phase error are nonlinear signal distortions found in video systems and are defined as follows: Differential gain error is defined as the change in amplitude at the color subcarrier frequency as the picture signal is varied from blanking to white level. Differential phase error is defined as the change in the phase of the color subcarrier as the picture signal is varied from blanking to white level. R<sub>L</sub> = 300Ω.

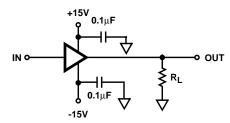

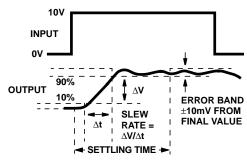

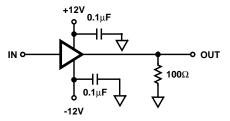

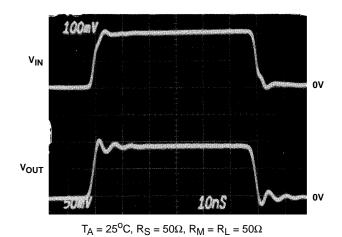

## Test Circuits and Waveforms

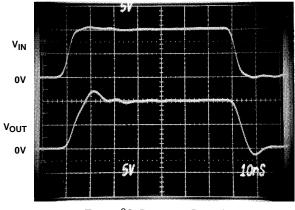

FIGURE 1. SLEW RATE AND SETTLING TIME

FIGURE 3. SETTLING TIME AND SLEW RATE

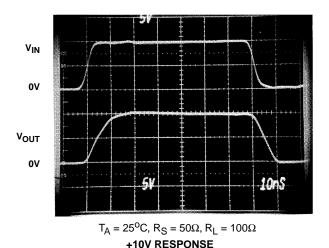

**FIGURE 2. TRANSIENT RESPONSE**

FIGURE 4. RISE TIME AND OVERSHOOT

$T_A = 25^{\circ}C$ ,  $R_S = 50\Omega$ ,  $R_L = 1k\Omega$ +10V RESPONSE

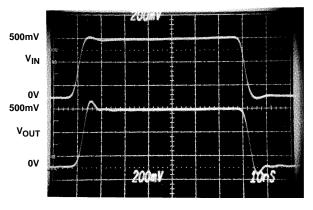

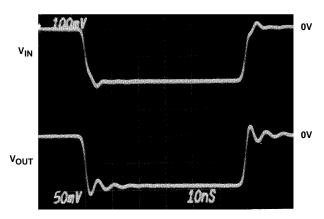

## Test Circuits and Waveforms (Continued)

$T_A = 25^{\circ}C$ ,  $R_S = 50\Omega$ ,  $R_L = 100\Omega$

**PULSE RESPONSE**

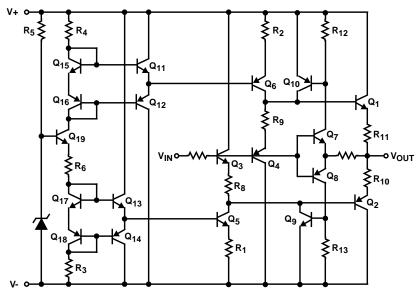

## Schematic Diagram

# Application Information

## **Layout Considerations**

The wide bandwidth of the HA-5033 necessitates that high frequency circuit layout procedures be followed. Failure to follow these guidelines can result in marginal performance.

Probably the most crucial of the RF/video layout rules is the use of a ground plane. A ground plane provides isolation and minimizes distributed circuit capacitance and inductance which will degrade high frequency performance. This ground plane shielding can also incorporate the metal case of the HA-5033 since pin #2 is internally tied to the package. This feature allows the user to make metal to metal contact between the ground plane and the package, which extends shielding, provides additional heat sinking and eliminates the use of a socket, IC sockets contribute inter-lead capacitance which limits device bandwidth and should be avoided.

For the PDIP, pin 6 can be tied to either supply, grounded, or simply not used. But to optimize device performance and improve isolation, it is recommended that this pin be grounded.

Other considerations are proper power supply bypassing and keeping the input and output connections as short as possible which minimizes distributed capacitance and reduces board space.

## **Power Supply Decoupling**

For optimum device performance, it is recommended that the positive and negative power supplies be bypassed with capacitors to ground. Ceramic capacitors ranging in value from  $0.01\mu F$  to  $0.1\mu F$  will minimize high frequency variations in supply voltage. Solid tantalum capacitors  $1\mu F$  or larger will optimize low frequency performance.

It is also recommended that the bypass capacitors be connected close to the HA-5033 (preferably directly to the supply pins).

Figure 5 is based on:

$$P_{DMAX} = \frac{T_{JMAX} - T_{A}}{\theta_{JA}}$$

Where: T<sub>JMAX</sub> = Maximum Junction Temperature of the Device

T<sub>A</sub> = Ambient Temperature

$\theta_{JA}$  = Junction to Ambient Thermal Resistance

FIGURE 5. MAXIMUM POWER DISSIPATION vs

TEMPERATURE

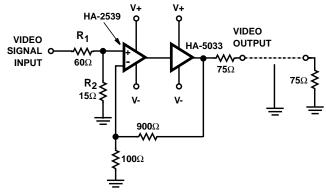

# Typical Applications (Also see Application Note AN548)

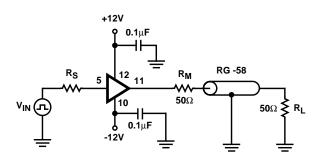

FIGURE 6. VIDEO COAXIAL LINE DRIVER  $50\Omega$  SYSTEM

FIGURE 7. VIDEO GAIN BLOCK

$\boldsymbol{V}_{O} \, = \, \boldsymbol{V}_{IN} \Bigg[ \frac{\boldsymbol{R}_{L}}{\boldsymbol{R}_{L} + \boldsymbol{R}_{M}} \Bigg] \, = \, \bigg[ \frac{1}{2} \bigg] \boldsymbol{V}_{IN}$

$$T_A = 25^{o}C, R_S = 50\Omega, R_M = R_L = 50\Omega$$

$$\boldsymbol{V}_O \; = \; \boldsymbol{V}_{IN} \! \left[ \frac{\boldsymbol{R}_L}{\boldsymbol{R}_L + \boldsymbol{R}_M} \right] = \left[ \frac{1}{2} \right] \! \boldsymbol{V}_{IN}$$

#### **NEGATIVE PULSE RESPONSE**

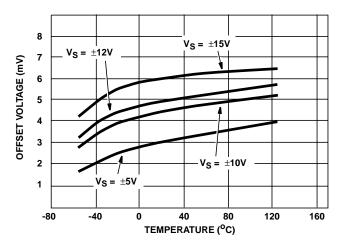

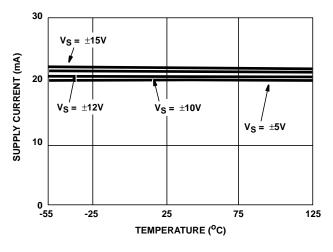

# **Typical Performance Curves**

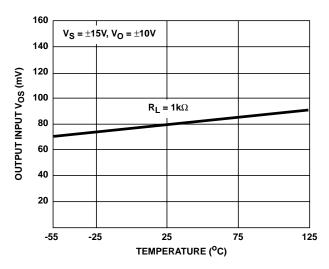

FIGURE 8. INPUT OFFSET VOLTAGE vs TEMPERATURE

FIGURE 10. SUPPLY CURRENT vs TEMPERATURE

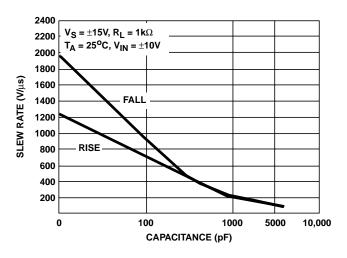

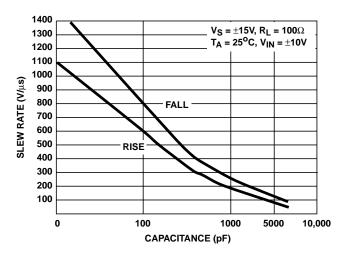

FIGURE 12. SLEW RATE vs LOAD CAPACITANCE

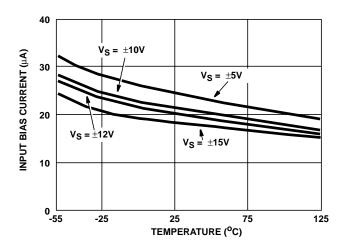

FIGURE 9. INPUT BIAS CURRENT vs TEMPERATURE

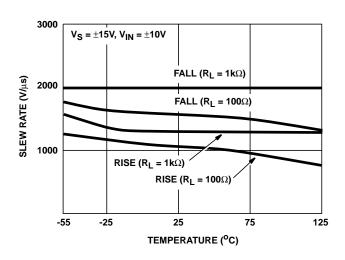

FIGURE 11. SLEW RATE vs TEMPERATURE

FIGURE 13. SLEW RATE vs LOAD CAPACITANCE

# Typical Performance Curves (Continued)

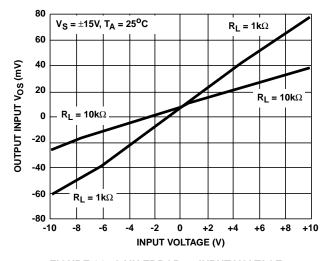

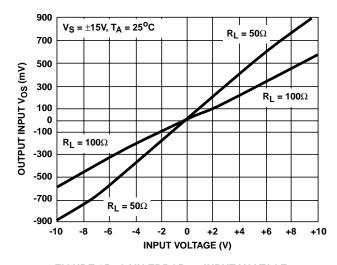

FIGURE 14. GAIN ERROR vs INPUT VOLTAGE

FIGURE 16. GAIN ERROR vs TEMPERATURE

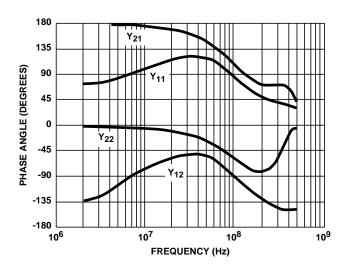

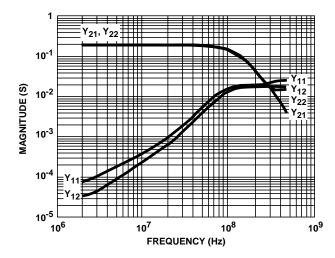

FIGURE 18. Y - PARAMETERS PHASE vs FREQUENCY

FIGURE 15. GAIN ERROR vs INPUT VOLTAGE

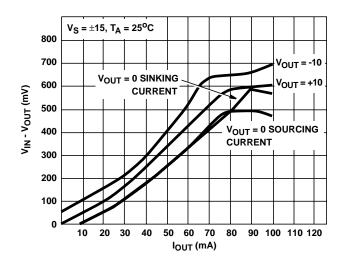

FIGURE 17.  $V_{IN}$  -  $V_{OUT}$  vs  $I_{OUT}$

FIGURE 19. Y - PARAMETER MAGNITUDE vs FREQUENCY

# Typical Performance Curves (Continued)

FIGURE 20. POWER SUPPLY REJECTION RATIO vs FREQUENCY

FIGURE 22. TOTAL HARMONIC DISTORTION vs INPUT VOLTAGE

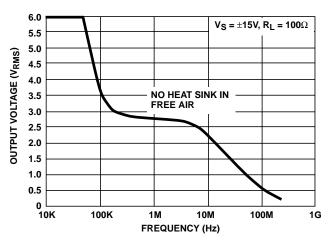

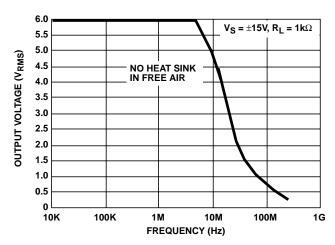

FIGURE 24. OUTPUT SWING vs FREQUENCY (NOTE)

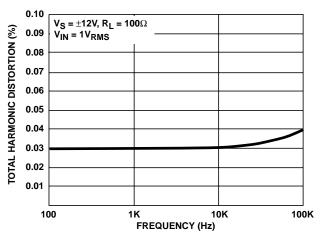

FIGURE 21. TOTAL HARMONIC DISTORTION vs FREQUENCY

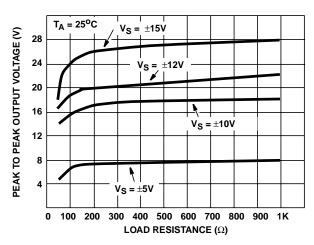

FIGURE 23. OUTPUT VOLTAGE SWING vs LOAD RESISTANCE

FIGURE 25. OUTPUT SWING vs FREQUENCY (NOTE)

NOTE:

This curve was obtained by noting the output voltage necessary to produce an observable distortion for a given frequency. If higher distortion is acceptable, then a higher output voltage for a given frequency can be obtained. However, operating the HA-5033 with increased distortion (to the right of curve shown), will also be accompanied by an increase in supply current. The resulting increase in chip temperature must be considered and heat sinking will be necessary to prevent thermal runaway. This characteristic is the result of the output transistor operation. If the signal amplitude or signal frequency or both are increased beyond the curve shown, the NPN, PNP output transistors will approach a condition of being simultaneously on. Under this condition, thermal runaway can occur.

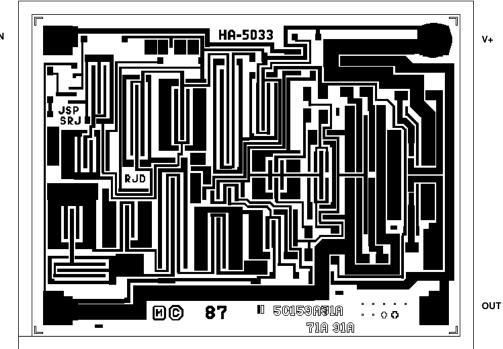

## Die Characteristics

### **DIE DIMENSIONS:**

51 mils x 67 mils x 19 mils 1300μm x 1700μm x 483μm

### **METALLIZATION:**

Type: Al, 1% Cu Thickness: 16kÅ ±2kÅ

#### PASSIVATION:

Type: Nitride (Si $_3$ N $_4$ ) over Silox (SiO $_2$ , 5% Phos.) Silox Thickness: 12kÅ  $\pm$ 2kÅ

Nitride Thickness: 3.5kÅ ±1.5kÅ

### SUBSTRATE POTENTIAL (Powered Up):

Unbiased

### TRANSISTOR COUNT:

20

### PROCESS:

Bipolar Dielectric Isolation

# Metallization Mask Layout

**HA-5033**

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com