# 1SC2060P2Ax-17 Preliminary Datasheet

Single-Channel High-Power High-Frequency SCALE-2 Driver Core

### Abstract

The 1SC2060P2Ax-17 is a 20W, 60A CONCEPT driver core. This high-performance SCALE-2 driver targets highpower single-channel IGBT and MOSFET applications such as induction heating, resonant and high-frequency power conversion as well as parallel gate driving of large modules.

It features newly developed planar transformer technology for a real leap forward in power density, noise immunity, and reliability.

Equipped with the latest SCALE-2 chipset, the gate driver supports switching up to 500kHz at best-in-class efficiency. The 1SC2060P2Ax-17 effectively comprises a complete single-channel IGBT driver core, fully equipped with an isolated DC/DC converter, short-circuit protection, advanced active clamping and supply-voltage monitoring.

With its extremely compact outline of 44mm x 74mm and a total height of typ. 6.5mm, it delivers high power density with an attractive form factor. Thanks to the highly integrated SCALE-2 chipset, the component count is reduced by 80% compared to conventional solutions. This results in significantly increased reliability and reduced costs.

Dedicated IGBT and MOSFET mode

### Safety Notice!

The data contained in this data sheet is intended exclusively for technically trained staff. Handling all high-voltage equipment involves risk to life. Strict compliance with the respective safety regulations is mandatory!

Any handling of electronic devices is subject to the general specifications for protecting electrostatic-sensitive devices according to international standard IEC 60747-1, Chapter IX or European standard EN 100015 (i.e. the workplace, tools, etc. must comply with these standards). Otherwise, this product may be damaged.

### Important Product Documentation

This data sheet contains only product-specific data. For a detailed description, must-read application notes and important information that apply to this product, please refer to "1SC2060P Description & Application Manual" on <a href="https://www.IGBT-Driver.com/go/1SC2060P">www.IGBT-Driver.com/go/1SC2060P</a>

### Absolute Maximum Ratings

| Parameter                       | Remarks                                             | Min  | Max     | Unit                 |

|---------------------------------|-----------------------------------------------------|------|---------|----------------------|

| Supply voltage $V_{DC}$         | VDC to GND                                          | 0    | 16      | V                    |

| Supply voltage $V_{CC}$         | VCC to GND                                          | 0    | 16      | V                    |

| Logic input and output voltages | Primary side, to GND                                | -0.5 | VCC+0.5 | i V                  |

| SO current                      | Failure condition, total current                    |      | 20      | mA                   |

| Gate peak current I out         | Notes 1, 11                                         | -60  | +60     | А                    |

| Average supply current $I_{DC}$ | Notes 2, 3                                          |      | 2100    | mA                   |

| Output power                    | Ambient temperature <70°C (Notes 4, 5)              |      | 23      | W                    |

|                                 | Ambient temperature 85°C (Note 4)                   |      | 21      | W                    |

| Switching frequency F           |                                                     |      | 500     | kHz                  |

| Test voltage (50Hz/1min.)       | Primary to secondary side (Note 12)                 |      | 5000 \  | / <sub>AC(eff)</sub> |

| Operating voltage               | Primary to secondary side                           |      | 1700    | $V_{peak}$           |

| dV/dt                           | Rate of change of input to output voltage (Note 17) |      | 100     | kV/µs                |

| Operating temperature           | Note 5                                              | -40  | + 85    | °C                   |

| Storage temperature             |                                                     | -40  | + 90    | °C                   |

### **Recommended Operating Conditions**

| Power Supply                   | Remarks                           | Min  | Тур | Max  | Unit |

|--------------------------------|-----------------------------------|------|-----|------|------|

| Supply voltage V <sub>DC</sub> | VDC to GND, IGBT mode             | 14.5 | 15  | 15.5 | V    |

| Supply voltage $V_{DC}$        | VDC to GND, MOSFET mode (Note 10) | 6    |     | 12   | V    |

| Supply voltage $V_{\rm CC}$    | VCC to GND                        | 14.5 | 15  | 15.5 | V    |

### Electrical Characteristics (IGBT mode)

### All data refer to +25°C and $V_{\rm CC}$ = $\,V_{\rm DC}$ = 15V unless otherwise specified.

| Power supply                         | Remarks                             | Min  | Тур  | Max  | Unit |

|--------------------------------------|-------------------------------------|------|------|------|------|

| Supply current I DC                  | Without load                        |      | 36   | 60   | mA   |

| Supply current $I_{CC}$              | F = 0Hz                             |      | 12   | 15   | mA   |

| Supply current $I_{cc}$              | F = 360kHz                          |      | 31   |      | mA   |

| Coupling capacitance C <sub>io</sub> | Primary to output, total            |      | 40   |      | pF   |

| Power Supply Monitoring              | Remarks                             | Min  | Тур  | Max  | Unit |

| Supply threshold $V_{CC}$            | Primary side, clear fault           | 11.9 | 12.6 | 13.3 | V    |

|                                      | Primary side, set fault (Note 18)   | 11.3 | 12.0 | 12.7 | V    |

| Monitoring hysteresis                | Primary side, set/clear fault       | 0.35 |      |      | V    |

| Supply threshold $V_{ISO}$ - $V_E$   | Secondary side, clear fault         | 12.1 | 12.6 | 13.1 | V    |

|                                      | Secondary side, set fault (Note 18) | 11.5 | 12.0 | 12.5 | V    |

| Monitoring hysteresis                | Secondary side, set/clear fault     | 0.35 |      |      | V    |

| Supply threshold $V_{E}$ - $V_{COM}$ | Secondary side, clear fault         | 5    | 5.15 | 5.3  | V    |

|                                      | Secondary side, set fault (Note 18) | 4.7  | 4.85 | 5    | V    |

| Monitoring hysteresis                | Secondary side, set/clear fault     | 0.15 |      |      | V    |

| Logic Inputs and Outputs             | Remarks                             | Min  | Тур  | Max  | Unit |

| Input bias current                   | V(1N) > 3V                          |      | 190  |      | μA   |

| Turn-on threshold                    | V(IN)                               |      | 2.6  |      | V    |

| Turn-off threshold                   | V(IN)                               |      | 1.3  |      | V    |

| SO output voltage                    | Failure condition, I(SO)<20mA       |      |      | 0.7  | V    |

| Short-Circuit Protection             | Remarks                             | Min  | Тур  | Max  | Unit |

| Current through pin REF              | R(REF, VE)<70kΩ                     |      | 150  |      | μA   |

| Minimum response time                | Note 15                             |      | 1.2  |      | μs   |

| Minimum blocking time                | Note 16                             |      | 9    |      | μs   |

| Timing Characteristics               | Remarks                             | Min  | Тур  | Max  | Unit |

| Turn-on delay t <sub>d(on)</sub>     | Note 6                              |      | 75   |      | ns   |

| Turn-off delay t <sub>d(off)</sub>   | Note 6                              |      | 70   |      | ns   |

| Jitter of turn-on delay              | Note 20                             |      | ±1   |      | ns   |

| Jitter of turn-off delay             | Note 20                             |      | ±1   |      | ns   |

| Output rise time t <sub>r(out)</sub> | Note 7                              |      | 10   |      | ns   |

| Output fall time $t_{f(out)}$        | Note 7                              |      | 15   |      | ns   |

| Transmission delay of fault state    | Note 19                             |      | 400  |      | ns   |

| Electrical Isolation                                                                                    | Remarks                                                                                                                                                                      | Min                      | Тур        | Мах  | Unit                                                  |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------|------|-------------------------------------------------------|

| Test voltage (50Hz/1s)<br>Partial discharge extinction volt.<br>Oreepage distance<br>Clearance distance | Primary to secondary side (Note 12)<br>Note 13<br>Primary to secondary side<br>Primary to secondary side                                                                     | 5000<br>1768<br>15<br>15 | 5050       | 5100 | V <sub>AC(eff)</sub><br>V <sub>peak</sub><br>mm<br>mm |

| Output                                                                                                  | Remarks                                                                                                                                                                      | Min                      | Тур        | Max  | Unit                                                  |

| Blocking capacitance VISO to VE<br>Blocking capacitance VE to COM                                       | Note 14<br>Note 14                                                                                                                                                           |                          | 9.4<br>9.4 |      | μF<br>μF                                              |

| External gate resistor loop Turn-on gate resistor $R_{g(on)}$ Turn-off gate resistor $R_{g(off)}$       | $\label{eq:Fsecond} \begin{split} F &\leq 250 \text{kHz} \mbox{ (Note 8)} \\ F &\leq 250 \text{kHz} \mbox{ (Note 9)} \\ F &\leq 250 \text{kHz} \mbox{ (Note 9)} \end{split}$ | 2.0<br>1.0<br>1.0        |            |      | Ω<br>Ω<br>Ω                                           |

| External gate resistor loop Turn-on gate resistor $R_{g(on)}$ Turn-off gate resistor $R_{g(off)}$       | $\label{eq:Fsecond} \begin{split} F &\leq 310 \text{kHz} \mbox{ (Note 8)} \\ F &\leq 310 \text{kHz} \mbox{ (Note 9)} \\ F &\leq 310 \text{kHz} \mbox{ (Note 9)} \end{split}$ | 3.2<br>1.6<br>1.6        |            |      | Ω<br>Ω<br>Ω                                           |

| External gate resistor loop Turn-on gate resistor $R_{g(on)}$ Turn-off gate resistor $R_{g(off)}$       | $\label{eq:Fsecond} \begin{split} F &\leq 360 \text{kHz} \mbox{ (Note 8)} \\ F &\leq 360 \text{kHz} \mbox{ (Note 9)} \\ F &\leq 360 \text{kHz} \mbox{ (Note 9)} \end{split}$ | 4.8<br>2.4<br>2.4        |            |      | Ω<br>Ω<br>Ω                                           |

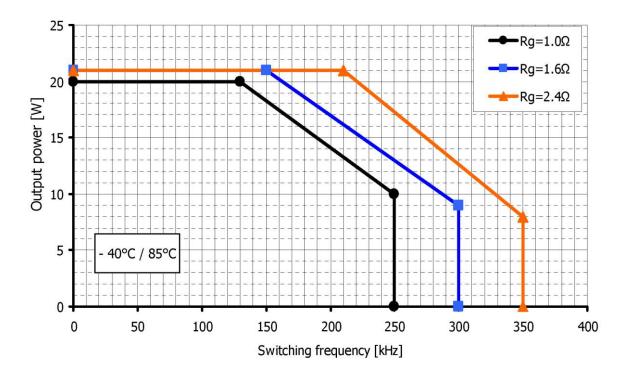

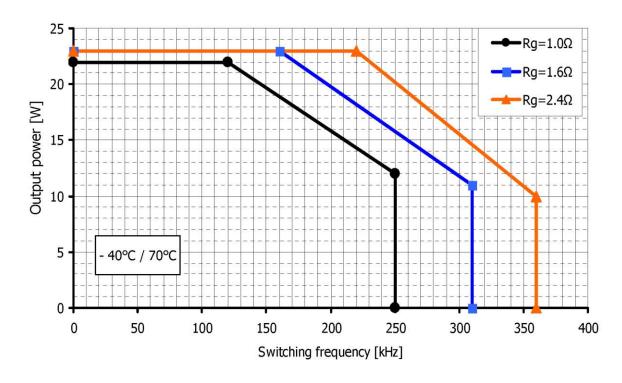

#### Output power

The permissible drive power at the output of the driver card is given versus switching frequency for different total gate resistance values. Linear interpolation is permissible for gate resistance values other than those shown. However, no extrapolation beyond the given data range is allowed.

Fig. 1 Output power vs. switching frequency at ambient temperature range – 40°C through 85°C

Fig. 2 Output power vs. switching frequency at ambient temperature range – 40°C through 70°C

To check if the driver output power is in accordance with the data given in Figs. 1 and 2, proceed as follows:

- determine the actual gate charge of the power switch

- check with note 14

- determine the output voltage swing of the driver at the required switching frequency

- calculate the output power as gate charge x voltage swing x frequency

- check the calculated power at the relevant switching frequency against the diagram "Output power vs. switching frequency" at the appropriate max. temperature (70°C / 85°C)

The actual value of the driver's output voltage swing should be taken to determine the output power drawn from the driver. If the nominal (no-load) value is taken, the driver will not be operated up to its full capacity. See the section "Output voltage swing" for output voltage swing vs. output power.

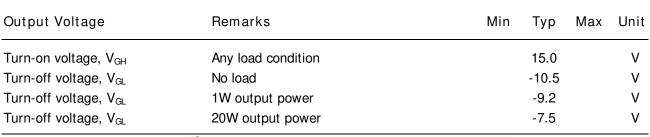

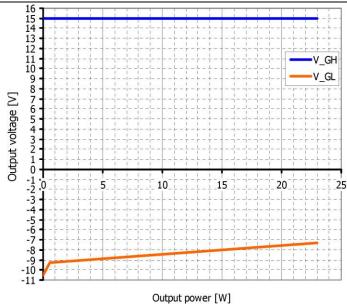

#### Output voltage swing

The output voltage swing consists of two distinct segments. First, there is the turn-on voltage  $V_{GH}$  between pins GH and VE.  $V_{GH}$  is regulated and maintained at a constant level for all output power values and frequencies.

The second segment of the output voltage swing is the turn-off voltage  $V_{GL}$ .  $V_{GL}$  is measured between pins GL and VE. It is a negative voltage. It changes with the output power to accommodate the inevitable voltage drop across the internal DC/DC converter.

Fig. 3 Output voltage swing (typ.) vs. output power

### Electrical Characteristics (MOSFET Mode)

### All data refer to +25°C and $V_{\rm CC}$ = 15V unless stated otherwise.

| Power supply                                       | Remarks                             | Min  | Тур  | Max  | Unit |

|----------------------------------------------------|-------------------------------------|------|------|------|------|

| Supply current I DC                                | V <sub>DC</sub> =9.2V, without load |      | 25   |      | mA   |

| Supply current $I_{CC}$                            | F = 0Hz                             |      | 12   |      | mA   |

| Supply current $I_{cc}$                            | F = 500kHz                          |      | 39   |      | mA   |

| Coupling capacitance Cio                           | Primary to output, total            |      | 40   |      | pF   |

| Power Supply Monitoring                            | Remarks                             | Min  | Тур  | Max  | Unit |

| Supply threshold $V_{cc}$                          | Primary side, clear fault           | 11.9 | 12.6 | 13.3 | V    |

|                                                    | Primary side, set fault (Note 18)   | 11.3 | 12.0 | 12.7 | V    |

| Monitoring hysteresis                              | Primary side, set/clear fault       | 0.35 |      |      | V    |

| Supply threshold V <sub>ISO</sub> -V <sub>VE</sub> | Secondary side, clear fault         | 8.3  | 8.75 | 9.2  | V    |

|                                                    | Secondary side, set fault (Note 18) | 7.9  | 8.2  | 8.6  | V    |

| Monitoring hysteresis                              | Secondary side, set/clear fault     | 0.23 | 0.5  |      | V    |

| Logic Inputs and Outputs                           | Remarks                             | Min  | Тур  | Max  | Unit |

| Input bias current                                 | V(1N) > 3V                          |      | 160  |      | μA   |

| Turn-on threshold                                  | V(IN)                               |      | 2.6  |      | V    |

| Turn-off threshold                                 | V(IN)                               |      | 1.3  |      | V    |

| SO output voltage                                  | Failure condition, I(SO)<20mA       |      |      | 0.7  | V    |

| Short-circuit Protection                           | Remarks                             | Min  | Тур  | Max  | Unit |

| Current through pin REF                            | R(REF, VE)<70kΩ                     |      | 150  |      | μA   |

| Minimum response time                              | Note 15                             |      | 1.2  |      | μs   |

| Minimum blocking time                              | Note 16                             |      | 9    |      | μs   |

| Timing Characteristics                             | Remarks                             | Min  | Тур  | Max  | Unit |

| Turn-on delay t <sub>d(on)</sub>                   | Note 6                              |      | 75   |      | ns   |

| Turn-off delay t <sub>d(off)</sub>                 | Note 6                              |      | 70   |      | ns   |

| Jitter of turn-on delay                            | Note 20                             |      | ±1   |      | ns   |

| Jitter of turn-off delay                           | Note 20                             |      | ±1   |      | ns   |

| Output rise time t <sub>r(out)</sub>               | Note 7                              |      | 10   |      | ns   |

| Output fall time t <sub>f(out)</sub>               | Note 7                              |      | 15   |      | ns   |

| Transmission delay of fault state                  | Note 19                             |      | 400  |      | ns   |

| Electrical Isolation                       | Remarks                             | Min            | Тур  | Max  | Unit                 |

|--------------------------------------------|-------------------------------------|----------------|------|------|----------------------|

| Test voltage (50Hz/1s)                     | Primary to secondary side (Note 12) | 5000           | 5050 | 5100 | V <sub>AC(eff)</sub> |

| Partial discharge extinction volt.         | Note 13                             | 1768           |      |      | $V_{peak}$           |

| Creepage distance                          | Primary to secondary side           | 15             |      |      | mm                   |

| Clearance distance                         | Primary to secondary side           | 15             |      |      | mm                   |

| Output                                     | Remarks                             | Min            | Тур  | Max  | Unit                 |

| Blocking capacitance VISO to VE            | Note 14                             |                | 9.4  |      | μF                   |

| Blocking capacitance VE to COM             | VE is short-circuited to COM        | Not applicable |      |      |                      |

| External gate resistor loop                | $F \le 500 \text{kHz}$ (Note 8)     | 2.0            |      |      | Ω                    |

| Turn-on gate resistor $R_{g(on)}$          | $F \le 500 kHz$ (Note 9)            | 1.0            |      |      | Ω                    |

| Turn-off gate resistor R <sub>g(off)</sub> | $F \le 500 \text{kHz}$ (Note 9)     | 1.0            |      |      | Ω                    |

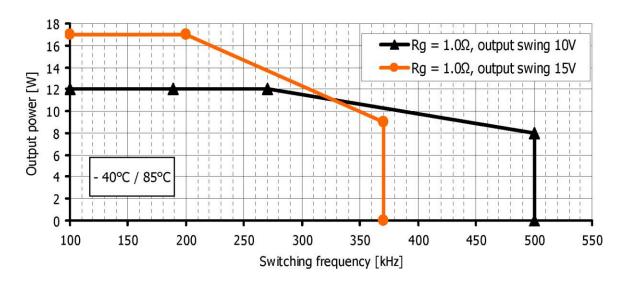

#### Output power

The permissible drive power at the output of the driver card is given versus the switching frequency for an output voltage swing of 10V and 15V. No extrapolation is allowed beyond the given data range towards higher frequency values.

*Fig. 4* Output power vs. switching frequency for ambient temperature range – 40°C through **85°C** To check if the driver output power is in accordance with the data given in Fig. 4, proceed as follows:

- determine the actual gate charge of the power switch

- check with note 14

- determine the output voltage swing of the driver at the required switching frequency

- calculate the output power as gate charge x voltage swing x frequency

• check the calculated power at the relevant switching frequency against the diagram "Output power vs. switching frequency" at the appropriate max. temperature (85°C)

The actual value of the driver's output voltage swing should be taken to determine the output power drawn from the driver. If the nominal (no-load) value is taken, the driver will not be operated up to its full capacity. See the section "Output voltage swing" for output voltage swing vs. output power.

#### Output voltage swing

The output voltage swing in MOSFET mode directly follows the primary-side input voltage  $V_{DC}$ . The following table gives exemplary input voltages  $V_{DC}$  for a set of output voltages under various load conditions.

| $V_{DC}$ for $V_{GH}$ = 10V                                  | Remarks                     | Min | Тур        | Max | Unit   |

|--------------------------------------------------------------|-----------------------------|-----|------------|-----|--------|

| Primary side input, $V_{DC}$<br>Primary side input, $V_{DC}$ | No load<br>12W output power |     | 6.3<br>7.8 |     | V<br>V |

| V <sub>DC</sub> for V <sub>GH</sub> = 15V                    | Remarks                     | Min | Тур        | Max | Unit   |

|                                                              |                             |     |            |     |        |

#### Footnotes to the Key Data

- 1) The maximum peak gate current refers to the highest current level occurring during the product lifetime. It is an absolute value and does also apply for short pulses.

- 2) The average supply input current is limited for thermal reasons. Higher values than specified by the absolute maximum rating are permissible (e.g. during power supply start up) if the average remains below the given value, provided the average is taken over a time period which is shorter than the thermal time constants of the driver in the application.

- 3) There is no means of actively controlling or limiting the input current in the driver. In the case of start-up with very high blocking capacitor values, or in case of short circuit at the output, the supply input current has to be limited externally.

- 4) The maximum output power must not be exceeded at any time during operation. The absolute maximum rating must also be observed for time periods shorter than the thermal time constants of the driver in the application.

- 5) An extended output power range is specified in the output power section for maximum ambient temperatures of 70°C. In that case, the absolute maximum rating for the operating temperature changes to (-40°C 70°C) and the absolute maximum output power rating changes to 23W.

- 6) The delay time is measured between 50% of the input signal and 20% voltage swing of the corresponding output. The delay time is independent of the output loading.

- 7) Output rise and fall times are measured between 10% and 90% of the nominal output swing. The values are given for the driver side of the gate resistors. The time constant of the output load in conjunction with the present gate resistors leads to an additional delay at the load side of the gate resistors.

- 8) The external gate resistor loop comprises all resistors located between the driver gate and the driver emitter. The internal resistance of any output load (e.g. an IGBT module) makes no contribution. Example:

Total turn-on gate resistance:  $1.0\Omega$ Total turn-off gate resistance:  $1.5\Omega$

IGBT module internal gate resistance:  $0.25\Omega$

Leads to:

External turn-on gate resistance:  $0.75\Omega$ External turn-off gate resistance:  $1.25\Omega$ External gate resistor loop:  $2.0\Omega$

- 9) The values given refer to the total gate resistance, including both external resistors and the internal resistance of the power module / transistor.

- 10) The secondary side output voltage swing must not exceed 20V.

- 11) The maximum current given is the short circuit value of the output stage. Continuous operation is limited by thermal constraints. The surface temperature of the output stage must not exceed 125°C.

- 12) HiPot testing (= dielectric testing) must generally be restricted to suitable components. This gate driver is suited for HiPot testing. Nevertheless, it is strongly recommended to limit the testing time to 1s slots as stipulated by EN 50178. Excessive HiPot testing at voltages much higher than  $1200V_{AC(eff)}$  may lead to insulation degradation. No degradation has been observed over 1min. testing at  $5000V_{AC(eff)}$ . Every production sample shipped to customers has undergone 100% testing at  $5000V_{AC(eff)}$  (typical) for 1s.

- 13) Partial discharge measurement is performed in accordance with IEC 60270 and isolation coordination specified in EN 50178. The minimum value given is designed to include appropriate safety margins for long-term ageing. Accelerated ageing tests show virtually no insulation deterioration. Minimum partial discharge extinction voltages remain > 2100V even after 2600 slow thermal cycles between -40°C and 125°C and also after 500 thermal shock cycles between -55°C and 150°C. The partial discharge extinction voltage is coordinated for safe isolation to EN 50178.

- 14) External blocking capacitors are to be placed between VISO and VE as well as VE and COM for gate charges exceeding 3µC. Ceramic capacitors are recommended. A minimum external blocking capacitance of 3µF is recommended for every 1µC of gate charge beyond 3µC. Insufficient external blocking can lead to reduced driver efficiency and thus to thermal overload.

- 15) The minimum response time given is valid for the circuit given in the description and application manual (Figs. 5 and 6) with the values of table 1 ( $C_a=0pF$ ,  $R_{th}=43k\Omega$ ).

- 16) The blocking time sets a minimum time span between the end of any fault state and the start of normal operation (remove fault from pin SO). The value of the blocking time can be adjusted at pin TB. The specified blocking time is valid if TB is connected to GND.

- 17) This specification guarantees that the drive information will be transferred reliably even at a high DClink voltage and with ultra-fast switching operations.

- 18) Undervoltage monitoring of the corresponding supply voltage (VCC to GND as well as VISO to VE and VE to COM which correspond with the approximate turn-on and turn-off gate-emitter voltages). If the corresponding voltage drops below this limit, the power semiconductor is switched off and a fault is transmitted to SO.

- 19) Transmission delay of fault state from the secondary side to the primary status output.

- 20) Jitter measurements are performed with input signal IN switching between 0V and 5V referred to GND, with a corresponding rise time and fall time of 5ns.

### Legal Disclaimer

This data sheet specifies devices but cannot promise to deliver any specific characteristics. No warranty or guarantee is given – either expressly or implicitly – regarding delivery, performance or suitability.

CT-Concept Technologie AG reserves the right to make modifications to its technical data and product specifications at any time without prior notice. The general terms and conditions of delivery of CT-Concept Technologie AG apply.

### Ordering Information

The general terms and conditions of delivery of CT-Concept Technologie AG apply.

Type Designation Description

1SC2060P2A0-17 Single-channel SCALE-2 driver core

Product home page: www.IGBT-Driver.com/go/1SC2060P

Refer to www.IGBT-Driver.com/go/nomenclature for information on driver nomenclature

### Information about Other Products

For other drivers, product documentation, and application support

Please click: www.IGBT-Driver.com

### Manufacturer

CT-Concept Technologie AG Intelligent Power Electronics Renferstrasse 15 CH-2504 Biel-Bienne Switzerland

Tel. +41 - 32 - 344 47 47 Fax +41 - 32 - 344 47 40

E-mail Info@IGBT-Driver.com Internet www.IGBT-Driver.com

© 2008..2011 CT-Concept Technologie AG - Switzerland. We reserve the right to make any technical modifications without prior notice. Version from 2016-05-20

All rights reserved.