# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **User's Manual**

# V850E/IA1

# 32-bit Single-Chip Microcontrollers

## **Hardware**

μPD703116 μPD703116(A) μPD703116(A1) μPD70F3116 μPD70F3116(A) μPD70F3116(A1)

Document No. U14492EJ6V0UD00 (6th edition)

Date Published February 2008 N

## [MEMO]

#### NOTES FOR CMOS DEVICES —

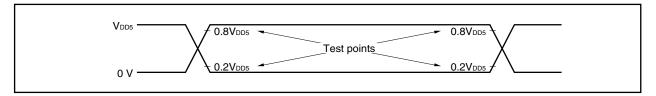

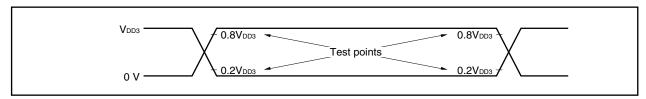

#### 1 VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

## (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

## **③ PRECAUTION AGAINST ESD**

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

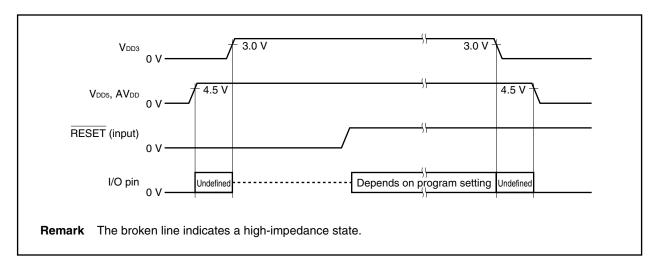

## (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

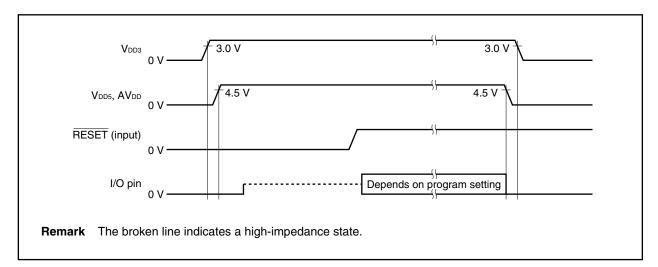

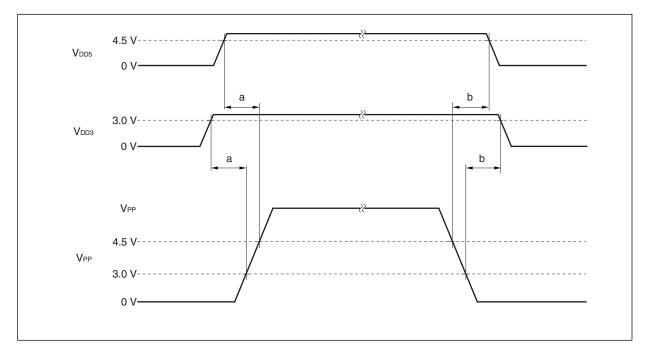

## **5** POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

## **6** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of December, 2007. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

#### INTRODUCTION

#### Readers

This manual is intended for users who wish to understand the functions of the V850E/IA1 and design application systems using it.

The target products are as follows.

- Standard products: μPD703116, 70F3116

- Special products: μPD703116(A), 703116(A1), 70F3116(A), 70F3116(A1)

#### **Purpose**

This manual introduces the hardware functions of the V850E/IA1 shown below for user's understanding.

## Organization

This manual is divided into two parts: Hardware (this manual) and Architecture (V850E1 Architecture User's Manual).

#### Hardware

- Pin functions

- CPU function

- Internal peripheral functions

- Flash memory programming

- Electrical specifications

## Architecture

- Data type

- Register set

- Instruction format and instruction set

- Interrupt and exception

- Pipeline operation

#### **How to Read This Manual**

It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

- Cautions 1. The application examples in this manual apply to "standard" quality grade products for general electronic systems. When using an example in this manual for an application that requires a "special" quality grade product, thoroughly evaluate the component and circuit to be actually used to see if they satisfy the special quality grade.

- 2. When using this manual as a manual for a special grade product, read the part numbers as follows.

$\mu$ PD703116  $\rightarrow$  703116(A), 703116(A1)  $\mu$ PD70F3116  $\rightarrow$  70F3116(A), 70F3116(A1)

- To understand the overall functions of the V850E/IA1

- →Read this manual according to the **CONTENTS**.

- To find the details of a register where the name is known

- → Refer to APPENDIX B REGISTER INDEX.

- · How to read register formats

- → The name of a bit whose number is in angle brackets (<>) is defined as a reserved word in the device file.

When the register format of each register describes 0 or 1, other values are prohibited to be specified.

- To understand the details of an instruction function

- →Refer to the V850E1 Architecture User's Manual.

- To know details of the electrical specifications of the V850E/IA1

- → Refer to CHAPTER 18 ELECTRICAL SPECIFICATIONS.

The mark <R> shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

#### Conventions

Data significance: Higher digits on the left and lower digits on the right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

Memory map address: Higher address on the top and lower address on the

bottom

**Note**: Footnote for item marked with **Note** in the text

Caution: Information requiring particular attention

**Remark**: Supplementary information Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory

capacity):  $K \text{ (kilo): } 2^{10} = 1,024$

M (mega):  $2^{20} = 1,024^2$ G (giga):  $2^{30} = 1,024^3$

α (gigα). 2 = 1,02+

Data type: Word ... 32 bits

Halfword ... 16 bits Byte ... 8 bits

## **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

## Documents related to V850E/IA1

| Document Name                                                                                               | Document No. |

|-------------------------------------------------------------------------------------------------------------|--------------|

| V850E1 Architecture User's Manual                                                                           | U14559E      |

| V850E/IA1 Hardware User's Manual                                                                            | This manual  |

| V850E/IA1, V850E/IA2 AC Motor Inverter Control Using Vector Operation Application Note                      | U14868E      |

| Inverter Control by V850 Series 120° Excitation Method Control by Zero-<br>Cross Detection Application Note | U17209E      |

| Inverter Control by V850 Series Vector Control by Encoder Application Note                                  | U17324E      |

| Inverter Control by V850 Series Vector Control by Hole Sensor Application Note                              | U17338E      |

| V850 Series Flash Memory Self-Programming User's Manual                                                     | U15673E      |

## **Documents related to development tools (User's Manuals)**

| Document Nam                                                                                  | Document No.        |         |

|-----------------------------------------------------------------------------------------------|---------------------|---------|

| IE-V850E-MC, IE-V850E-MC-A (In-circuit em                                                     | U14487E             |         |

| IE-703114-MC-EM1 (In-circuit emulator optio                                                   | n board)            | U16533E |

| CA850 (Ver. 3.00) (C compiler package)                                                        | Operation           | U17293E |

|                                                                                               | C Language          | U17291E |

|                                                                                               | Assembly Language   | U17292E |

|                                                                                               | Link Directives     | U17294E |

| PM+ (Ver. 6.30) (Project manager)                                                             |                     | U18416E |

| ID850 (Ver. 3.00) (Integrated debugger)                                                       | Operation           | U17358E |

| TW850 (Ver. 2.00) (Performance analysis tun                                                   | ing tool)           | U17241E |

| SM850 (Ver. 2.50) (System simulator)                                                          | Operation           | U16218E |

| SM850 (Ver. 2.00 or later) (System External Part User Open simulator) Interface Specification |                     | U14873E |

| SM+ (System simulator)                                                                        | Operation           | U18601E |

|                                                                                               | User Open Interface | U18212E |

| RX850 (Ver. 3.20) (Real-time OS)                                                              | Basics              | U13430E |

|                                                                                               | Installation        | U17419E |

|                                                                                               | Technical           | U13431E |

|                                                                                               | Task Debugger       | U17420E |

| RX850 Pro (Ver. 3.21) (Real-time OS)                                                          | Basics              | U18165E |

|                                                                                               | Installation        | U17421E |

|                                                                                               | Technical           | U13772E |

|                                                                                               | Task Debugger       | U17422E |

| RX-NET (Ver. 1.30) (TCP/IP library)                                                           | U15083E             |         |

| AZ850 (Ver. 3.30) (System performance analy                                                   | U17423E             |         |

| PG-FP4 Flash Memory Programmer                                                                | U15260E             |         |

| PG-FP5 Flash Memory Programmer                                                                | U18865E             |         |

## **CONTENTS**

| CHAPTI | ER 1 IN | TRODUCTION                                                                      | 17 |

|--------|---------|---------------------------------------------------------------------------------|----|

| 1.1    | Outline | 9                                                                               | 17 |

| 1.2    | Feature | es                                                                              | 20 |

| 1.3    | Applica | ations                                                                          | 22 |

| 1.4    | Orderii | ng Information                                                                  | 22 |

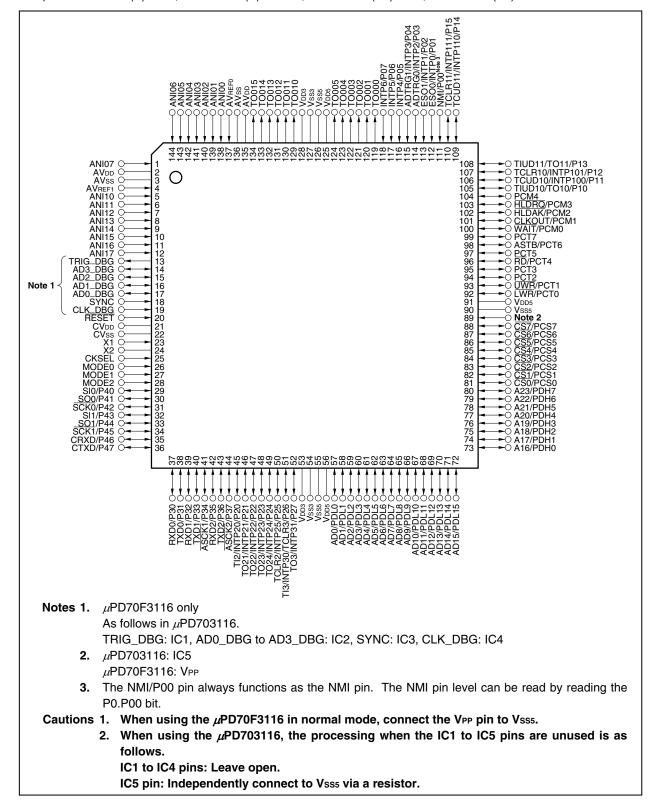

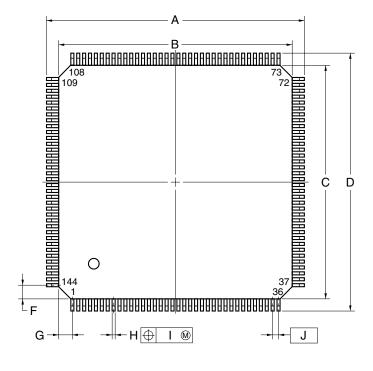

| 1.5    | Pin Co  | nfiguration (Top View)                                                          | 23 |

| 1.6    | Config  | uration of Function Block                                                       | 25 |

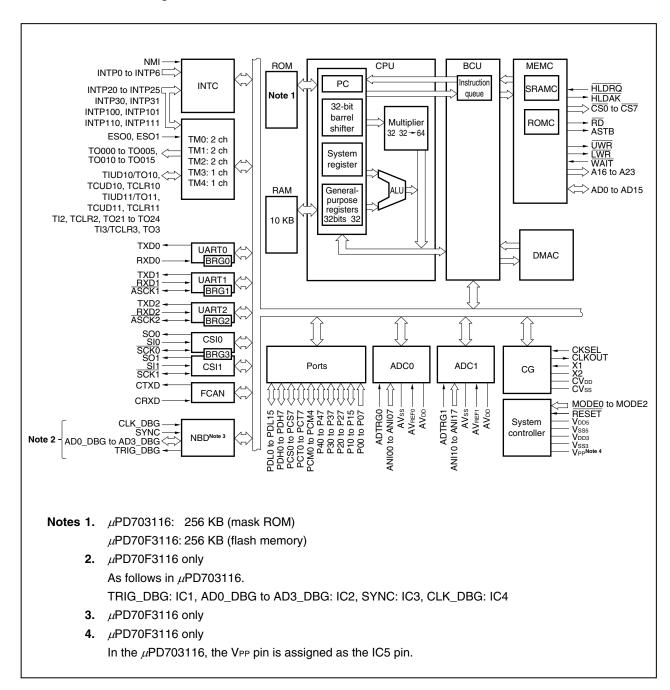

|        | 1.6.1   | Internal block diagram                                                          | 25 |

|        | 1.6.2   | Internal units                                                                  | 26 |

| 1.7    | Differe | nces Between Products                                                           | 28 |

| CHAPTI |         | N FUNCTIONS                                                                     |    |

| 2.1    | List of | Pin Functions                                                                   | 29 |

| 2.2    | Pin Sta | itus                                                                            | 35 |

| 2.3    | Descri  | ption of Pin Functions                                                          | 36 |

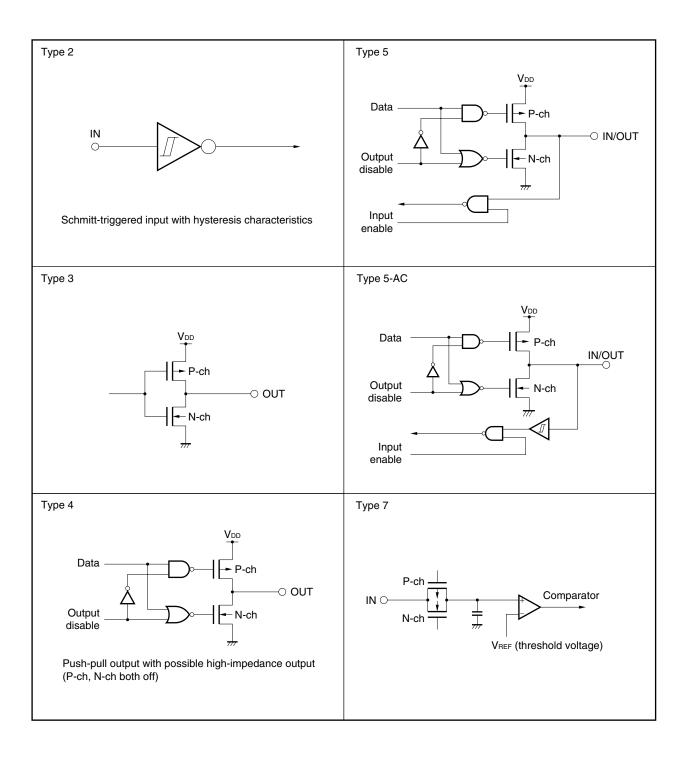

| 2.4    | Types   | of Pin I/O Circuit and Connection of Unused Pins                                | 44 |

| 2.5    | Pin I/O | Circuits                                                                        | 46 |

| CHAPTI | ER 3 CI | PU FUNCTION                                                                     | 47 |

| 3.1    | Feature | es                                                                              | 47 |

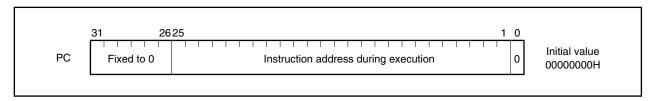

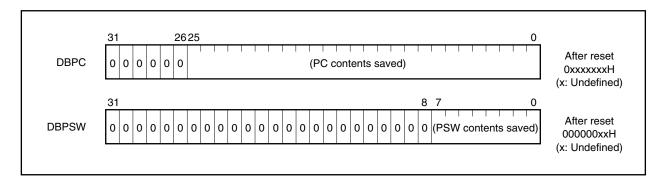

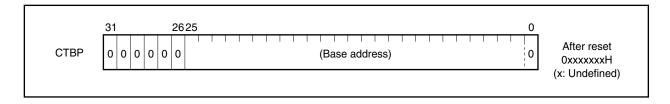

| 3.2    | CPU R   | egister Set                                                                     | 48 |

|        | 3.2.1   | Program register set                                                            | 49 |

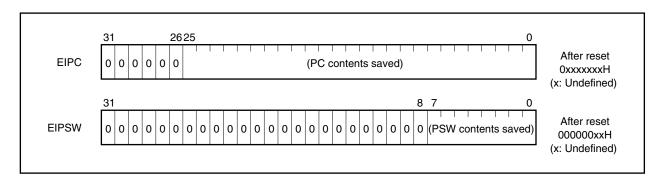

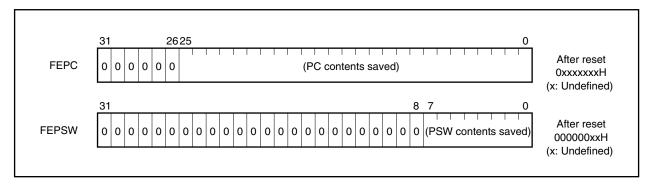

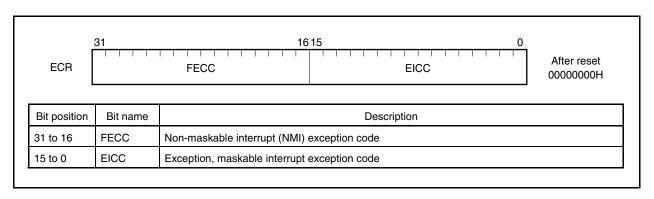

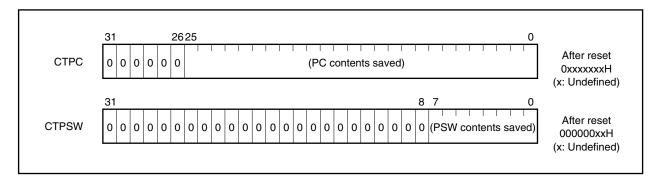

|        | 3.2.2   | System register set                                                             | 50 |

| 3.3    | Operat  | ion Modes                                                                       | 56 |

|        | 3.3.1   | Operation modes                                                                 | 56 |

|        | 3.3.2   | Operation mode specification                                                    | 57 |

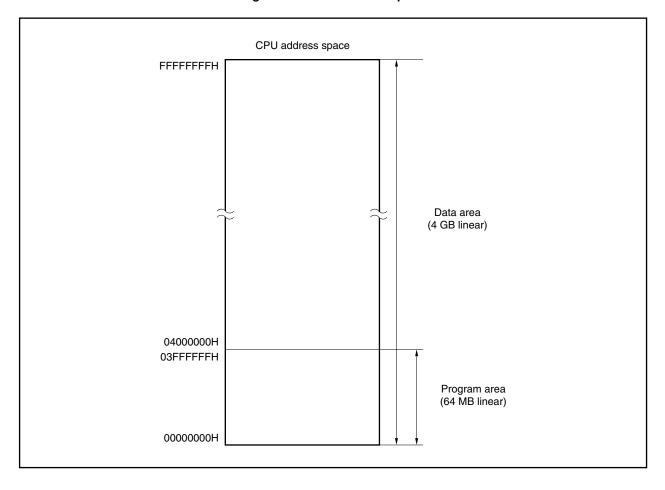

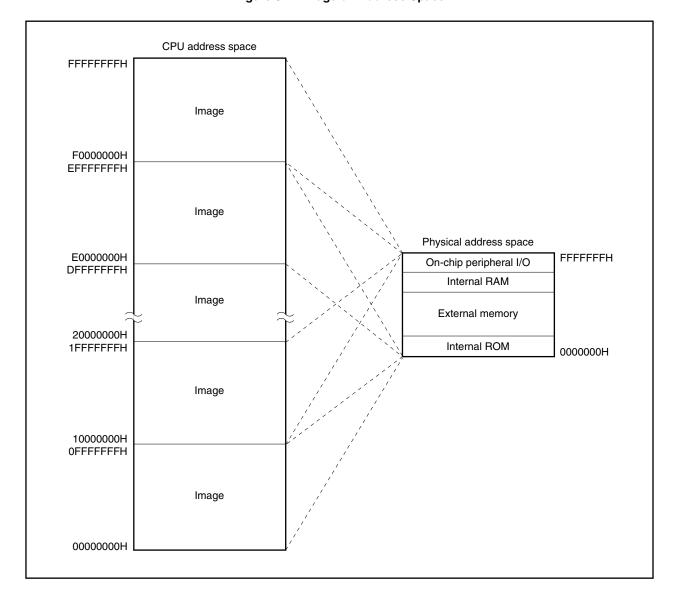

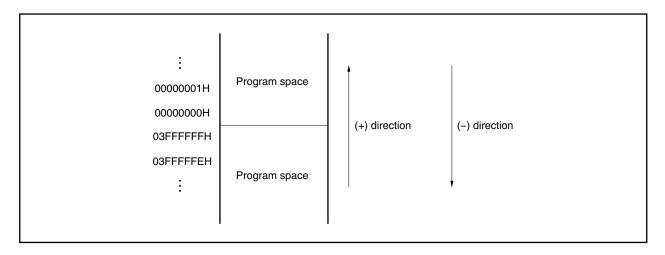

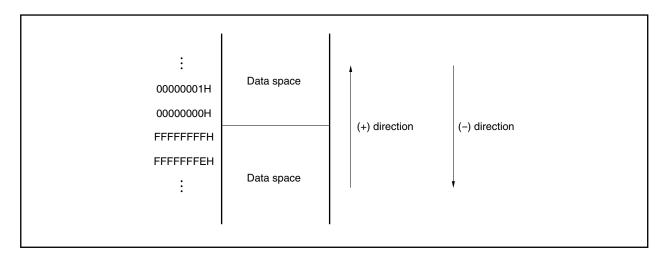

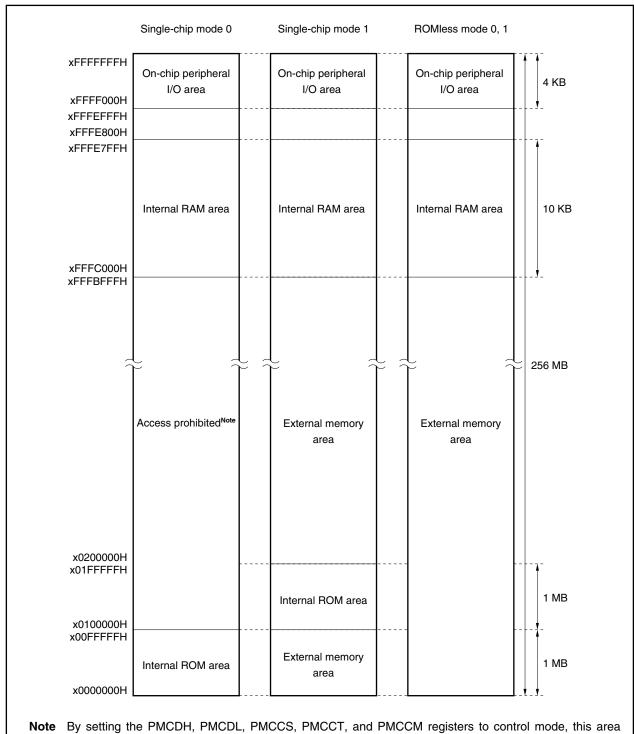

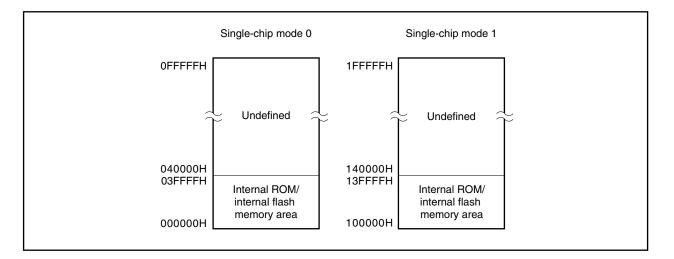

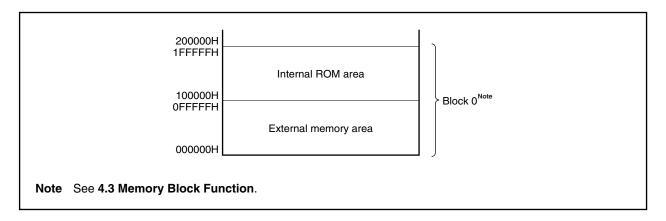

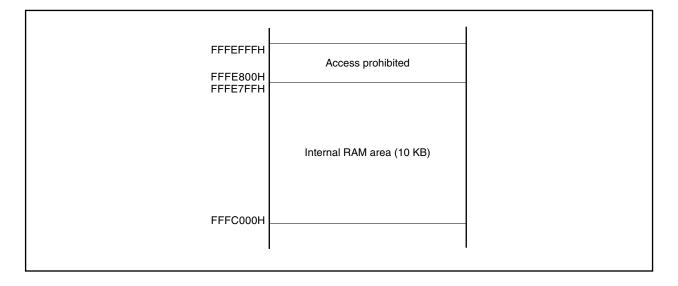

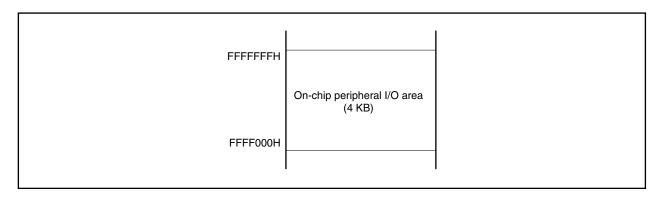

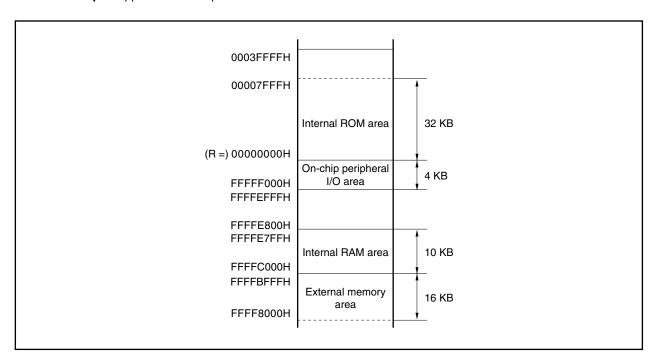

| 3.4    | Addres  | ss Space                                                                        | 58 |

|        | 3.4.1   | CPU address space                                                               | 58 |

|        | 3.4.2   | Image                                                                           | 59 |

|        | 3.4.3   | Wrap-around of CPU address space                                                | 60 |

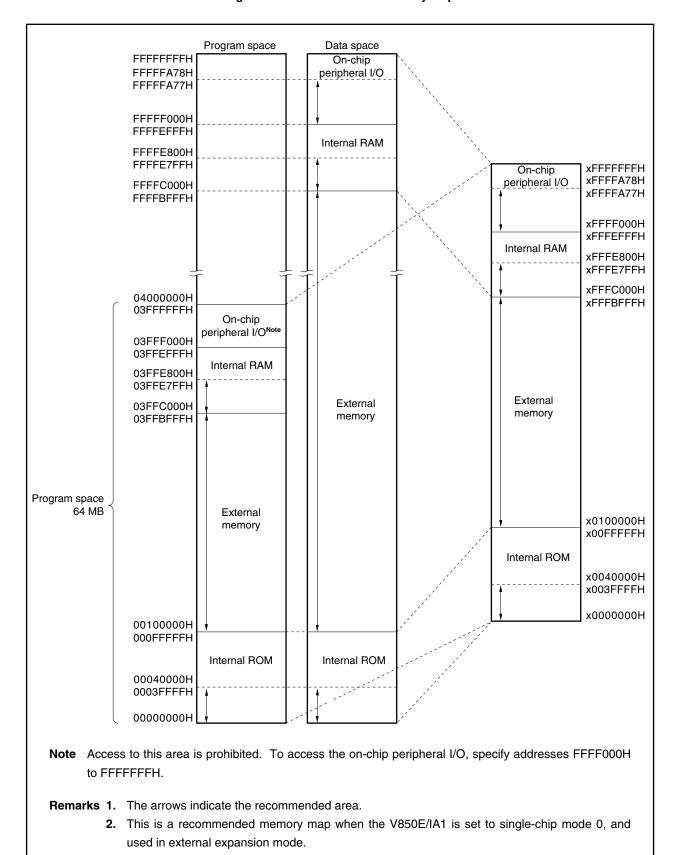

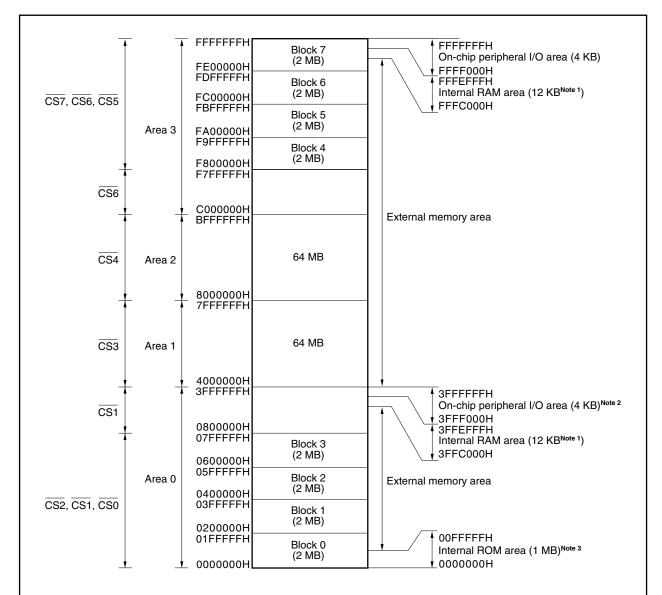

|        | 3.4.4   | Memory map                                                                      | 61 |

|        | 3.4.5   | Area                                                                            | 62 |

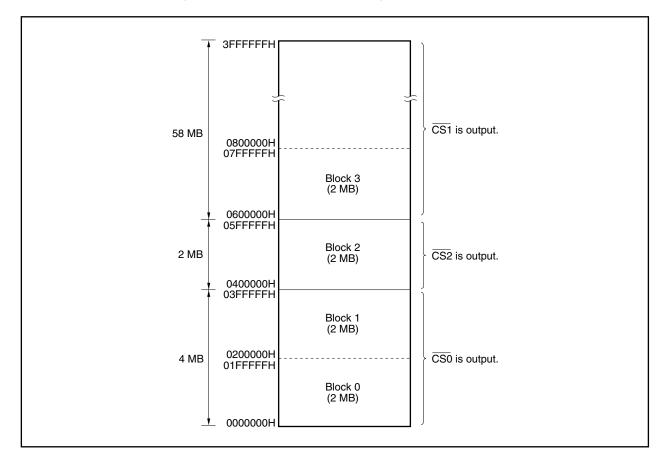

|        | 3.4.6   | External memory expansion                                                       | 66 |

|        | 3.4.7   | Recommended use of address space                                                | 67 |

|        | 3.4.8   | On-chip peripheral I/O registers                                                | 69 |

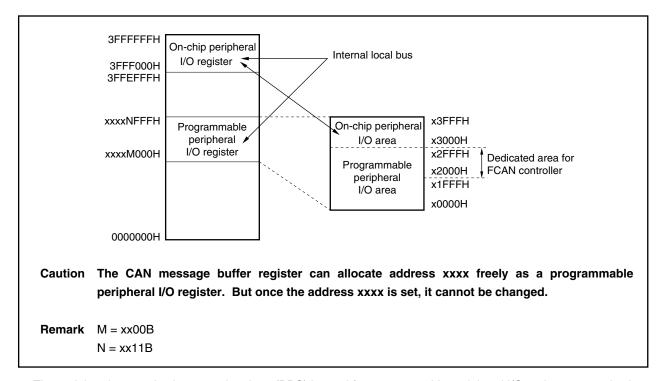

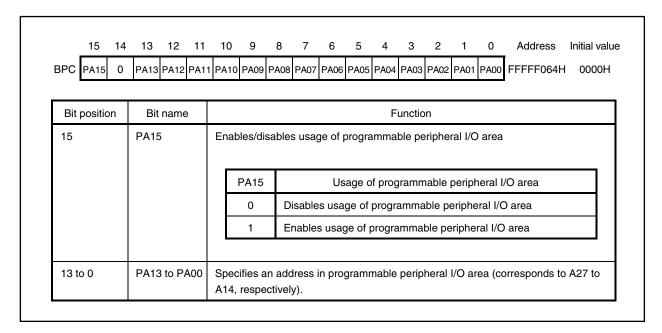

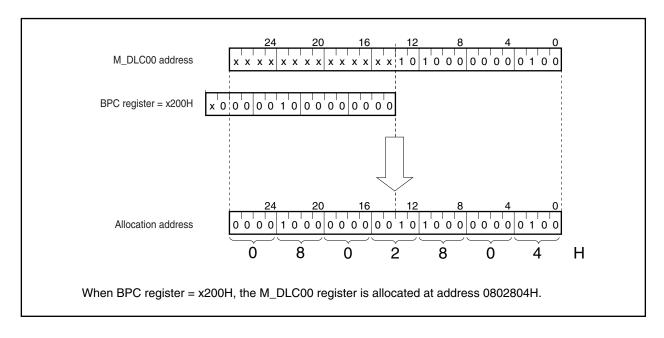

|        | 3.4.9   | Programmable peripheral I/O registers                                           | 80 |

|        | 3.4.10  | Specific registers                                                              | 97 |

|        | 3.4.11  | System wait control register (VSWC)                                             | 97 |

|        | 3.4.12  | Cautions                                                                        | 97 |

| CHAPTI | ER 4 BI | US CONTROL FUNCTION                                                             | 99 |

| 4.1    | Feature | es                                                                              | 99 |

| 4.2    |         | ontrol Pins                                                                     |    |

|        | 4.2.1   | Pin status during internal ROM, internal RAM, and on-chip peripheral I/O access |    |

| 4.3    | Memor   | y Block Function                                                                |    |

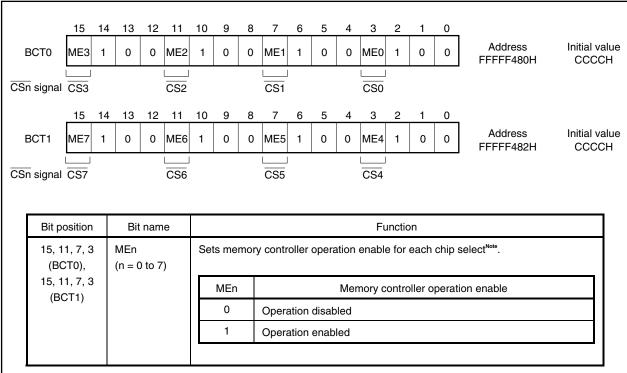

|        | 4.3.1   | Chip select control function                                  | 101 |

|--------|---------|---------------------------------------------------------------|-----|

| 4.4    | Bus C   | Cycle Type Control Function                                   | 104 |

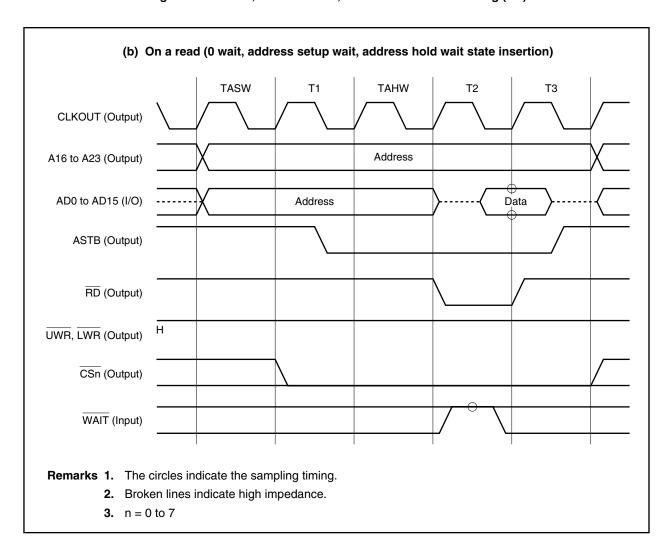

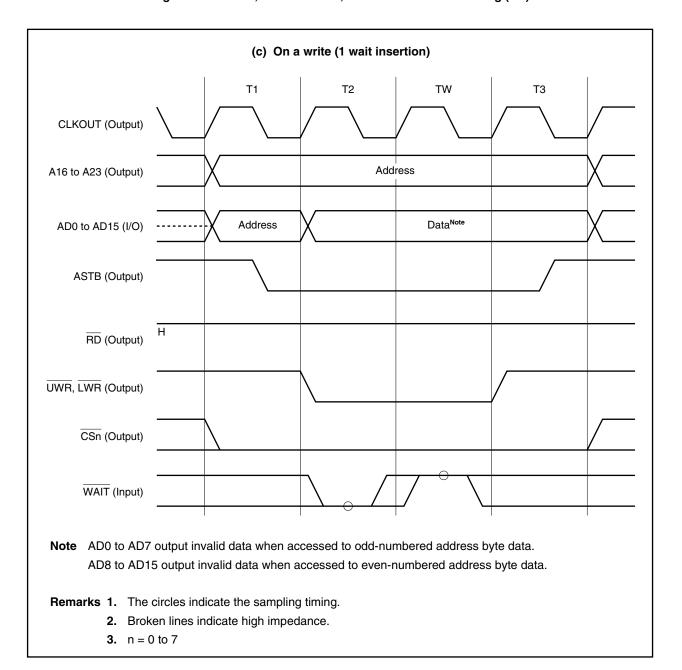

| 4.5    | Bus A   | Access                                                        | 105 |

|        | 4.5.1   | Number of access clocks                                       | 105 |

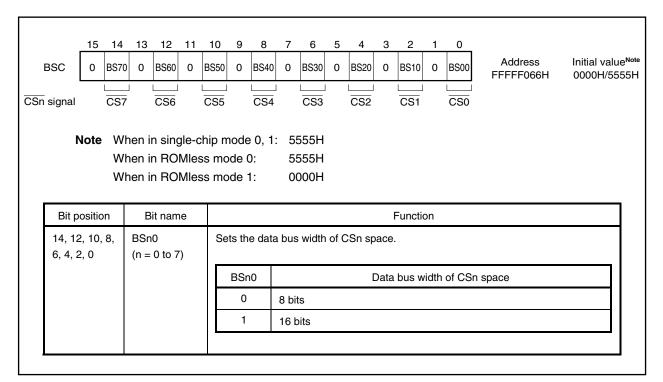

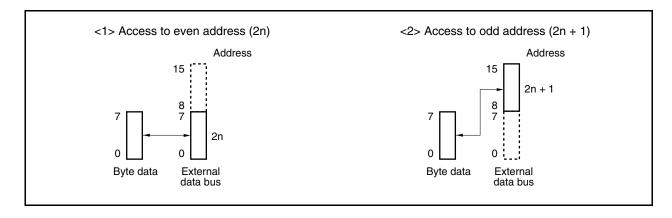

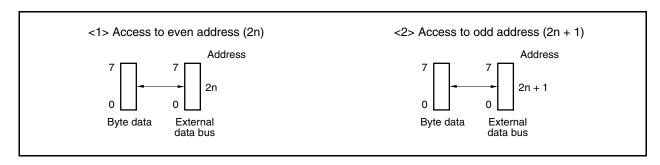

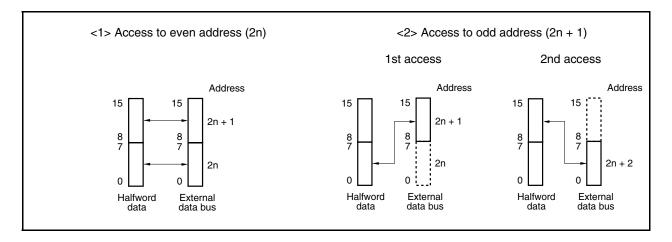

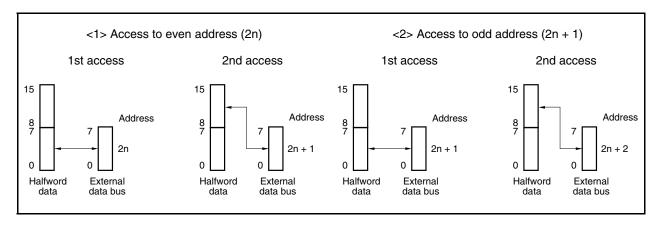

|        | 4.5.2   | Bus sizing function                                           | 106 |

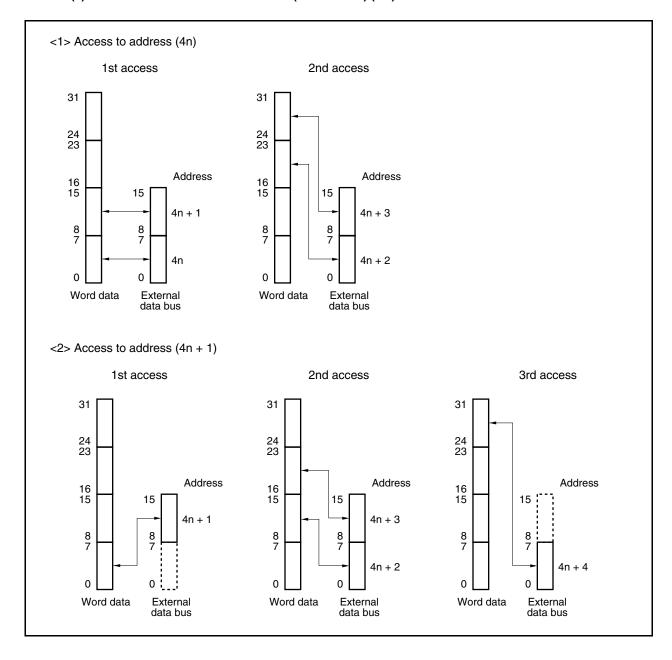

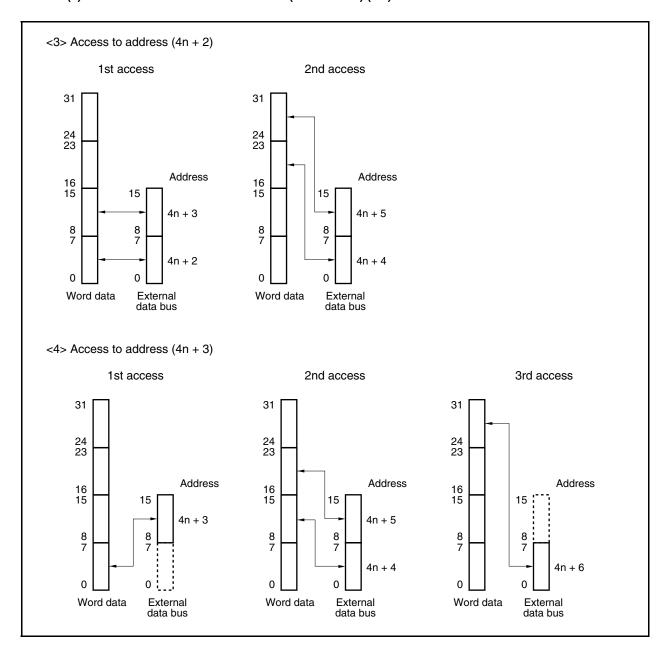

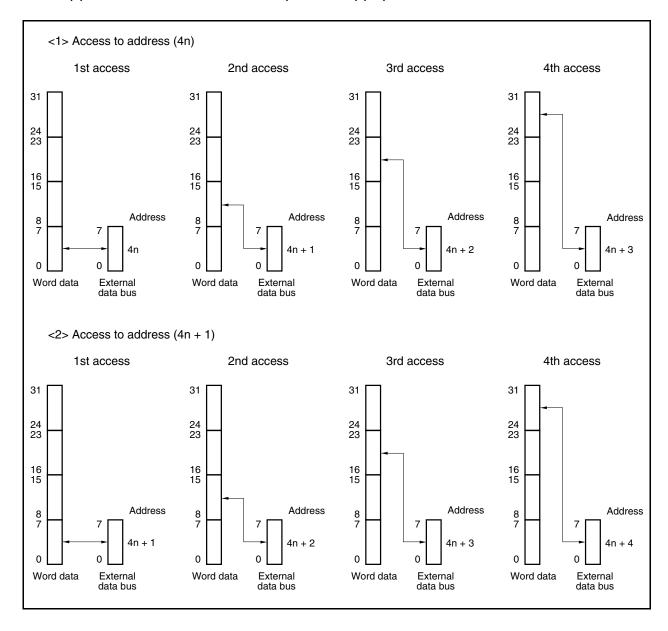

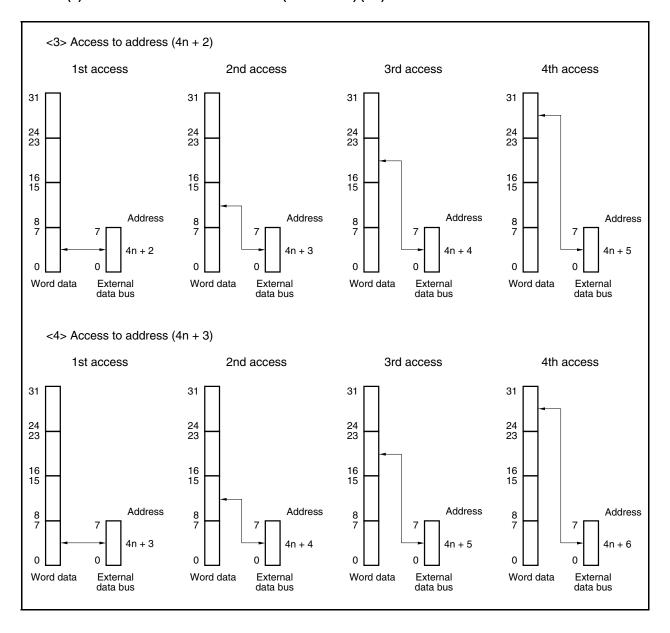

|        | 4.5.3   | Word data processing format                                   | 106 |

|        | 4.5.4   | Bus width                                                     | 107 |

| 4.6    | Wait F  | Function                                                      | 113 |

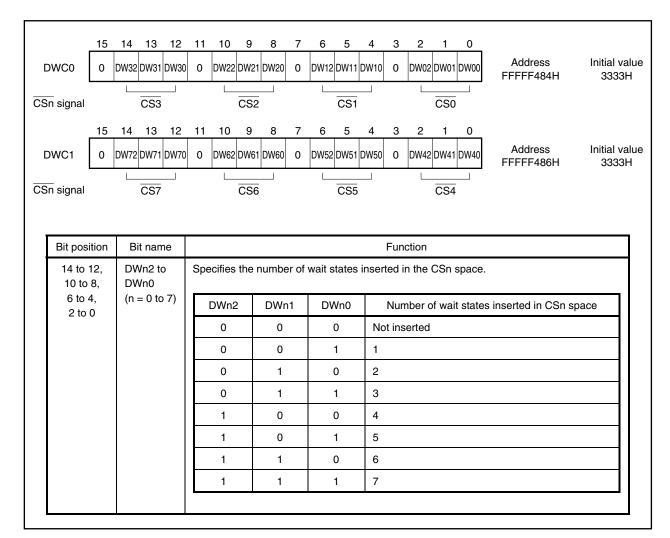

|        | 4.6.1   | Programmable wait function                                    | 113 |

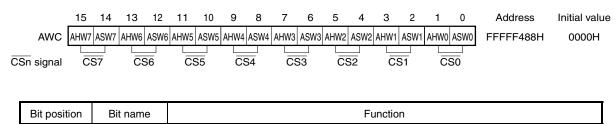

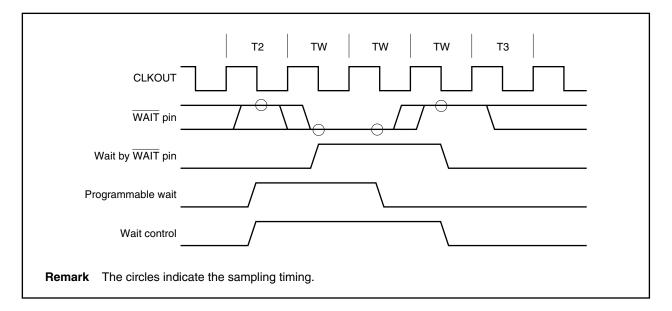

|        | 4.6.2   | External wait function                                        | 115 |

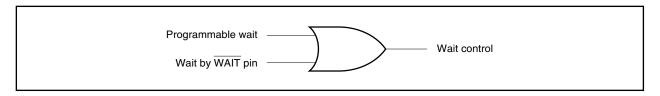

|        | 4.6.3   | Relationship between programmable wait and external wait      | 115 |

| 4.7    | Idle St | tate Insertion Function                                       | 116 |

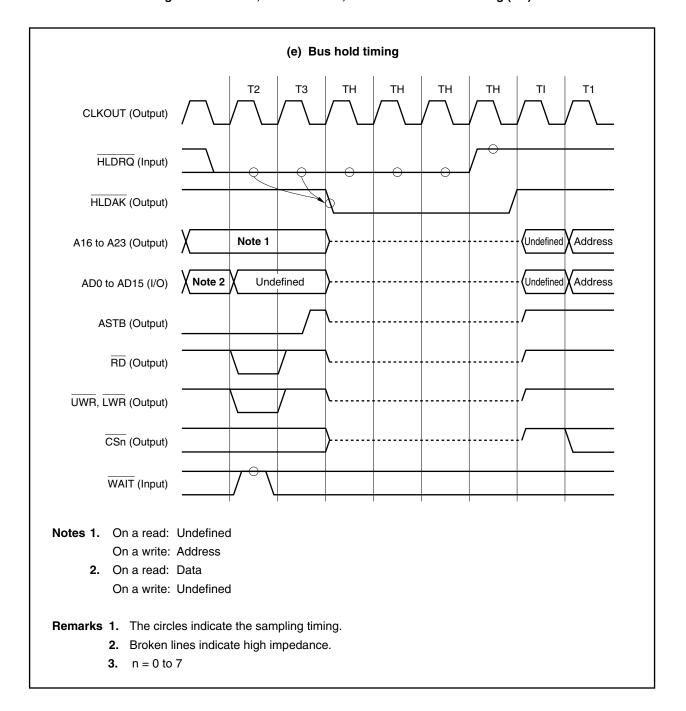

| 4.8    | Bus H   | fold Function                                                 | 117 |

|        | 4.8.1   | Function outline                                              | 117 |

|        | 4.8.2   | Bus hold procedure                                            | 117 |

|        | 4.8.3   | Operation in power save mode                                  | 118 |

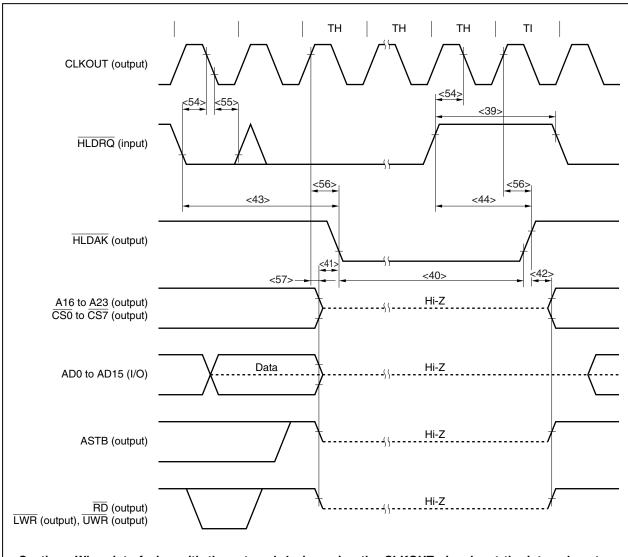

|        | 4.8.4   | Bus hold timing                                               | 118 |

| 4.9    | Bus P   | Priority Order                                                | 119 |

| 4.10   | Bound   | dary Operation Conditions                                     | 119 |

|        | 4.10.1  | Program space                                                 | 119 |

|        | 4.10.2  | Data space                                                    | 119 |

|        |         | ACMORY ACCESS CONTROL FUNCTION                                | 400 |

|        |         | MEMORY ACCESS CONTROL FUNCTION                                |     |

| 5.1    |         | /I, External ROM, External I/O Interface                      |     |

|        | 5.1.1   | Features                                                      |     |

|        | 5.1.2   | SRAM, external ROM, external I/O access                       | 121 |

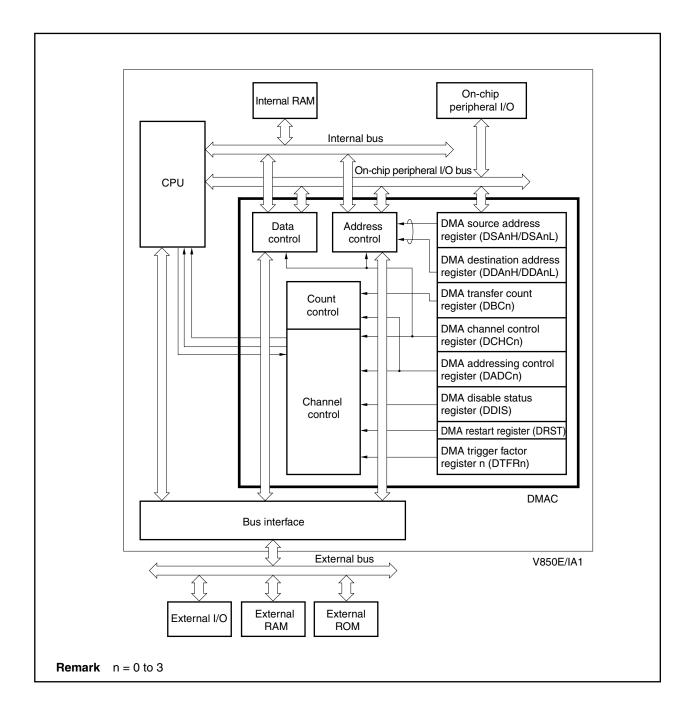

| СНАВТІ | ER 6 D  | DMA FUNCTIONS (DMA CONTROLLER)                                | 126 |

| 6.1    |         | res                                                           |     |

| 6.2    |         | guration                                                      |     |

| 6.3    | •       | ol Registers                                                  |     |

| 0.5    | 6.3.1   | DMA source address registers 0 to 3 (DSA0 to DSA3)            |     |

|        | 6.3.2   | DMA destination address registers 0 to 3 (DDA0 to DDA3)       |     |

|        | 6.3.3   | DMA transfer count registers 0 to 3 (DBC0 to DBC3)            |     |

|        | 6.3.4   | DMA addressing control registers 0 to 3 (DADC0 to DADC3)      |     |

|        | 6.3.5   | DMA channel control registers 0 to 3 (DCHC0 to DCHC3)         |     |

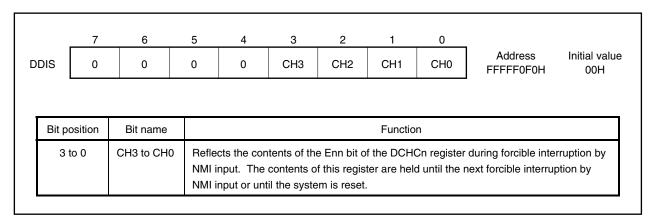

|        | 6.3.6   | DMA disable status register (DDIS)                            |     |

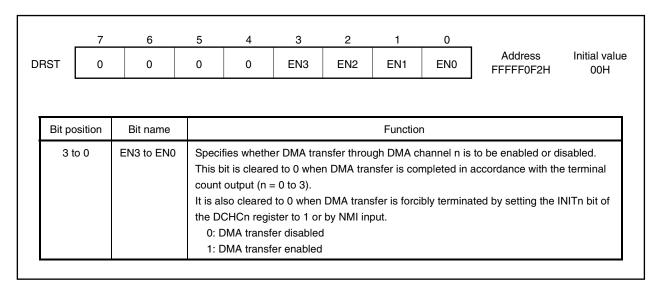

|        | 6.3.7   | DMA restart register (DRST)                                   |     |

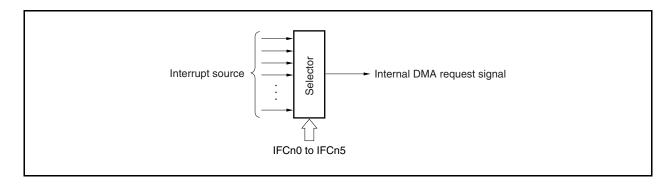

|        | 6.3.8   | DMA trigger factor registers 0 to 3 (DTFR0 to DTFR3)          |     |

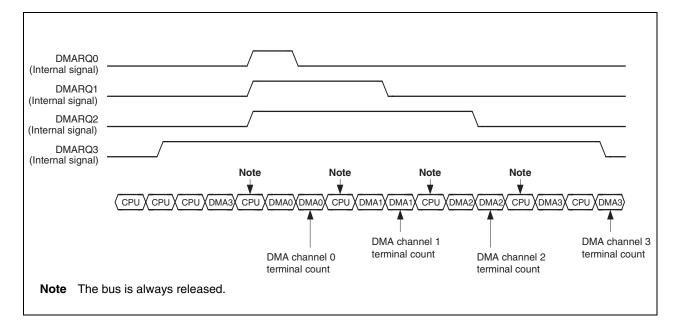

| 6.4    |         | fer Mode                                                      |     |

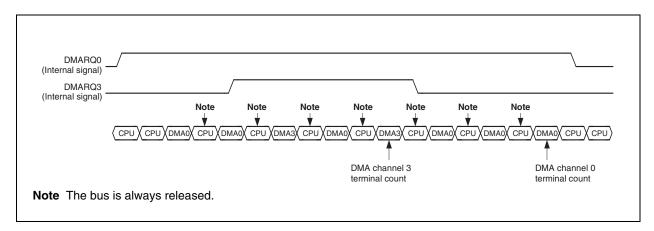

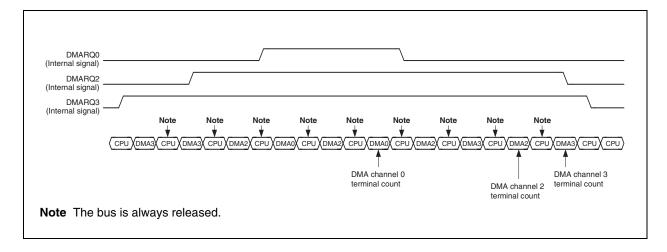

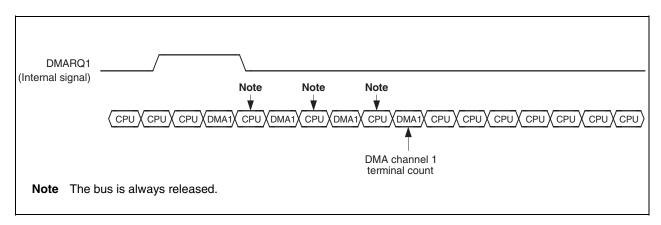

| 0.4    | 6.4.1   | Single transfer mode                                          |     |

|        | 6.4.2   | Single-step transfer mode                                     |     |

|        | 6.4.3   | Block transfer mode                                           |     |

| 6.5    |         | fer Types                                                     |     |

| 0.5    | 6.5.1   | Two-cycle transfer                                            |     |

| 6.6    |         | fer Target                                                    |     |

| 3.0    | 6.6.1   | Transfer type and transfer target                             |     |

|        | 6.6.2   | External bus cycles during DMA transfer (two-cycle transfer)  |     |

|        | ٥.٥.٢   | External bad by did adming bill than bill (two by die handle) | 147 |

| 6.7        | DMA Channel Priorities147       |                                                                  |     |  |

|------------|---------------------------------|------------------------------------------------------------------|-----|--|

| 6.8        | Next Address Setting Function14 |                                                                  |     |  |

| 6.9        | DMA Transfer Start Factors      |                                                                  |     |  |

| 6.10       | Forcib                          | ole Interruption                                                 | 150 |  |

| 6.11       | DMA 1                           | Transfer End                                                     | 150 |  |

| 6.12       | Forcib                          | ble Termination                                                  | 151 |  |

|            | 6.12.1                          | Restriction related to DMA transfer forcible termination         | 152 |  |

| 6.13       | Times                           | Related to DMA Transfer                                          | 153 |  |

| 6.14       | Preca                           | utions                                                           | 154 |  |

|            | 6.14.1                          | Interrupt factors                                                | 155 |  |

|            |                                 | NITED DUDY (EVALUATION DE CASONIA EUNICE)                        | 4   |  |

|            |                                 | NTERRUPT/EXCEPTION PROCESSING FUNCTION                           |     |  |

| 7.1<br>7.2 |                                 | res Maskable Interrupt                                           |     |  |

| 1.2        |                                 | •                                                                |     |  |

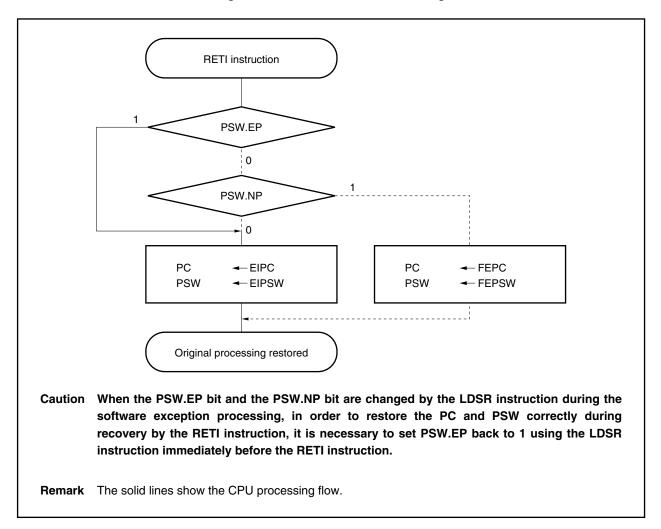

|            | 7.2.1<br>7.2.2                  | Operation                                                        |     |  |

|            |                                 | Restore                                                          |     |  |

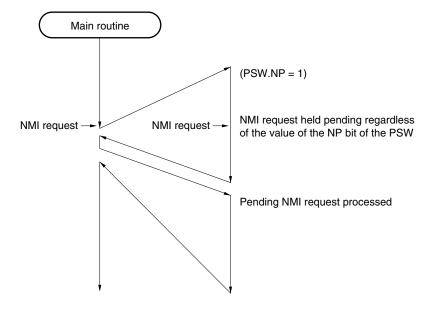

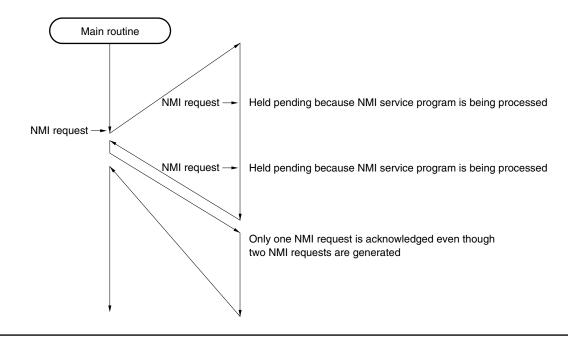

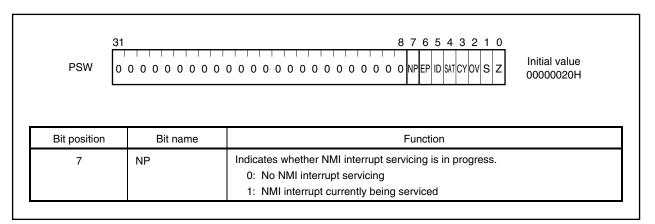

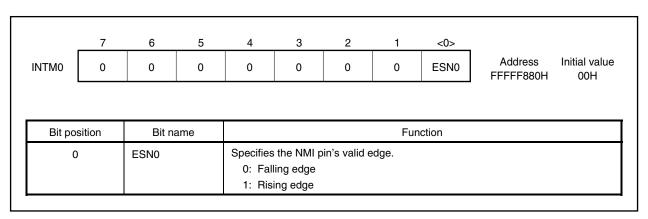

|            | 7.2.3<br>7.2.4                  | Non-maskable interrupt status flag (NP)  Edge detection function |     |  |

| 7.3        |                                 | able Interrupts                                                  |     |  |

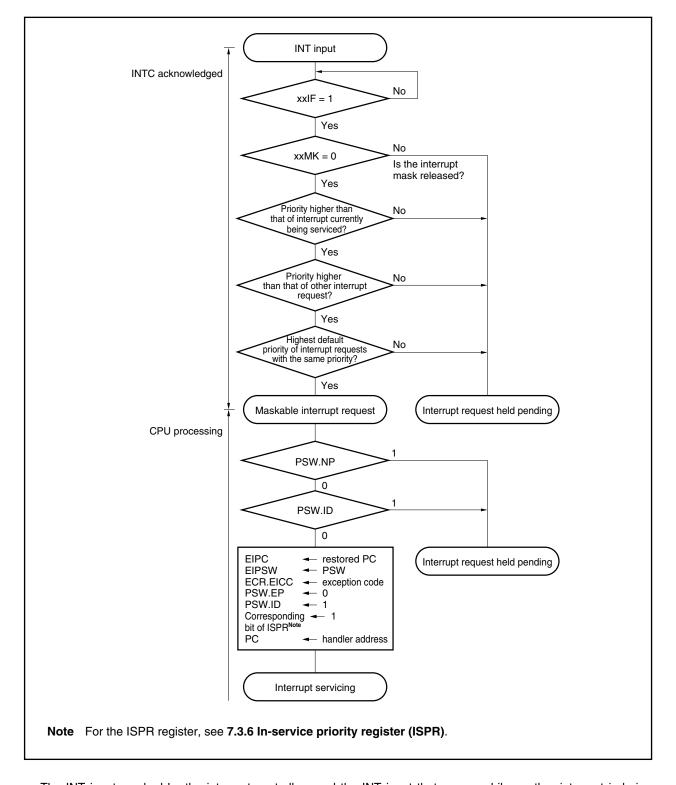

| 7.5        | 7.3.1                           | Operation                                                        |     |  |

|            | 7.3.2                           | Restore                                                          |     |  |

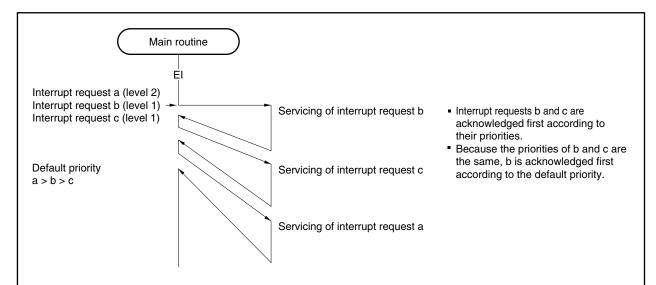

|            | 7.3.3                           | Priorities of maskable interrupts                                |     |  |

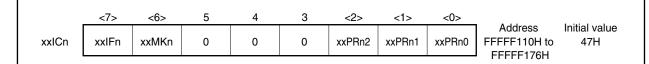

|            | 7.3.4                           | Interrupt control register (xxICn)                               |     |  |

|            | 7.3.5                           | Interrupt mask registers 0 to 3 (IMR0 to IMR3)                   |     |  |

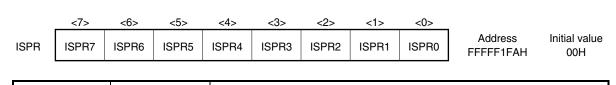

|            | 7.3.6                           | In-service priority register (ISPR)                              |     |  |

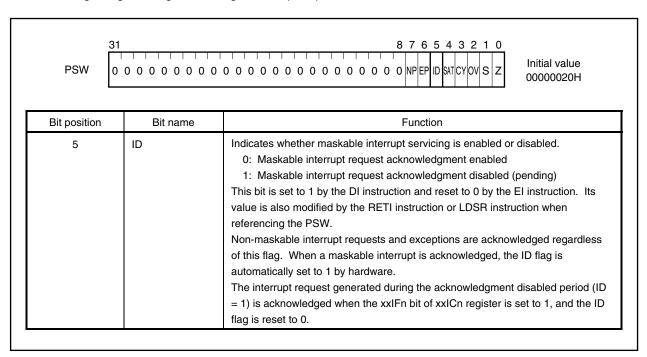

|            | 7.3.7                           | Maskable interrupt status flag (ID)                              |     |  |

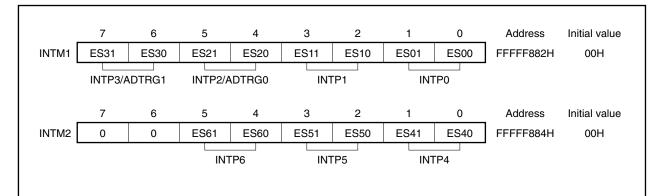

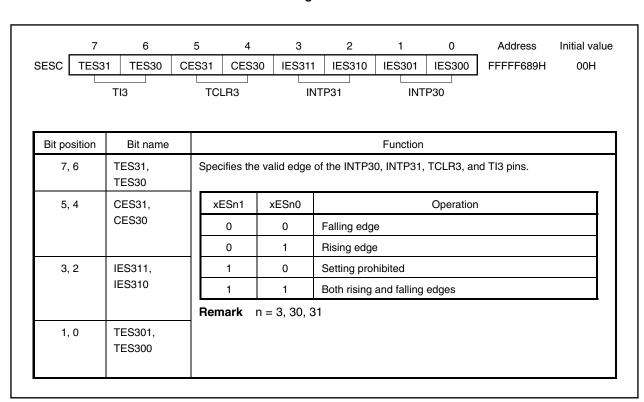

|            | 7.3.8                           | Interrupt trigger mode selection                                 |     |  |

| 7.4        | Softwa                          | are Exception                                                    |     |  |

|            | 7.4.1                           | Operation                                                        | 187 |  |

|            | 7.4.2                           | Restore                                                          | 188 |  |

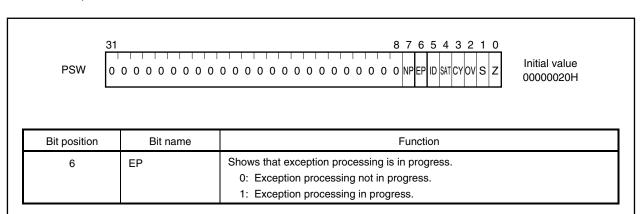

|            | 7.4.3                           | Exception status flag (EP)                                       | 189 |  |

| 7.5        | Excep                           | otion Trap                                                       | 190 |  |

|            | 7.5.1                           | Illegal opcode definition                                        | 190 |  |

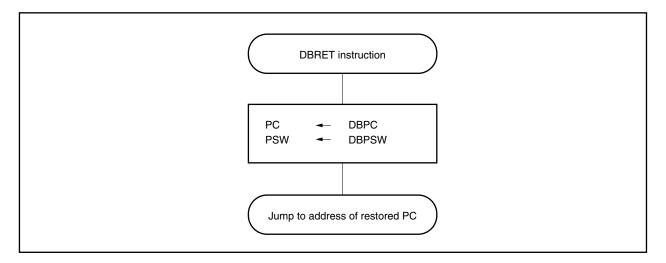

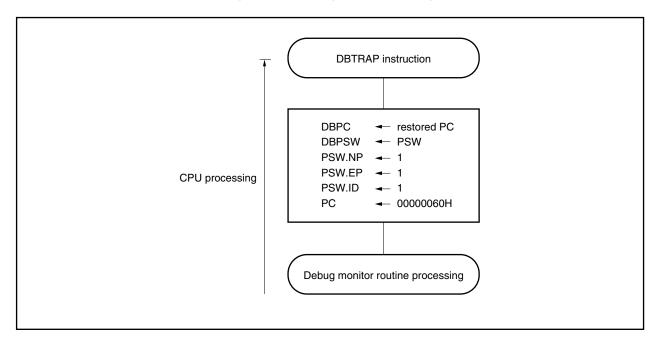

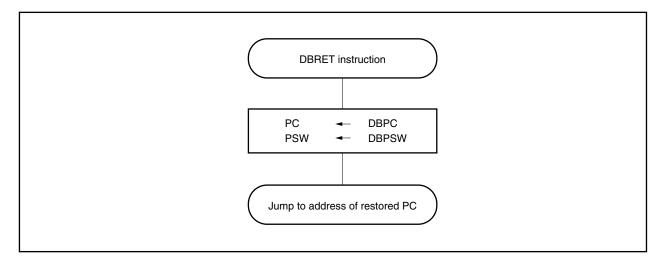

|            | 7.5.2                           | Debug trap                                                       | 192 |  |

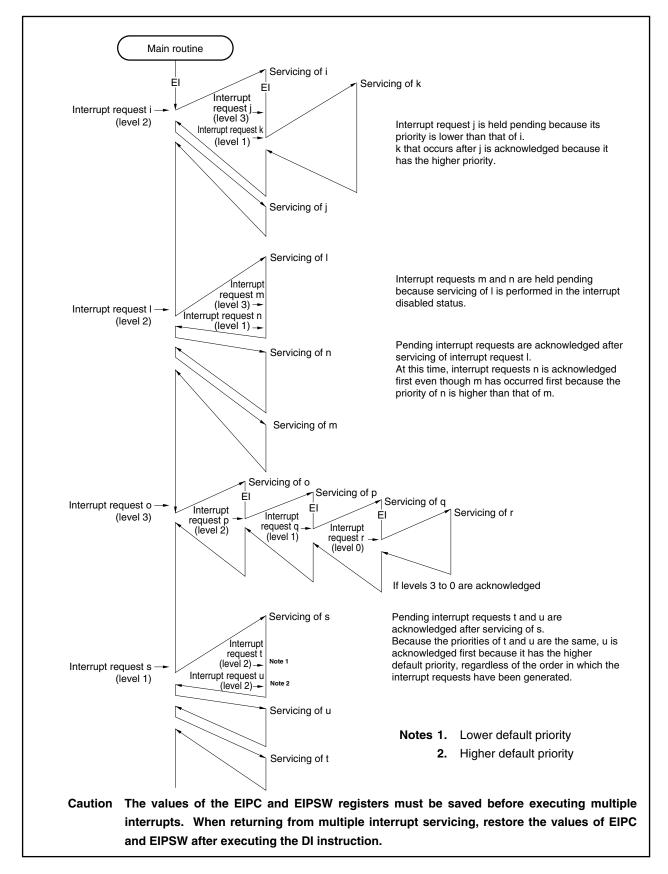

| 7.6        | Multip                          | ole Interrupt Servicing Control                                  | 194 |  |

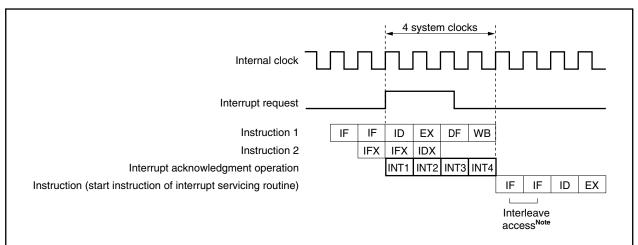

| 7.7        | Interru                         | upt Response Time                                                | 195 |  |

| 7.8        | Period                          | ds in Which CPU Does Not Acknowledge Interrupts                  | 197 |  |

|            |                                 |                                                                  |     |  |

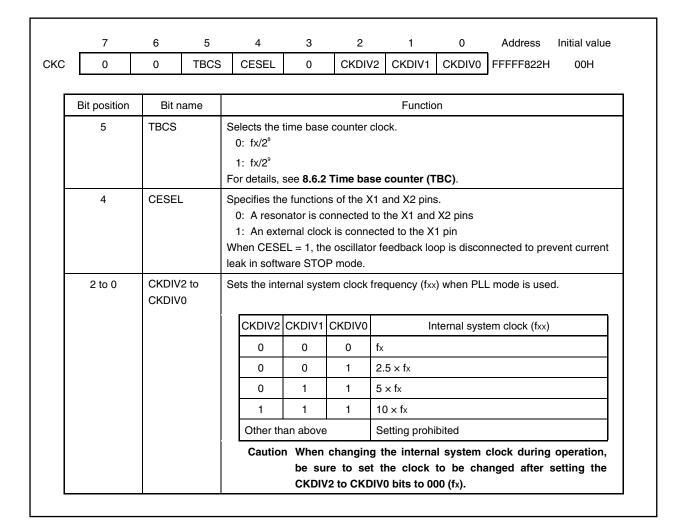

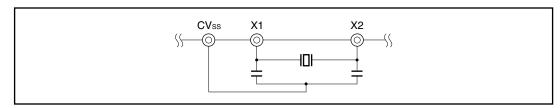

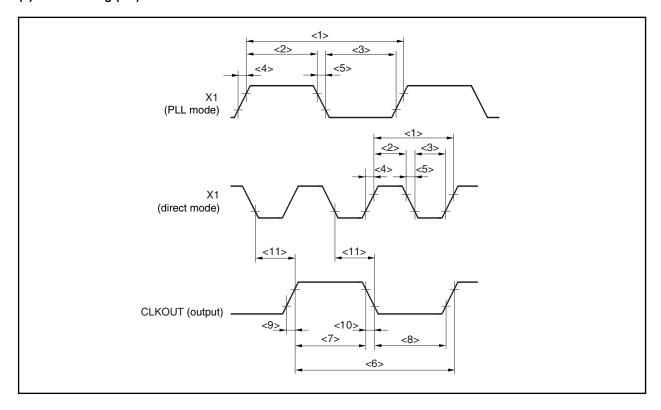

|            |                                 | CLOCK GENERATION FUNCTION                                        |     |  |

| 8.1        |                                 | res                                                              |     |  |

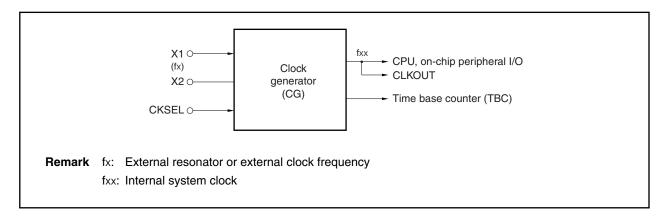

| 8.2        |                                 | guration                                                         |     |  |

| 8.3        | •                               | Clock Selection                                                  |     |  |

|            | 8.3.1                           | Direct mode                                                      |     |  |

|            | 8.3.2                           | PLL mode                                                         |     |  |

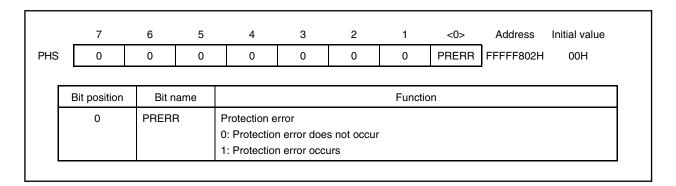

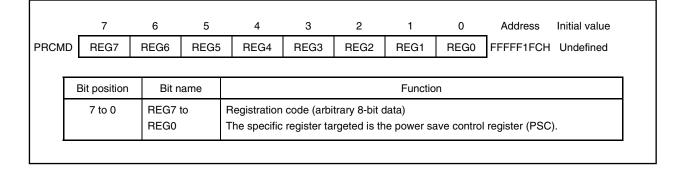

|            | 8.3.3<br>8.3.4                  | Peripheral command register (PHCMD)                              |     |  |

|            | 8.3.4<br>8.3.5                  | Peripheral status register (PHS)                                 |     |  |

| 8.4        |                                 | ockup                                                            |     |  |

| 8.5   | Power  | r Save Control                                             | 205 |

|-------|--------|------------------------------------------------------------|-----|

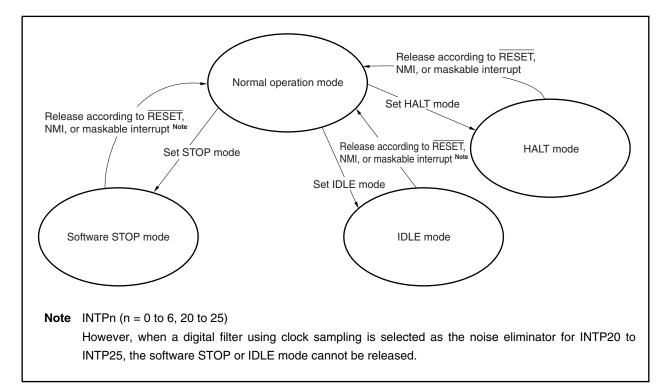

|       | 8.5.1  | Overview                                                   | 205 |

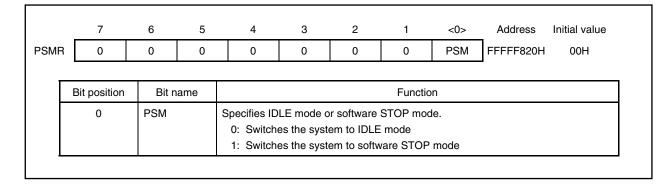

|       | 8.5.2  | Control registers                                          | 208 |

|       | 8.5.3  | HALT mode                                                  | 211 |

|       | 8.5.4  | IDLE mode                                                  | 213 |

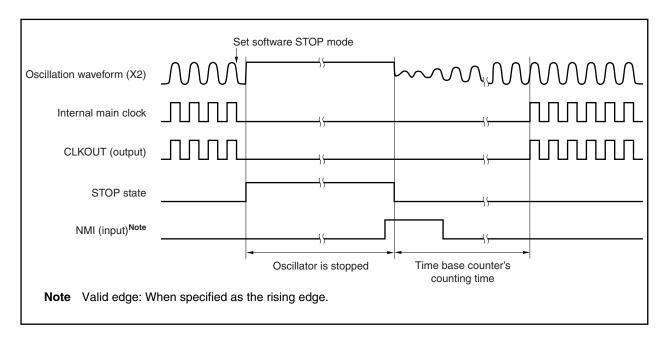

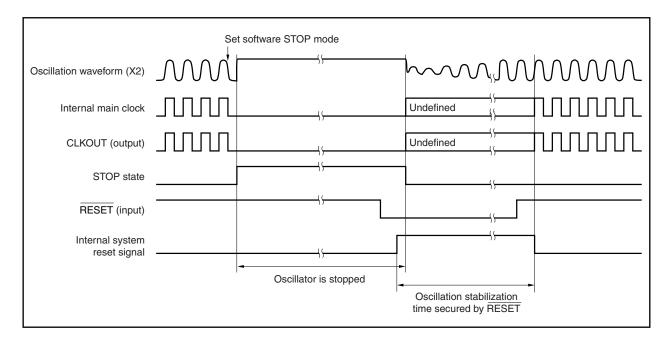

|       | 8.5.5  | Software STOP mode                                         | 215 |

| 8.6   | Secur  | ring Oscillation Stabilization Time                        | 217 |

|       | 8.6.1  | Oscillation stabilization time security specification      | 217 |

|       | 8.6.2  | Time base counter (TBC)                                    | 218 |

| CHADT | FR Q T | TIMER/COUNTER FUNCTION                                     | 210 |

| 9.1   |        | · 0                                                        |     |

| 0     | 9.1.1  | Features (timer 0)                                         |     |

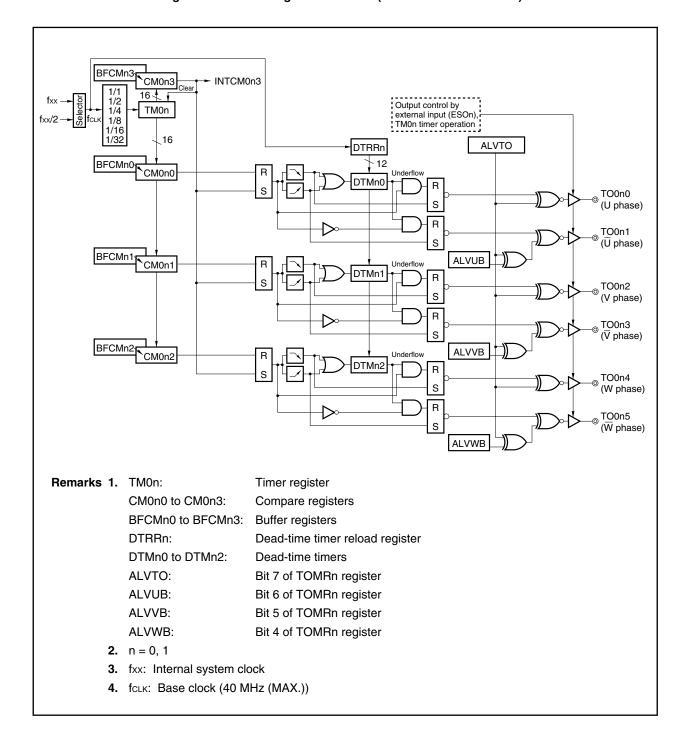

|       | 9.1.2  | Function overview (timer 0)                                |     |

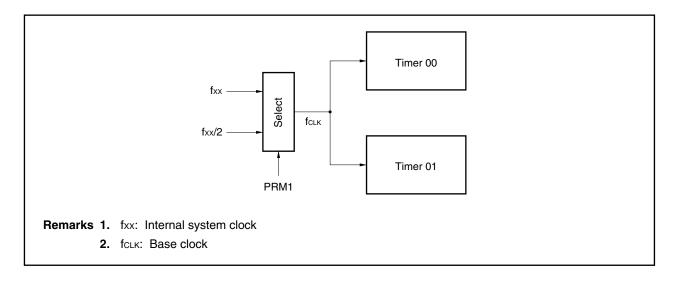

|       | 9.1.3  | Basic configuration                                        |     |

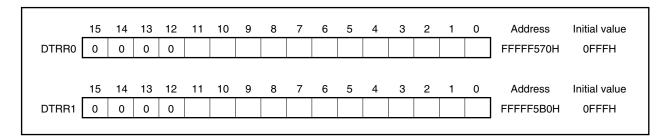

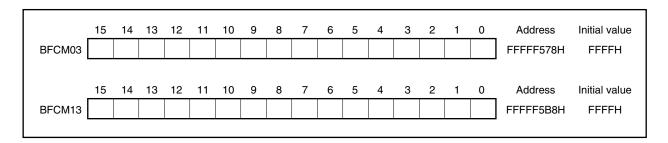

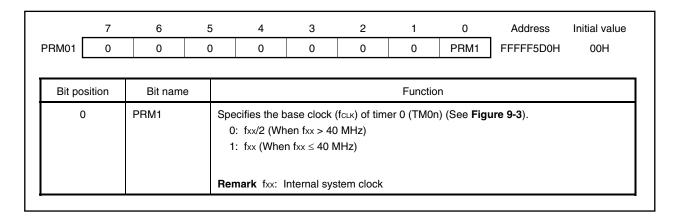

|       | 9.1.4  | Control registers                                          |     |

|       | 9.1.5  | Operation                                                  |     |

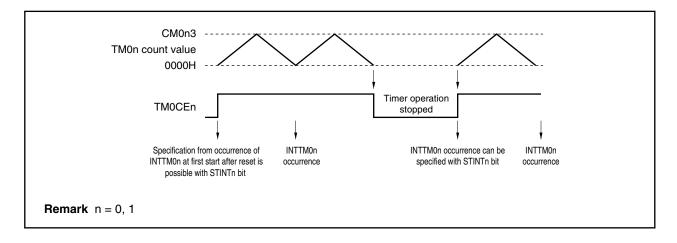

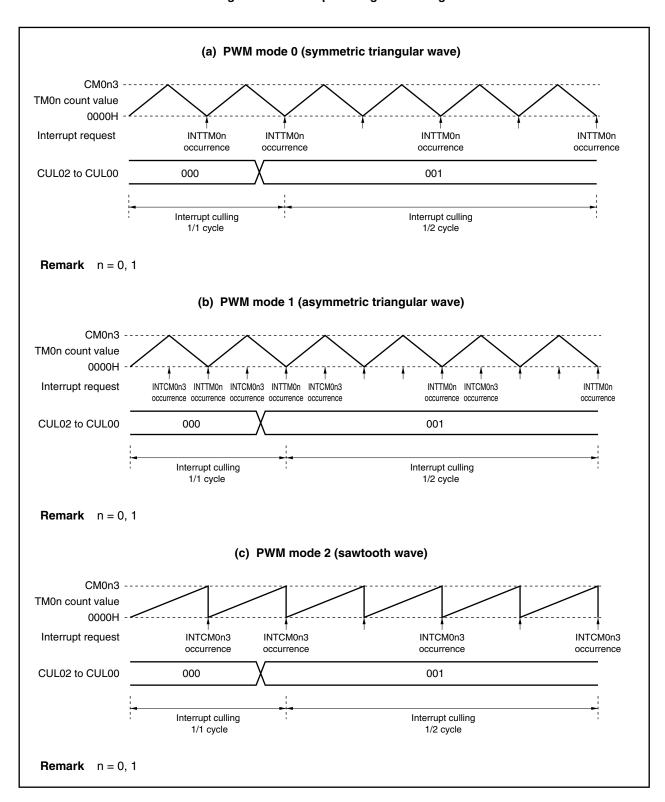

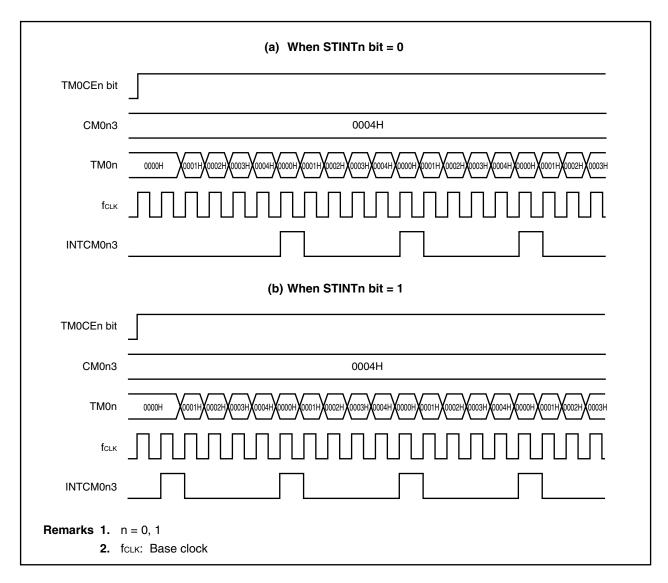

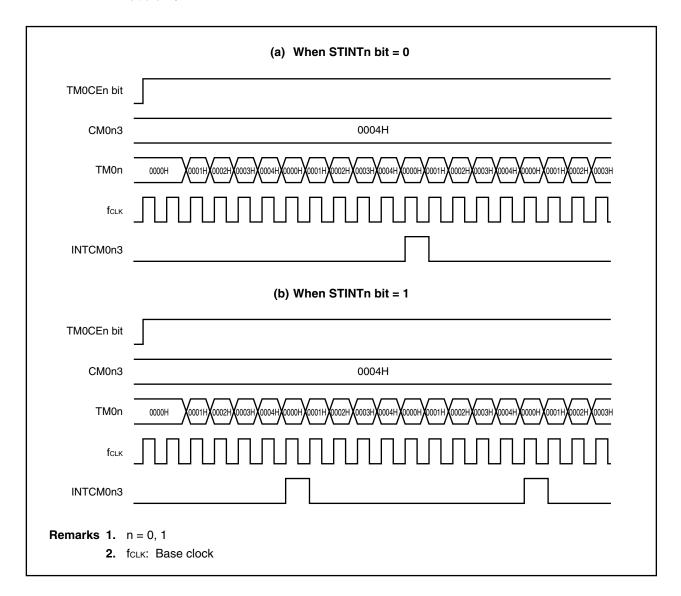

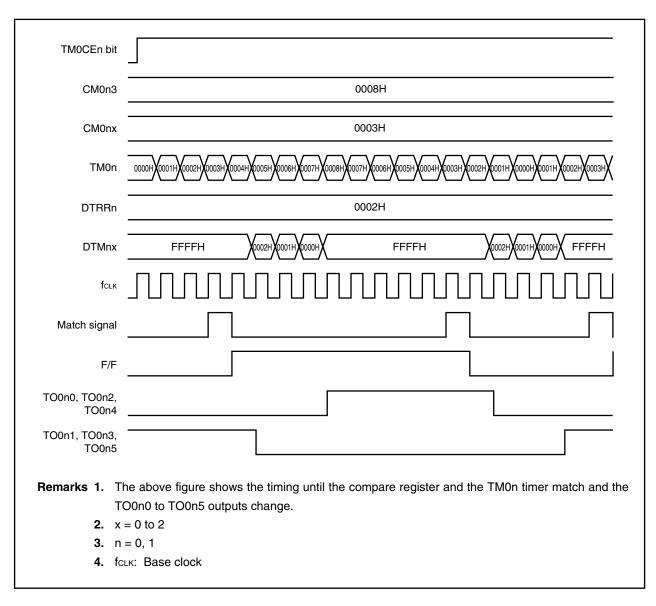

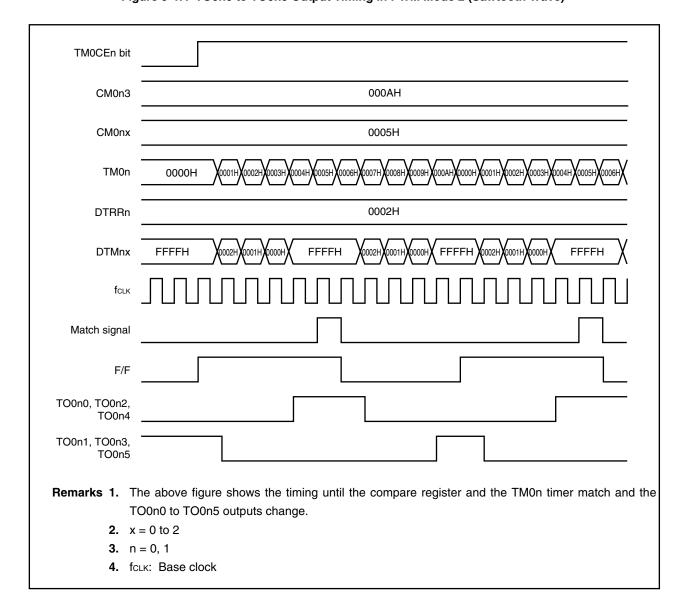

|       | 9.1.6  | Operation timing                                           |     |

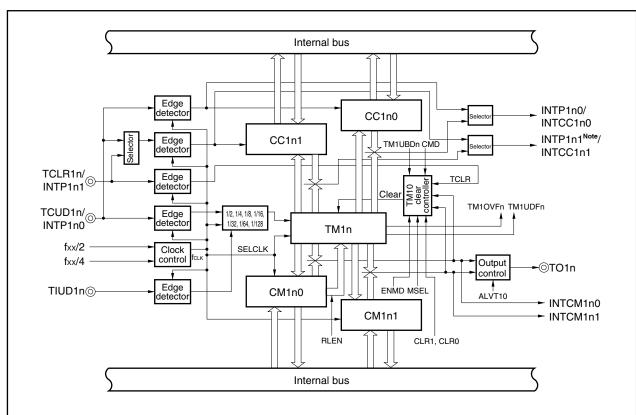

| 9.2   |        | · 1                                                        |     |

| 0.2   | 9.2.1  | Features (timer 1)                                         |     |

|       | 9.2.2  | Function overview (timer 1)                                |     |

|       | 9.2.3  | Basic configuration                                        |     |

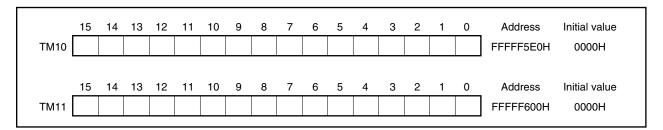

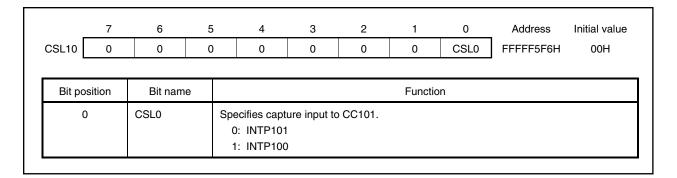

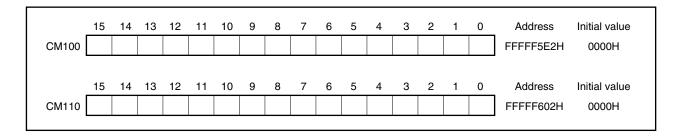

|       | 9.2.4  | Control registers                                          |     |

|       | 9.2.5  | Operation                                                  |     |

|       | 9.2.6  | Supplementary description of internal operation            |     |

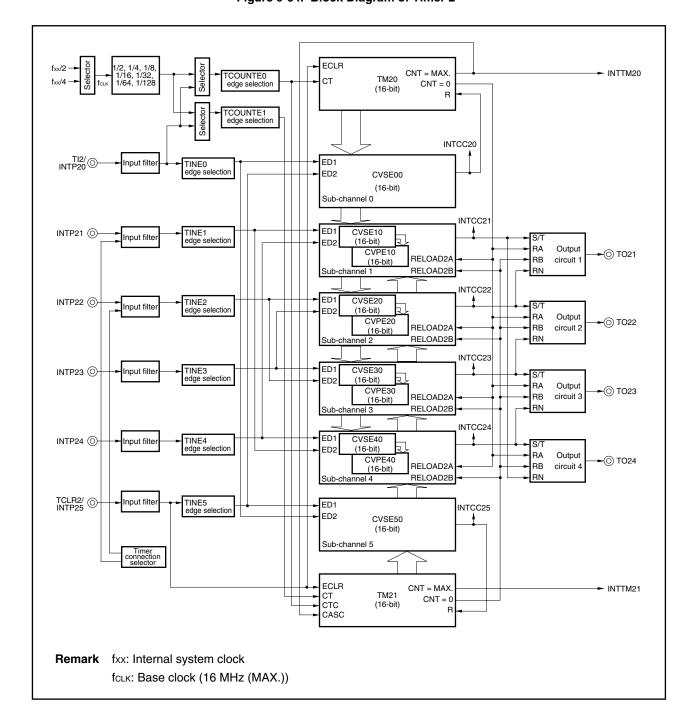

| 9.3   | Timer  | · 2                                                        |     |

|       | 9.3.1  | Features (timer 2)                                         | 327 |

|       | 9.3.2  | Function overview (timer 2)                                |     |

|       | 9.3.3  | Basic configuration                                        | 329 |

|       | 9.3.4  | Control registers                                          | 336 |

|       | 9.3.5  | Operation                                                  |     |

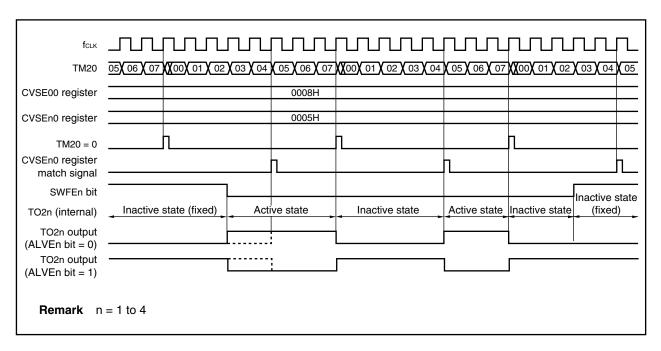

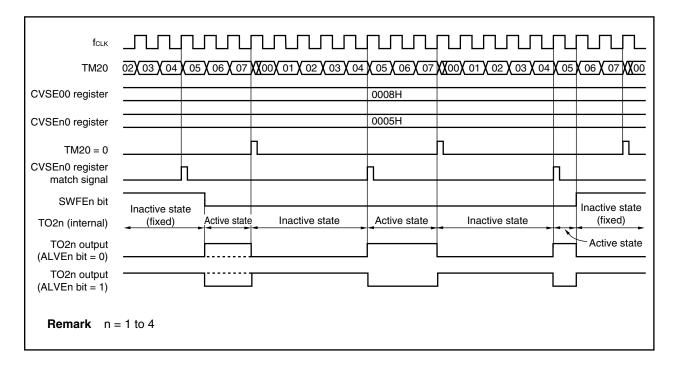

|       | 9.3.6  | PWM output operation when timer 2 operates in compare mode |     |

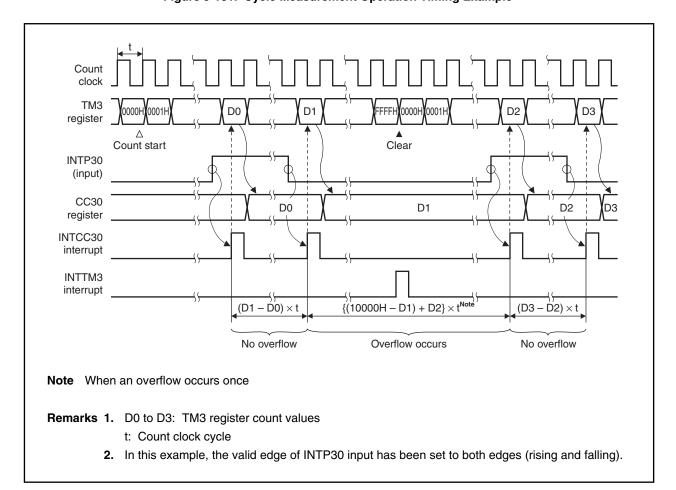

| 9.4   | Timer  | · 3                                                        |     |

|       | 9.4.1  | Features (timer 3)                                         | 375 |

|       | 9.4.2  | Function overview (timer 3)                                | 375 |

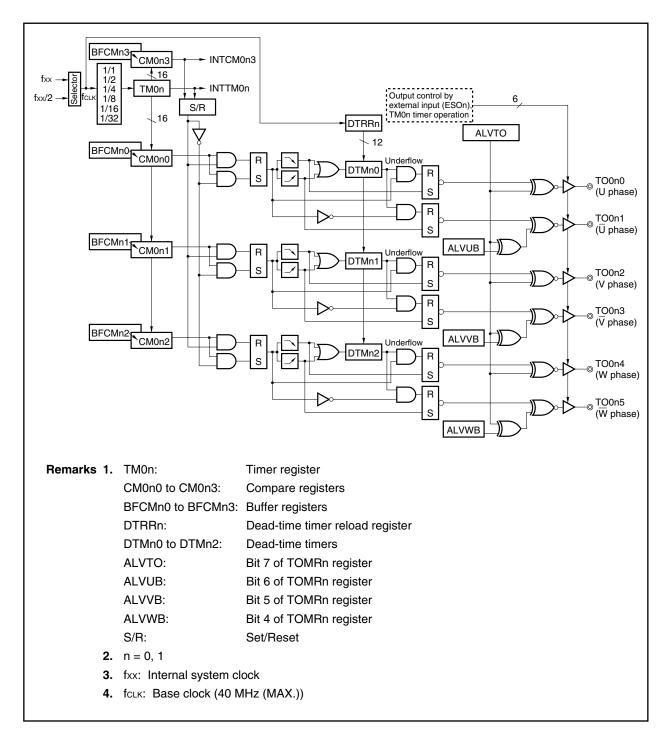

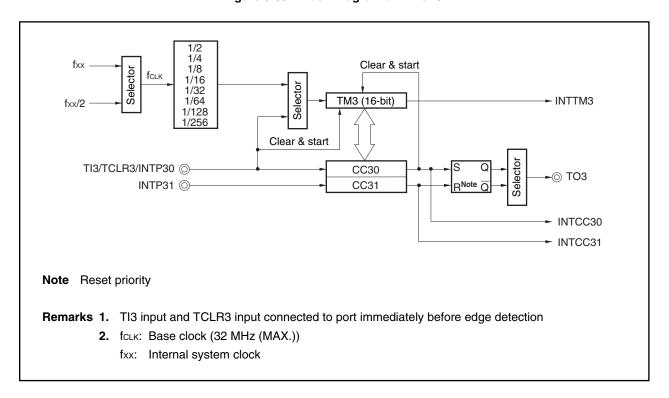

|       | 9.4.3  | Basic configuration                                        | 376 |

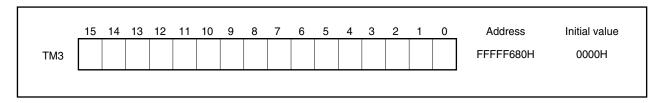

|       | 9.4.4  | Control registers                                          | 381 |

|       | 9.4.5  | Operation                                                  | 387 |

|       | 9.4.6  | Application examples                                       | 394 |

|       | 9.4.7  | Precautions                                                | 400 |

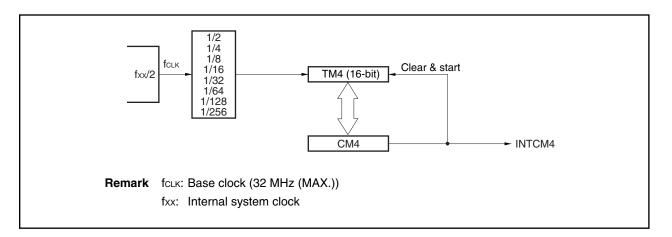

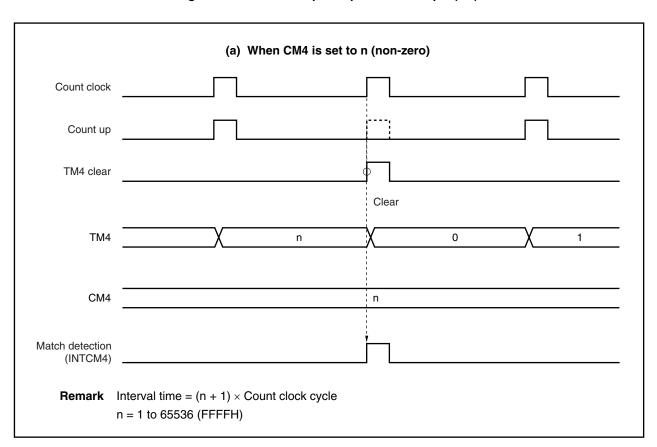

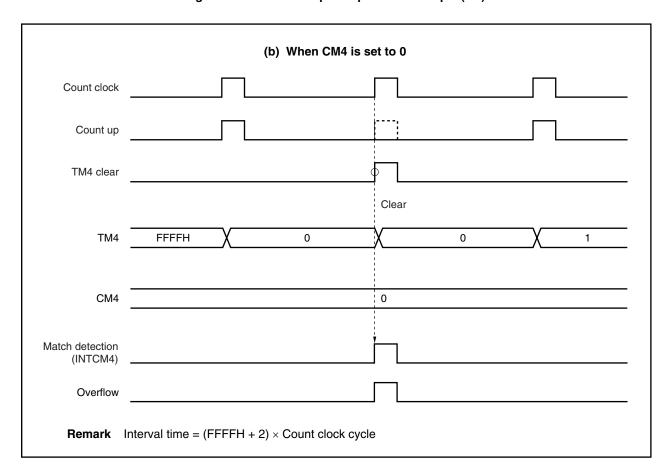

| 9.5   | Timer  | <sup>,</sup> 4                                             | 401 |

|       | 9.5.1  | Features (timer 4)                                         | 401 |

|       | 9.5.2  | Function overview (timer 4)                                | 401 |

|       | 9.5.3  | Basic configuration                                        | 402 |

|       | 9.5.4  | Control register                                           | 406 |

|       | 9.5.5  | Operation                                                  | 407 |

|       | 9.5.6  | Application example                                        | 409 |

|       | 9.5.7  | Precautions                                                | 409 |

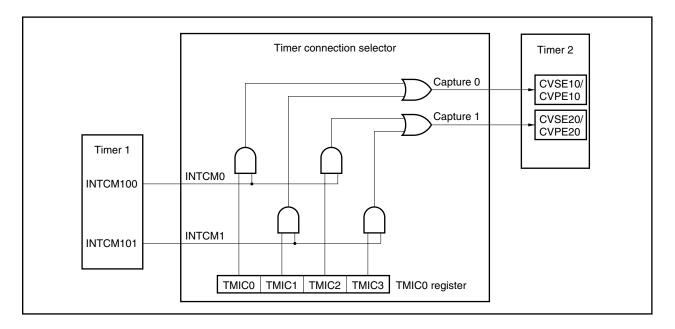

| 9.6    | Timer  | Connection Function                              | 410 |

|--------|--------|--------------------------------------------------|-----|

|        | 9.6.1  | Overview                                         | 410 |

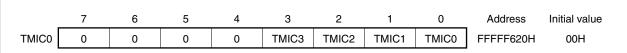

|        | 9.6.2  | Control register                                 | 411 |

| CHAPTE | R 10   | SERIAL INTERFACE FUNCTION                        | 412 |

| 10.1   | Featur | res                                              | 412 |

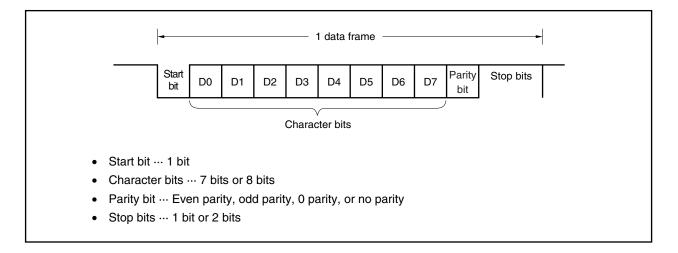

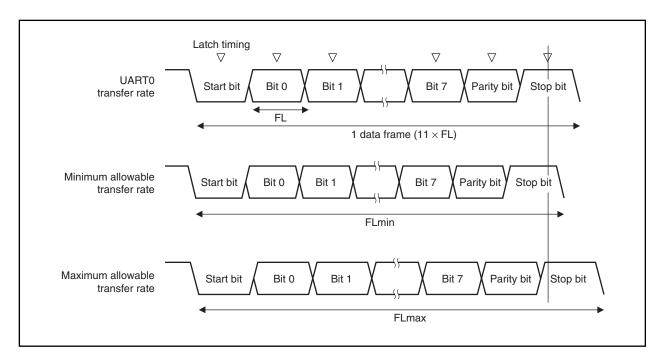

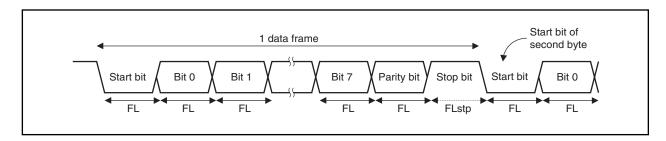

| 10.2   | Async  | chronous Serial Interface 0 (UART0)              | 413 |

|        | 10.2.1 | Features                                         | 413 |

|        | 10.2.2 | Configuration                                    | 414 |

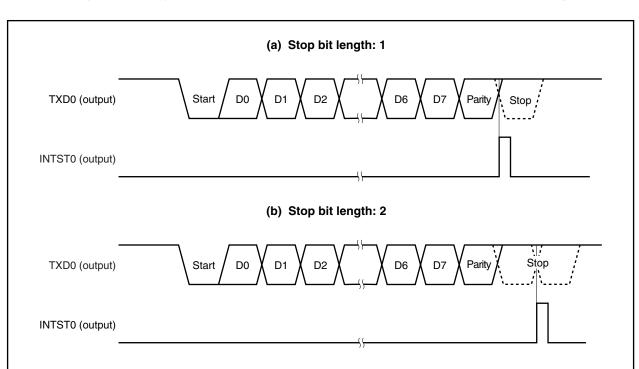

|        | 10.2.3 | Control registers                                | 416 |

|        | 10.2.4 | Interrupt requests                               | 423 |

|        | 10.2.5 | Operation                                        | 424 |

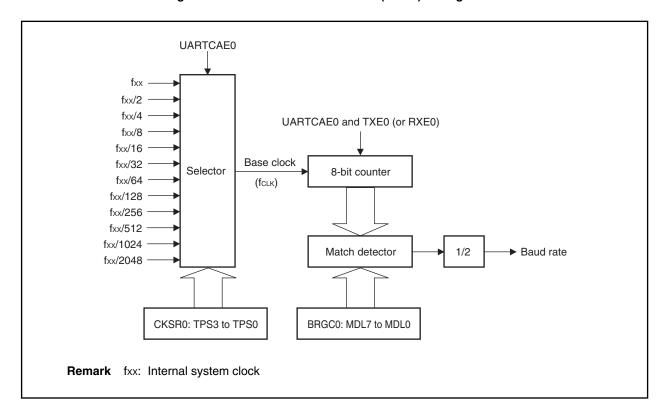

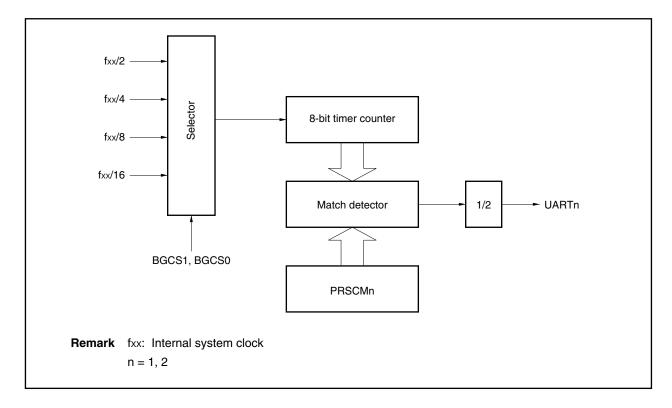

|        | 10.2.6 | Dedicated baud rate generator 0 (BRG0)           | 436 |

|        | 10.2.7 | Precautions                                      | 443 |

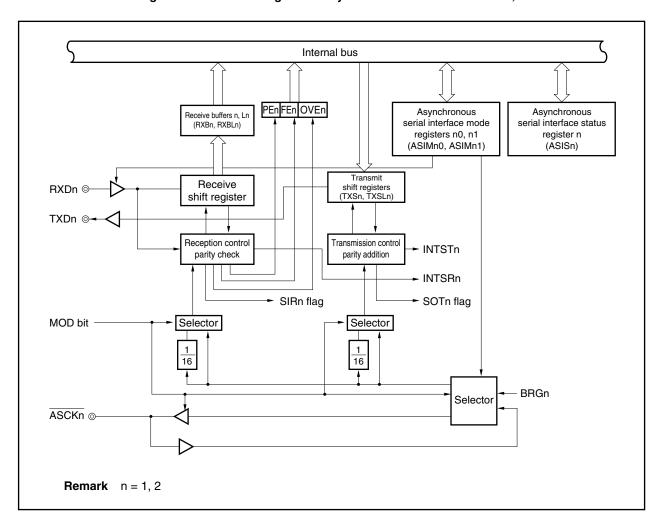

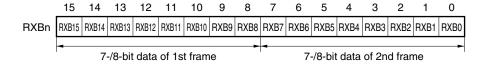

| 10.3   | Async  | chronous Serial Interfaces 1, 2 (UART1, UART2)   | 444 |

|        | 10.3.1 | Features                                         | 444 |

|        | 10.3.2 | Configuration                                    | 445 |

|        | 10.3.3 | Control registers                                | 447 |

|        | 10.3.4 | Interrupt requests                               | 456 |

|        | 10.3.5 | Operation                                        | 457 |

|        | 10.3.6 | Synchronous mode                                 | 466 |

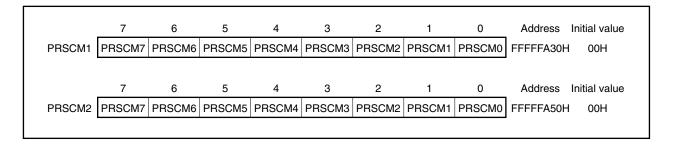

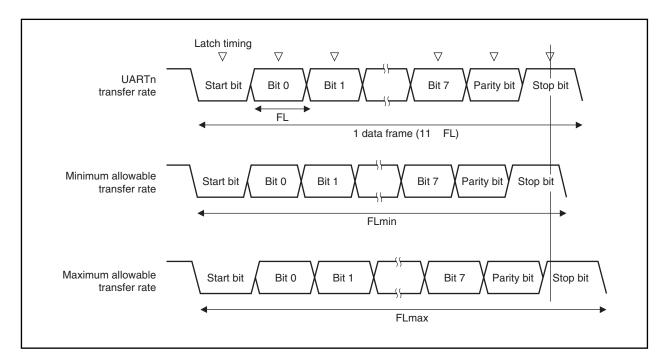

|        | 10.3.7 | Dedicated baud rate generators 1, 2 (BRG1, BRG2) | 471 |

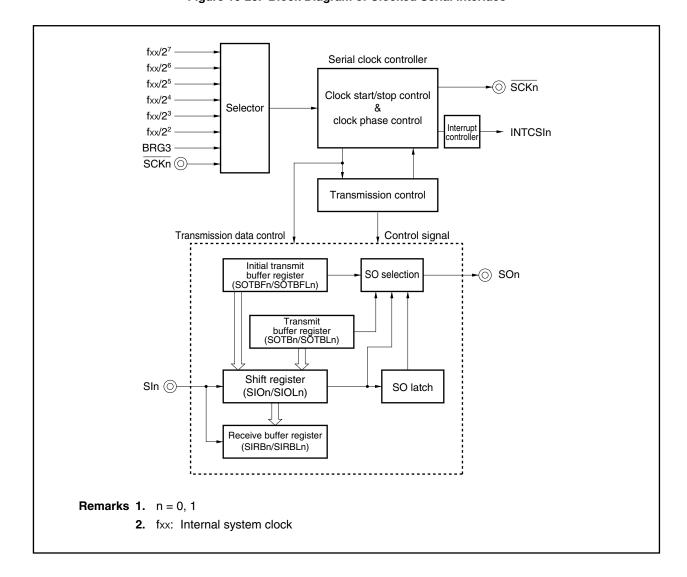

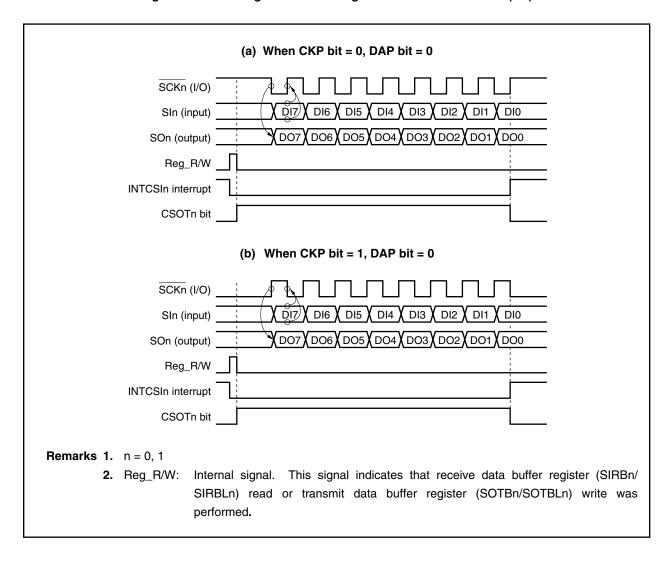

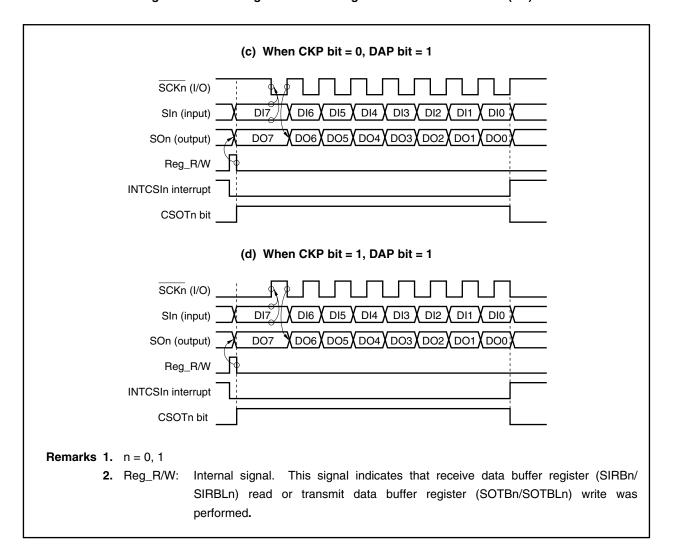

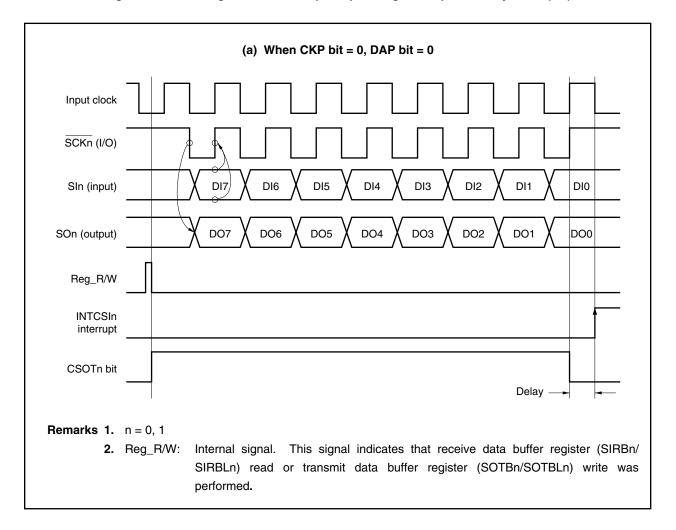

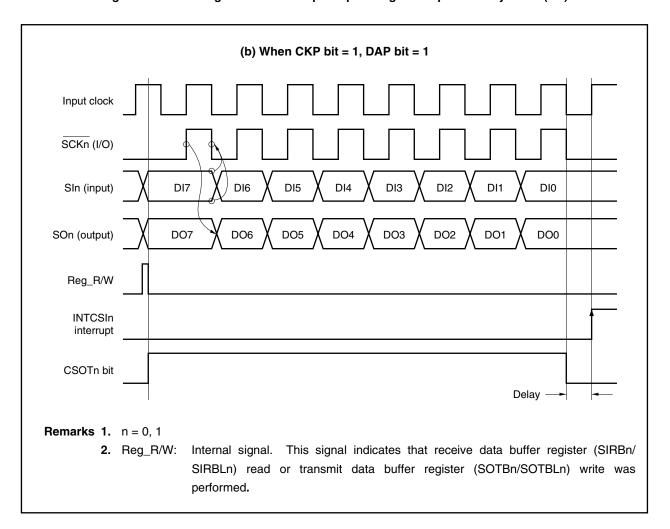

| 10.4   | Clocke | ed Serial Interfaces 0, 1 (CSI0, CSI1)           | 479 |

|        | 10.4.1 | Features                                         | 479 |

|        | 10.4.2 | Configuration                                    | 479 |

|        | 10.4.3 | Control registers                                | 481 |

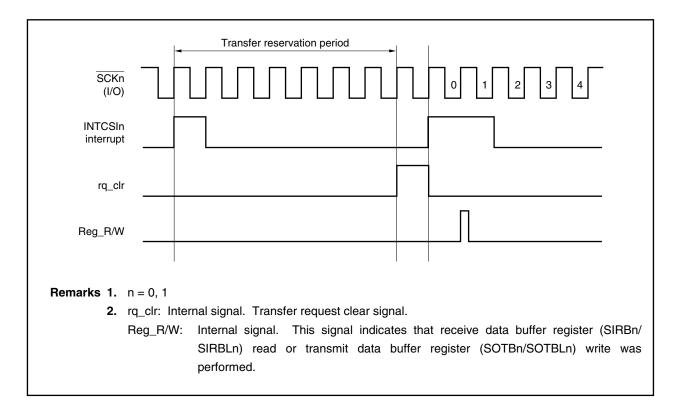

|        | 10.4.4 | Operation                                        | 495 |

|        | 10.4.5 | Output pins                                      | 510 |

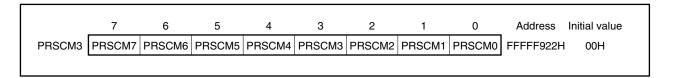

|        | 10.4.6 | Dedicated baud rate generator 3 (BRG3)           | 511 |

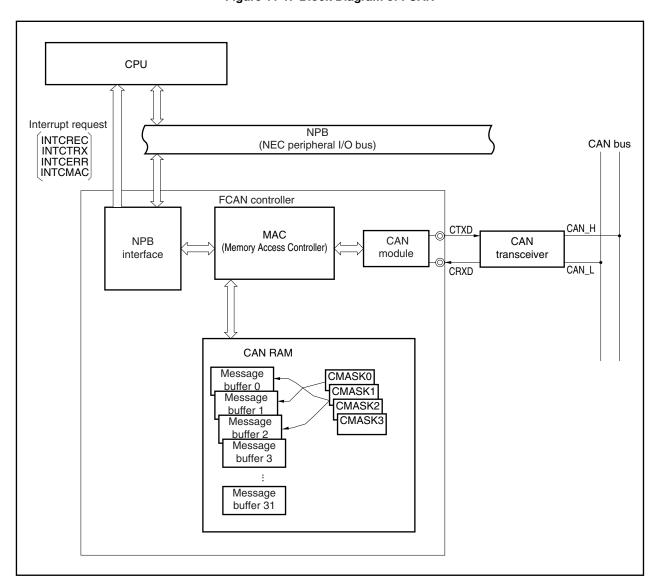

| CHAPTE | R 11   | FCAN CONTROLLER                                  | 515 |

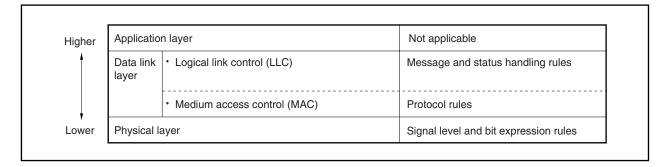

|        |        | ion Overview                                     |     |

| 11.2   | -      | guration                                         |     |

| 11.3   | Config | guration of Messages and Buffers                 | 518 |

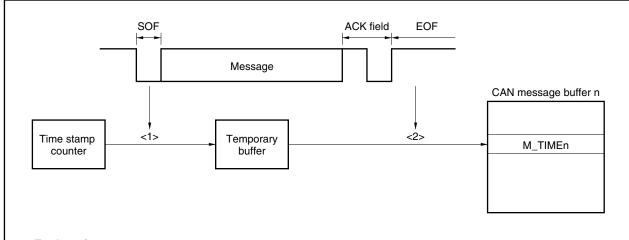

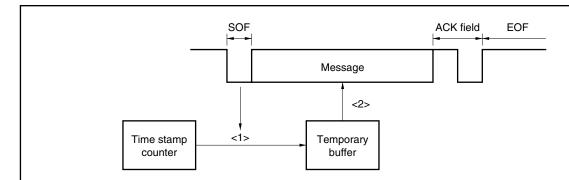

| 11.4   |        | Stamp Function                                   |     |

| 11.5   | Messa  | age Processing                                   |     |

|        | 11.5.1 | Message transmission                             | 522 |

|        | 11.5.2 | Message reception                                | 524 |

| 11.6   |        | Function                                         |     |

| 11.7   | Protoc | col                                              | 527 |

|        | 11.7.1 | Protocol mode function                           | 527 |

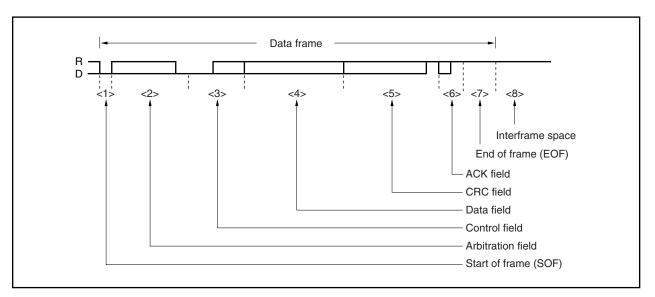

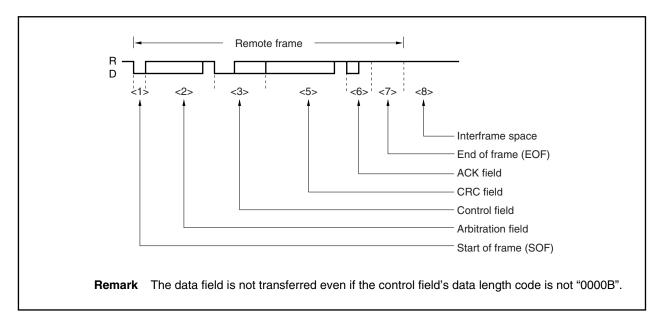

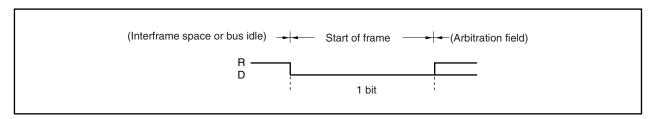

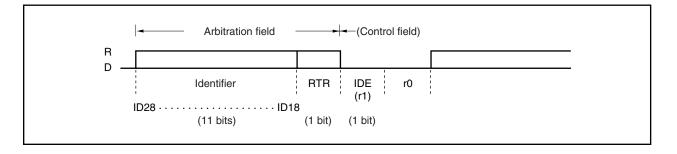

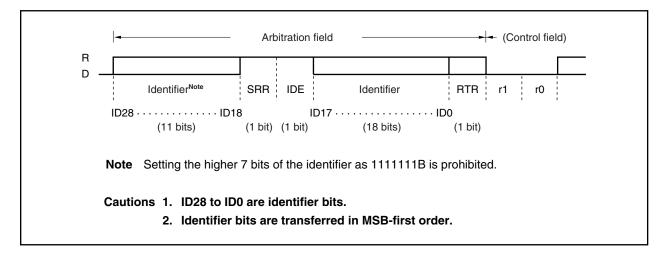

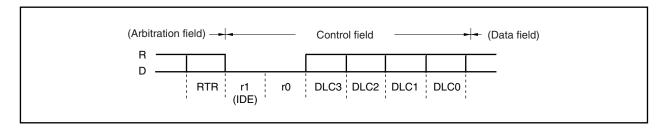

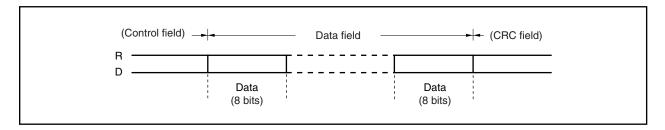

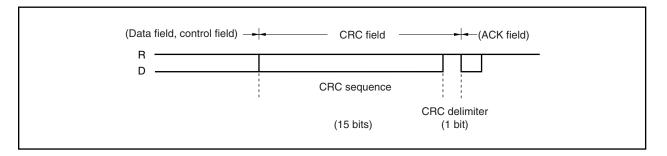

|        | 11.7.2 | Message formats                                  | 528 |

| 11.8   | Functi | ions                                             | 537 |

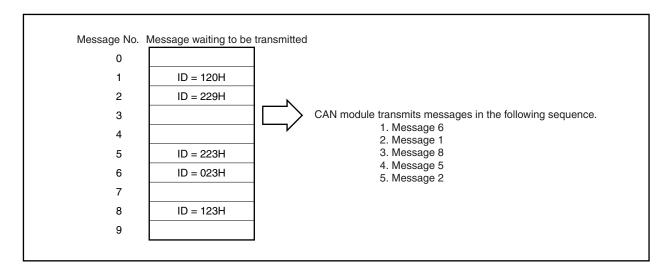

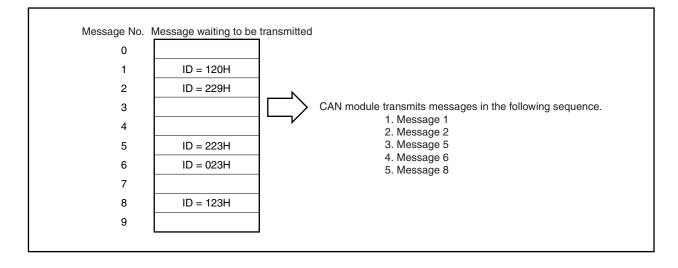

|        | 11.8.1 | Determination of bus priority                    | 537 |

|        | 11.8.2 | Bit stuffing                                     | 537 |

|        | 11.8.3 | Multi-master                                     |     |

|        | 11.8.4 | Multi-cast                                       |     |

|        | 11.8.5 | CAN sleep mode/CAN stop mode function            | 538 |

|         | 11.8.6 Error control function                                       | 538 |

|---------|---------------------------------------------------------------------|-----|

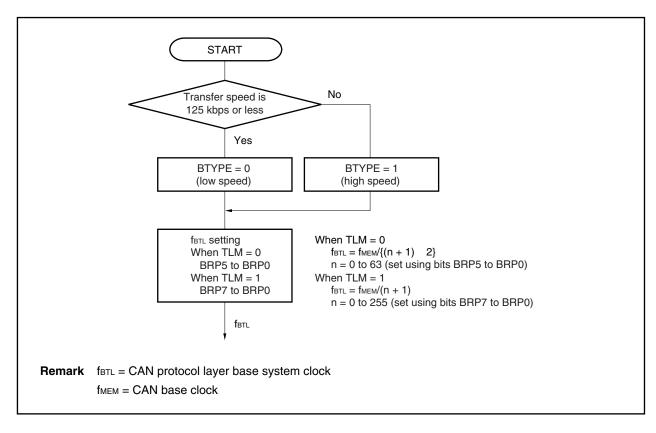

|         | 11.8.7 Baud rate control function                                   | 541 |

| 11.9    | Cautions on Bit Set/Clear Function                                  | 544 |

| 11.10   | 0 Control Registers                                                 | 546 |

| 11.11   | 1 Operations                                                        | 598 |

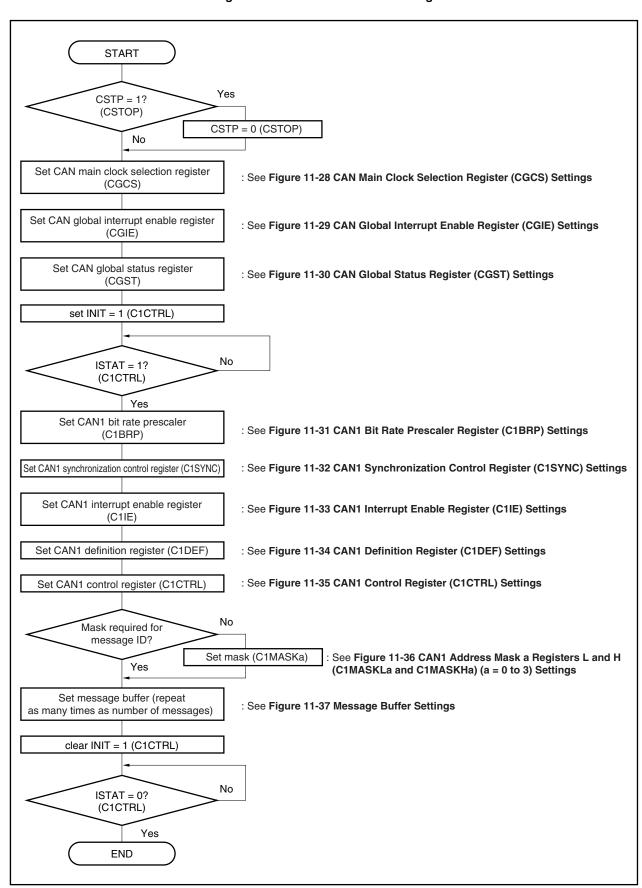

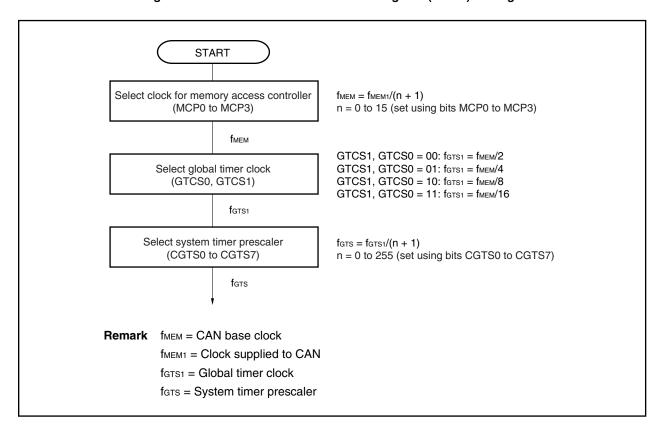

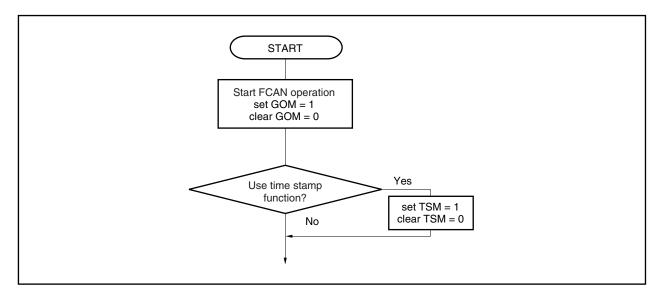

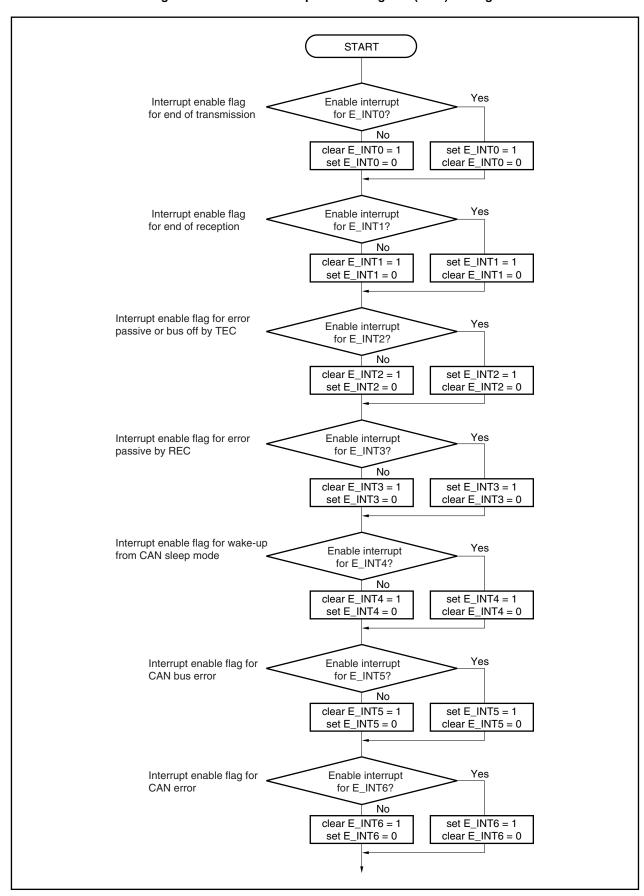

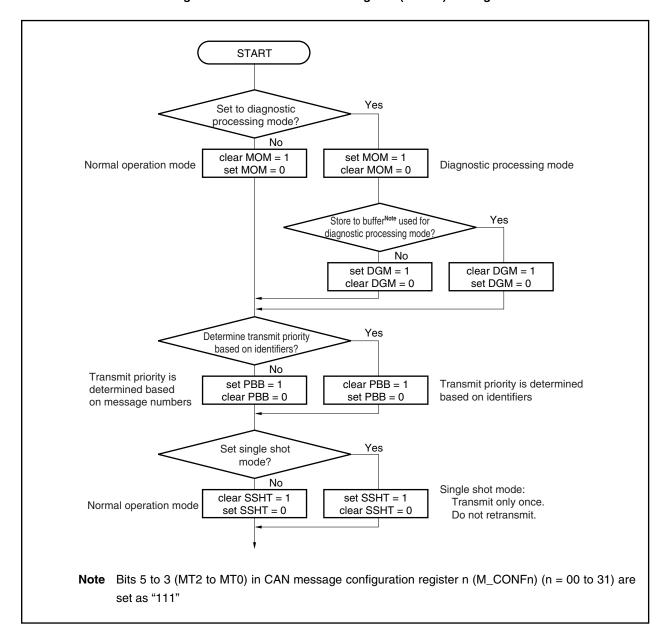

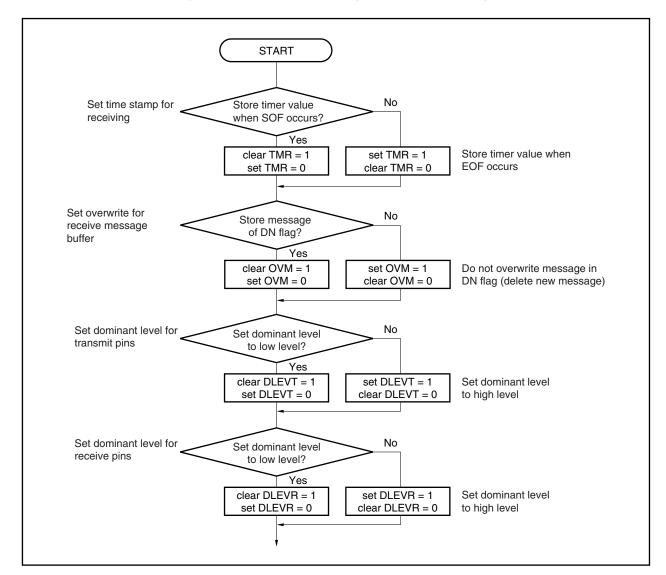

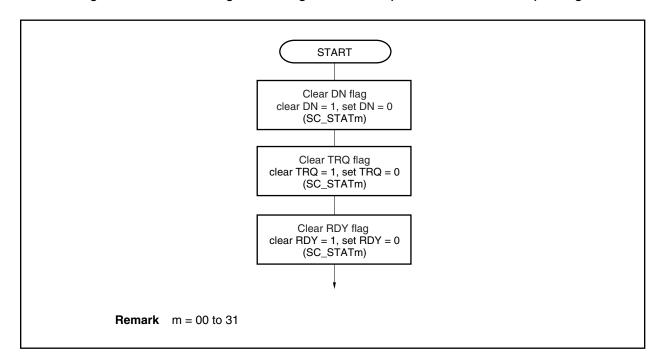

|         | 11.11.1 Initialization processing                                   | 598 |

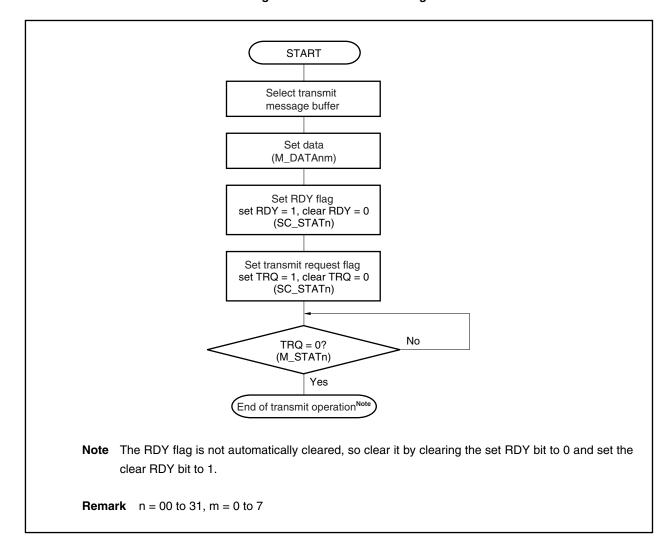

|         | 11.11.2 Transmit setting                                            | 611 |

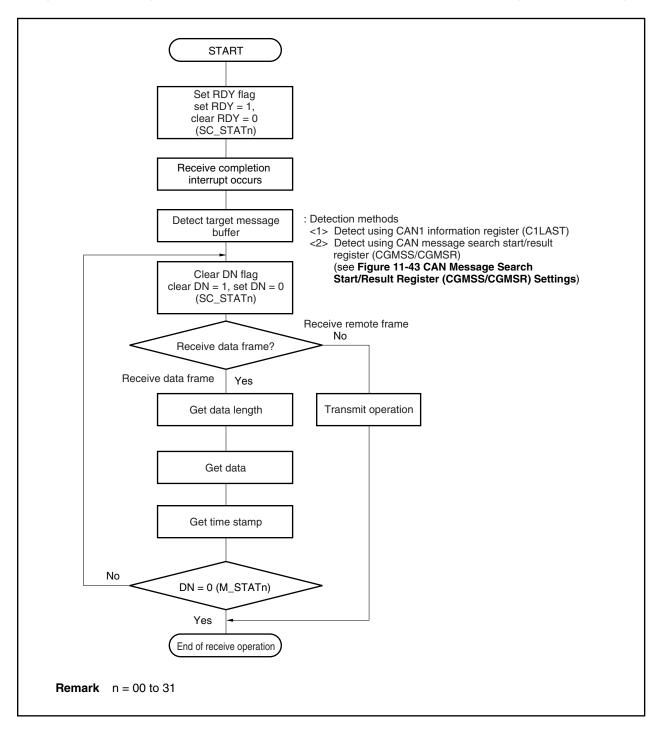

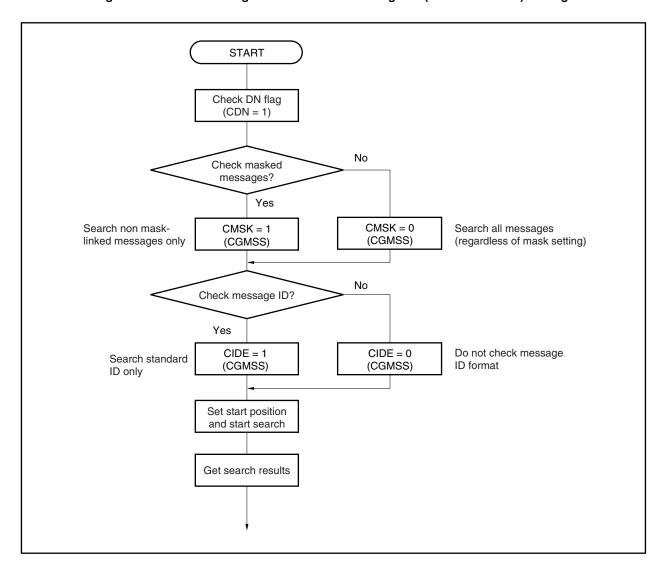

|         | 11.11.3 Receive setting                                             | 612 |

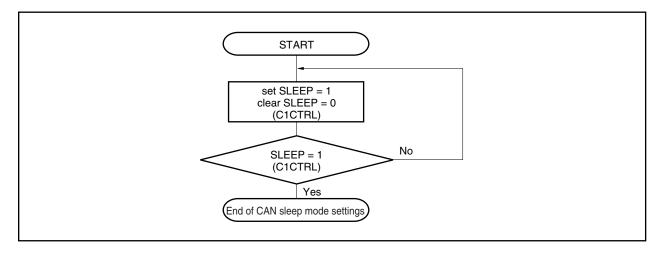

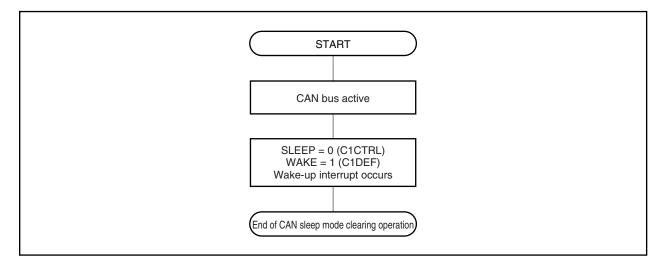

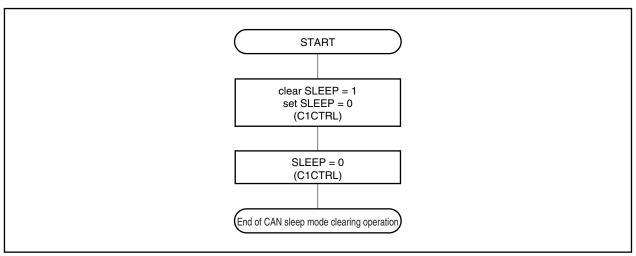

|         | 11.11.4 CAN sleep mode                                              | 614 |

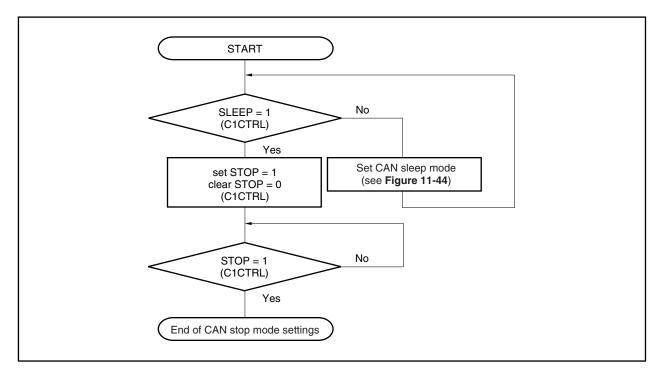

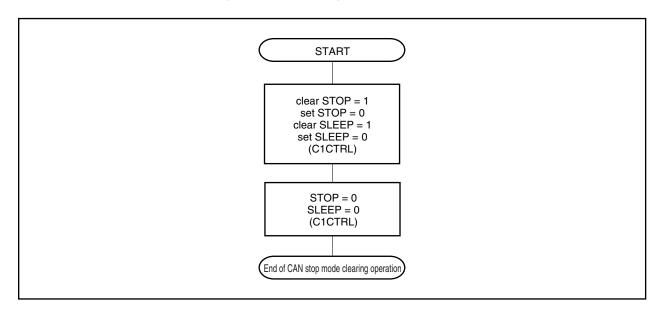

|         | 11.11.5 CAN stop mode                                               | 615 |

| 11.12   | 2 Rules for Correct Setting of Baud Rate                            | 617 |

| 11.13   | 3 Ensuring Data Consistency                                         | 621 |

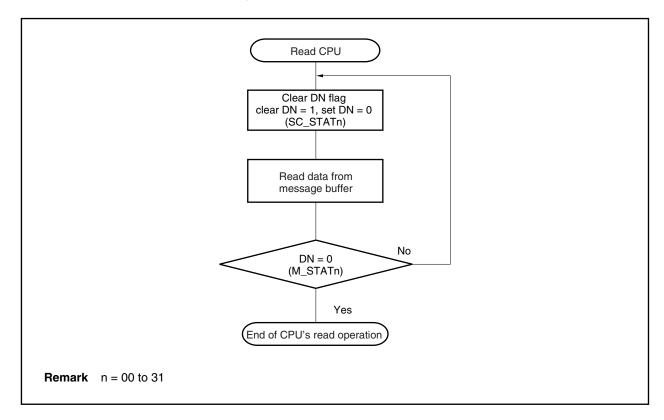

|         | 11.13.1 Sequential data read                                        | 621 |

|         | 11.13.2 Burst read mode                                             | 622 |

| 11.14   | 4 Interrupt Conditions                                              | 623 |

|         | 11.14.1 Interrupts that are generated for FCAN controller           | 623 |

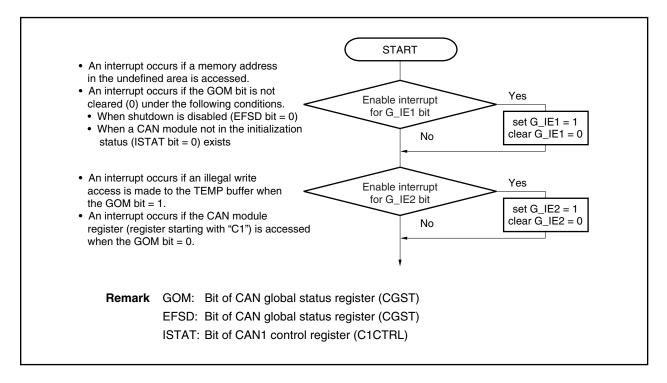

|         | 11.14.2 Interrupts that are generated for global CAN interface      | 623 |

| 11.15   | 5 How to Shut Down FCAN Controller                                  | 624 |

| 11.16   | 6 Cautions on Use                                                   | 625 |

|         |                                                                     |     |

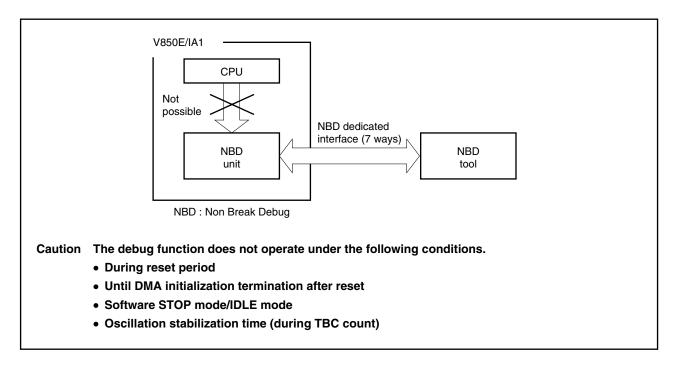

|         | ER 12 NBD FUNCTION ( $\mu$ PD70F3116)                               |     |

| 12.1    | Overview                                                            |     |

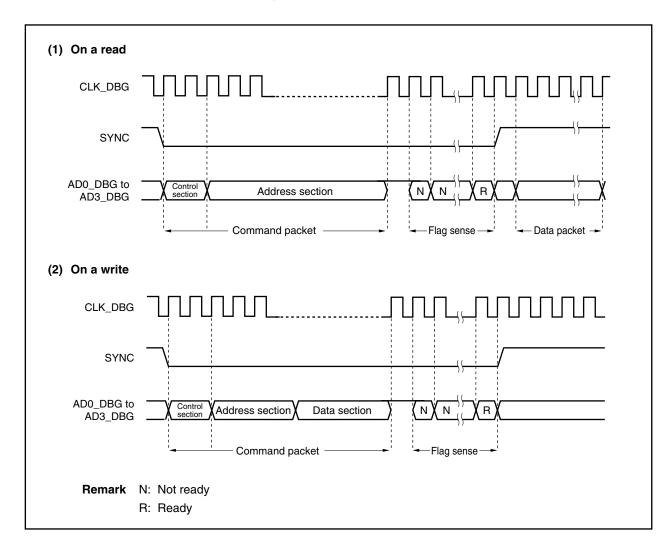

| 12.2    |                                                                     |     |

| 12.3    |                                                                     |     |

| 12.4    |                                                                     |     |

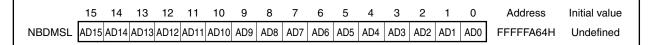

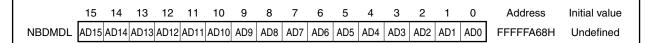

|         | 12.4.1 RAM monitoring, accessing NBD space                          |     |

|         | 12.4.2 Event detection function                                     |     |

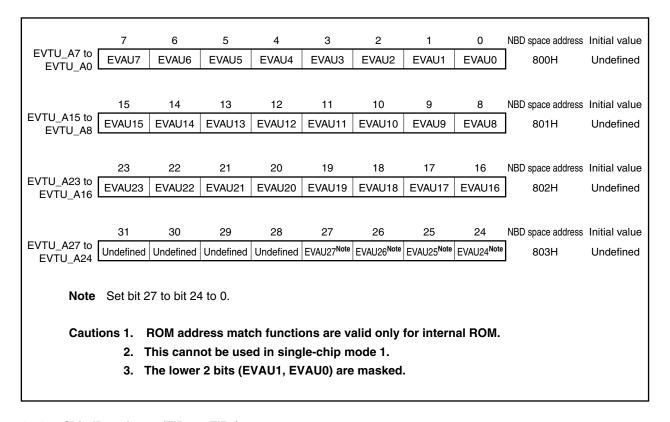

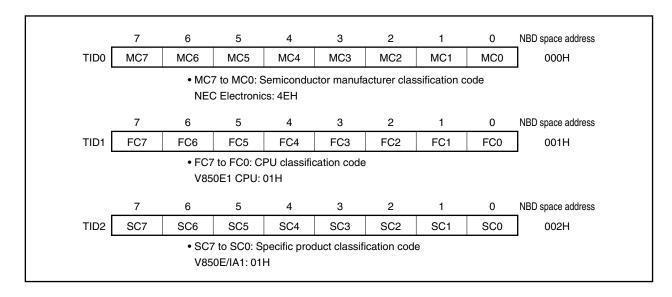

|         | 12.4.3 Chip ID registers (TID0 to TID2)                             |     |

| 12.5    | 3                                                                   |     |

| 12.6    |                                                                     |     |

|         | 12.6.1 General restrictions                                         |     |

|         | 12.6.2 Restrictions related to read or write of RAM by NBD          |     |

|         | 12.6.3 Restrictions related to NBD event trigger function           |     |

| 40.     | 12.6.4 How to detect termination of DMA initialization via NBD tool |     |

| 12.7    | Initialization Required for DMA (2 Channels)                        | 640 |

| CLIADTE | ED 12 A/D CONVERTED                                                 | 644 |

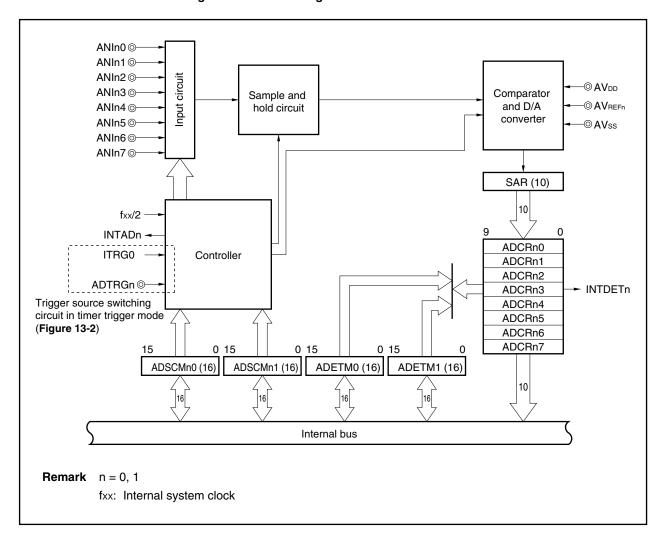

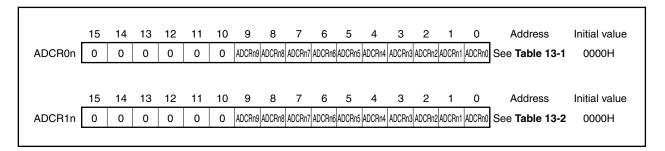

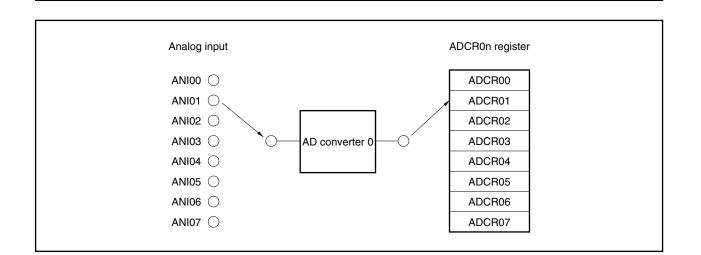

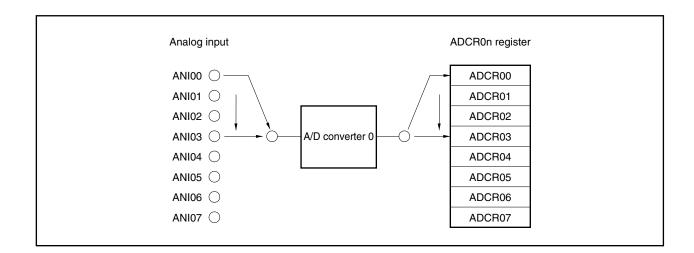

| 13.1    | ER 13 A/D CONVERTERFeatures                                         |     |

| 13.1    | Configuration                                                       |     |

| 13.2    | _                                                                   |     |

| 13.4    | Interrupt Requests                                                  |     |

| 13.4    |                                                                     |     |

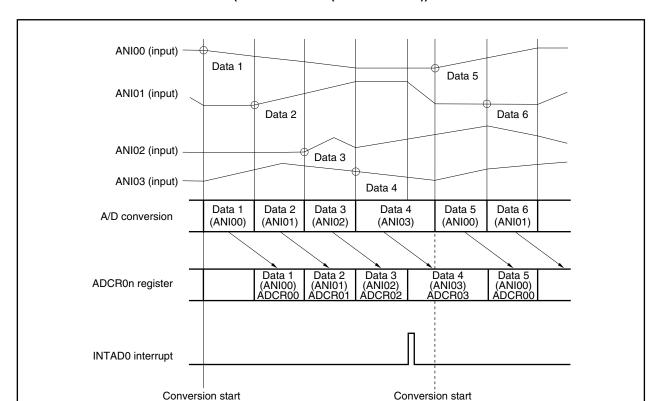

| 13.3    | 13.5.1 A/D converter basic operation                                |     |

|         | 13.5.2 Operation modes and trigger modes                            |     |

| 13.6    |                                                                     |     |

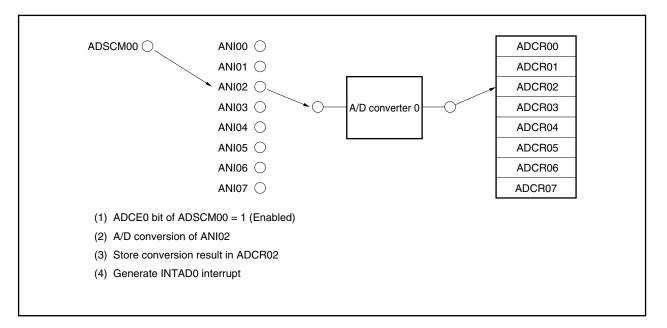

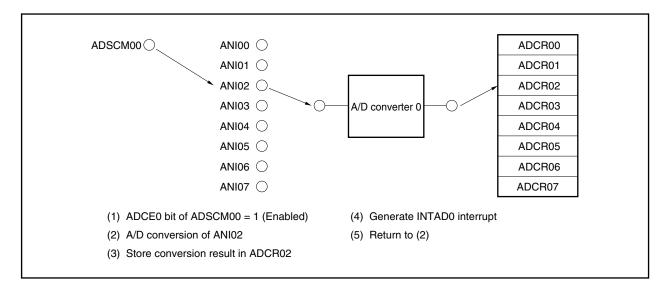

| 15.0    | 13.6.1 Operation in select mode                                     |     |

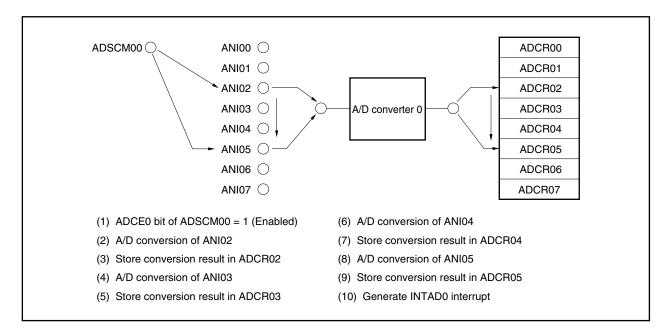

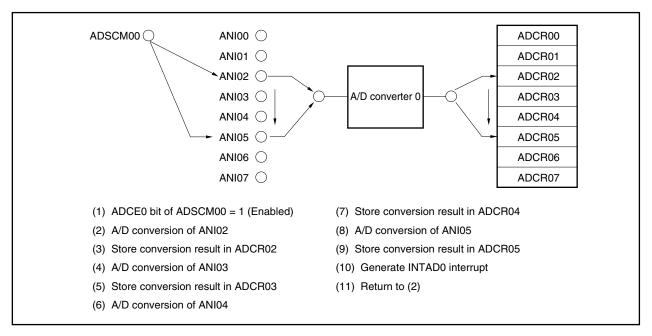

|         | 13.6.2 Operation in scan mode                                       |     |

| 13.7    | ·                                                                   |     |

|         | p                                                                   |     |

|        | 13.7.1   | Operation in select mode                                                                     | 664   |

|--------|----------|----------------------------------------------------------------------------------------------|-------|

|        | 13.7.2   | Operation in scan mode                                                                       | 665   |

| 13.8   | Operat   | ion in Timer Trigger Mode                                                                    | . 666 |

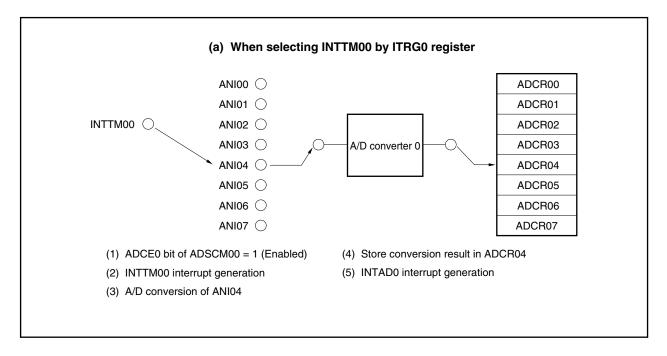

|        | 13.8.1   | Operation in select mode                                                                     | 666   |

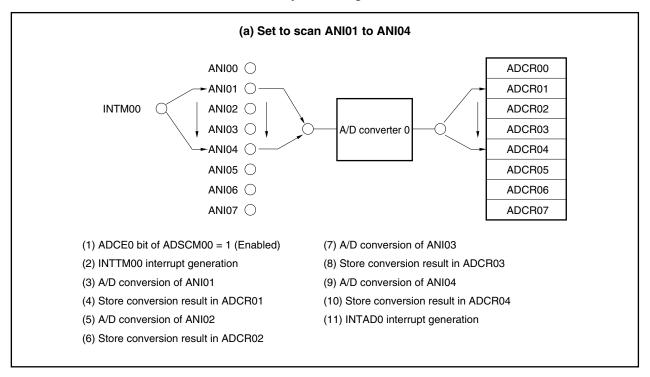

|        | 13.8.2   | Operation in scan mode                                                                       | 667   |

| 13.9   | Operat   | ion in External Trigger Mode                                                                 | . 668 |

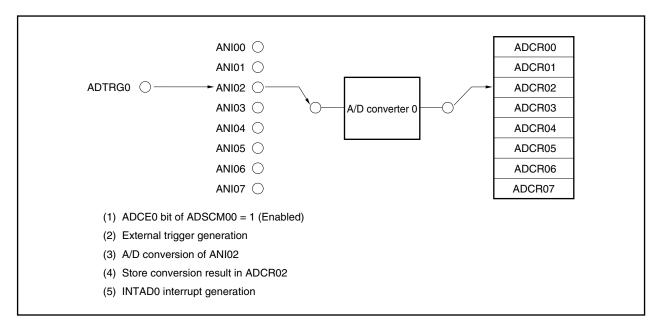

|        | 13.9.1   | Operation in select mode                                                                     | 668   |

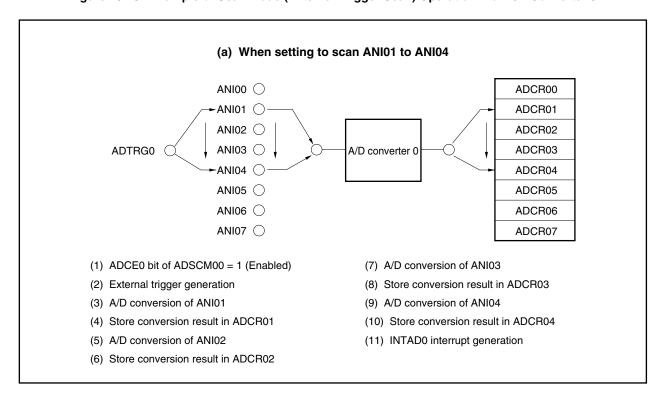

|        | 13.9.2   | Operation in scan mode                                                                       | 669   |

| 13.10  | ) Precau | itions on Operation                                                                          | . 670 |

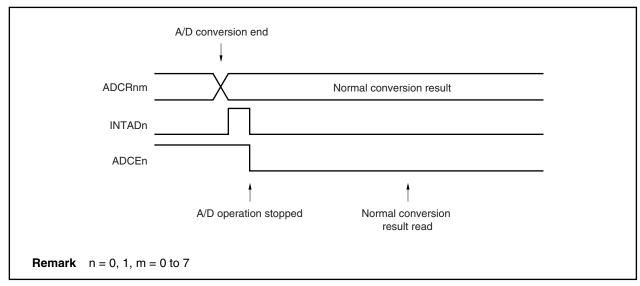

|        | 13.10.1  | Stopping A/D conversion operation                                                            | 670   |

|        | 13.10.2  | Trigger input during A/D conversion operation                                                | 670   |

|        | 13.10.3  | External or timer trigger interval                                                           | 670   |

|        | 13.10.4  | Operation in standby modes                                                                   | 670   |

|        | 13.10.5  | Compare match interrupt in timer trigger mode                                                | 671   |

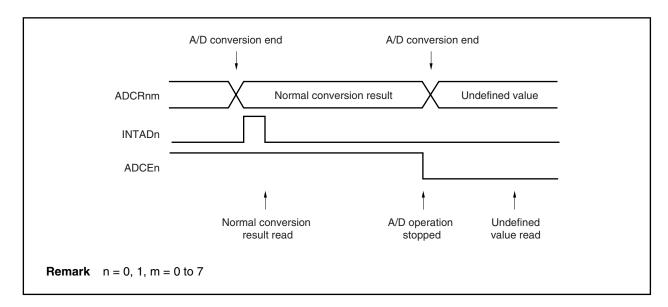

|        | 13.10.6  | Timing that makes the A/D conversion result undefined                                        | 671   |

|        | 13.10.7  | Restriction caused by contention between occurrence of a timer trigger and input of an       |       |

|        |          | external trigger                                                                             | 672   |

|        | 13.10.8  | Termination of A/D conversion when forcibly suspending scan mode (A/D trigger mode, A/D      |       |

|        |          | trigger polling mode, timer trigger mode, external trigger mode) or select mode (A/D trigger |       |

|        |          | polling mode)                                                                                | 673   |

|        | 13.10.9  | Variation of A/D conversion results                                                          | 673   |

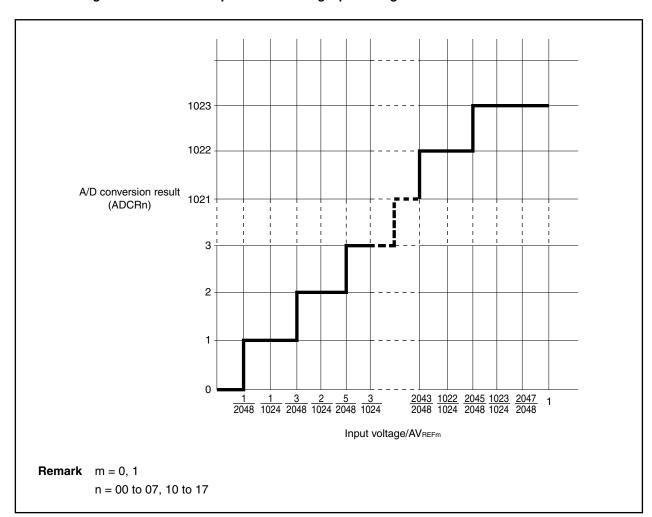

|        | 13.10.10 | A/D conversion result hysteresis characteristics                                             | 673   |

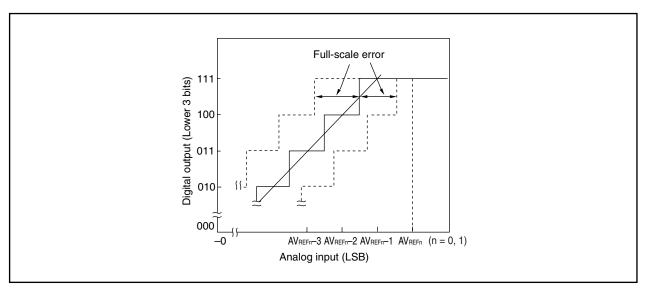

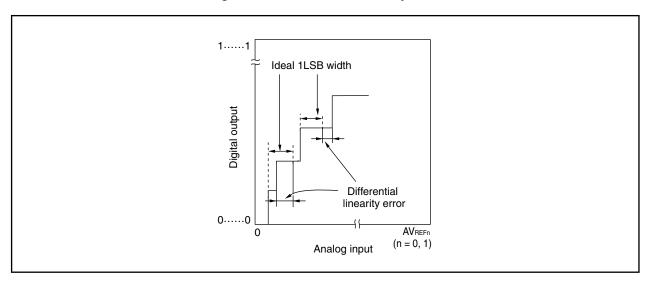

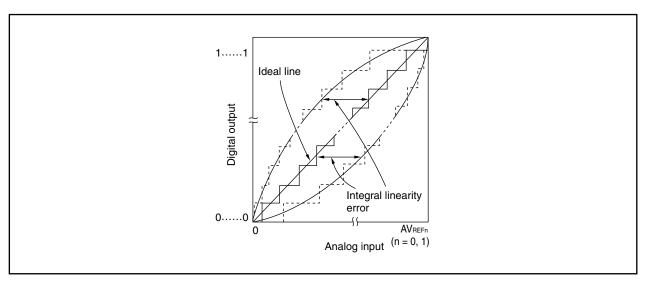

| 13.11  | How to   | Read A/D Converter Characteristics Table                                                     | . 674 |

|        |          |                                                                                              |       |

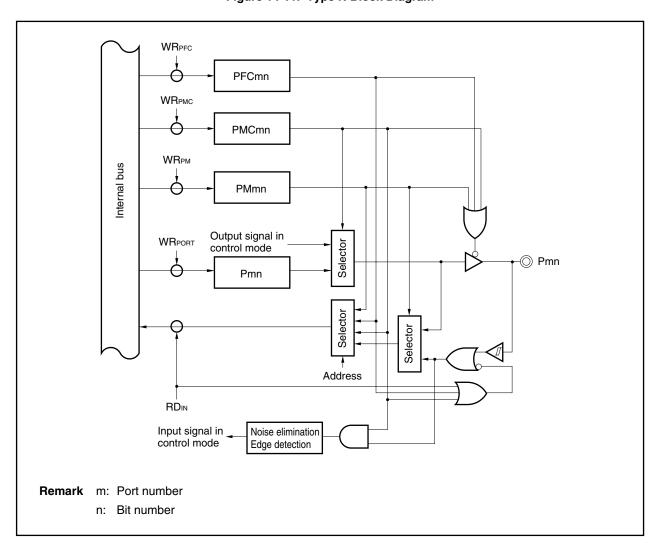

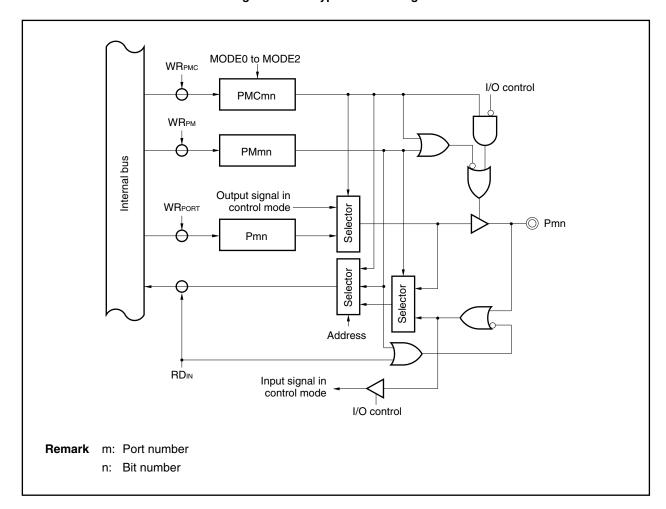

| CHAPTE |          | PORT FUNCTIONS                                                                               |       |

| 14.1   |          | es                                                                                           |       |

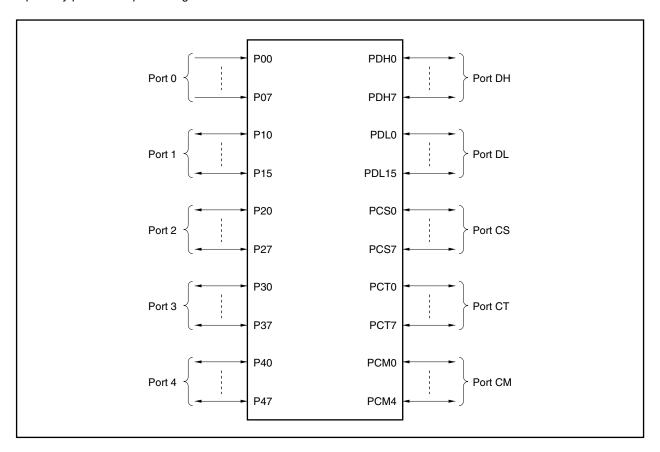

| 14.2   |          | Configuration of Ports                                                                       |       |

| 14.3   | Pin Fu   | nctions of Each Port                                                                         |       |

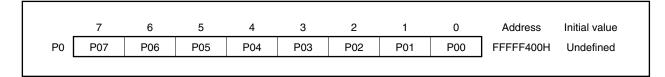

|        | 14.3.1   | Port 0                                                                                       |       |

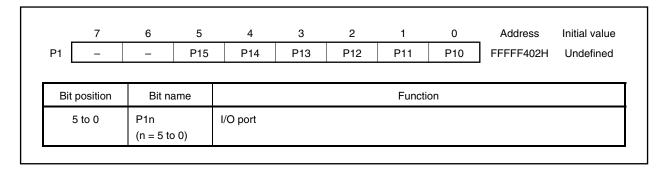

|        | 14.3.2   | Port 1                                                                                       |       |

|        | 14.3.3   | Port 2                                                                                       |       |

|        | 14.3.4   | Port 3                                                                                       |       |

|        | 14.3.5   | Port 4                                                                                       |       |

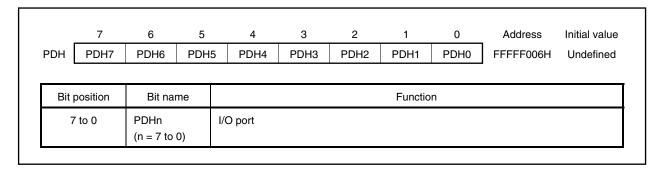

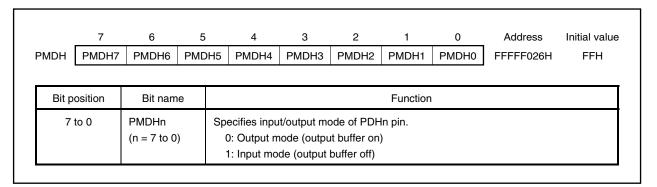

|        | 14.3.6   | Port DH                                                                                      |       |

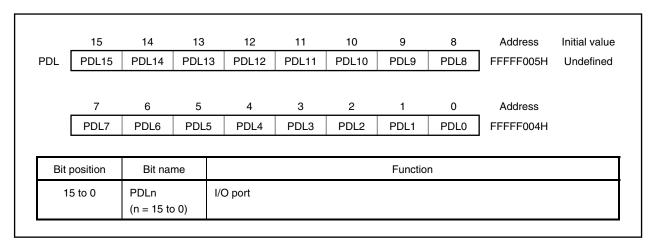

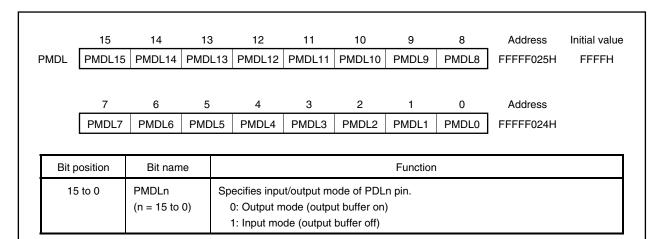

|        | 14.3.7   | Port DL                                                                                      |       |

|        | 14.3.8   | Port CS                                                                                      |       |

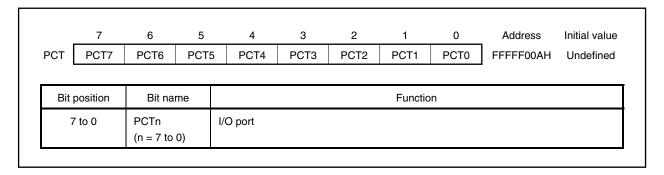

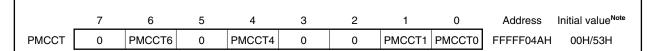

|        | 14.3.9   | Port CT                                                                                      |       |

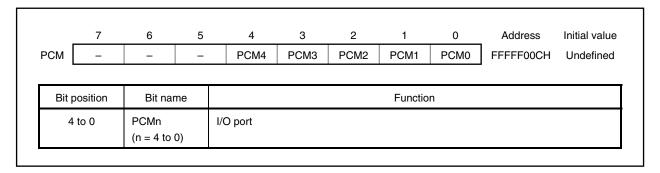

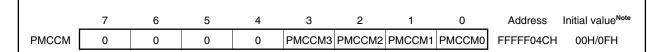

|        |          | Port CM                                                                                      |       |

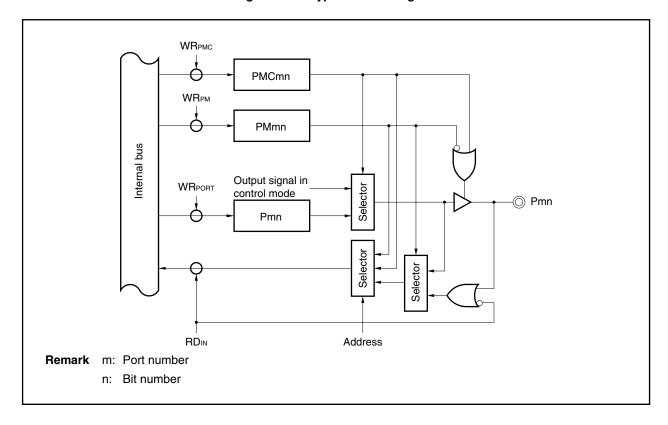

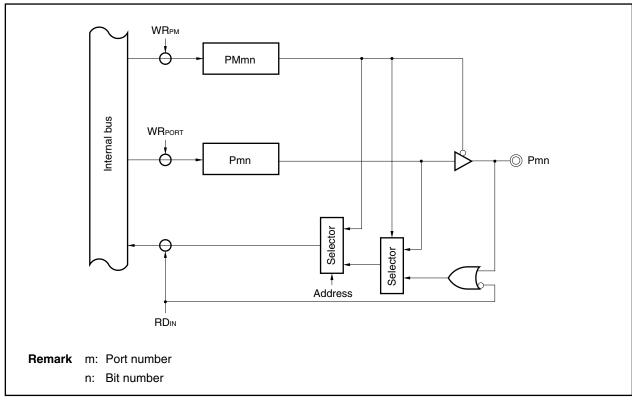

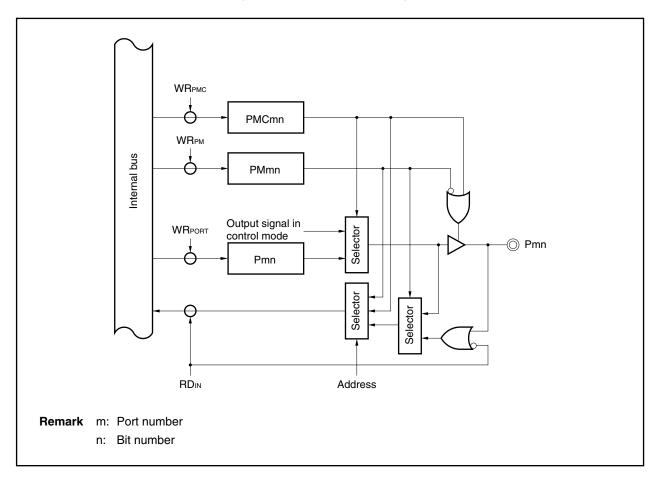

| 14.4   | Operat   | ion of Port Function                                                                         |       |

|        | 14.4.1   | Writing to I/O port                                                                          |       |

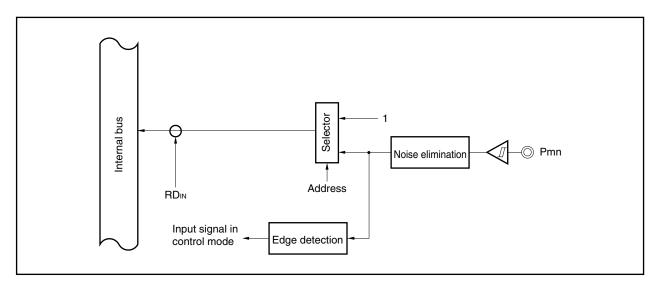

|        | 14.4.2   | Reading from I/O port                                                                        |       |

|        | 14.4.3   | Output status of alternate function in control mode                                          |       |

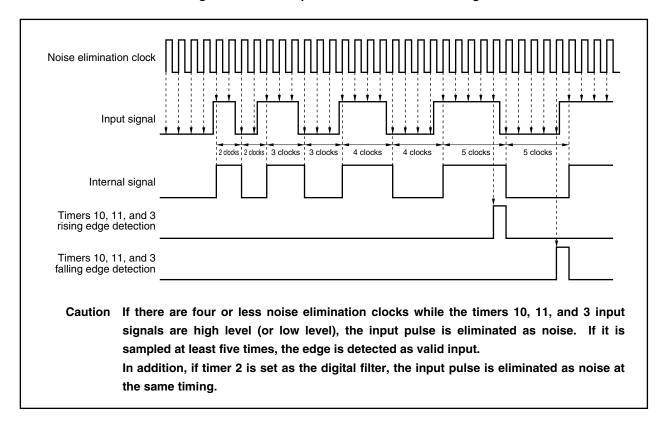

| 14.5   | Noise I  | Eliminator                                                                                   | . 715 |

|        | 14.5.1   | Interrupt pins                                                                               |       |

|        | 14.5.2   | Timer 10, timer 11, timer 3 input pins                                                       |       |

|        | 14.5.3   | Timer 2 input pins                                                                           | 720   |

|        |          |                                                                                              |       |

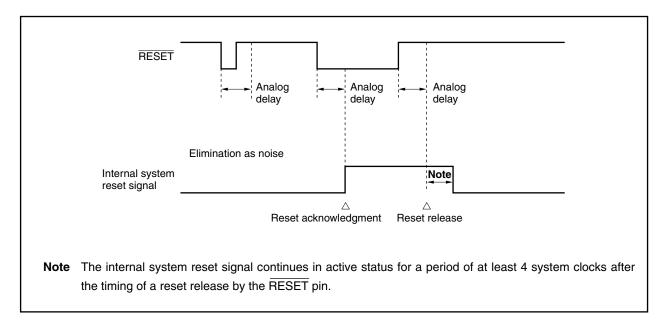

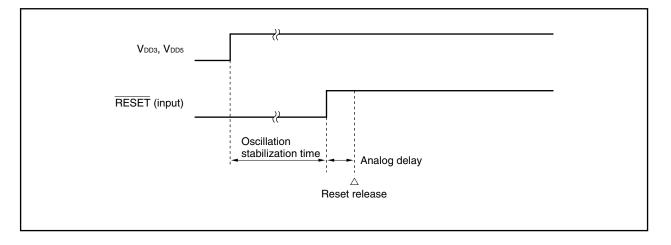

| CHAPTE | R 15 F   | RESET FUNCTION                                                                               | 723   |

| 15.1    | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 723 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 15.2    | Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 723 |

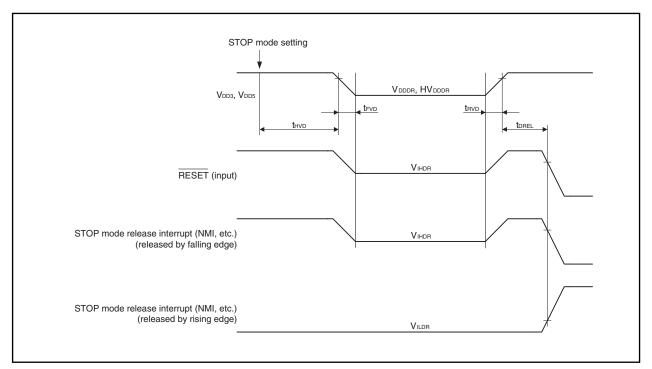

| 15.3    | Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 725 |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

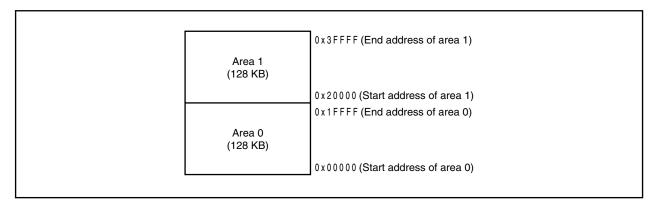

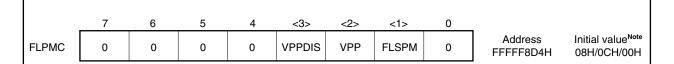

| CHAPTE  | R 16 FLASH MEMORY ( PD70F3116)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 731 |

| 16.1    | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 731 |

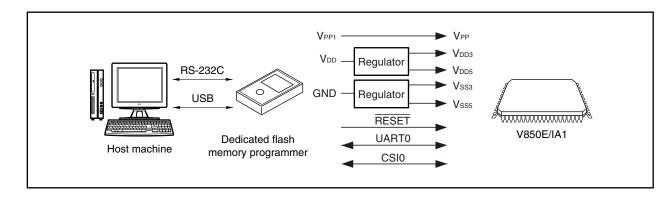

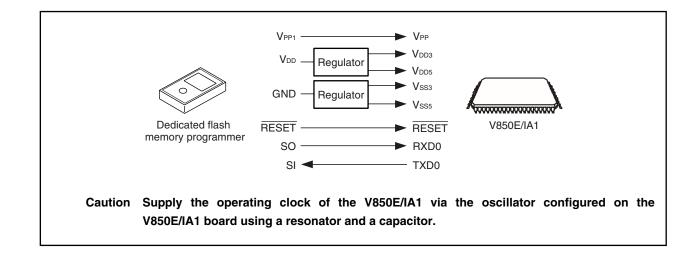

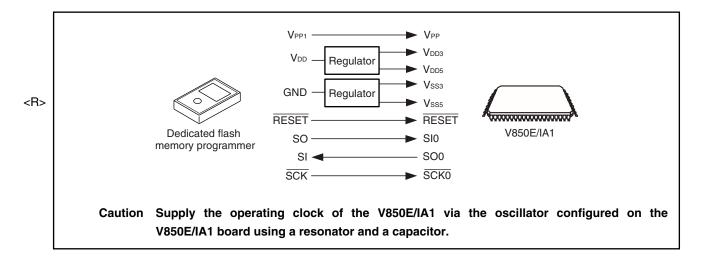

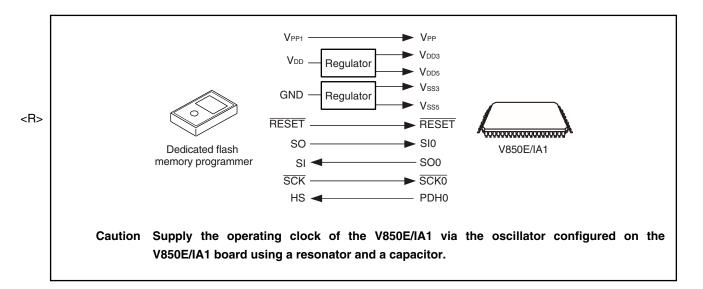

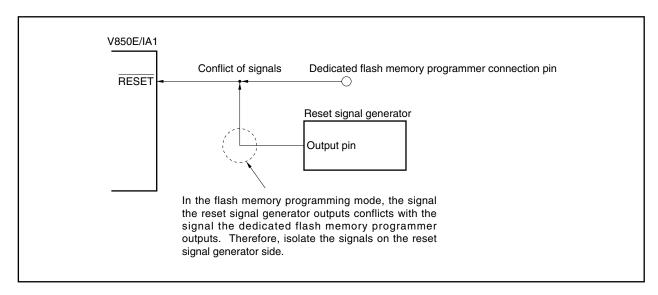

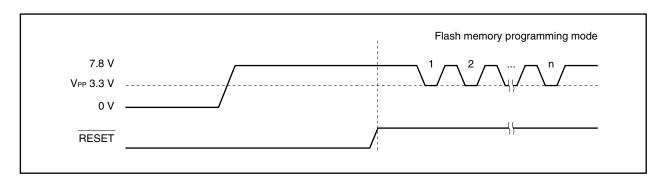

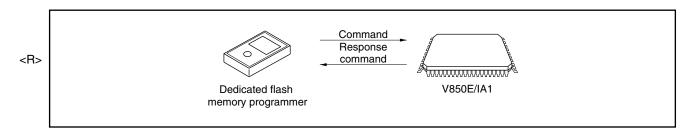

| 16.2    | Writing by Flash Memory Programmer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 731 |

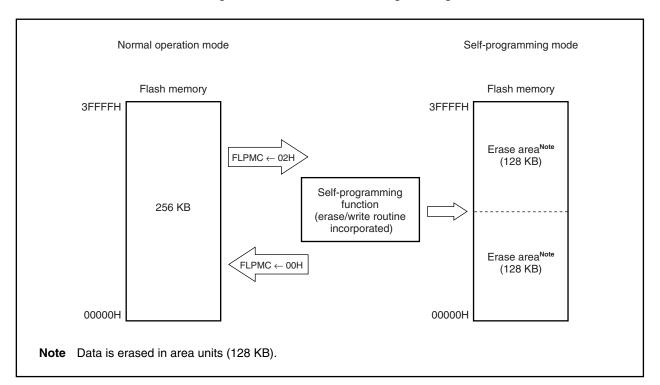

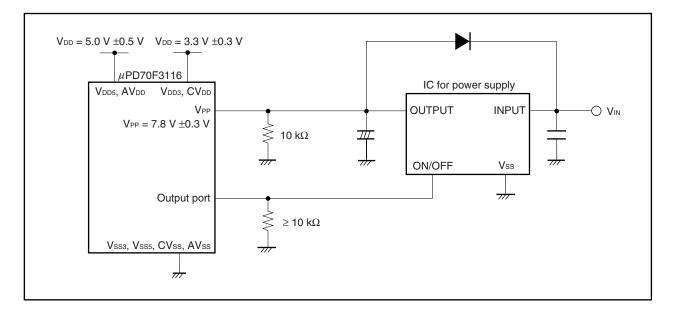

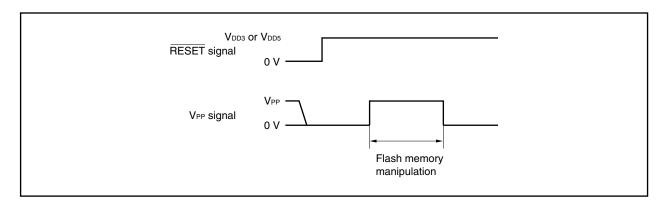

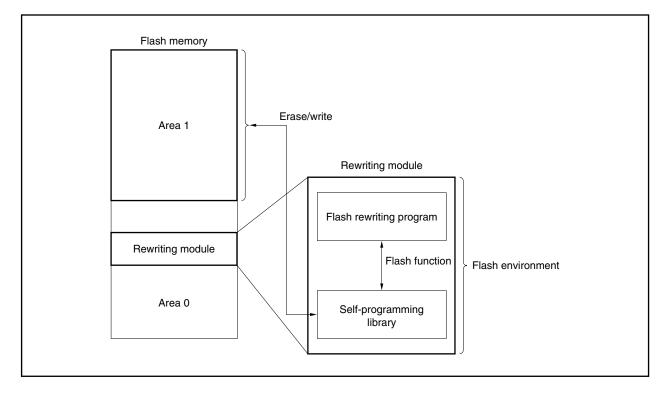

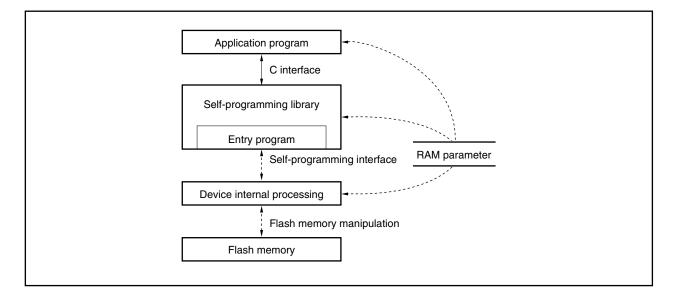

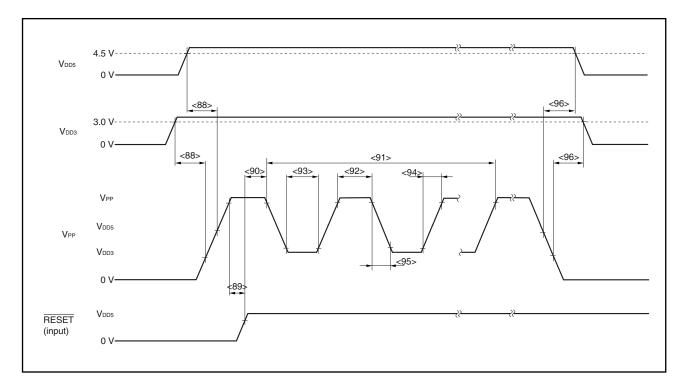

| 16.3    | Programming Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 733 |