3288.7

Data Sheet September 2000 File Number

# Digital Down Converter

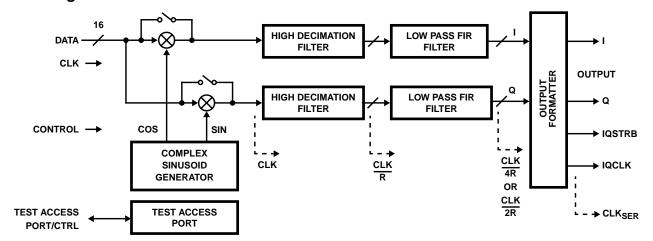

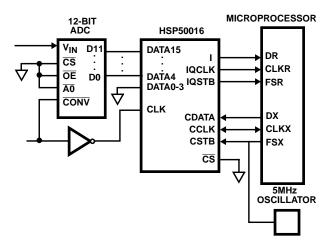

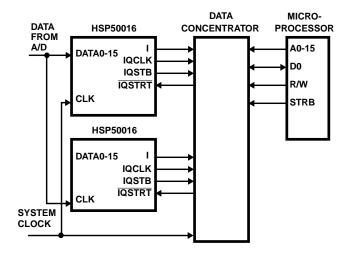

The Digital Down Converter (DDC) is a single chip synthesizer, quadrature mixer and lowpass filter. Its input data is a sampled data stream of up to 16 bits in width and up to a 75 MSPS data rate. The DDC performs down conversion, narrowband low pass filtering and decimation to produce a baseband signal.

The internal synthesizer can produce a variety of signal formats. They are: CW, frequency hopped, linear FM up chirp, and linear FM down chirp. The complex result of the modulation process is lowpass filtered and decimated with identical real filters in the in-phase (I) and quadrature (Q) processing chains.

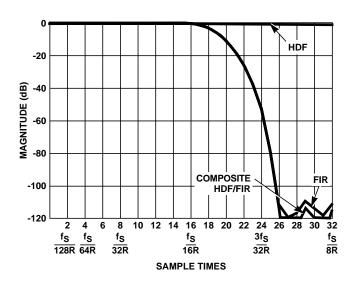

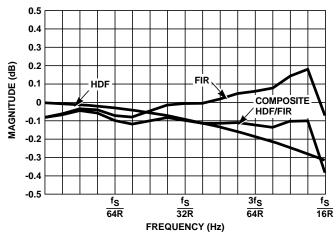

Lowpass filtering is accomplished via a High Decimation Filter (HDF) followed by a fixed Finite Impulse Response (FIR) filter. The combined response of the two stage filter results in a -3dB to -102dB shape factor of better than 1.5. The stopband attenuation is greater than 106dB. The composite passband ripple is less than 0.04dB. The synthesizer and mixer can be bypassed so that the chip operates as a single narrow band low pass filter.

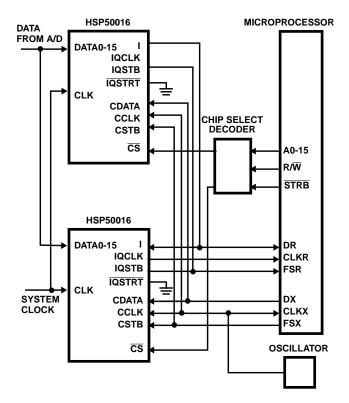

The chip receives forty bit serial commands as a control input. This interface is compatible with the serial I/O port available on most microprocessors.

The output data can be configured in fixed point or single precision floating point. The fixed point formats are 16, 24, 32, or 38-bit, two's complement, signed magnitude, or offset binary.

The circuit provides an IEEE 1149.1 Test Access Port.

#### **Features**

- 75 MSPS Input Data Rate

- 16-Bit Data Input; Offset Binary or 2's Complement Format

- Spurious Free Dynamic Range Through Modulator >102dB

- Frequency Selectivity: <0.006Hz

- · Identical Lowpass Filters for I and Q

- Passband Ripple: <0.04dB

- Stopband Attenuation: >104dB

- Filter -3dB to -102dB Shape Factor: <1.5</li>

- Decimation Factors from 32 to 131,072

- · IEEE 1149.1 Test Access Port

- HSP50016-EV Evaluation Board Available

# **Applications**

- · Cellular Base Stations

- Smart Antennas

- · Channelized Receivers

- Spectrum Analysis

- Related Products: HI5703, HI5746, HI5766 A/Ds

### Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>(°C) | PACKAGE    | PKG.<br>NO. |

|----------------|---------------------|------------|-------------|

| HSP50016JC-52  | 0 to 70             | 44 Ld PLCC | N44.65      |

| HSP50016JC-75  | 0 to 70             | 44 Ld PLCC | N44.65      |

# **Block Diagram**

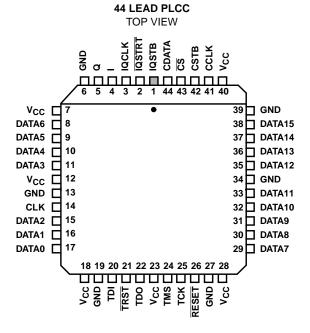

## **Pinout**

# Pin Description

| NAME     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Vcc      | -    | +5V Power.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| GND      | -    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| DATA0-15 | I    | Input Data Bus. Selectable between two's complement and offset binary. DATA0 is the LSB.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| CLK      | I    | Clock for input data bus. f <sub>S</sub> is the frequency of CLK, which is also the input sample rate.                                                                                                                                                                                                                                                                                                                       |  |  |  |

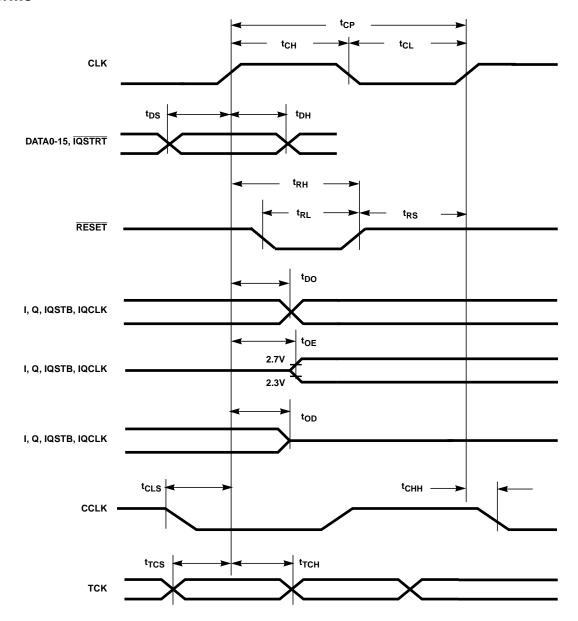

| RESET    | I    | RESET initializes the internal state of the DDC. During RESET, all internal processing stops. RESET facilitates the synchronization of multiple chips for Auto Three-State operation. If the Force bits in Control Word 7 are inactive and the IEEE Test Access Port is in an Idle state, RESET causes the IQCLK, IQSTB, I and Q outputs to go to a high impedance state.                                                    |  |  |  |

|          |      | All Control Registers are updated from their respective Control Buffer Registers on the third rising edge of CLK after the deassertion of RESET. If RESET is deasserted $t_{RS}$ nanoseconds prior to the rising edge of CLK, the internal reset will deassert synchronously. If $t_{RS}$ is violated, then the circuit contains a synchronizer which will cause reset to be deasserted internally one or more clocks later. |  |  |  |

|          |      | An initial reset is required to guarantee proper operation of the DDC. Active low.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ı        | 0    | The I output has three modes: I data; I data followed by Q data; real data.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Q        | 0    | The Q output has two modes: Q data and the carry out of the Phase Adder.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| IQCLK    | 0    | IQ Clock: Bit or word clock for the I and Q outputs.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| IQSTB    | 0    | IQ Strobe: Beginning or end of word indicator for I and Q.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IQSTRT   | I    | IQ Start: Initiates output data sequence. Active low.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

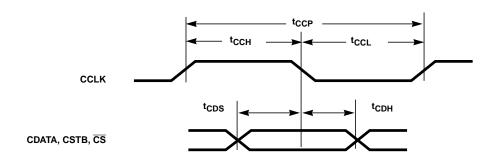

| CDATA    | I    | Control Data: Port for control data input.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| CCLK     | I    | Control Data Clock: Control data input bit clock.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CSTB     | I    | Control Data Strobe: Beginning of word indicator for control data.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| CS       | I    | Chip Select: Enables control data loading of DDC. Active low.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

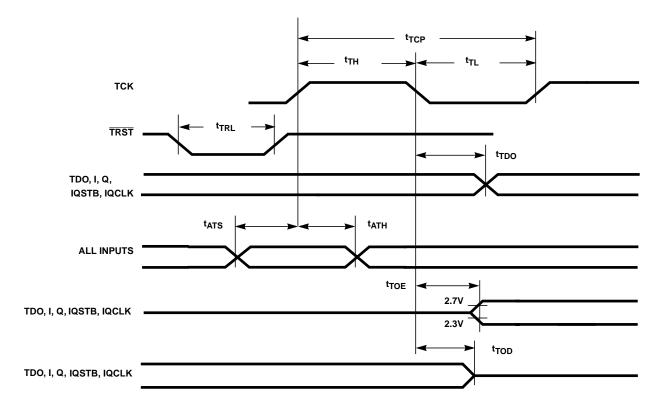

| TCK      | I    | Test Clock: Bit Clock for IEEE 1149.1 Data. This signal should be either tied low or pulled high when t TAP is not used.                                                                                                                                                                                                                                                                                                     |  |  |  |

| TMS      | I    | Test Port Mode Select: This signal should be either left unconnected or pulled high when the TAP is rused.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| TDI      | I    | Test Data Input for IEEE Test Port: This signal should be either left unconnected or pulled high when the TAP is not used.                                                                                                                                                                                                                                                                                                   |  |  |  |

| TDO      | 0    | Test Data Output for IEEE Test Port: This output will be in the high impedance state when the TAP is not used.                                                                                                                                                                                                                                                                                                               |  |  |  |

| TRST     | I    | Test Port Reset. Active Low. This signal should be tied low when the TAP is not used.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

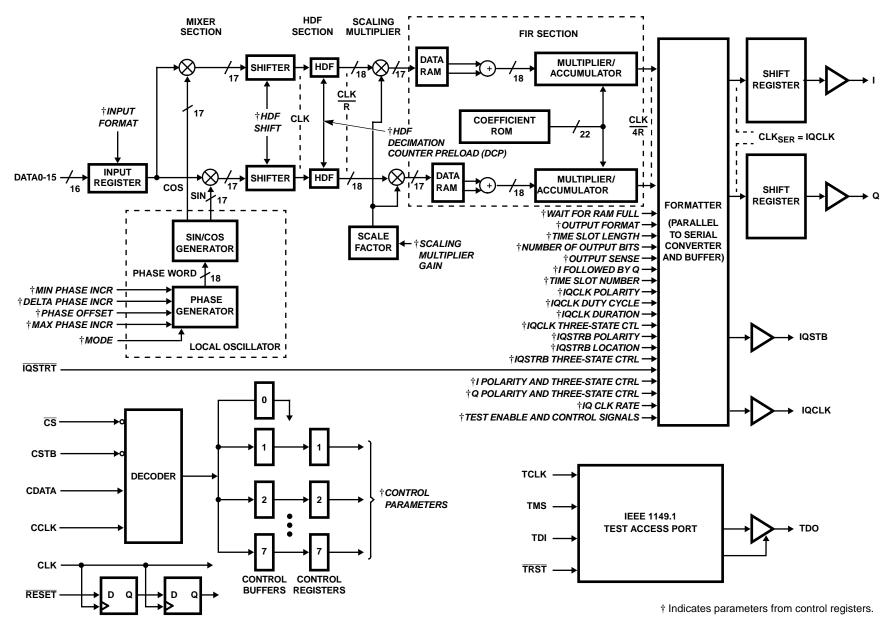

# **DDC Functional Block Diagram**

FIGURE 1. FUNCTIONAL BLOCK DIAGRAM

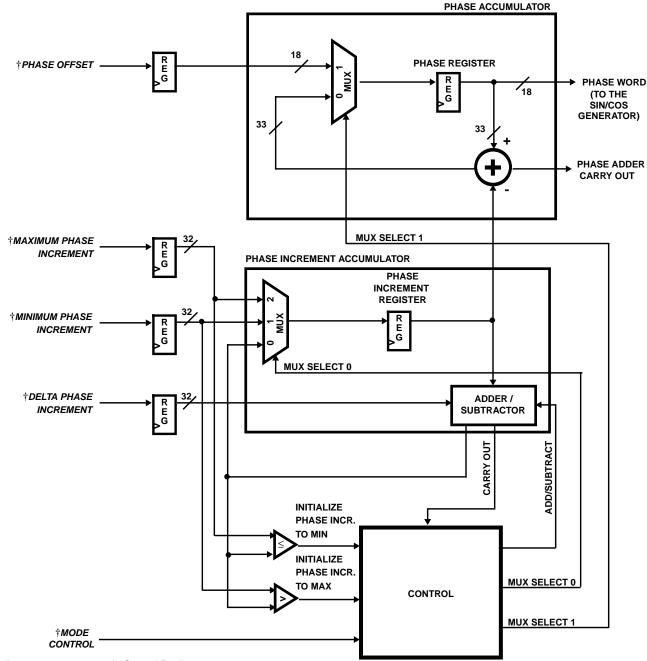

## Phase Generator Block Diagram

† Indicates parameters set in Control Registers.

FIGURE 2. PHASE GENERATOR BLOCK DIAGRAM

# Functional Description

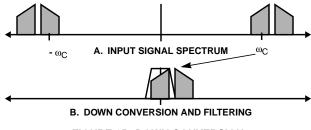

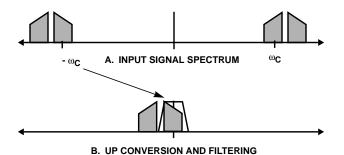

The primary function of the DDC is to extract a narrow frequency band of interest from a wideband input, convert that band to baseband and output it in either a quadrature or real form. This narrow band extraction is accomplished by down converting and centering the band of interest at DC. The conversion is done by multiplying the input data with a quadrature sinusoid. A quadrature lowpass filter is applied to

the multiplier outputs. Identical real lowpass filters are provided in the in-phase (I) and quadrature phase (Q) processing branches. Each filtering chain consists of a cascaded HDF and FIR filter, which extracts the band of interest. During filtering, the signal is decimated by a rate which is proportional to the output bandwidth. The bandwidth of the resulting signal is the double sided passband width of the lowpass filters. An Output Formatter manipulates the filter output to provide the data in a variety of serial data formats.

#### Local Oscillator

Signal data clocked into the DATA0-15 input of the DDC is multiplied by a quadrature sinusoid in the Mixer Section (see Figure 1). The data input to the DDC is a 16-bit real data stream which is sampled on the rising edges of CLK. It can be in two's complement or offset binary format.

The input data is passed to a mixer, which is composed of two real multipliers. One of these multiplies the input data samples by the in-phase (cosine) component of the quadrature sinusoid, and the other multiplies the input data samples by the quadrature (sine) component. The in-phase and quadrature data paths are designated I and Q respectively. The sine and cosine are generated in the local oscillator as shown in Figure 1.

The local oscillator is programmed to produce a quadrature sinusoid with programmable frequency and phase. The frequency can be constant (Continuous Wave - CW), linearly increasing (up chirp), linearly decreasing (down chirp), or linear up/down chirp. The initial phase of the waveform is set by the phase offset.

The phase, frequency and chirp limits of the quadrature sinusoid are controlled by the Phase Generator (Figure 2). The output of the Phase Generator is an 18-bit phase word that represents the current phase angle of the complex sinusoid. The Phase Generator automatically increments the phase angle by a preprogrammed amount on every rising edge of CLK. Stepping the output phase from 0 through full scale ( $2^{18}$  - 1) steps the phase angle of the quadrature sinusoid from 0 to (-2+2<sup>-17</sup>) $\pi$  radians. *NOTE: The phase is stepped in a clockwise (decreasing) direction to support down conversion.* The frequency of the complex sinusoid is determined by the number of clocks needed for the phase to step though its full range of  $2\pi$  radians. The required phase increment for a given local oscillator frequency is calculated by:

Phase Increment = INT

$$[(f_C/f_S) 2^{33}]H$$

$f_C = (Phase Incr) f_S 2^{-33}; 0 < f_C < f_S/2$  (EQ. 1)

where:

f<sub>C</sub> is the desired local oscillator frequency

fs is the input sampling frequency

Phase Increment is the Control Word Value (in Hex)

There are five parameters which control the Phase Generator: Phase offset, minimum phase increment, maximum phase increment, delta phase increment and Mode Control. These values are programmed via Control Words 2, 3, and 4. Mode Control is used to select the function of the other parameters.

The phase offset is the initial setting of the phase word going to the SIN/COS Generator. Subsequent phases of the sinusoid are calculated relative to this offset. The minimum phase increment has two mode dependent functions: when the SIN/COS Generator is forming a CW waveform, the

minimum phase increment is the phase step taken on every clock. When the SIN/COS Generator is producing a chirped sinusoid, the minimum phase increment is the smallest phase step taken. Maximum phase increment is only used during Chirped Modes; it is the largest allowable phase increment. During Chirp Modes, the delta phase increment is the difference between successive phase increments.

The four phase parameters are stored in their respective registers in the Phase Generator. The Phase Register stores the current phase angle. On the first clock following the deassertion of RESET, the 18 MSBs of the Phase Register are loaded from the Phase Offset Register. On every rising edge of CLK thereafter, the output of the Phase Increment Register is subtracted from the 32 LSBs of the current phase. The 33-bit difference is stored back in the Phase Register on the next CLK. The 18 most significant bits of the Phase Register form the phase word, which is the input to the SIN/COS Generator.

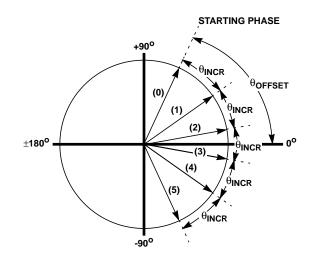

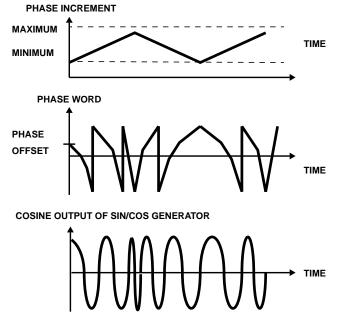

Figure 3 gives a graphic representation of the phase parameters for the CW case. To understand their interrelationships, the phase should be visualized as the angle of a rotating vector. When the local oscillator in the DDC is programmed to generate a CW waveform, the multiplexers are configured so that the Minimum Phase Increment is stored in the Phase Increment Register; this value is subtracted from the output of the Phase Register on every CLK and the difference becomes the new Phase Register value. The Delta Phase Increment and Maximum Phase Increment are ignored when generating a CW.

FIGURE 3. PHASE WORD PARAMETERS FOR CW CASE

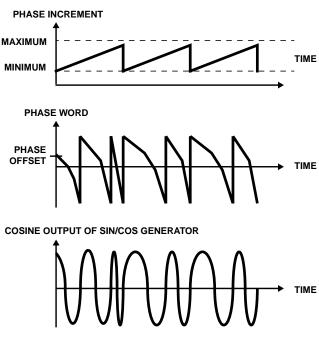

In Up Chirp Mode the local oscillator generates a signal with a linearly increasing frequency (Figure 4A). The Phase Increment Register is initially loaded with the minimum Phase Increment value; on every clock, the contents of the Phase Increment Register is subtracted from the current output of the Phase Register. Simultaneously, the Delta

Phase Increment Register is added to the 24 LSBs of the output of the Phase Increment Register. On the next CLK, that sum is stored back in the Phase Increment Register, the new phase is stored in the Phase Register and the process is repeated. The phase increment is allowed to grow until the next phase increment would equal or exceed the maximum phase increment value. When this happens, the Phase Increment Register is reset to the minimum phase increment and the cycle starts over again.

NOTE: The phase increment is never equal to the maximum phase increment, since the Phase Increment Register is reloaded if the next phase increment value would be greater than the maximum phase increment. From the time the Phase Generator starts at the minimum phase increment until it reaches the maximum phase increment, the phase word on clock n is given by:

Phase Offset -[Minimum Phase Increment + n (Delta Phase Increment)] (EQ. 2)

An example of the outputs of the Phase Increment Register, Phase Register, and the I output of the SIN/COS Generator are shown in Figure 4B.

STARTING PHASE +90°  $\theta_{INCR}$  $\theta_{\text{OFFSET}}$ (0)  $\theta_{INCR} + 2\theta_{\Delta}$  $\dot{\theta}_{INCR} + \theta_{\Delta}$ ±180° HINCR.  $\theta_{INCR}$  + 2 $\theta_{\Delta}$ (5) $\theta$ INCR  $\theta_{\mathsf{INCR}}$  + 3 $\theta_{\Delta}$  $\theta_{INCR} + 4\theta_{\Delta}$ -90°  $\theta_{INCR} + 5\theta_{\Delta} > \theta_{MAX}$  INCR THEN START NEW RAMP

FIGURE 4A. PHASE WORD DURING UP CHIRP

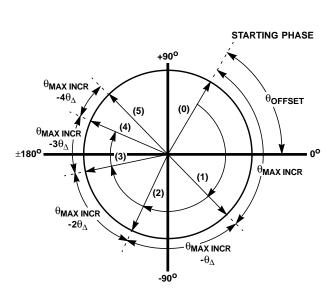

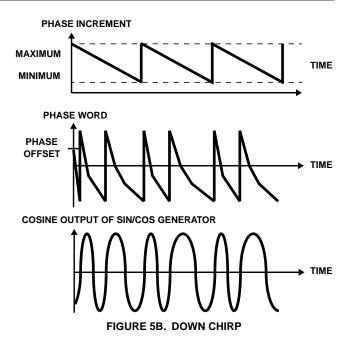

In Down Chirp Mode the local oscillator generates a signal with a linearly decreasing frequency (Figure 5A). The maximum phase increment is loaded into the Phase Increment Register and the phase offset value goes into the Phase Register. The delta phase increment is subtracted from the 24 LSBs of the phase increment to form a new phase increment at each clock. The phase increment is allowed to diminish until it reaches the minimum phase increment value, then it is reset to the maximum phase increment value and the cycle is repeated. Note that the value of the phase increment can be equal to, but never less than the minimum phase increment, since the Phase Increment Register is reloaded if the next phase increment value would be less than the minimum phase increment. This feature protects the DDC from exceeding the Nyquist frequency. In this case, from the time the Phase Generator starts at the maximum phase increment until it reaches the minimum phase increment, the phase word on clock n is given by:

Phase Offset -[Minimum Phase Increment (EQ. 3)

- n (Delta Phase Increment)]

See Figure 5B for a graphical representation of this process.

FIGURE 5A. PHASE WORD DURING DOWN CHIRP

FIGURE 6. UP/DOWN CHIRP

In Up/down Chirp Mode, the phase accumulator is set to the phase offset value and the minimum phase increment is loaded into the Phase Increment Register. The delta phase increment is added to the 24 LSBs of the Phase Increment Register to form a new phase increment at each clock. The phase increment is allowed to grow until it nears the maximum phase increment value (as defined in the up chirp description). The delta phase increment value is then subtracted from the least significant bits of the Phase Increment Register to form a new phase increment at each clock. The phase increment is allowed to diminish until it

reaches the minimum phase increment value (as defined in the down chirp description). The Phase Increment Register is then reloaded with the minimum phase increment, and the up/down cycle begins again. See Figure 6 for a graphical representation of this process.

The minimum and maximum phase increments have allowable values from 0 to 2<sup>32</sup>-1. This corresponds to the phase increment:

$$0 < Phase \ Increment < \pi (1-2^{-32}) \ radians \ \eqno(EQ.\ 4)$$

The Delta Phase Increment parameter can take on values from 0 to  $2^{24}$  - 1 which corresponds to the Delta Phase Increment:

$$0 < Delta Phase Increment < \pi(2^{-8} - 2^{-32})$$

radians (EQ. 5)

The output of the phase accumulator forms the input to the SIN/COS Generator which in turn produces a quadrature vector which rotates clockwise: the outputs are  $cos(\omega n)$  and  $-sin(\omega n)$ . The outputs of the SIN/COS Generator are two's complement values which are scaled to prevent overflow in subsequent operations in the DDC under normal operation. The scale factor has a negligible effect on the end to end DDC gain.

The frequency resolution of the DDC = (frequency of CLK)/ (Number of Phase Register bits). At the maximum clock rate, this results in a frequency selectivity of  $75MHz/2^{33} = 0.009Hz$ . The 18-bit phase word yields a phase noise figure of greater than 102dB.

#### Mixer

The Mixer performs quadrature modulation by multiplying the output of the SIN/COS Generator by the input data. The outputs of the I and Q multipliers are symmetrically rounded to 17 bits to preserve the 102dB spurious free dynamic range (SFDR). The result of the quadrature modulation process is passed to the High Decimating Filter (HDF) Section.

#### **High Decimation Filter**

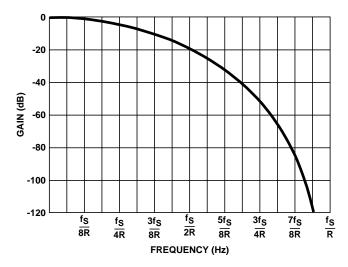

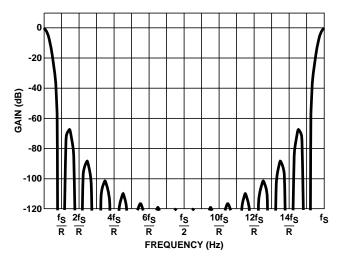

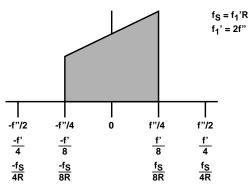

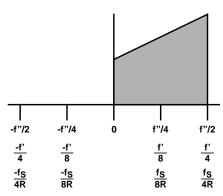

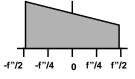

The High Decimation Filter (HDF) Section is comprised of two real HDF filters, one processing the I data branch and one processing the Q data branch. Each branch has the lowpass response shown in Figure 7. The normalized HDF frequency impulse response is given by the equation:

$$H(f) = \left[ \frac{Sin(\pi F_S)}{Sin(\pi F_S/R)} \right]^5 \left[ \frac{1}{R} \right]^5$$

(EQ. 6)

where  $F_S$  is the input sampling rate; R is the decimation (rate change) factor.

Figure 7A shows this equation plotted from DC to the first null, while Figure 7B shows the equation plotted from DC response to f<sub>S</sub>.

#### NOTE: The HDF is a true FIR filter; i.e., the phase is linear.

The data path through the HDF was designed to ensure a true 16-bit noise floor (approximately 98dB) at the output of the DDC. The structure of the HDF filter used in the DDC is a five stage decimation filter. The width of each successive stage decreases such that the LSBs are lost due to truncation [1]. As a result, the data must be processed in the MSBs of the filter so that the noise due to truncation is below the required noise floor. Thus, the input data of the HDF must be shifted so that its output data fills the HDF output word. The shift is a function of the desired HDF decimation rate R and the number of HDF filter stages (which is fixed at 5). The shift is performed by the Data Shifter, which positions

the input data to the HDF for the maximum dynamic range while avoiding overflow errors. The shift factor is programmed into the Shift field of Control Word 4. The value in this field is calculated by the equation:

Shift =

$$75 - \text{Ceiling}(5 \log_2(R))$$

(EQ. 7)

where R is the HDF decimation factor and Ceiling(X) denotes the ceiling function of X; i.e., the result is X if X is an integer, otherwise the result is the next higher integer.

During RESET, the HDF is initialized and will not output any information until it is filled with new data.

NOTE: The output rate of the HDF is CLK divided by the HDF decimation factor (CLK/R). The HDF decimation counter preload (DCP) is programmed in Control Word 5, bits 21-35 and has the value: DCP = R -I, where R is the HDF decimation factor.

FIGURE 7A. FREQUENCY RESPONSE OF HIGH DECIMATION

FILTER FROM DC TO FIRST NULL

(FOR R = 16)

Gain (dB) = 20log [H(f)]

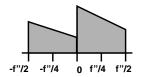

FIGURE 7B. DDC HC FREQUENCY RESPONSE (FOR R = 16) Gain (dB) = 20log[H(f)]

### Scaling Multipliers

The output of each HDF is passed to a Scaling Multiplier. The Scaling Multipliers are used to compensate for the HDF gain, which is between 1 (inclusive) and 0.5 (non-inclusive), or (0.5, 1.0). The gain through the HDF is dependent on the decimation factor: when the decimation is an even power of two, the HDF gain is equal to 1; otherwise, the gain must be compensated for in the Scaling Multiplier. The HDF gain is given by the equation:

HDF Gain =

$$R^5/2^{CEILING(5 \log_2(R))}$$

(EQ. 8)

where R is the HDF decimation factor. The compensating Scale Factor, which is input to both Scaling Multipliers, is given by the equation:

Scale Factor =

$$2^{\text{CEILING}(5 \log_2(R))}/R^5$$

(EQ. 9)

where R is the HDF decimation factor.

**NOTE:** The Scale Factor falls in the interval [1, 2). The output of the scaling multiplier is symmetrically rounded to 17 bits.

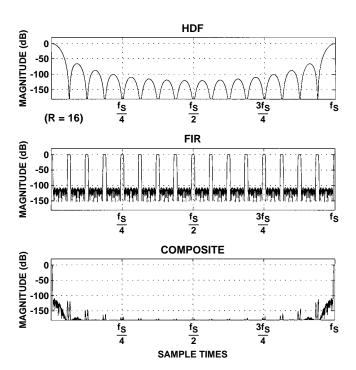

FIGURE 8A. DDC HDF, FIR, AND COMPOSITE FILTER RESPONSE (FOR R = 16)

The binary formats of the inputs and outputs of the scaling multiplier are as follows:

Input from HDF:  $a_0(-2^0)$ .  $a_1(2^{-1})$   $a_2(2^{-2})$ ...  $a_{17}(2^{-17})$  Scale factor:  $a_0(2^0)$ .  $a_1(2^{-1})$   $a_2(2^{-2})$ ...  $a_{15}(2^{-15})$  Output:  $a_0(-2^0)$ .  $a_1(2^{-1})$   $a_2(2^{-2})$ ...  $a_{16}(2^{-16})$

#### FIR Filter

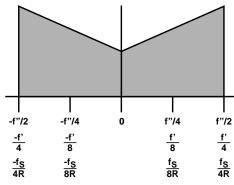

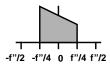

The Scaling Multiplier output is passed to the FIR Filter, which performs aliasing attenuation, passband roll off compensation and transition band shaping. The FIR Filter Section is functionally two identical 121 tap lowpass FIR filters, one each for the I and Q channel. The two filters are each implemented as sum of products, each with a single multiplier, with the coefficients stored in ROM. The filters' passbands are precompensated to be the inverse of the response of the HDF. The frequency responses of the HDF, FIR, and Composite HDF/FIR filters are shown in Figure 8. The composite passband of the HDF and FIR filter frequency response is shown in Figure 9. The FIR coefficients are scaled so that the maximum gain of the composite filter is less than or equal to 0dB. The composite passband ripple is less than 0.04dB.

FIGURE 8B. DDC FILTER RESPONSES (FOR R = 16)

FIGURE 9. FIR COMPENSATION FOR HDF ROLL OFF (FOR R = 16)

The coefficients of the filter are quantized to 22 bits to preserve greater than 106dB of stopband attenuation. The sum of products of each filter output calculation is a 38-bit number with 37 fractional bits.

When a quadrature output is selected, the outputs of the FIR filters are decimated by a factor of four. When real output is selected, only the I output is active. The output is decimated by two in this case. When Filter Only Mode is selected, only the I filter path is active and its output is decimated by four.

The composite filter bandwidths are a function of the HDF decimation rate and the FIR Filter shape. The double sided bandwidths are specified by Equations 10 and 11.

$$-3$$

dB BW<sub>DS</sub> =  $0.1375$ F<sub>S</sub>/R  $16 < R < 16384$  (EQ. 10)

$$-102$$

dB BW<sub>DS</sub> =  $0.2002$ F<sub>S</sub>/R  $16 < R < 16384$  (EQ. 11)

where  $F_S = CLK$ ; R = HDF Decimation Factor.

The single sided bandwidths are specified in Equations 12 and 13.

$$-3dB BW_{SS} = 0.06875F_{S}/R$$

(EQ. 12)

$$-102 dB BW_{SS} = 0.100097 F_{S}/R$$

(EQ. 13)

where  $F_S = CLK$ ; R = HDF Decimation Factor.

NOTE: The output data rate of the FIR is the HDF output rate divided by either 2 or 4, depending on mode. Recall the HDF output rate is CLK/R. (See Table 1.)

TABLE 1. FIR OUTPUT RATE AND DECIMATION

| OUTPUT MODE | FIR OUTPUT RATE | FIR DECIMATION |

|-------------|-----------------|----------------|

| Real        | CLK/2R          | 2              |

| Complex     | CLK/4R          | 4              |

| Filter Only | CLK/4R          | 4              |

R - HDF Decimation Factor

#### Output Formatter

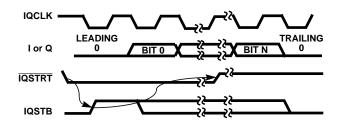

The circuit has two serial data outputs, I and Q. The timing of the output bits is referenced to IQCLK and IQSTB. There are several modes of operation for the data and control line interface, all of which were designed to be compatible with common microprocessors. These interface modes are selected by loading the appropriate control words (see Tables 3 through 10, with Table 9 containing most interface parameters).

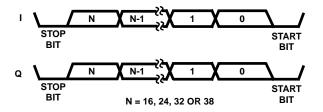

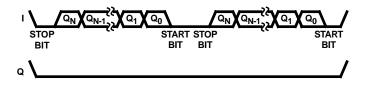

Quadrature data output can occur in one of two ways: simultaneously or sequentially. The simultaneous method clocks out the I and Q data on their respective serial output pins. The I followed by Q method clocks I and Q out sequentially on the I output pin: the entire I word is serially clocked out first, then the entire Q word. In real data Output Mode, the Formatter converts the quadrature data to real and clocks it out serially on the I output pin. In all modes, the I and Q outputs return to the zero state after the last bit is transmitted.

When the "I followed by Q" signal (CW6, bit 35) is low, I data will appear on the I output and Q data will appear on the Q output.

When the "I followed by Q" signal (CW6, bit 35) is asserted, the Q output is inactive and I data, followed by Q data appear on the I output. When in this state, and both the "Test Enable" signal (CW1, Bit 3), and "Q Strobe on Rollover" signal (CW7, Bit 10) signal are asserted, the Phase

Generator Carry Out will appear on the output. Control Word 5 contains fields to set the number of output bits transmitted to the arithmetic representation and interface control of the serial output data. Control Word 4, Bits 31-32, allow selection of baseband centered quadrature on baseband offset quadrature complex outputs. Control Word 4, Bit 0, allows selection of spectral inversion. In addition, the output drivers for I, Q, IQCLK and IQSTB can be individually enabled or placed in a high impedance state using Control Word 6, Bits 20-28. These options are explained below.

When the "Output Spectrum" signal (CW4, bits 31-32) is set to "01", then the real output data appears on the I output and the Q output in the I/Q separate mode. When in I Mode followed by Q Mode, the Q slot is also real data since the real mode outputs at twice the rate of the complex mode (CW4, bits 31-32 = 00).

When set for fixed point output, the output data can be in two's complement, offset binary or signed magnitude form. Data is converted to offset binary by complementing the most significant bit of a two's complement number. The length of the output data word can be 16, 24, 32 or 38-bits. The first three options are symmetrically rounded to the LSB of the output data; the fourth option represents the full 38-bit width of the accumulator and so represents exact arithmetic.

The output has a saturation option to prevent possible overflow due to a step input at power up. When Overflow Protection is enabled, the output is forced to be either the most positive or most negative number. Saturation is available in all four fixed point output options, and is set via Control Word 7, Bit 0.

Data can also be output in single precision floating point format (see Table 2). For all output data formats, the internal calculations are performed in exact two's complement integer arithmetic and the resulting data is converted in the Output Formatter.

**TABLE 2. FLOATING POINT FORMAT**

| SIGN | EXPONENT                         | MANTISSA  |                                       |  |

|------|----------------------------------|-----------|---------------------------------------|--|

| -20  | 2 <sup>7</sup> to 2 <sup>0</sup> | Implied 1 | 0.2 <sup>-1</sup> to 2 <sup>-23</sup> |  |

The I and Q pins can be programmed for either simultaneous or I followed by Q output. In simultaneous mode, the I and Q data appear on the I and Q pins, respectively. Each data sample is preceded by a leading zero bit, followed by the output data, followed by a trailing zero bit. In I followed by Q Mode, the output data appears on the I pin, and consists of a leading zero bit, then the I data, a trailing zero, a leading zero, the Q data, and finally a trailing zero bit. In Figures 10 through 12, the leading

and trailing zero bits occur before bit 0 and after bit N, respectively.

$$IQCLK Rate = \frac{CLK}{IQCLK Frequency} - 1$$

(EQ. 14)

A. SIMULTANEOUS OUTPUT MODE

B. I FOLLOWED BY Q OUTPUT MODE FIGURE 10. DATA OUTPUT MODES

IQCLK is used to delineate the bit or word timing of the I and Q outputs. There are several options on the configuration of IQCLK, which are controlled with Control Word 6 (see Table 8). The frequency of IQCLK is programmed to be a fraction of the CLK frequency, from (CLK rate)/2 to (CLK rate)/8192 (see Equation 14). If IQCLK Rate = 0, then IQCLK remains in its inactive state and the output bits change on the rising edges of CLK.

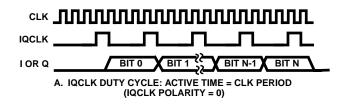

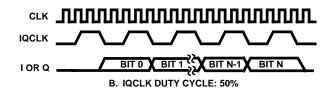

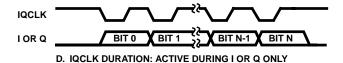

IQCLK can be programmed to be active continuously, or only during I or Q data output via the IQCLK duration bit. Using the IQCLK Duty Cycle bit, IQCLK is selectable as either 50% duty cycle or to be high for one period of CLK. In addition, the Formatter can be set so that the data bits are clocked on either the positive or negative edges of IQCLK with the IQCLK Polarity bit. Figure 11 shows the various modes of operation with IQCLK Polarity programmed for active high operation.

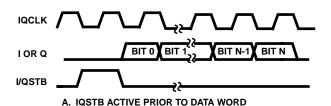

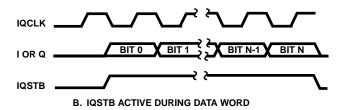

Control Word 6 also configures IQSTB, as shown in Figure 12. When programmed for Active Prior to Data Word, IQSTB is high for one period of IQCLK and terminates simultaneously with the beginning of the first data bit; otherwise it goes active with the beginning of the first bit and inactive with the end of the last bit. IQSTB can be programmed to be either active high or low.

FIGURE 11. TIMING FOR CLK, IQCLK, IQSTB, I AND Q

FIGURE 12. IQSTB TIMING

FIGURE 13. REQUESTED DATA OUTPUT TIMING

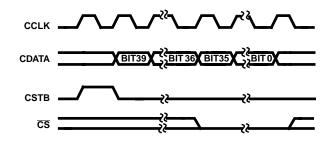

FIGURE 14. CONTROL WORD TIMING DIAGRAM

Data can be read out of the DDC on request through the use of the  $\overline{\text{IQSTRT}}$  pin. After passing through the Output Formatter, the I and Q data are stored in output buffers, which are updated at the end of the FIR Filter processing cycle. The  $\overline{\text{IQSTRT}}$  and IQSTB lines form a two line handshake as shown in Figure 13.  $\overline{\text{IQSTRT}}$  initiates the request. If the buffer has data in it, the DDC will begin an output data sequence on the next edge of IQCLK. The DDC will then put out one bit per IQCLK until the output cycle is complete. In I followed by Q Mode, one  $\overline{\text{IQSTRT}}$  will initiate an I output word followed by a Q output word. In real data Output Mode, one IQSTRT will initiate two samples of real data on the I pin.

To avoid the generation of multiple read cycles, IQSTRT must go inactive within 10 cycles of IQCLK after the initiation of IQSTB. The DDC will not update the output buffer again until the current output cycle has completed. When IQSTRT is used in this handshake mode, it must consist of pulses that satisfy the set up and hold requirements listed in the AC Timing Specifications and the pulses must occur at a rate of at least CLK/(HDF Decimation Factor x 4 -1). This mode of operation requires the Time Slot Number in Control Word 6 to be 0.

NOTE: When handshake mode is not used,  $\overline{\text{IQSTRT}}$  should be at a logic low.

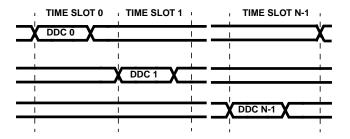

Auto Three-State Mode for IQCLK, IQSTB, I and Q allows multiple chips to operate using common data and output control lines. Each chip is assigned a Time Slot Number on the bus to use for outputting its data. All outputs programmed for Auto Three-State Mode are active during their time slot and are in a high impedance state at all other times. A time slot starts one CLK period prior to the beginning of the first bit of I or Q and ends (Time Slot Length) CLK periods afterwards. Assignment of a time slot is with reference to the deassertion of RESET. The minimum possible Time Slot Length for a given application is:

$$Length_{MIN} = [(Number of Output Bits + 2) \times Mode] + 1; or$$

(EQ. 15)

where Mode = 2 if the DDC is in either Real Output or I followed By Q Mode; else Mode = 1.

Note that Equation 15 is useful in all modes for calculating the number of IQCLKs necessary to complete one output data cycle. For a given decimation rate and output word length, the maximum value in the IQCLK Rate field is:

$$IQCLKRate_{MAX} = Floor \left[ \frac{(R) \times 4}{Length_{MIN}} \right] - 1;$$

(EQ. 16)

where Floor(X) represents the integer part of X, R is the HDF decimation factor, 4 is the FIR decimation factor.

### **Example Clock Calculations**

Clarification of the use of Equations 14-16, the calculation of the HDF and FIR clocks and the calculation of the IQCLK is best done by example:

The sample clock, CLK, is 10MHz ..... CLK = 10MHz The HDF Decimation Factor, R, is 100 (which makes the The Output Mode is I followed by  $Q \dots Mode = 2$ Complex output . . . . . . . . . FIR Decimation = 4 The desired number of output bits is 32.

- 1. We begin by identifying the HDF Input Rate: HDF Input Rate = CLK = 10MHz . . . . . . CLK = 10MHz

- 2. Next we calculate the HDF Output Rate: HDF Output Rate = CLK/R = 10MHz/(100) = 100kHz

- 3. Next we calculate the FIR output Rate: FIR Output Rate = CLK/4R = 25kHz. ..... FIR Output Rate = 25kHz

- 4. Next we calculate the minimum time slot length: Equation 15:

Length<sub>MIN</sub> =  $[(Number of Output Bits + 2) \times Mode] +1$ where the number of output bits = 32 and the Mode is 2 because of the I followed by Q output selection. Length<sub>MIN</sub> =  $[(32 + 2) \times 2] + 1 = 69 IQCLKs$

..... Length<sub>MIN</sub> = 69 IQCLKs

- 5. Next we calculate the IQCLK frequency: IQCLK frequency =  $[(F_S)(Length_{MIN})/(R)(4)] - 1$ IQCLK frequency = [(10MHz)(69)/(100)(4)] - 1 = 1.725MHzThe IQCLK frequency can be no slower than 1.725MHz if all of the bits are to be output of the DDC in a time slot. ..... Slowest Serial Output Rate = 1.725MHz

- 6. The Programmed value for the maximum IQCLK Rate, from Equation 16, is:

IQCLKRATE<sub>MAX</sub> = Floor[(R) x 4/ Length<sub>MIN</sub>] -1  $IQCLKRATE_{MAX} = Floor[(100 \times 4)/69] - 1 = 4$

The IQCLKRATE can be not greater than 4 if all of the bits are to be output of the DDC in a time slot.

. . . . . . . . . Control Word Value for IQCLK Ratemax =

[00004]H; 0 0000 0000 0100<sub>LSB</sub>

7. Let's sanity check with Equation 14. IQCLK Rate = [(CLK/IQCLKfreq)-1] = [10E6/1.725E6] -1 = 4.This checks!

### **Control Word Input**

The DDC has eight 40-bit control words which are loaded through the four pin control interface. The format and timing of this interface is compatible with the serial interface timing of most common DSP microprocessors (see Figure 14). The words are shifted MSB first, where bit 39 of the control word is the MSB. Bits 39 through 37 are the control word address, i.e., the target control buffer. CS must go low before bit 35 is clocked in. All 40 bits of the control word must be loaded. The formats of the control words are shown in Tables 3 through 10.

The control words are double buffered: each control word is initially loaded into one of eight control buffers for subsequent down loading into the corresponding Control Register. The internal circuitry of the DDC uses the Control Registers to regulate its operation. Control buffers can be downloaded in one of two ways. Loading a Buffer Register with bit 36 = 1 causes all Control Registers to be updated from their respective control buffers when the current word is finished loading. If bit 36 = 0, then only that control buffer is updated and the operation of the DDC is not affected. All Control Registers are updated from their respective buffers on the third rising edge of CLK following the deassertion of RESET. NOTE: Control Word 0 is unique in that it is only used to update the seven Control Registers, and it is recognized by the DDC regardless of the state of CS. In systems with multiple DDCs, this allows the user to update the configuration of all chips simultaneously without using RESET.

To ensure that the control information is properly loaded, the frequency of CLK must be greater than the frequency of CCLK. In addition, RESET must remain inactive during the loading of a control word.

## TABLE 3. DESTINATION ADDRESS = 0

| BIT<br>POSITION | FUNCTION | DESCRIPTION                                                               |  |  |  |

|-----------------|----------|---------------------------------------------------------------------------|--|--|--|

| 39-37           | Address  | 000 = Control Word 0                                                      |  |  |  |

| 36              | Update   | 0 = Update Only This Control Register<br>1 = Update All Control Registers |  |  |  |

| 35-32           | Reserved | All Zeroes                                                                |  |  |  |

## TABLE 4. PHASE GENERATOR/TEST ENABLE/OUTPUT REGISTER

|                 | DESTINATION ADDRESS = 1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BIT<br>POSITION | FUNCTION                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 39-37           | Address                    | 001 = Control Word 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 36              | Update                     | 0 = Update Only This Control Register 1 = Update All Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 35-4            | Minimum Phase<br>Increment | Bits $35\text{-}4=2^{31}\dots2^{0}$ . Range: $0 < \text{Minimum Phase Increment} < \pi (1\text{-}2^{-32})$ radians. In the CW mode this is the phase increment of the NCO which is added to the NCO intitial phase offset state. The desired Sin/Cos generator (local oscillator) frequency is set by the equation: $\mathbf{f_C} = (\mathbf{phase increment})\mathbf{f_S}2^{-33}$ ; where $\mathbf{f_C}$ is the desired local oscillator frequency, $\mathbf{f_S}$ is the input sampling frequency, and phase increment is the control word value in hexidecimal.  To calculate the value to be programmed into this field, use this equation: $\mathbf{phase increment} = \mathbf{INT}[\mathbf{f_C}/\mathbf{f_S})2^{33}]\mathbf{hex}$ Some examples of phase increments and local oscillator frequencies: $00000000\mathbf{h}$ : $\mathbf{f_C} = \mathbf{zero frequency}$ $0000000\mathbf{h}$ : $\mathbf{f_C} = \mathbf{f_S}/2^{33}$ - lowest frequency $(75\mathbf{MHz} \times 2^{-33} = 8.73\mathbf{mHz})$ $10000000\mathbf{h}$ : $\mathbf{f_C} = \mathbf{f_S}/32$ $2000000\mathbf{h}$ : $\mathbf{f_C} = \mathbf{f_S}/4$ $8000000\mathbf{h}$ : $\mathbf{f_C} = \mathbf{f_S}/4$ $10000000\mathbf{h}$ : $10000000\mathbf{h}$ : $10000000\mathbf{h}$ : $100000000\mathbf{h}$ : $1000000000000000000000000000000000000$ |  |  |  |

| 3               | Test Enable                | 0 = Test Features Disabled<br>1 = Test Features Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 2-0             | Phase Generator Mode       | 000 = Filter Only 001 = Normal Mode (CW) 010 = Reserved 011 = Up Chirp 100 = Reserved 101 = Down Chirp 110 = Reserved 111 = Up/Down Chirp Note that the lsb sets the gain through the DDC as follows: 0 = Gain is1 1 = Gain is 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

## TABLE 5. PHASE GENERATOR REGISTER

|                 | DESTINATION ADDRESS = 2    |                                                                                                                                                                                                                                               |  |  |

|-----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BIT<br>POSITION | FUNCTION                   | DESCRIPTION                                                                                                                                                                                                                                   |  |  |

| 39-37           | Address                    | 010 = Control Word 2                                                                                                                                                                                                                          |  |  |

| 36              | Update                     | 0 = Update Only This Control Register 1 = Update All Control Registers                                                                                                                                                                        |  |  |

| 35-32           | Reserved                   | All Zeroes                                                                                                                                                                                                                                    |  |  |

| 31-0            | Maximum Phase<br>Increment | Bits 31-0 = $2^{31}$ $2^{0}$ . Range: is 0 < Maximum Phase Increment < $\pi(1-2^{-32})$ radians. This parameter is only used in the CHIRP modes, and this is the largest allowable phase increment. Set to 0 in the Filter Only and CW modes. |  |  |

### TABLE 6. PHASE GENERATOR/OUTPUT TIME SLOT REGISTER

|                 | DESTINATION ADDRESS = 3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT<br>POSITION | FUNCTION                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 39-37           | Address                 | 011 = Control Word 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 36              | Update                  | 0 = Update Only This Control Register 1 = Update All Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 35-32           | Reserved                | All Zeroes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 31-18           | Time Slot Length        | Time Slot Length in IQCLK Periods; Bits 31-18 = 2 <sup>13</sup> 2 <sup>0</sup> . Range is (19,25, 33, 37, 39, 49, 65 and 77) The equation for calculating the value for this filed is:  TSL = [[(Number of Output Bits + 2)Mode] + 1]Hex; where mode is 2 if the DDC is in either the real or I followed by Q mode. Mode is 1 for all other DDC operational modes.  Allowable Minimum Time Slot Lengths: (18)1 + 1 = 19 (13 hexidecimal); (18)2 + 1 = 37 (25 hexidecimal); Real Output or I followed by Q  (24)1 + 1 = 25 (19 hexidecimal); Real Output or I followed by Q  (32)1 + 1 = 33 (21 hexidecimal); Real Output or I followed by Q  (38)1 + 1 = 39 (27 hexidecimal); Real Output or I followed by Q |  |  |  |  |

| 17-0            | Phase Offset            | Starting Phase Angle of Phase Accumulator; Range = 0 to $2\pi$ . Bits 17-0 = $2^{32}$ $2^{15}$ . Some example phase offset hexidecimal values : $0000 - 0$ $1000 - \pi/2$ $2000 - \pi$ $3000 - 3\pi/2$ $3fff - 2\pi$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

TABLE 7. PHASE GENERATION/HDF.OUTPUT REGISTER

|                 | DESTINATION ADDRESS = 4          |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BIT<br>POSITION | FUNCTION                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 39-37           | Address                          | 100 = Control Word 4                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 36              | Update                           | 0 = Update Only This Control Register<br>1 = Update All Control Registers                                                                                                                                                                                                                                                                                    |  |  |  |

| 35-33           | Reserved                         | All Zeroes                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 32-31           | Output<br>Spectrum               | 00 = No Up Conversion,Complex Output 01 = Up Convert by f"/4, Real Output 10 = Up Convert by f"/2,Complex Output 11 = Reserved Mode                                                                                                                                                                                                                          |  |  |  |

| 30-7            | Delta Phase Increment            | 24-Bit Delta Phase Increment. Bits $30-7=2^{23}2^0$ . Range: $0 < Delta Phase Increment < \pi (2^{-8}-2^{-32})$                                                                                                                                                                                                                                              |  |  |  |

| 6-1             | HDF Data Shift<br>(Shift Factor) | 16-Bit HDF Gain Compensation Number - the shift portion. HDF Input Data Shift (Towards LSB). Bits $6-1=2^52^0$ . Range: $0 \le$ Shift Factor $\le$ 55 decimal; Range: $[0 \le$ Shift Factor $\le$ 37]hex Calculate the value for this field using this equation: HDF Data Shift = [75 - Ceiing(5 log <sub>2</sub> (R))]hex Note: $\log_2(x) = (3.32)\log(x)$ |  |  |  |

| 0               | Spectral Reverse                 | 0 = Normal Output<br>1 = Spectrally Reversed Output                                                                                                                                                                                                                                                                                                          |  |  |  |

## TABLE 8. HDF/OUTPUT REGISTER

|                 | DESTINATION ADDRESS = 5                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BIT<br>POSITION | N FUNCTION DESCRIPTION                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 39-37           | Address                                        | 101 = Control Word 5                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 36              | Update                                         | 0 = Update Only This Control Register 1 = Update All Control Registers                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 35-21           | HDF Decimation<br>Counter Preload<br>(HDF DCP) | HDF Decimation Counter Preload. Range: 15 < HDF Decimation Counter Preload < 32,767 Calculate the value for this feild using this equation:  HDF DCP = R - 1; where R is the HDF decimation (rate change) factor.  Common HDF decimation (rate change) factors and associated hexidecimal HDF DCP values:  000f: R = 16 00ff: R = 128 01ff: R = 512 03ff: R = 1,024 07ff: R = 2,048 0fff: R = 4,096 1fff: R = 8,192 3fff: R = 16,384 7fff: R = 32,768 |  |  |

# TABLE 8. HDF/OUTPUT REGISTER (Continued)

|                 | DESTINATION ADDRESS = 5                   |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                            |                                                                                                                          |  |

|-----------------|-------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| BIT<br>POSITION | FUNCTION                                  |                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |                            |                                                                                                                          |  |

| 20-5            | Scaling Multiplier Gain<br>(Scale Factor) | Range:<br>Field Fo<br>Calculat<br>Scale F<br>ING(x) i | 16-Bit HDF Gain Compensation Number - the multiplier portion.  Range: 1 ≤ Scale Factor < 2, Field Format = 2 <sup>0</sup> .2 <sup>-1</sup> 2 <sup>-15</sup> .  Calculate the value for this field using this equation:  Scale Factor = 2 <sup>CEILING(5log</sup> 2 <sup>(R))</sup> /(R) <sup>5</sup> ; where R is the HDF decimation (rate change) factor and CEIL-ING(x) is equal to x for integer values, otherwise is equal to the next higher integer.  Common HDF decimation factors (R), decimation counter preload (DCP) and Scale Factors (SF) values: |              |                            |                                                                                                                          |  |

|                 |                                           | R                                                     | DCP(de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | c) DCP(h     | nex) SF(dec)               | SF(hex)                                                                                                                  |  |

|                 |                                           | 16                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 000       |                            | 8000                                                                                                                     |  |

|                 |                                           | 128                                                   | 3 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27 007       | f 1.000                    | 8000                                                                                                                     |  |

|                 |                                           | 512                                                   | 2 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 01f       | f 1.00                     | 8000                                                                                                                     |  |

|                 |                                           | 1,024                                                 | 1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23 03f       | f 1.000                    | 8000                                                                                                                     |  |

|                 |                                           | 2,048                                                 | 3 2,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47 07f       | f 1.000                    | 8000                                                                                                                     |  |

|                 |                                           | 4,096                                                 | 4,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95 Offf      | 1.000                      | 8000                                                                                                                     |  |