# CMOS Single-Supply Rail-to-Rail Input/Output Operational Amplifier

# OP150/OP250/OP450

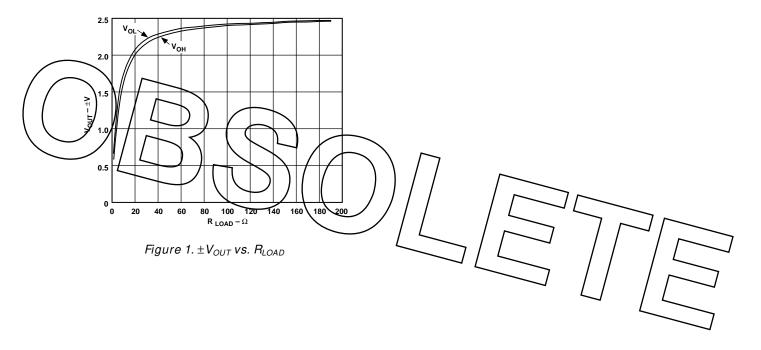

Single-Supply Operation: 2.7 V to 6 V High Output Current: ±250 mA Low Supply Current: 600 μA/ Amp

Wide Bandwidth: 4 MHz Slew Rate: 6.5 V/μs No Phase Reversal Low Input Currents Unity Gain Stable

APPLICATIONS

**FEATURES**

Battery Powered Instrumentation

Multi Media Audio Medical

-Remote Sensors ASIC Input or Output Amplifier

Automotive Headphone Drive

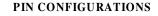

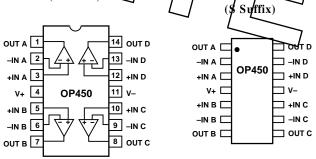

8-Lead Narrow-Body SO (S Suffix)

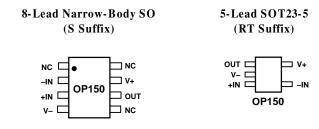

8 Lead Epoxy DIP (P Suffix)

**OP250**

ead SQ

8 V+

6 –IN B

7 OUT B

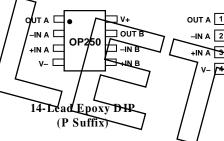

14-Lead TSSOP (RU Suffix)

#### GENERAL DESCRIPTION

The OP150, OP250 and OP450 are single, dual and quad *CMOS* single-supply, 4 MHz bandwidth amplifiers featuring *rail-to-rail inputs and outputs*. All are guaranteed to operate from a *3 volt single supply* as well as a +5 volt supply.

The OP150 family of amplifiers have very low input bias currents. The outputs are capable of driving 250 mA loads and are stable with capacitive loads as high as 500 pF.

Applications for these amplifiers include portable medical equipment, safety and security, and interface for transducers with high output impedances.

Supply current is only 600 µA per amplifier.

The ability to swing rail-to-rail at both the input and output enables designers to build multistage filters in single-supply systems and maintain high signal-to-noise ratios.

The OP150/OP250/OP450 are specified over the extended industrial (-40°C to +125°C) temperature range. The OP150 single amplifiers are available in 8-pin SO surface mount and the 5-pin SOT23-5 packages. The OP250 dual is available in 8-pin plastic DIPs and SO surface mount packages. The OP450 quad is available in 14-pin DIPs, TSSOP and narrow 14-pin SO packages. Consult factory for TSSOP availability.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

# OP150/OP250/OP450-SPECIFICATIONS

#

| Parameter                                                                                          | Symbol                                                      | Conditions                                                                                                                                                                                                              | Min      | Тур            | Max | Units                                       |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|-----|---------------------------------------------|

| INPUT CHARACTERISTICS Offset Voltage OP150                                                         | Vos                                                         |                                                                                                                                                                                                                         |          |                | 5   | mV                                          |

| Offset Voltage OP250/OP450                                                                         | Vos                                                         | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                  |          |                | 5   | m V<br>m V                                  |

| Input Bias Current                                                                                 | $I_B$                                                       | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                  |          | 10             | 60  | mV<br>pA                                    |

| Input Offset Current                                                                               | Ios                                                         | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                  |          | 25             |     | pA<br>pA                                    |

| Input Voltage Range<br>Common-Mode Rejection Ratio                                                 | CMRR                                                        | $-40^{\circ}C \le T_{A} \le +125^{\circ}C$ $V_{CM} = 0 \text{ V to 3 V}$ $-40^{\circ}C \le T_{A} \le +125^{\circ}C$                                                                                                     | 0<br>60  |                | 3   | pA<br>V<br>dB<br>dB                         |

| Large Signal Voltage Gain                                                                          | $A_{VO}$                                                    | $R_L = 10 \text{ k}\Omega, V_O = 0.3 \text{ V to } 2.7 \text{ V}$<br>-40°C \le T_A \le +125°C                                                                                                                           |          | 40             |     | V/mV<br>V/mV                                |

| Large Signal Voltage Gain Large Signal Voltage Gain Offset Voltage Drift                           | Avo<br>ΔVos/ΔT                                              | $R_L = 2 \text{ k}\Omega, V_O = 0.3 \text{ V to } 2.7 \text{ V}$ $R_L = 1 \text{ k}\Omega, V_O = 0.3 \text{ V to } 2.7 \text{ V}$                                                                                       |          | 16<br>10       |     | V/mV<br>V/mV<br>μV/°C                       |

| Bias Current Drift Offset Current Drift                                                            | $\Delta I_{\rm P}/\Delta T$<br>$\Delta I_{\rm OS}/\Delta T$ |                                                                                                                                                                                                                         |          |                |     | pA/°C<br>pA/°C                              |

| OUTPUT CHARACTERISTICS Output Voltage High                                                         | VOH                                                         | I <sub>L</sub> = 100 µA<br>-10°C to +125°C                                                                                                                                                                              | 2.95     | 7/99           |     | V                                           |

| Output Voltage Low                                                                                 | $V_{OL}$                                                    | $I_{L} = 10 \text{ mA}$ $-40^{\circ}\text{C to } +125^{\circ}\text{C}$ $I_{L} = 100  \mu\text{A}$ $-40^{\circ}\text{C to } +125^{\circ}\text{C}$ $I_{L} = 10 \text{ mA}$ $-40^{\circ}\text{C to } +125^{\circ}\text{C}$ |          | 2.95           | 10  | mV<br>mV<br>mV                              |

| Output Current                                                                                     | $I_{OUT}$                                                   | -40°C to +125°C                                                                                                                                                                                                         |          | ±250           |     | mA<br>mA                                    |

| Open Loop Impedance                                                                                | Z <sub>OUT</sub>                                            | $f = 1 \text{ MHz}, A_V = 1$                                                                                                                                                                                            |          |                |     | Ω                                           |

| POWER SUPPLY Power Supply Rejection Ratio                                                          | PSRR                                                        | $V_S = 2.7 \text{ V to 6 V}$<br>-40°C \le T_A \le +125°C                                                                                                                                                                | 70<br>68 |                |     | dB<br>dB                                    |

| Supply Current/Amplifier                                                                           | $I_{SY}$                                                    | $V_{O} = 0 \text{ V}$<br>-40°C \le T <sub>A</sub> \le +125°C                                                                                                                                                            |          | 500<br>650     | 600 | μA<br>μA                                    |

| DYNAMIC PERFORMANCE Slew Rate Settling Time Gain Bandwidth Product Phase Margin Channel Separation | SR<br>t <sub>S</sub><br>GBP<br>Øo<br>CS                     | $R_{L} = 10 \text{ k}\Omega$ $To 0.01\%$ $f = 1 \text{ kHz}, R_{L} = 10 \text{ k}\Omega$                                                                                                                                |          | 2.7<br>2<br>75 |     | V/µs<br>µs<br>MHz<br>Degrees<br>dB          |

| NOISE PERFORMANCE Voltage Noise Voltage Noise Density Current Noise Density                        | $egin{array}{c} e_n \ p-p \ e_n \ i_n \end{array}$          | 0.1 Hz to 10 Hz<br>f = 1 kHz                                                                                                                                                                                            |          | 55             |     | $\mu V p-p \\ nV/\sqrt{Hz} \\ pA/\sqrt{Hz}$ |

Specifications subject to change without notice.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#

| Parameter                                      | Symbol                                             | Conditions                                                                                                          | Min      | Тур                     | Max                | Units        |

|------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------|-------------------------|--------------------|--------------|

| INPUT CHARACTERISTICS                          | **                                                 |                                                                                                                     |          |                         | _                  | ***          |

| Offset Voltage OP150                           | Vos                                                | 400G & T 1050G                                                                                                      |          |                         | 5                  | m V          |

| Offset Voltage OP250/OP450                     | W                                                  | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                              |          |                         | 5                  | mV<br>mV     |

| Offset Voltage OP230/OP430                     | Vos                                                | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                              |          |                         | 3                  | mV           |

| Input Bias Current                             | $I_{\mathrm{B}}$                                   | 40 C 3 I A 3 1 1 2 3 C                                                                                              |          | 30                      | 50                 | pA           |

| input Blus Current                             | -в                                                 | $-40$ °C $\leq T_A \leq +125$ °C                                                                                    |          | 50                      | 60                 | pA           |

| Input Offset Current                           | I <sub>OS</sub>                                    | A                                                                                                                   |          | 0.1                     | 8                  | pA           |

| •                                              |                                                    | $-40$ °C $\leq T_A \leq +125$ °C                                                                                    |          |                         | 16                 | pA           |

| Input Voltage Range                            |                                                    |                                                                                                                     | 0        |                         | 5                  | V            |

| Common-Mode Rejection Ratio                    | CMRR                                               | $V_{\rm CM} = 0 \text{ V to 5 V}$                                                                                   | 60       |                         |                    | dB           |

|                                                |                                                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                              |          |                         |                    | dB           |

| Large Signal Voltage Gain                      | $A_{VO}$                                           | $R_L = 10 \text{ k}\Omega, V_O = 0.3 \text{ V to } 4.7 \text{ V}$                                                   |          | 40                      |                    | V/mV         |

|                                                |                                                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                              |          | 1.6                     |                    | V/mV         |

| Large Signal Voltage Gain                      | $A_{VO}$                                           | $R_L = 2 k\Omega$ , $V_O = 0.3 V$ to 2.7 V                                                                          |          | 16                      |                    | V/mV<br>V/mV |

| Large Signal Voltage Sain Offset Voltage Drift | $\Delta V_{OS}\Delta T$                            | $R_L = 1 \text{ kQ}, V_O = 0.3 \text{ V to } 2.7 \text{ V}$<br>$40^{\circ}\text{C} \le T \le + 125^{\circ}\text{C}$ |          | 10<br>1.5               |                    | μV/°C        |

| Bias Current Drift                             | $\Delta V_{OS} \Delta T$ $\Delta I_{A} / \Delta T$ | -40 C \ 1\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                          |          | 1.5                     |                    | pA/°C        |

| Offset Current Drift                           | $\Delta I_{OS}/\Delta \Gamma$                      |                                                                                                                     |          | 20                      |                    | pA/°C        |

|                                                | 08/21                                              | acksquare                                                                                                           | $\sim$ 7 | 20                      |                    | pri c        |

| OUTPUT CHARACTERISTICS                         |                                                    |                                                                                                                     |          |                         | $\supset$ $\sim$   |              |

| Output Voltage High                            | $V_{OH}$                                           | L=100 μA/ L                                                                                                         |          | 4.99                    | $\sim$ / $^{\sim}$ | ₩            |

|                                                |                                                    | $-40^{\circ}\text{C to} + 1/25^{\circ}\text{C}$                                                                     |          | 1 [                     | [                  | \\           |

|                                                |                                                    | $I_{L} = 10 \text{ mA}$                                                                                             |          | <b>/</b> 4.9 <b>/</b> 5 | / _                | V            |

| 0 4 4 1/4 1                                    | 3.7                                                | -40°C to +125°C                                                                                                     |          | / /                     | / /                | V .7         |

| Output Voltage Low                             | V <sub>OL</sub>                                    | $I_L = 100 \mu\text{A}$<br>-40°C to +125°C                                                                          |          |                         | 11                 | m√<br>mV     |

|                                                |                                                    | $I_{L} = 10 \text{ mA}$                                                                                             |          | 30                      |                    | m V          |

|                                                |                                                    | -40°C to +125°C                                                                                                     |          | 30                      |                    | mV           |

| Output Current                                 | I <sub>OUT</sub>                                   | 40 € 10 1 123 €                                                                                                     |          | ±250                    |                    | mA           |

| o aspar carrent                                | 1001                                               | -40°C to +125°C                                                                                                     |          |                         |                    | m A          |

| Open Loop Impedance                            | $Z_{OUT}$                                          | $f = 1 \text{ MHz}, A_V = 1$                                                                                        |          |                         |                    | Ω            |

| DOWED CHIDDLY                                  |                                                    |                                                                                                                     |          |                         |                    |              |

| POWER SUPPLY  Power Supply Principle Patie     | PSRR                                               | V - 27 V to 6 V                                                                                                     | 75       |                         |                    | dB           |

| Power Supply Rejection Ratio                   | PSKK                                               | $V_S = 2.7 \text{ V to 6 V}$<br>-40°C \le T_A \le +125°C                                                            | 70       |                         |                    | dB           |

| Supply Current/Amplifier                       | $I_{SY}$                                           | $V_0 = 0 \text{ V}$                                                                                                 | /0       |                         |                    | μA           |

| Supply Cultent//mipliner                       | 154                                                | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                              |          | 550                     | 650                | μΑ           |

|                                                |                                                    | 10 C = 1 A = 1123 C                                                                                                 |          |                         |                    | Par          |

| DYNAMIC PERFORMANCE                            |                                                    |                                                                                                                     |          |                         |                    |              |

| Slew Rate                                      | SR                                                 | $R_L = 10 \text{ k}\Omega$                                                                                          |          | 6.5                     |                    | V/µs         |

| Full Power Bandwidth                           | $BW_p$                                             | 1% Distortion                                                                                                       |          |                         |                    | kHz          |

| Settling Time                                  | t <sub>S</sub>                                     | То 0.01%                                                                                                            |          | 4                       |                    | μs           |

| Gain Bandwidth Product Phase Margin            | GBP                                                |                                                                                                                     |          | 4<br>75                 |                    | MHz          |

| Channel Separation                             | Øo<br>CS                                           | $f = 1 \text{ kHz}, R_L = 10 \text{ k}\Omega$                                                                       |          | 13                      |                    | Degrees      |

| <del>_</del>                                   |                                                    | 1 – 1 K112, KL – 10 K22                                                                                             |          |                         |                    | uD           |

| NOISE PERFORMANCE                              |                                                    |                                                                                                                     |          |                         |                    |              |

| Voltage Noise                                  | e <sub>n</sub> p-p                                 | 0.1 Hz to 10 Hz                                                                                                     |          |                         |                    | μV p-p       |

| Voltage Noise Density                          | e <sub>n</sub>                                     | f = 1  kHz                                                                                                          |          | 55                      |                    | nV/√Hz       |

| Voltage Noise Density                          | e <sub>n</sub>                                     | f = 10  kHz                                                                                                         |          | 35                      |                    | nV/√Hz       |

| Current Noise Density                          | i <sub>n</sub>                                     |                                                                                                                     |          |                         |                    | pA/√Hz       |

Specifications subject to change without notice.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

## OP150/OP250/OP450

## WAFER TEST LIMITS (@ $V_S = +5.0 \text{ V}$ , $V_{CM} = 0 \text{ V}$ , $T_A = +25 ^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                    | Symbol          | Conditions                              | Limit    | Units    |

|------------------------------|-----------------|-----------------------------------------|----------|----------|

| Offset Voltage               | Vos             |                                         | ±10      | mV max   |

| Input Bias Current           | I <sub>B</sub>  |                                         | 50       | pA max   |

| Input Offset Current         | I <sub>OS</sub> |                                         | 10       | pA max   |

| Input Voltage Range          | $V_{CM}$        |                                         | V- to V+ | V min    |

| Common-Mode Rejection Ratio  | CMRR            | $V_{CM} = 0 \text{ V to } 10 \text{ V}$ | 60       | dB min   |

| Power Supply Rejection Ratio | PSRR            | V = +2.7  V to  +7  V                   | 70       | dB min   |

| Large Signal Voltage Gain    | A <sub>VO</sub> | $R_L = 10 \text{ k}\Omega$              |          | V/mV min |

| Output Voltage High          | $V_{OH}$        | $R_L = 2 k\Omega$ to GND                | 2.9      | V min    |

| Output Voltage Low           | $V_{OL}$        | $R_L = 2 k\Omega \text{ to V} +$        | 55       | mV max   |

| Supply Current/Amplifier     | $I_{SY}$        | $V_O = 0 V, R_L = \infty$               | 650      | μA max   |

Electrical tests and water probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate pecifications based on dice lot qualifications through sample lot assembly and testing.

| Package Type           | $\theta_{\mathrm{JA}}{}^{3}$ | $\theta_{ m JC}$ | Units |

|------------------------|------------------------------|------------------|-------|

| 5-Pin SOT (RT)         | 325                          |                  | °C/W  |

| 8-Pin Plastic DIP (P)  | 103                          | 43               | °C/W  |

| 8-Pin SOIC (S)         | 158                          | 43               | °C/W  |

| 8-Pin TSSOP (RU)       | 240                          | 43               | °C/W  |

| 14-Pin Plastic DIP (P) | 76                           | 33               | °C/W  |

| 14-Pin SOIC (S)        | 120                          | 36               | °C/W  |

| 14-Pin TSSOP(RU)       | 180                          | 35               | °C/W  |

#### NOTES

## ORDERING GUIDE

| \                  | Temperature                         |                    |

|--------------------|-------------------------------------|--------------------|

| Model              | Range                               | Package Option     |

| ØP1/50GS           | $-40^{\circ}$ C to $+125^{\circ}$ C | 8-Pin SQIC         |

| /OP/50 <b>G</b> RT | -40°C to +125°C                     | 5-Pin SOT          |

| OP150GBC           | +/25°/C                             | DICE /             |

| OP250GP            | 7 $+40$ °C to +125°C                | 8-Pin/Plastic/DIN  |

| OP250GS            | 40°C to +125°C                      | \$-Pifn SOIC/      |

| OP250GRU           | -40°C to +125°C                     | /8-P/in TSSØP      |

| OP250GBC           | +25°C                               | LDICE / L          |

| OP450GP            | -40°C to $+125$ °C                  | 14-Pin Plastic DIP |

| OP450GS            | -40°C to $+125$ °C                  | 14-Pin SOIC        |

| OP450GRU           | -40°C to $+125$ °C                  | 14-Pin TSSOP       |

| OP450GBC           | +25°C                               | DICE               |

|                    |                                     |                    |

## CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the OP150/OP250/OP450 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

$<sup>^2\</sup>theta_{JA}$  is specified for the worst case conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for P-DIP packages;  $\theta_{JA}$  is specified for device soldered in circuit board for SOIC package.

## DICE CHARACTERISTICS

OP150 Die Size  $0.00 \times 0.00$  Inch, 00 Sq. Mils Substrate (Die Backside) Is Connected to V- Transistor Count, 00. OP250 Die Size  $0.044 \times 0.045$  Inch, 1,980 Sq. Mils Substrate (Die Backside) Is Connected to V- Transistor Count, 0. OP450 Die Size  $0.052 \times 0.058$  Inch, 3,016 Sq. Mils Substrate (Die Backside) Is Connected to V- Transistor Count, 127.