### ISL6161

**Dual Power Distribution Controller**

FN9104 Rev.7.00 Aug 16, 2018

The <u>ISL6161</u> is a hot swap dual supply power distribution controller that can be used in PCI Express (PCIe) applications.

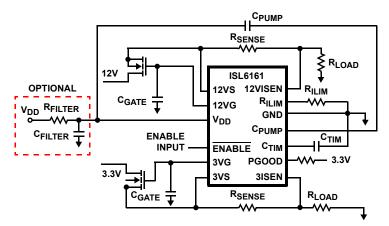

Two external N-channel MOSFETs are driven to distribute and control power while providing load fault isolation. At turn-on, the gate of each external N-channel MOSFET is charged with a 10µA current source. Capacitors on each gate create a programmable ramp (soft turn-on) to control in-rush currents, as Figure 1 shows. A built-in charge pump supplies the gate drive for the 12V supply N-channel MOSFET switch.

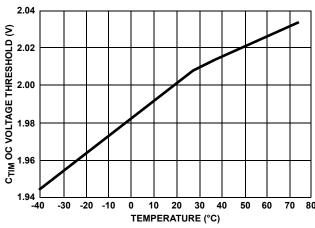

Two external current sense resistors and FETs provide overcurrent (OC) protection. When the current through either resistor exceeds the user programmed value, the controller enters Current Regulation mode. The timeout capacitor, C<sub>TIM</sub>, starts charging as the controller enters the timeout period. When C<sub>TIM</sub> charges to a 2V threshold, both N-Channel MOSFETs are latched off. In the event of a hard and fast fault of at least three times the programmed current limit level, the N-channel MOSFET gates are pulled low immediately before entering the timeout period. The controller is reset by a rising edge on the ENABLE pin.

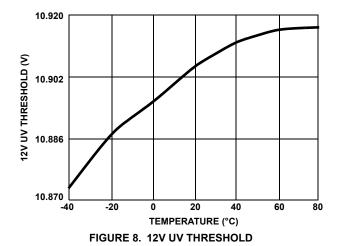

The ISL6161 constantly monitors both output voltages and reports either one being low on the PGOOD output as a low. The 12V PGOOD Voltage Threshold (Vth) is ~10.8V and the 3.3V Vth is ~2.85V nominally.

## **Related Literature**

For a full list of related documents, visit our website

• ISL6161 product information page

### **Features**

- Hot swap dual power distribution and control for +12V and +3.3V rails

- · Provides fault isolation

- · Programmable current regulation level

- Programmable timeout

- . Charge pump allows the use of N-channel MOSFETs

- · Power-good and OC latch indicators

- · Adjustable turn-on ramp

- · Protection during turn-on

- Two levels of current limit detection provide fast response to varying fault conditions

- 1µs response time to dead short

- 3µs response time to 200% current overshoot

- · Pb-free available (RoHS compliant)

## **Applications**

- PCle applications

- Power distribution and control

- · Hot plug and hot swap components

FIGURE 1. TYPICAL APPLICATION DIAGRAM

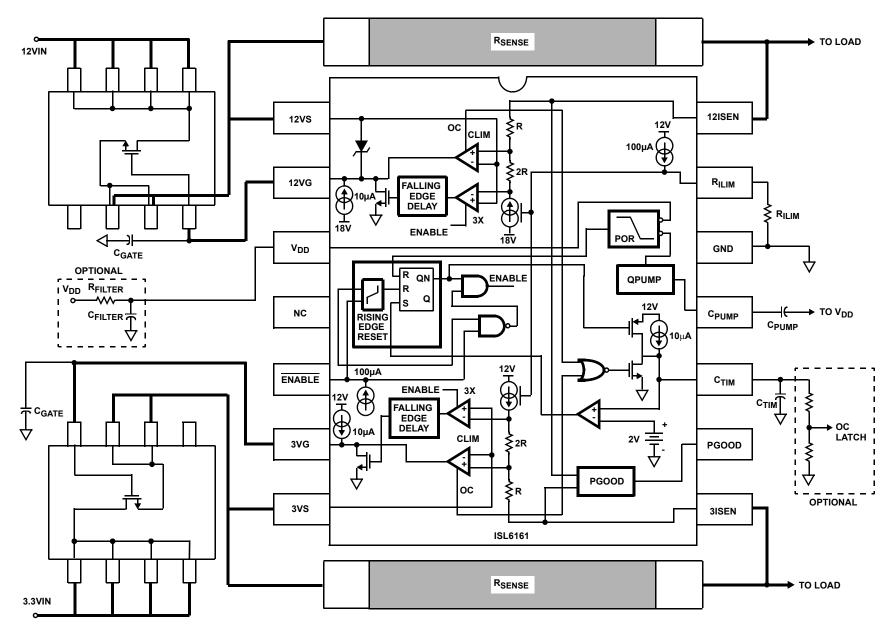

FIGURE 2. SIMPLIFIED SCHEMATIC (for 14 LD SOIC)

# **Ordering Information**

| PART NUMBER<br>(Notes 2, 3) | PART<br>MARKING | TEMP. RANGE<br>(°C) | TAPE AND REEL<br>(Units) (Note 1) | PACKAGE<br>(RoHS Compliant) | PKG. DWG. # |

|-----------------------------|-----------------|---------------------|-----------------------------------|-----------------------------|-------------|

| ISL6161IVZA-T               | 6161IVZ         | -40 to +85          | 2.5k                              | 16 Ld TSSOP                 | M16.173     |

| ISL6161CBZA                 | 6161CBZ         | 0 to +70            | -                                 | 14 Ld SOIC                  | M14.15      |

| ISL6161CBZA-T               | 6161CBZ         | 0 to +70            | 2.5k                              | 14 Ld SOIC                  | M14.15      |

#### NOTE:

- 1. Refer to  $\underline{\mathsf{TB347}}$  for details about reel specifications.

- 2. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), see the ISL6161 product information. For more information about MSL, refer to TB363.

# **Pin Configurations**

# **Pin Descriptions**

| PIN #<br>SOIC | PIN #<br>TSSOP | SYMBOL            | FUNCTION                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|----------------|-------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | 1              | 12VS              | 12V Source                        | Connect to the associated external N-channel MOSFET switch source to sense output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                              |

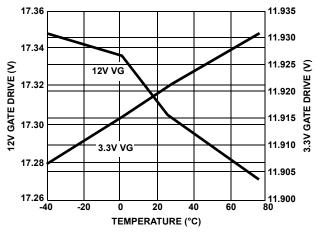

| 2             | 2              | 12VG              | 12V Gate                          | Connect to the associated N-channel MOSFET switch gate. A capacitor from this node to ground sets the turn-on ramp. At turn-on, this capacitor will be charged to ~17.4V by a $10\mu$ A current source.                                                                                                                                                                                                                                                                                                                 |

| 3             | 4              | V <sub>DD</sub>   | Chip Supply                       | Connect to the 12V supply. This can be connected directly to the +12V rail supplying the load voltage or to a dedicated $V_{DD}$ +12V supply. If connecting to the +12V rail supplying the load voltage, pay special attention to $V_{DD}$ decoupling to prevent sagging as heavy loads are switched on.                                                                                                                                                                                                                |

| 4             | 3,6,14         | NC                | Not Connected                     | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5             | 5              | ENABLE            | Enable/Reset                      | Turns on and resets the chip. Both outputs turn on when this pin is driven low. After a current limit timeout, the chip is reset by the rising edge of a reset signal applied to the ENABLE pin. This input has 100µA pull-up capability, which is compatible with 3V and 5V open drain and standard logic.                                                                                                                                                                                                             |

| 6             | 7              | 3VG               | 3V Gate                           | Connect to the gate of the external 3V N-channel MOSFET. A capacitor from this node to ground sets the turn-on ramp. At turn-on, this capacitor will be charged to $\sim 11.9V$ by a $10\mu A$ current source.                                                                                                                                                                                                                                                                                                          |

| 7             | 8              | 3VS               | 3V Source                         | Connect to the source side of 3V external N-channel MOSFET switch to sense output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8             | 9              | 3VISEN            | 3V Current Sense                  | Connect to the load side of the 3V sense resistor to measure the voltage drop across this resistor between the 3VS and 3VISEN pins.                                                                                                                                                                                                                                                                                                                                                                                     |

| 9             | 10             | PGOOD             | Power-Good<br>Indicator           | Indicates that all output voltages are within specification. PGOOD is driven by an open drain N-Channel MOSFET. It is pulled low when any output is not within specification.                                                                                                                                                                                                                                                                                                                                           |

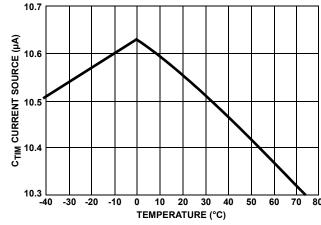

| 10            | 11             | C <sub>TIM</sub>  | Current Limit Timing<br>Capacitor | Connect a capacitor from this pin to ground. This capacitor controls the time between the onset of current limit and chip shutdown (current limit timeout). The duration of current limit timeout (in seconds) = $200k\Omega \times C_{TIM}$ (Farads).                                                                                                                                                                                                                                                                  |

| 11            | 12             | C <sub>PUMP</sub> | Charge Pump<br>Capacitor          | Connect a 0.1µF capacitor between this pin and V <sub>DD</sub> (Pin 3). Provides charge storage for the 12VG drive.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12            | 13             | GND               | Chip Ground                       | Chip ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

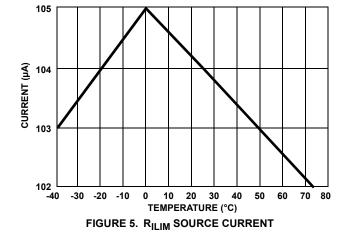

| 13            | 15             | R <sub>ILIM</sub> | Current Limit Set<br>Resistor     | A resistor connected between this pin and ground determines the current level at which current limit is activated. This current is determined by the ratio of the R <sub>ILIM</sub> resistor to the sense resistor (R <sub>SENSE</sub> ). The current at current limit onset is equal to $10\mu A \times (R_{ILIM}/R_{SENSE})$ . The ISL6161 can accommodate either a $10k\Omega$ resistor (OC Vth = $100mV$ ) or a $4.99k\Omega$ resistor for a lower trip (OC Vth = $53mV$ ). See Table 2 on page 7 for more details. |

| 14            | 16             | 12VISEN           | 12V Current Sense                 | Connect to the load side of the sense resistor to measure the voltage drop across this resistor.                                                                                                                                                                                                                                                                                                                                                                                                                        |

### **Absolute Maximum Ratings** T<sub>A</sub> = 25°C

| V <sub>DD</sub>                | 0.3V to +16V                   |

|--------------------------------|--------------------------------|

| 12VG, C <sub>PUMP</sub>        | 0.3V to 21V                    |

| 12VISEN, 12VS                  | 5V to V <sub>DD</sub> + 0.3V   |

| 3VISEN, 3VS                    | 5V to 7.5V                     |

| PGOOD, R <sub>ILIM</sub>       | 0.3V to 7.5V                   |

| ENABLE, C <sub>TIM</sub> , 3VG | 0.3V to V <sub>DD</sub> + 0.3V |

| ESD Classification             | 2kV (Class 2)                  |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 4)           | θ <sub>JA</sub> (°C/W) |

|------------------------------------------------|------------------------|

| 14 Ld SOIC Package                             | 67                     |

| 16 Ld TSSOP Package                            |                        |

| Maximum Junction Temperature (Plastic Package) | +150°C                 |

| Maximum Storage Temperature Range65            | 5°C to +150°C          |

| Pb-Free Reflow Profile                         | Refer to TB493         |

### **Operating Conditions**

| V <sub>DD</sub> Supply Voltage Range | +10.5V to +13.2V |

|--------------------------------------|------------------|

| Temperature Range (T <sub>A</sub> )  |                  |

| ISL6161IVZA                          | 40°C to +85°C    |

| ISL6161CBZA                          | 0°C to +70°C     |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured with the component mounted on a high-effective thermal conductivity test board in free air. Refer to TB379 for details.

- 5. All voltages are relative to GND, unless otherwise specified.

**Electrical Specifications**  $V_{DD} = 12V$ ,  $C_{VG} = 0.01\mu\text{F}$ ,  $C_{TIM} = 0.1\mu\text{F}$ ,  $R_{SENSE} = 0.1\Omega$ ,  $C_{BULK} = 220\mu\text{F}$ , ESR = 0.5W,  $T_A = T_J = -40\,^{\circ}\text{C}$  to +85 °C, unless otherwise specified. Parameters with MIN and/or MAX limits are 100% tested at +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| PARAMETER                                                                   | SYMBOL                 | TEST CONDITIONS                                              | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------------------------------|------------------------|--------------------------------------------------------------|------|------|------|-------|

| 12V CONTROL                                                                 | •                      |                                                              |      |      |      |       |

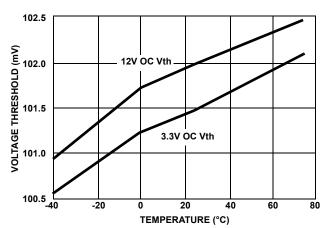

| Current Limit Threshold Voltage                                             | V <sub>IL12V</sub>     | R <sub>ILIM</sub> = 10kΩ                                     | 92   | 100  | 108  | mV    |

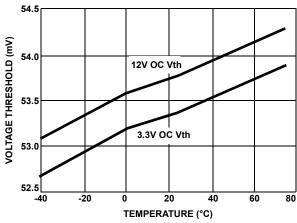

| (Voltage Across Sense Resistor)                                             |                        | R <sub>ILIM</sub> = 5kΩ                                      | 47   | 53   | 59   | mV    |

| 3x Current Limit Threshold Voltage                                          | 3 x V <sub>IL12V</sub> | R <sub>ILIM</sub> = 10kΩ                                     | 250  | 300  | 350  | mV    |

| (Voltage Across Sense Resistor)                                             |                        | R <sub>ILIM</sub> = 5kΩ                                      | 100  | 165  | 210  | mV    |

| ±20% Current Limit Response Time<br>(Current within 20% of Regulated Value) | 20%iLrt                | 200% Current Overload, $R_{ILIM}$ = 10kΩ, $R_{SHORT}$ = 6.0Ω | -    | 2    | -    | μs    |

| ±10% Current Limit Response Time<br>(Current within 10% of Regulated Value) | 10%iLrt                | 200% Current Overload, $R_{ILIM}$ = 10kΩ, $R_{SHORT}$ = 6.0Ω | -    | 4    | -    | μs    |

| ±1% Current Limit Response Time<br>(Current within 1% of Regulated Value)   | 1%iLrt                 | 200% Current Overload, $R_{ILIM}$ = 10kΩ, $R_{SHORT}$ = 6.0Ω | -    | 10   | -    | μs    |

| Response Time to Dead Short                                                 | RT <sub>SHORT</sub>    | C <sub>12VG</sub> = 0.01µF                                   | -    | 500  | -    | ns    |

| Gate Turn-On Time                                                           | t <sub>ON12V</sub>     | C <sub>12VG</sub> = 0.01µF                                   | -    | 12   | -    | ms    |

| Gate Turn-On Current                                                        | I <sub>ON12V</sub>     | C <sub>12VG</sub> = 0.01µF                                   | 8    | 10   | 12   | μΑ    |

| 3x Gate Discharge Current                                                   | 3Xdisl                 | 12VG = 18V                                                   | -    | 0.75 | -    | Α     |

| 12V Undervoltage Threshold                                                  | 12V <sub>VUV</sub>     |                                                              | 10.5 | 10.8 | 11.0 | V     |

| Charge Pumped 12VG Voltage                                                  | V12VG                  | C <sub>PUMP</sub> = 0.1μF                                    | 16.8 | 17.3 | 17.9 | V     |

| 3.3V CONTROL                                                                |                        |                                                              | ·    |      |      |       |

| Current Limit Threshold Voltage                                             | V <sub>IL3V</sub>      | R <sub>ILIM</sub> = 10kΩ                                     | 92   | 100  | 108  | mV    |

| (Voltage Across Sense Resistor)                                             |                        | R <sub>ILIM</sub> = 5kΩ                                      | 47   | 53   | 59   | mV    |

| 3x Current Limit Threshold Voltage                                          | 3 x V <sub>IL3V</sub>  | R <sub>ILIM</sub> = 10kΩ                                     | 250  | 300  | 350  | mV    |

| (Voltage Across Sense Resistor)                                             |                        | R <sub>ILIM</sub> = 5kΩ                                      | 100  | 155  | 210  | mV    |

| ±20% Current Limit Response Time<br>(Current within 20% of Regulated Value) |                        | 200% Current Overload, $R_{ILIM}$ = 10kΩ, $R_{SHORT}$ = 2.5Ω | -    | 2    | -    | μs    |

| ±10% Current Limit Response Time<br>(Current within 10% of Regulated Value) |                        | 200% Current Overload, $R_{ILIM}$ = 10kΩ, $R_{SHORT}$ = 2.5Ω | -    | 4    | -    | μs    |

**Electrical Specifications**  $V_{DD} = 12V$ ,  $C_{VG} = 0.01\mu$ F,  $C_{TIM} = 0.1\mu$ F,  $R_{SENSE} = 0.1\Omega$ ,  $C_{BULK} = 220\mu$ F, ESR = 0.5W,  $T_A = T_J = -40$  °C to +85 °C, unless otherwise specified. Parameters with MIN and/or MAX limits are 100% tested at +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested. **(Continued)**

| PARAMETER                                                                 | SYMBOL                 | TEST CONDITIONS                                              | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------------|------------------------|--------------------------------------------------------------|------|------|------|-------|

| ±1% Current Limit Response Time<br>(Current within 1% of Regulated Value) |                        | 200% Current Overload, $R_{ILIM}$ = 10kΩ, $R_{SHORT}$ = 2.5Ω | -    | 10   | -    | μs    |

| Response Time To Dead Short                                               | RT <sub>SHORT</sub>    | C <sub>VG</sub> = 0.01μF                                     | -    | 500  |      | ns    |

| Gate Turn-On Time                                                         | t <sub>ON3V</sub>      | C <sub>VG</sub> = 0.01μF                                     | -    | 5    | -    | ms    |

| Gate Turn-On Current                                                      | I <sub>ON3V</sub>      | C <sub>VG</sub> = 0.01μF                                     | 8    | 10   | 12   | μΑ    |

| 3x Gate Discharge Current                                                 | 3xdisl                 | C <sub>VG</sub> = 0.01μF, ENABLE = Low                       |      | 0.75 | -    | Α     |

| 3.3V Undervoltage Threshold                                               | 3.3V <sub>VUV</sub>    |                                                              | 2.7  | 2.85 | 3.0  | V     |

| 3.3VG High Voltage                                                        | 3VG                    |                                                              | 11.2 | 11.9 | -    | V     |

| SUPPLY CURRENT AND IO SPECIFICATIONS                                      | 3                      |                                                              |      | 1    |      |       |

| V <sub>DD</sub> Supply Current                                            | I <sub>VDD</sub>       |                                                              | 4    | 8    | 10   | mA    |

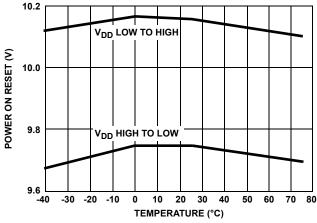

| V <sub>DD</sub> POR Rising Threshold                                      |                        |                                                              | 9.5  | 10.0 | 10.7 | V     |

| V <sub>DD</sub> POR Falling Threshold                                     |                        |                                                              | 9.0  | 9.4  | 9.8  | ٧     |

| Current Limit Timeout                                                     | t <sub>ILIM</sub>      | C <sub>TIM</sub> = 0.1μF                                     | -    | 20   | -    | ms    |

| ENABLE Pull-Up Voltage                                                    | PWRN_V                 | ENABLE Pin Open                                              | 1.8  | 2.4  | 3.2  | ٧     |

| ENABLE Rising Threshold                                                   | PWR_Vth                |                                                              | 1.1  | 1.5  | 2    | V     |

| ENABLE Hysteresis                                                         | PWR_hys                |                                                              | 0.1  | 0.2  | 0.3  | V     |

| ENABLE Pull-Up Current                                                    | PWRN_I                 |                                                              | 60   | 80   | 100  | μΑ    |

| Current Limit Timeout Threshold (C <sub>TIM</sub> )                       | C <sub>TIM</sub> _Vth  |                                                              | 1.8  | 2    | 2.2  | ٧     |

| C <sub>TIM</sub> Charging Current                                         | C <sub>TIM</sub> _I    |                                                              | 8    | 10   | 12   | μΑ    |

| C <sub>TIM</sub> Discharge Current                                        | C <sub>TIM</sub> _disl |                                                              | 1.7  | 2.6  | 3.5  | mA    |

| C <sub>TIM</sub> Pull-Up Current                                          | C <sub>TIM</sub> _disl | V <sub>CTIM</sub> = 8V                                       | 3.5  | 5    | 6.5  | mA    |

| R <sub>ILIM</sub> Pin Current Source Output                               | R <sub>ILIM</sub> _Io  |                                                              | 90   | 100  | 110  | μΑ    |

| Charge Pump Output Current                                                | Qpmp_lo                | C <sub>PUMP</sub> = 0.1μF, C <sub>PUMP</sub> = 16V           | 320  | 560  | 900  | μΑ    |

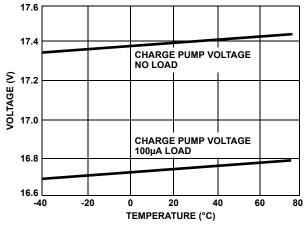

| Charge Pump Output Voltage                                                | Qpmp_Vo                | No Load                                                      | 17.2 | 17.4 | -    | V     |

| Charge Pump Output Voltage - Loaded                                       | Qpmp_Vlo               | Load Current = 100µA                                         | 16.2 | 16.7 | -    | ٧     |

| Charge Pump POR Rising Threshold                                          | Qpmp + Vth             |                                                              | 15.6 | 16   | 16.5 | ٧     |

| Charge Pump POR Falling Threshold                                         | Qpmp - Vth             |                                                              | 15.2 | 15.7 | 16.2 | V     |

# ISL6161 Description and Operation

The ISL6161 is a multi-featured +12V and +3.3V dual power supply distribution controller. Its features include programmable Current Regulation (CR) limiting and time to latch off.

At turn-on, the gate capacitor of each external N-channel MOSFET is charged with a  $10\mu\text{A}$  current source. These capacitors create a programmable ramp (soft turn-on). A charge pump supplies the gate drive for the 12V supply control FET switch, driving that gate to 17V.

The load currents pass through two external current sense resistors. When the voltage across either resistor quickly exceeds the user programmed Current Regulation Voltage Threshold (CRVth) level, the controller enters current regulation. The CRVth is set by the external resistor value on the R<sub>ILIM</sub> pin. At this time, the timeout

capacitor,  $C_{TIM}$ , starts charging with a  $10\mu A$  current source and the controller enters the timeout period. The timeout period length is set by the single external capacitor (see <u>Table 1 on page 7</u>) placed from the  $C_{TIM}$  pin (Pin 10) to ground and is characterized by a lowered gate drive voltage to the appropriate external N-channel MOSFET. When  $C_{TIM}$  charges to 2V, an internal comparator is tripped, and both N-channel MOSFETs are latched off. If the voltage across the sense resistors rises slowly in response to an OC condition, CR mode is entered at ~95% of the programmed CR level. This is due to the necessary hysteresis and response time in the CR control circuitry.

TABLE 1. C<sub>TIM</sub> RECOMMENDATIONS

| C <sub>TIM</sub> CAPACITOR<br>(μF) | NOMINAL TIME-OUT PERIOD (ms) |

|------------------------------------|------------------------------|

| 0.022                              | 4.4                          |

| 0.047                              | 9.4                          |

| 0.1                                | 20                           |

#### NOTE:

6. Nominal time-out period in seconds =  $C_{TIM} \times 200 \text{k}\Omega$ .

Table 2 shows R<sub>SENSE</sub> and R<sub>ILIM</sub> recommendations and the resulting CR level for the specified PCle add-in card connector sizes. First select an R<sub>ILIM</sub> value for the appropriate CRVth, then choose the R<sub>SENSE</sub> value for the desired OC trip. Other applications can select either 4.99kΩ or 10kΩ for R<sub>ILIM</sub>; the accuracy of the CRVth is measured for both. Values below 4.99kΩ are not recommended due to possible noise sensitivity. Values between 4.99kΩ and 10kΩ can be used, but are not measured for accuracy.

TABLE 2. R<sub>SENSE</sub> AND R<sub>ILIM</sub> RECOMMENDATIONS

| PCIe<br>ADD-IN CARD<br>CONNECTOR | R <sub>ILIM</sub> (kΩ) | 3.3V R <sub>SENSE</sub> (mΩ),<br>NOMINAL CR (A) | 12V R <sub>SENSE</sub><br>(mΩ),<br>NOMINAL CR<br>(A) | NOMINAL<br>CRVth<br>(mV) |

|----------------------------------|------------------------|-------------------------------------------------|------------------------------------------------------|--------------------------|

| X1                               | 10                     | 30, 3.3                                         | 150, 0.7                                             | 100                      |

|                                  | 4.99                   | 15, 3.5                                         | 90, 0.6                                              | 53                       |

| X4/X8                            | 10                     | 30, 3.3                                         | 40, 2.5                                              | 100                      |

|                                  | 4.99                   | 15, 3.5                                         | 20, 2.6                                              | 53                       |

| X16                              | 10                     | 30, 3.3                                         | 16, 6.3                                              | 100                      |

|                                  | 4.99                   | 15, 3.5                                         | 8, 6.6                                               | 53                       |

#### NOTE:

7. Nominal CR Vth =  $R_{ILIM} \times 10\mu A = OC \times R_{SENSE}$

The ISL6161 responds to a load short (defined as a current level three times the OC set point with a fast transition) by immediately driving the relevant N-channel MOSFET gate to OV in ~3  $\mu$ s. The gate voltage is then slowly ramped up, soft-starting the N-channel MOSFET to the programmed current regulation limit level. This is the start of the timeout period if the abnormal load condition still exists. The programmed current regulation level is held until either the OC event ends or the timeout period expires. If the OC event ends, the N-channel MOSFET is fully enhanced and the  $C_{TIM}$  charging current is diverted away from the capacitor. If the timeout period expires before the OC event ends, then both gates are quickly pulled to OV, turning off both N-Channel MOSFETs simultaneously.

Upon any UV condition, the PGOOD signal will pull low when tied high through a resistor to the logic supply. This pin is a fault indicator, but is not the OC latch-off indicator. For an OC latch-off indication, monitor  $C_{TIM}$  (Pin 10). This pin will rise rapidly to 12V when the timeout period expires. See Figure 2 on page 2 for an OC latch-off circuit suggestion.

The ISL6161 is reset by a rising edge on the  $\overline{\text{ENABLE}}$  pin and is turned on by the  $\overline{\text{ENABLE}}$  pin being driven low.

# **Application Considerations**

In a non PCIe, motor drive application, **current loop stabilization** is facilitated through a small value resistor in series with the gate timing capacitor. As the ISL6161 drives a highly inductive current load, instability characterized by the gate voltage repeatedly ramping up and down may occur. Stability can be easily enhanced by substituting a larger gate resistor. Improve stability by eliminating long point-to-point wiring to the load.

The ENABLE internal pull-up makes the ISL6161 well suited for implementation on either side of the connector in which a motherboard prebiased condition or a load board staggered connection is present. In either case, the ISL6161 turns on in Soft-Start mode, protecting the supply rail from sudden current loading.

During the **timeout delay period** with the ISL6161 in current limit mode, the  $V_{GS}$  of the external N-channel MOSFETs is reduced, driving the N-channel MOSFET switch into a high  $r_{DS(ON)}$  state. Thus, avoid extended timeout periods, because the external N-Channel MOSFETs may be damaged or destroyed due to excessive internal power dissipation. Refer to the MOSFET manufacturer's datasheet for SOA information.

With the high levels of inrush current (highly capacitive loads and motor start-up currents), **choosing the current regulation (CR) level** is crucial to provide both protection and still allow for this inrush current without latching off. Consider this in addition to the timeout delay when choosing MOSFETs for your design.

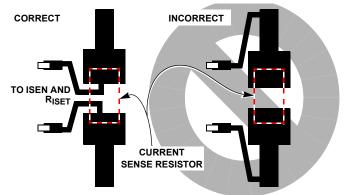

Physical layout of the R<sub>SENSE</sub> resistors is critical to avoid inadvertently lowering the CR and trip levels. Ideally, trace routing between the R<sub>SENSE</sub> resistors and the ISL6161 should be as direct and as short as possible with zero current in the sense lines.

FIGURE 3. SENSE RESISTOR PCB LAYOUT

Monitor the xISEN pins to **detect open loads**. Although gated off, the external FET  $I_{DSS}$  will cause the xISEN pins to float above ground to some voltage when no load is attached. If this is not desired, 5k resistors from the xISEN pins to ground will prevent the outputs from floating when the external switch FETs are disabled and the outputs are open.

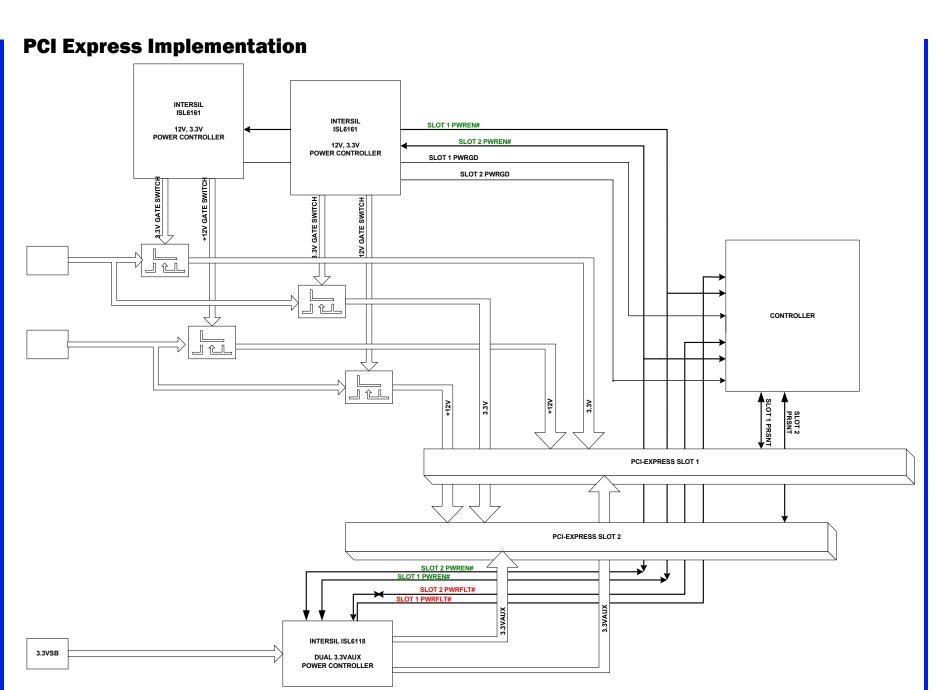

For **PCle applications**, the ISL6161 and the ISL6118 provide the fundamental hotswap function for the +12V and +3.3V main rails and the +3.3V auxiliary rails, respectively, as shown in <u>"PCl Express Implementation" on page 10</u>.

# **Typical Performance Curves**

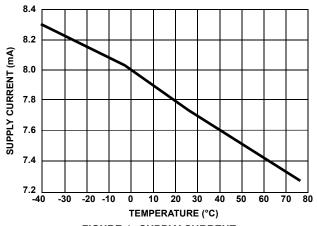

FIGURE 4. SUPPLY CURRENT

FIGURE 6. C<sub>TIM</sub> CURRENT SOURCE

FIGURE 7.  $C_{TIM}$  OC VOLTAGE THRESHOLD

2.8750 2.8725 2.8700 2.8675 2.8650 -40 -20 0 20 40 60 80 TEMPERATURE (°C)

FIGURE 9. 3.3V UV THRESHOLD

# Typical Performance Curves (Continued)

FIGURE 10. 12V, 3.3V GATE DRIVE

FIGURE 11. PUMP VOLTAGE

FIGURE 12. OC VOLTAGE THRESHOLD WITH  $R_{LIM} = 5k\Omega$

FIGURE 13. OC VOLTAGE THRESHOLD WITH  $R_{LIM}$  =  $10k\Omega$

FIGURE 14. POWER-ON RESET VOLTAGE THRESHOLD

FIGURE 15. PCI EXPRESS IMPLEMENTATION OF THE ISL6161 AND ISL6118

**Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure you have the latest revision.

| DATE             | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aug 16, 2018     | FN9104.7 | Updated Ordering information table by removing ISL6161IVZA, adding tape and reel parts, adding tape and reel unit column, and updating Note 1. Updated Disclaimer.                                                                                                                                                                                                  |

| Jan 23, 2018     | FN9104.6 | -Applied new Header/FooterAdded Related Literature section to page 1Cleaned up simplified schematic on page 2Added ISL6161IVZA Information throughout documentAdded MSL note (Note 3)Clarified R <sub>ILIM</sub> in Pin Descriptions table on page 4Fixed unit typo on page 9Added caption to figure on page 10Removed About Intersil verbiage. Updated Disclaimer. |

| December 3, 2015 | FN9104.5 | Added Rev History and About Intersil Verbiage. Updated Ordering Information on page 1. Updated POD M14.15 to most current version. Rev change is as follows: Added land pattern and moved dimensions from table onto drawing.                                                                                                                                       |

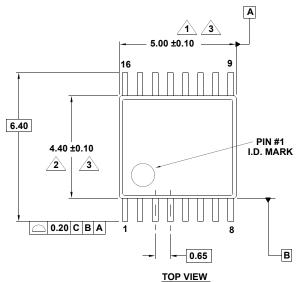

# **Package Outline Drawings**

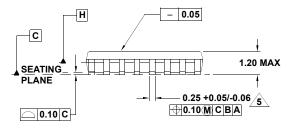

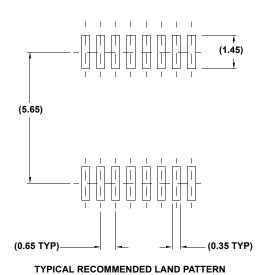

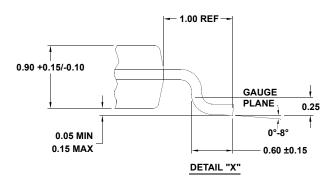

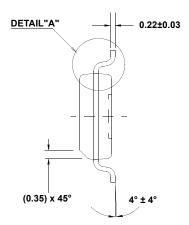

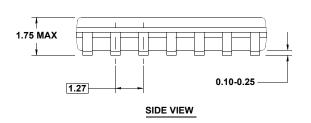

M16.173

16 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP) Rev 2, 5/10

For the most recent package outline drawing, see M16.173.

SIDE VIEW

#### NOTES:

- 1. Dimension does not include mold flash, protrusions or gate burrs.

Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

- 2. Dimension does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 per side.

- 3. Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- <u>5.</u> Dimension does not include dambar protrusion. Allowable protrusion shall be 0.08mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimension in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153.

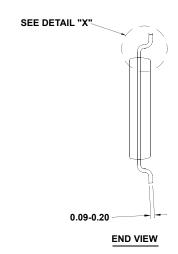

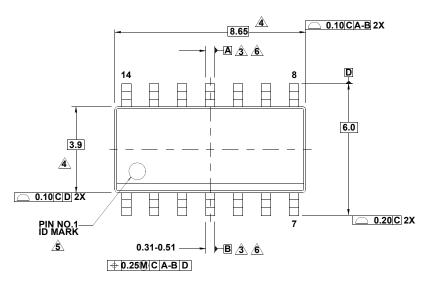

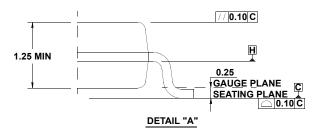

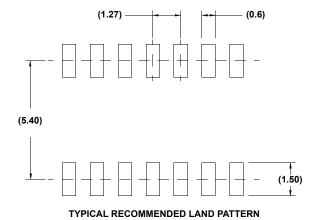

# 14 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 1, 10/09

TOP VIEW

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSEY14.5m-1994.

- 3. Datums A and B to be determined at Datum H.

- 4. Dimension does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side.

- 5. The pin #1 indentifier may be either a mold or mark feature.

- 6. Does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm total in excess of lead width at maximum condition.

- 7. Reference to JEDEC MS-012-AB.

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or

- When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

(Rev.4.0-1 November 2017)

#### **SALES OFFICES**

## Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

California Eastern Laboratories, Inc.

4590 Patrick Henry Drive, Santa Clara, Califo Tel: +1-408-919-2500, Fax: +1-408-988-0279 California 95054-1817, U.S.A.

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004

Renesas Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tel: +44-1628-651-700

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, German Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd.

80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd.

Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. I td.

No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +822-558-3737, Fax: +822-558-5538