Multi-threaded SoCs deliver high performance per watt

# QorlQ<sup>®</sup> T4240, T4160 and T4080 Multicore Processors

The QorIQ T4 family is the flagship of the QorIQ T series. Advanced 28 nm process technology, integration, new higher speed I/O, clustered memory subsystems, hardware acceleration and power management give the T4 family a very high performance profile in an embedded power envelope.

The T4240 advanced multicore processor features 12 physical and 24 virtual high performance cores scaling up to 1.8 GHz. The T4 family is joined by the T4160 (16 virtual cores) and T4080 (eight virtual cores) processors, and the family has a 3x performance scaling factor within a pin-compatible package. The T4 family features sophisticated support for hardware and software virtualization solutions.

## TARGET MARKETS AND APPLICATIONS

The T4 family is ideal for combined control and data plane processing. Like other QorlQ devices, the T4 family of processors' high level of integration offers significant space, weight and power benefits compared to multiple discrete devices.

- Service provider networking: RNC, metro networking, gateway, core/edge router, EPC, CRAN, ATCA and AMC solutions

- Enterprise equipment: Router, switch services, UTM

- Data centers: NFV, SDN, ADC, WOC, UTM, proxy, server appliance, PCI Express<sup>®</sup> (PCIe) offload

- Storage controllers: FCoE bridging, iSCSI controller, SAN controller

- Aeronautics, defense and government: Radar imaging, ruggedized network appliance, cockpit display

- Industrial computing: Single-board computers, test equipment

# FEATURES OF DISTINCTION

|                        | T4080 | T4160 | T4240  |

|------------------------|-------|-------|--------|

| Cores (Dual Threaded)  | 4     | 8     | 12     |

| L2 Cache               | 2 MB  | 4 MB  | 6 MB   |

| CoreNet Platform Cache | 1 MB  | 1 MB  | 1.5 MB |

| DDR Controllers        | 2     | 2     | 3      |

| SerDes Lanes           | 24    | 24    | 36     |

| Max 10 Gbit/s Ethernet | 2     | 2     | 4      |

| Max 1 Gbit/s Ethernet  | 13    | 13    | 16     |

| PCIe Controllers       | 3     | 3     | 4      |

#### **ADVANCED CORES**

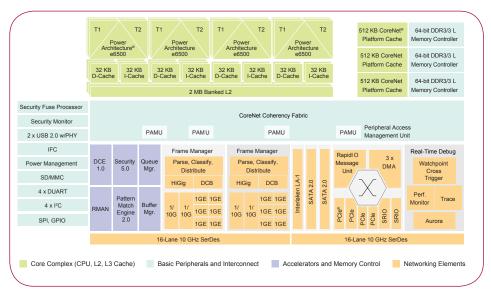

The T4 family of processors are based on the new Power Architecture® e6500 core. The e6500 uses a 64-bit sevenstage pipeline for low latency response to unpredictable code execution paths, boosting single-threaded performance. The e6500 also offers higher aggregate instructions per clock at lower power with an innovative "fused core" approach to threading. The e6500 core's fully resourced dual threads provide 1.7 times the performance of a single thread.

The e6500 cores are clustered in banks of four cores sharing a 2 MB L2 cache, allowing efficient sharing of code and data within a multicore cluster. Each e6500 core implements the AltiVec® technology SIMD engine, dramatically boosting the performance of heavy math algorithms with DSP-like performance. The e6500 core features include:

- Up to 1.8 GHz dual-threaded operation

- ▶ 7 DMIPS/MHz per core

- Advanced power saving modes, including state retention power gating

## VIRTUALIZATION

The T4 family of processors includes support for hardware-assisted virtualization. The e6500 core offers an extra core privilege level (hypervisor) and hardware offload of logical to real address translation. In addition, the T4 family of processors includes platform-level enhancements supporting I/O virtualization with DMA memory protection through IOMMUs and configurable "storage profiles" that provide isolation of I/O buffers between guest environments. Virtualization software for the T4 family includes kernel virtualization machine (KVM), Linux® containers, hypervisor and commercial virtualization software from Enea®, Green Hills Software®, Mentor Graphics® and Wind River.

#### **QorlQ T4240 PROCESSOR BLOCK DIAGRAM**

# DATA PATH ACCELERATION ARCHITECTURE (DPAA)

The T4 family of processors enhances the QorlQ DPAA, an innovative multicore infrastructure for scheduling work to cores (physical and virtual), hardware accelerators and network interfaces. The FMAN, a primary element of the DPAA, parses headers from incoming packets and classifies and selects data buffers with optional policing and congestion management. The FMAN passes its work to the QMAN, which assigns it to cores or accelerators with a multilevel scheduling hierarchy. The T4240 processor's implementation of the DPAA offers accelerators for cryptography, enhanced regular expression pattern matching and compression/decompression.

# SYSTEM PERIPHERALS AND NETWORKING

For networking, there are dual FMANs with an aggregate of up to 16 any-speed MAC controllers that connect to PHYs, switches and backplanes over RGMII, SGMII, QSGMII, HiGig2, XAUI, XFI and 10Gbase-KR. The FMAN also supports new quality-of-service features through egress traffic shaping and priority flow control for data center bridging in converged data center networking applications. High-speed system expansion is supported through four PCI Express controllers that support varieties of lane lengths for PCIe specification 3.0, including endpoint SR-IOV with 128 virtual functions. Other peripheral interfaces include SRIO, Interlaken-LA, SATA, SD/MMC, I<sup>2</sup>C, UART, SPI, a NOR/ NAND controller, GPIO and a 1866 MT/s DDR3L controller.

## DPAA HARDWARE ACCELERATORS

| Frame Manager (FMAN)          | 50 Gbit/s classify, parse and distribute    |

|-------------------------------|---------------------------------------------|

| Buffer Manager (BMAN)         | 64 buffer pools                             |

| Queue Manager (QMAN)          | Up to 2 <sup>24</sup> queues                |

| RapidIO Manager (RMAN)        | Seamless mapping to DPAA                    |

| Security (SEC)                | 40 Gbit/s: 3 DES, AES; 20 Gbit/s: Kasumi/F8 |

| Pattern Matching Engine (PME) | 10 Gbit/s                                   |

| Data Compression Engine (DCE) | 20 Gbit/s aggregate                         |

### SOFTWARE AND TOOL SUPPORT

- Enea®: Real-time operating system support and virtualization software

- Green Hills<sup>®</sup>: Comprehensive portfolio of software and hardware development tools, trace tools, RTOS and virtualization software

- Mentor Graphics<sup>®</sup>: Commercial-grade Linux<sup>®</sup> solution and Vista simulation model which allows for a TLM2 simulation environment, software development and power estimation

- The Mentor Embedded Performance Library is a high-performance computing library of advanced math and signal-processing functions for AltiVec technology

- ➤ Wind River: Development tools, RTOS, Linux OS and virtualization software

## **QorlQ T4240 COMMUNICATIONS PROCESSOR FEATURES LIST**

| Dual-threaded<br>e6500 Cores Built on<br>Power Architecture®<br>Technology   | <ul> <li>Arranged in clusters of four e6500s sharing a 2 MB L2 cache</li> <li>12 dual-threaded cores on T4240, 8 on T4160, and 4 on T4080</li> <li>Up to 1.8 GHz with 64-bit ISA support (Power Architecture v2.06-compliant)</li> <li>AltiVec<sup>®</sup> technology SIMD engine</li> <li>User, supervisor and hypervisor instruction levels</li> </ul>                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CoreNet Platform<br>Cache                                                    | • 1.5 MB configured as triple 512 KB blocks (1 MB on T4160 and T4080 processors)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Hierarchical<br>Interconnect Fabric                                          | <ul> <li>CoreNet<sup>®</sup> fabric supporting coherent and non-coherent transactions with prioritization and bandwidth allocation amongst CoreNet endpoints</li> <li>1.6 Tb/s coherent read bandwidth</li> <li>QMAN fabric supporting packet-level queue management and quality of service scheduling</li> </ul>                                                                                                                                                                                                                                                            |

| 64-bit DDR3/3L<br>SDRAM Memory<br>Controllers                                | <ul> <li>Up to 1866 MT/s</li> <li>Three controllers on T4240 processor (two on T4160 and T4080 processors)</li> <li>ECC and interleaving support</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DPAA Incorporates<br>Acceleration for the<br>Following Functions             | <ul> <li>Packet parsing, classification and distribution (FMAN 1.1)</li> <li>Queue management for scheduling, packet sequencing and congestion management (QMAN 1.1)</li> <li>Hardware buffer management for buffer allocation and de-allocation (BMAN 1.1)</li> <li>Cryptography acceleration (SEC 5.0) at up to 40 Gbit/s</li> <li>RegEx pattern matching acceleration (PME 2.0) at up to 10 Gbit/s</li> <li>Decompression/compression acceleration (DCE 1.0) at up to 20 Gbit/s</li> <li>DPAA chip-to-chip interconnect via RapidIO message manager (RMAN 1.0)</li> </ul> |

| SerDes                                                                       | <ul> <li>32 lanes total at up to 10 GHz (24 lanes on T4160 and T4080 processors)</li> <li>Supports SGMII, QSGMII, HiGig, XAUI, XFI, 10Gbase-KR, PCIe rev 1.1/2.0/3.0,<br/>Interlaken-LA, sRIO</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |

| Ethernet Interfaces                                                          | <ul> <li>Up to four 10 GE Ethernet MACs (two on T4160 and T4080 processors)</li> <li>Up to 16 1 GE Ethernet MACs (13 on T4160 and T4080 processors)</li> <li>Maximum configuration of 4 x 10 GE + 12 x 1 GE (2 x 10 GE + 10 x 1GE on T4160 and T4080 processors)</li> </ul>                                                                                                                                                                                                                                                                                                  |

| High-Speed<br>Peripheral Interfaces                                          | <ul> <li>Four PCI Express 2.0/3.0 controllers (three on T4160 and T4080 processors)</li> <li>Endpoint SR-IOV with 2 PFs (Physical Functions) and 128 VFs (Virtual Functions)</li> <li>Two serial RapidIO 2.0 controllers/ports running at up to 5 GHz with Type 11 messaging and Type 9 data streaming support</li> <li>Interlaken look-aside interface for serial TCAM connection</li> </ul>                                                                                                                                                                                |

| Additional Peripheral<br>Interfaces                                          | <ul> <li>Two serial ATA (SATA 2.0) controllers</li> <li>Two High-Speed USB 2.0 controllers with integrated PHY</li> <li>Enhanced secure digital host controller (SD/MMC/eMMC)</li> <li>Enhanced serial peripheral interface</li> <li>Four I<sup>2</sup>C controllers</li> <li>Four UARTs</li> <li>Integrated flash controller supporting NAND and NOR flash</li> </ul>                                                                                                                                                                                                       |

| DMA                                                                          | Three eight-channel DMA controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Support for<br>Hardware<br>Virtualization<br>and Partitioning<br>Enforcement | <ul> <li>Extra privilege level for hypervisor support</li> <li>Logical to real address translation</li> <li>Virtual core aware MMU/TLB</li> <li>vMPIC (virtualized interrupt controller)/virtual core capable PPC cores</li> <li>vDMA (user-level DMA engine)</li> <li>PAMUv2 (I/O MMU supporting paging)</li> <li>DPAA (Ethernet MAC virtualization, accelerator virtualization)</li> </ul>                                                                                                                                                                                 |

| QorlQ Trust<br>Architecture 2.0                                              | <ul> <li>Secure boot, secure debug, tamper detection, volatile key storage, alternate<br/>image and key revocation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## www.nxp.com/QorlQ

NXP, the NXP logo, AltiVec and QorIQ are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2016 NXP B.V.