# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

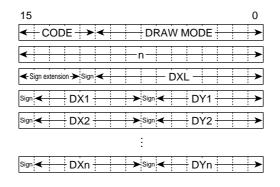

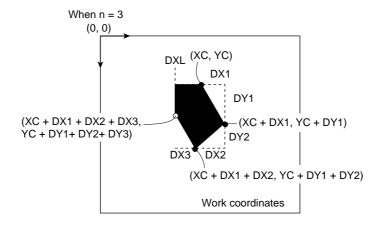

#### Cautions

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# SuperH<sup>™</sup> RISC engine Peripheral LSI

# HD64413A Q2SD

# Quick 2D Graphics Renderer with Synchronous DRAM Interface

User's Manual

# RENESAS

ADE-602-204A

Rev. 2.0 09/24/02 Hitachi, Ltd.

# Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# **General Precautions on Handling of Product**

- 1. Treatment of NC Pins

- Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

- 2. Treatment of Unused Input Pins

- Note: Fix all unused input pins to high or low level. Generally, the input pins of CMOS products are high-impedation

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

- 3. Processing before Initialization

- Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

- 4. Prohibition of Access to Undefined or Reserved Addresses

- Note: Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Pins

- Pin configuration

- Pin Arrangement

- Pin Functions

- 7. Description of UGM Architecture

- 8. Description of Display List

The configuration of the functional description of each command differs according to the command. However, the generic style includes the following items:

- i) Function

- ii) Command Format

- iii) Command Description

- iv) Example

- 9. Descriptions of Registers

- List of Registers

- Descriptions of Registers

# 10. Usage Notes

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given.

- 11. Electrical Characteristics

- 12. Appendix

# Preface

The Q2SD (Quick 2D Graphics Renderer with Synchronous DRAM Interface) is a 2D graphics renderer that supports SDRAM interface in the SH microcomputer graphics accelerator "Quick" series (Q Series), based on the concepts of simplicity, realtime operation, and upgradability.

The Q2SD is a high-performance graphics rendering LSI for multimedia applications, which provides both drawing and display, video input functions integrated into a single chip.

- Target Users: This manual was written for users who will be using the Q2SD Series in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

- Objective: This manual was written to explain the hardware functions and electrical characteristics of the Q2SD Series to the target users. In this revised version, descriptions of the video input function, the list of related manuals, and points to have gotten questions from customers are reviewed.

Notes on reading this manual:

Read the manual according to the contents. This manual can be roughly categorized into parts on overview, descriptions of the UGM architecture, display list, and registers, and usage notes. These are arranged in that order. Rules: Number notation: Binary is B'xxxx, hexadecimal is H'xxxx. Signal notation: An overbar is added to a low-active signal: xxxx

Related Manuals: The latest versions of all related manuals are available from our web site. Please ensure you have the latest versions of all documents you require. http://www.hitachisemiconductor.com/

Q2SD Series manuals:

| Manual Title                          | ADE No.     |  |

|---------------------------------------|-------------|--|

| Q2SD Series Hardware Manual           | This manual |  |

|                                       |             |  |

| Application notes:                    |             |  |

| Manual Title                          | ADE No.     |  |

| HD64413A Q2SD Application Notes/Q & A | ADE-502-070 |  |

# Contents

| Secti | on 1   | Overview                                           | 1    |

|-------|--------|----------------------------------------------------|------|

| 1.1   | Featu  | 'es                                                | .2   |

| 1.2   | A List | of Specifications                                  | .9   |

| 1.3   | Block  | Diagram                                            | . 10 |

| 1.4   |        | ssing States                                       |      |

|       | 1.4.1  | Power On                                           | . 13 |

|       | 1.4.2  | Initial States (when Specified Power is Supplied)  | . 13 |

|       | 1.4.3  | Reset State (when Low Level is Input to RESET Pin) | .14  |

|       | 1.4.4  | UGM Initialization State                           | .14  |

|       | 1.4.5  | Normal Operating State                             | . 14 |

| Secti | on 2   | Pins                                               | 15   |

| 2.1   | Pin Co | onfiguration                                       | . 15 |

| 2.2   |        | rrangement                                         |      |

| 2.3   |        | inctions                                           |      |

| 2.4   | Syster | n Control Pins                                     | . 23 |

|       | 2.4.1  | Operating Mode Pins                                |      |

|       | 2.4.2  | Clock Pins                                         |      |

|       | 2.4.3  | Reset Pin                                          | .25  |

|       | 2.4.4  | Power Supply Pin                                   | .25  |

| 2.5   | CPU I  | nterface Pins                                      | .26  |

|       | 2.5.1  | CPU Writes                                         | .26  |

|       | 2.5.2  | CPU Reads                                          | .26  |

|       | 2.5.3  | DMA Writes                                         | .27  |

|       | 2.5.4  | Interrupts                                         | . 28 |

| 2.6   | UGM    | Interface Pins                                     | .28  |

| 2.7   | Displa | y Interface Pins                                   | . 28 |

|       | 2.7.1  | Display Signal Output                              | . 28 |

|       | 2.7.2  | Video Encoder Interface                            | . 29 |

|       | 2.7.3  | CRT Interface                                      | . 29 |

|       | 2.7.4  | D/A Converter                                      |      |

| 2.8   | Video  | Interface Pins                                     | . 30 |

|       | 2.8.1  | Video Input Interface                              | 30   |

| Secti | on 3   | UGM Architecture                                   | 33   |

| 3.1   | Featu  | es                                                 |      |

| 3.2   |        | Access                                             |      |

|       | 3.2.1  | UGM Access Priority                                |      |

|       | 3.2.2  | UGM Access by the CPU                              |      |

|       | 3.2.3   | UGM Access by DMAC                                           | 35  |

|-------|---------|--------------------------------------------------------------|-----|

|       | 3.2.4   | UGM Access by Q2SD                                           | 35  |

|       | 3.2.5   | Register Access from the CPU                                 | 36  |

|       | 3.2.6   | Register Updating                                            | 37  |

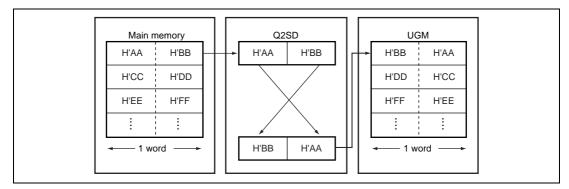

|       | 3.2.7   | Byte Exchange Function                                       | 39  |

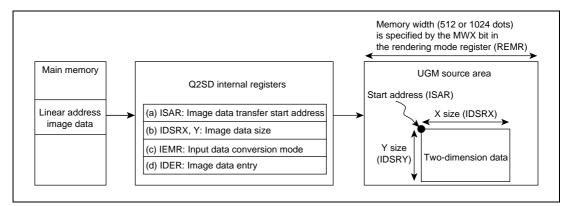

|       | 3.2.8   | 2-Dimensional Image Data Exchange Function                   | 40  |

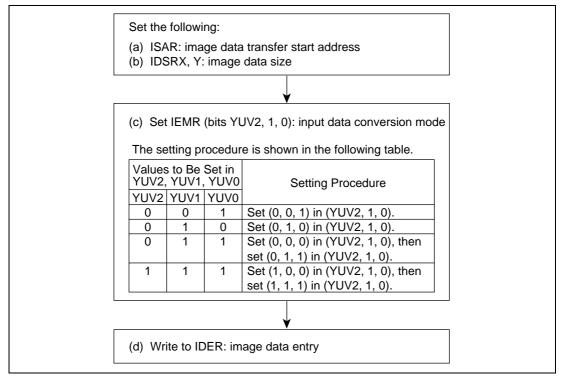

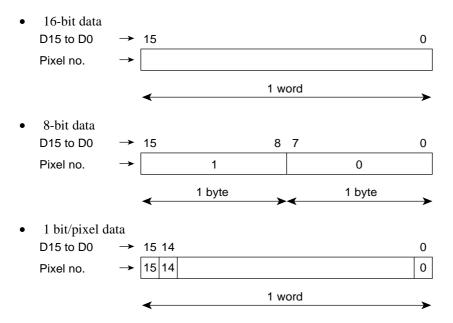

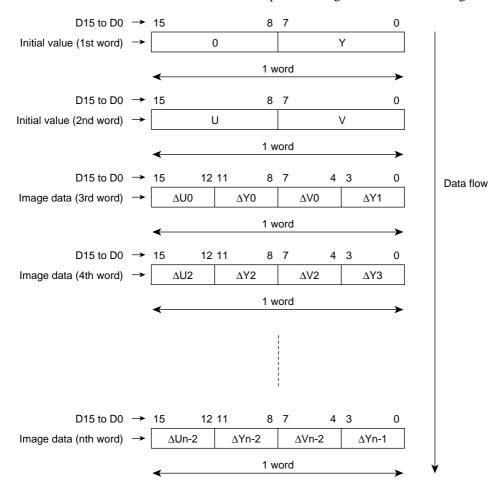

|       | 3.2.9   | Input Color Data Configurations                              | 44  |

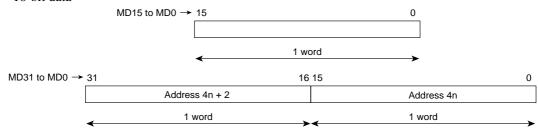

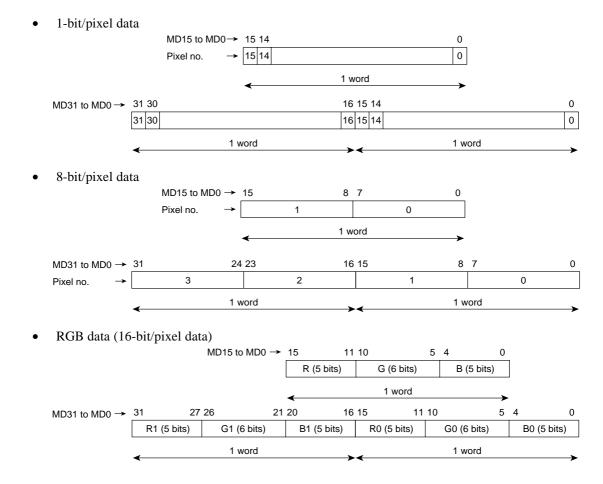

|       | 3.2.10  | Configurations of Data in UGM                                | 47  |

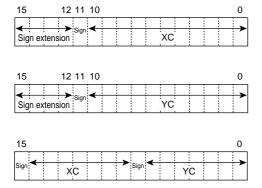

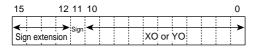

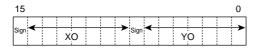

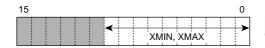

|       | 3.2.11  | Q2SD Internal Data Format                                    | 49  |

|       | 3.2.12  | Interrupt Output Function                                    | 50  |

| 3.3   | Unified | l Graphics Memory (UGM)                                      | 51  |

|       | 3.3.1   | Memory Address                                               | 51  |

|       | 3.3.2   | Memory Map                                                   | 56  |

|       | 3.3.3   | Coordinate Systems                                           | 59  |

|       | 3.3.4   | Double-Buffering Control                                     | 68  |

|       | 3.3.5   | Refresh Control                                              | 74  |

| 3.4   | Display | у                                                            | 75  |

|       | 3.4.1   | Display Functions                                            | 75  |

|       | 3.4.2   | Screen Display Composition                                   | 78  |

|       | 3.4.3   | Scanning Systems                                             | 81  |

|       | 3.4.4   | Synchronization Systems                                      | 90  |

|       | 3.4.5   | Color Expansion of Display Screen                            | 94  |

| 3.5   | Render  | ing                                                          | 96  |

|       | 3.5.1   | Commands                                                     | 96  |

|       | 3.5.2   | Image Data Reference                                         | 98  |

|       | 3.5.3   | Rendering Attributes                                         | 101 |

|       | 3.5.4   | Command Fetching                                             | 110 |

|       | 3.5.5   | Internal Buffer                                              | 113 |

| 3.6   | Video   | Capture                                                      | 114 |

|       | 3.6.1   | Configuring Circuit for Video Capture                        | 114 |

|       | 3.6.2   | Video Capture Mode                                           | 116 |

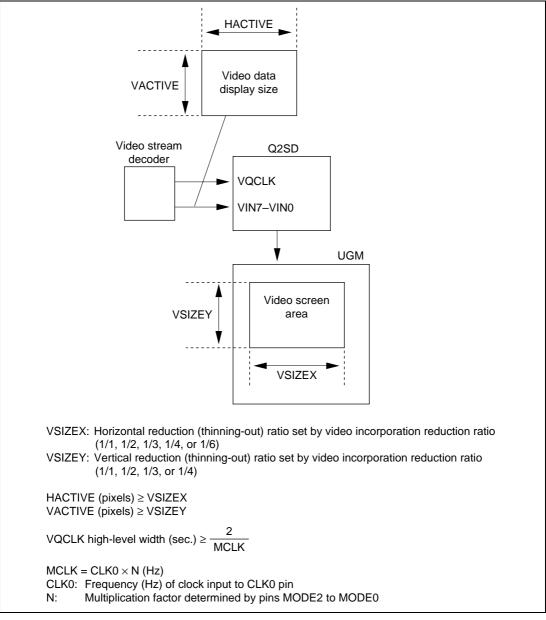

|       | 3.6.3   | Reduction of Video Capture Images                            | 122 |

|       | 3.6.4   | Setting Video Capture Position                               | 123 |

|       | 3.6.5   | Format of Captured Data                                      | 125 |

|       | 3.6.6   | YCbCr and RGB Data                                           | 127 |

| 3.7   | Video   | Display Function                                             | 128 |

|       | 3.7.1   | Video Screen Display                                         | 128 |

|       | 3.7.2   | Relationship between the Display Mode and Video-Capture Mode | 129 |

| Secti | ion 4   | Display List                                                 | 137 |

| 4.1   | Four-V  | ertex Screen Drawing                                         |     |

|       | 4.1.1   | POLYGON4A                                                    | 138 |

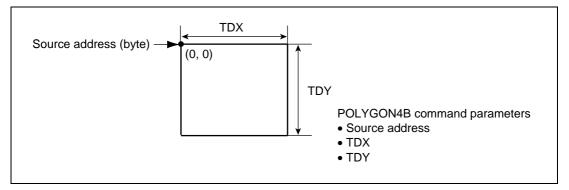

|       | 4.1.2   | POLYGON4B                                                    | 143 |

|       |         |                                                              |     |

# RENESAS

Rev. 2.0, 09/02, page vii of xviii

|       | 4.1.3    | POLYGON4C                                  | 147 |

|-------|----------|--------------------------------------------|-----|

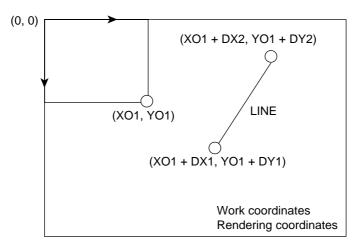

| 4.2   | Line D   | rawing                                     | 151 |

|       | 4.2.1    | LINE                                       | 151 |

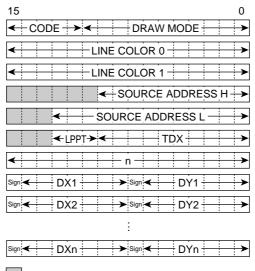

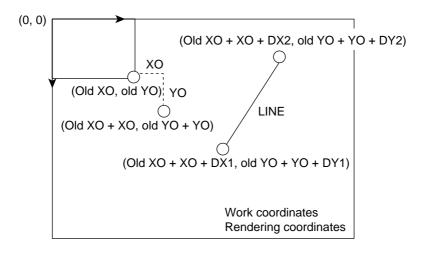

|       | 4.2.2    | RLINE                                      | 154 |

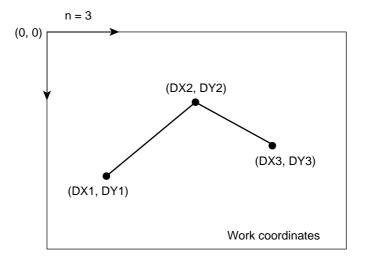

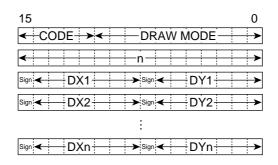

|       | 4.2.3    | PLINE                                      | 156 |

|       | 4.2.4    | RPLINE                                     | 159 |

| 4.3   | Work S   | creen Drawing Command                      | 162 |

|       | 4.3.1    | FTRAP                                      | 162 |

|       | 4.3.2    | RFTRAP                                     | 165 |

|       | 4.3.3    | CLRW                                       | 168 |

| 4.4   | Work L   | ine Drawing                                | 170 |

|       | 4.4.1    | LINEW                                      | 170 |

|       | 4.4.2    | RLINEW                                     | 173 |

| 4.5   | Registe  | r Setting Commands                         | 175 |

|       | 4.5.1    | MOVE                                       | 175 |

|       | 4.5.2    | RMOVE                                      | 177 |

|       | 4.5.3    | LCOFS                                      | 179 |

|       | 4.5.4    | RLCOFS                                     | 181 |

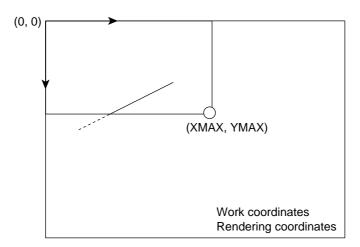

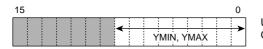

|       | 4.5.5    | SCLIP                                      | 183 |

|       | 4.5.6    | UCLIP                                      | 185 |

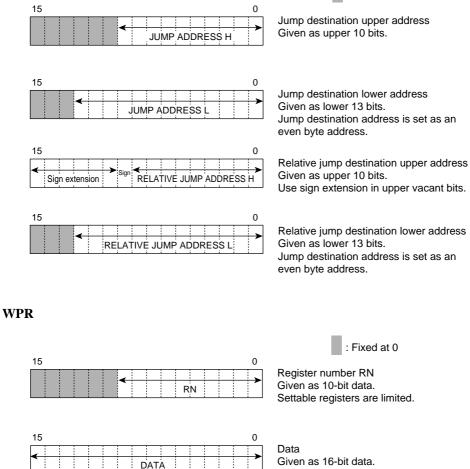

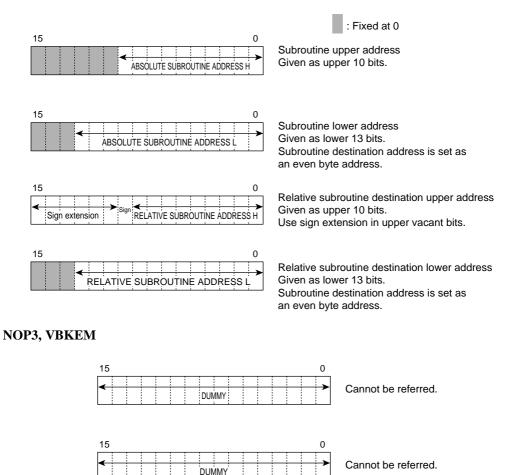

|       | 4.5.7    | WPR                                        | 187 |

| 4.6   | Sequen   | ce Control Commands                        | 189 |

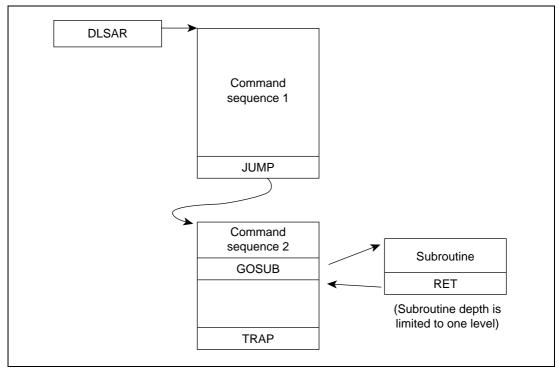

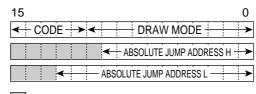

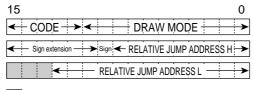

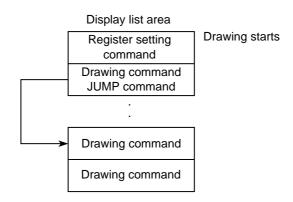

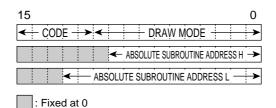

|       | 4.6.1    | JUMP                                       | 189 |

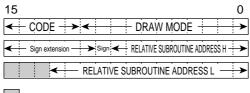

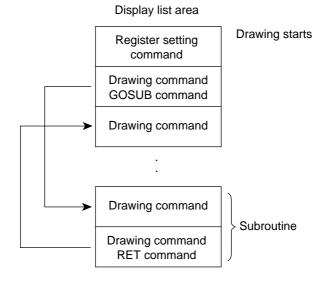

|       | 4.6.2    | GOSUB                                      | 191 |

|       | 4.6.3    | RET                                        | 194 |

|       | 4.6.4    | NOP3                                       | 195 |

|       | 4.6.5    | VBKEM                                      | 196 |

|       | 4.6.6    | TRAP                                       | 197 |

|       |          |                                            |     |

| Secti | on 5 l   | Registers                                  | 199 |

| 5.1   | Registe  | r Map                                      | 199 |

| 5.2   | Interfac | e Control Registers                        | 202 |

|       | 5.2.1    | System Control Register (SYSR)             | 203 |

|       | 5.2.2    | Status Register (SR)                       | 209 |

|       | 5.2.3    | Status Register Clear Register (SRCR)      | 213 |

|       | 5.2.4    | Interrupt Enable Register (IER)            | 214 |

|       | 5.2.5    | Memory Mode Register (MEMR)                | 216 |

|       | 5.2.6    | Display Mode Register (DSMR)               |     |

|       | 5.2.7    | Display Mode 2 Register (DSMR2)            |     |

|       | 5.2.8    | Rendering Mode Register (REMR)             | 225 |

|       | 5.2.9    | Input Data Conversion Mode Register (IEMR) |     |

|       | 5.2.10   | Video Incorporation Mode Register (VIMR)   |     |

| 5.3   | Memor    | y Control Registers                        | 234 |

|       |          |                                            |     |

|     | 5.3.1  | Display Size Registers (DSR)                           | 234 |

|-----|--------|--------------------------------------------------------|-----|

|     | 5.3.2  | Display Address Registers (DSAR)                       | 235 |

|     | 5.3.3  | Display List Start Address Registers (DLSAR)           | 236 |

|     | 5.3.4  | Multi-Valued Source Area Start Address Register (SSAR) | 237 |

|     | 5.3.5  | Work Area Start Address Register (WSAR)                | 238 |

|     | 5.3.6  | Background Start Coordinate Registers (BGSR)           | 239 |

|     | 5.3.7  | Video Area Start Address Registers (VSAR)              | 240 |

|     | 5.3.8  | Video Window Size Registers (VSIZER)                   | 242 |

|     | 5.3.9  | Cursor Area Start Address Register (CSAR)              | 243 |

|     | 5.3.10 | Rendering Start Address Register (RSAR)                | 244 |

| 5.4 | Displa | y Control Registers                                    | 244 |

|     | 5.4.1  | Display Window Registers (DSWR)                        | 245 |

|     | 5.4.2  | Horizontal Sync Pulse Width Register (HSWR)            | 247 |

|     | 5.4.3  | Horizontal Scan Cycle Register (HCR)                   | 247 |

|     | 5.4.4  | Vertical Start Position Register (VSPR)                | 247 |

|     | 5.4.5  | Vertical Scan Cycle Register (VCR)                     | 248 |

|     | 5.4.6  | Display Off Output Registers (DOOR)                    | 249 |

|     | 5.4.7  | Color Detection Registers (CDER)                       | 250 |

|     | 5.4.8  | Equalizing Pulse Width Register (EQWR)                 | 250 |

|     | 5.4.9  | Separation Width Register (SPWR)                       | 251 |

|     | 5.4.10 | Video Display Start Position Registers (VPR)           | 252 |

|     | 5.4.11 | Cursor Display Start Position Registers (CSR)          | 253 |

|     | 5.4.12 | Color Palette Registers (CP000R to CP255R)             | 255 |

| 5.5 | Render | ring Control Registers                                 | 257 |

|     | 5.5.1  | Command Status Registers (CSTR)                        | 257 |

|     | 5.5.2  | Current Pointer Registers (CURR)                       | 258 |

|     | 5.5.3  | Local Offset Registers (LCOR)                          | 259 |

|     | 5.5.4  | User Clipping Area Registers (UCLR)                    | 259 |

|     | 5.5.5  | System Clipping Area Registers (SCLR)                  | 261 |

|     | 5.5.6  | Return Address Registers (RTNR)                        | 261 |

|     | 5.5.7  | Color Offset Register (COLOR)                          | 262 |

| 5.6 | Data T | ransfer Control Registers                              | 263 |

|     | 5.6.1  | DMA Transfer Start Address Registers (DMASR)           | 263 |

|     | 5.6.2  | DMA Transfer Word Count Registers (DMAWR)              | 264 |

|     | 5.6.3  | Image Data Transfer Start Address Registers (ISAR)     | 265 |

|     | 5.6.4  | Image Data Size Registers (IDSR)                       | 266 |

|     | 5.6.5  | Image Data Entry Register (IDER)                       | 267 |

|     | ion 6  | Usage Notes                                            | 269 |

| 6.1 |        | -On Sequence                                           |     |

| 6.2 |        | 64-Mbit SDRAM (×16 Type)                               |     |

| 6.3 |        | nterface Unit FIFO                                     |     |

| 6.4 | Video  | Fetching Start Timing                                  | 272 |

Rev. 2.0, 09/02, page ix of xviii

| 6.5          | Drawin    | g Using Linear Format Source                              | 272 |

|--------------|-----------|-----------------------------------------------------------|-----|

| 6.6          | SDRAM     | M Mode Register Values for UGM Set by Q2SD                | 273 |

|              |           |                                                           |     |

| Secti        | on 7 I    | Electrical Characteristics                                | 275 |

| 7.1          | Absolu    | te Maximum Ratings                                        | 275 |

| 7.2          | Recom     | mended Operating Conditions                               | 275 |

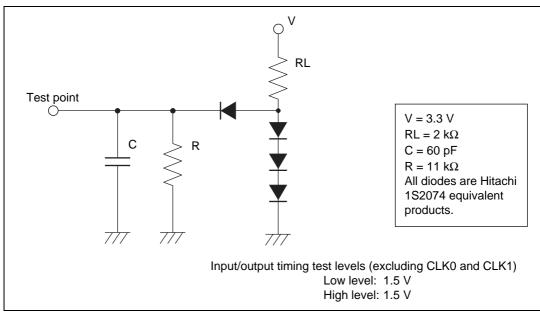

| 7.3          | Electric  | cal Characteristics Test Methods                          | 276 |

|              | 7.3.1     | Timing Testing                                            |     |

|              | 7.3.2     | Test Load Circuit (All Output and Input/Output Pins)      | 277 |

| 7.4          | Electric  | cal Characteristics                                       | 278 |

|              | 7.4.1     | DC Characteristics                                        | 278 |

|              | 7.4.2     | AC Characteristics                                        | 280 |

| 7.5          | Timing    | Charts                                                    | 288 |

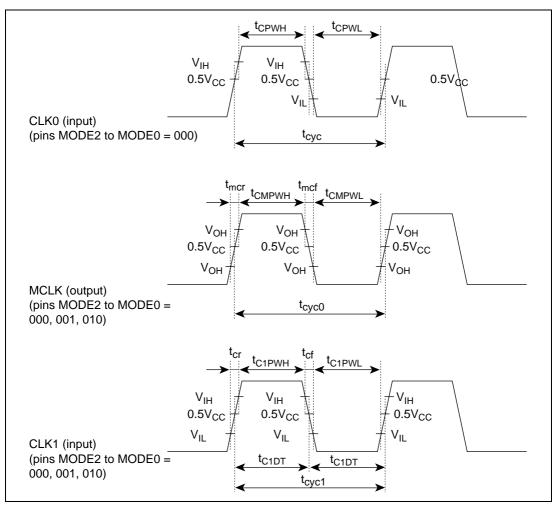

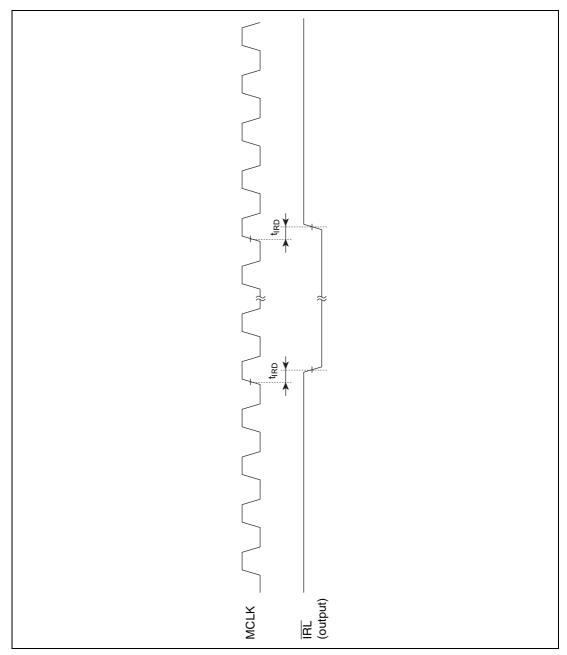

|              | 7.5.1     | Clocks                                                    | 288 |

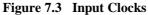

|              | 7.5.2     | Reset Timing                                              | 288 |

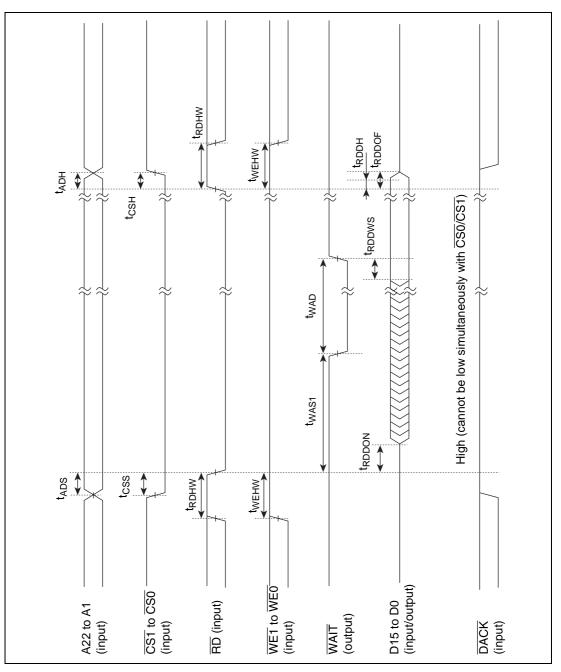

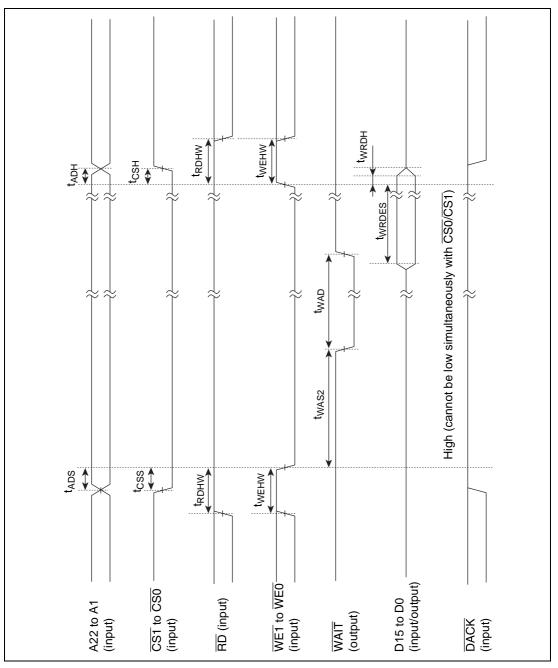

|              | 7.5.3     | CPU Read Cycle Timing                                     | 289 |

|              | 7.5.4     | CPU Write Cycle Timing                                    | 290 |

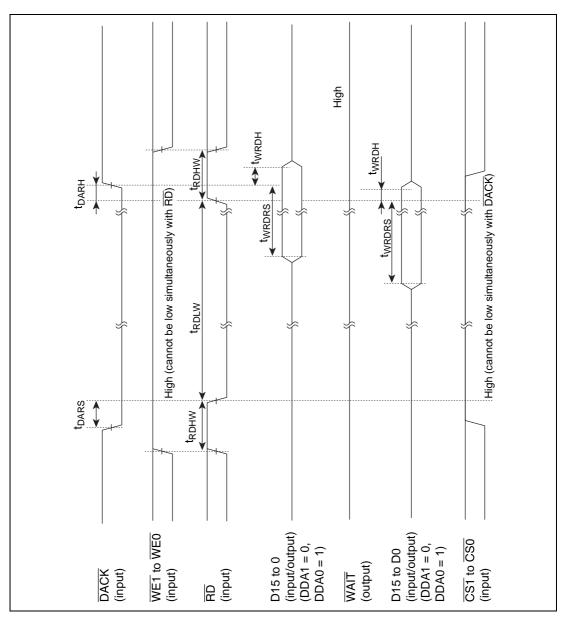

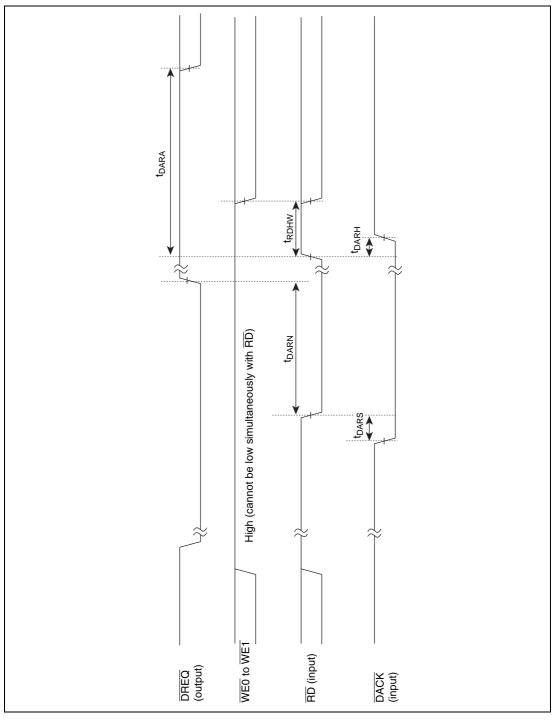

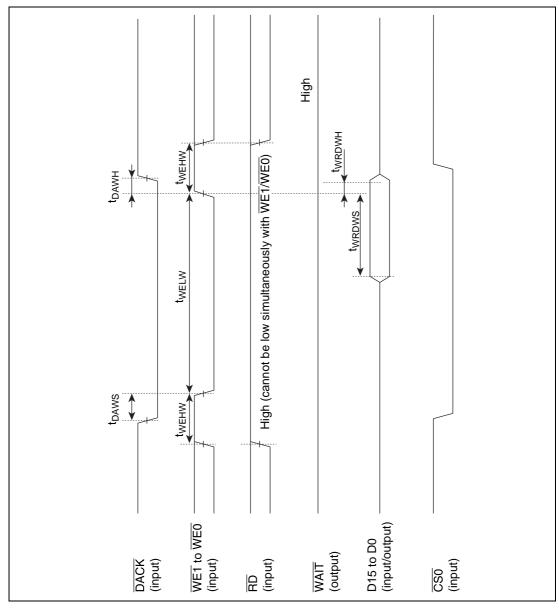

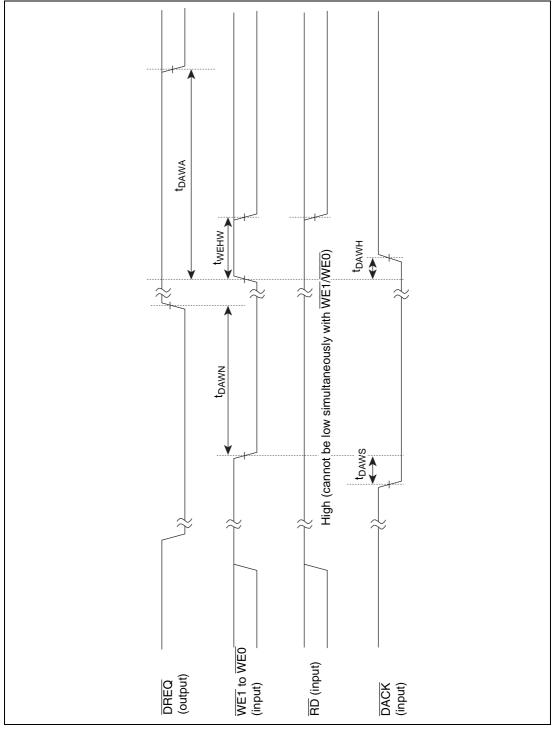

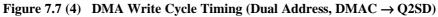

|              | 7.5.5     | DMA Write Cycle Timing (DMAC $\rightarrow$ Q2SD)          |     |

|              | 7.5.6     | Interrupt Output Timing                                   |     |

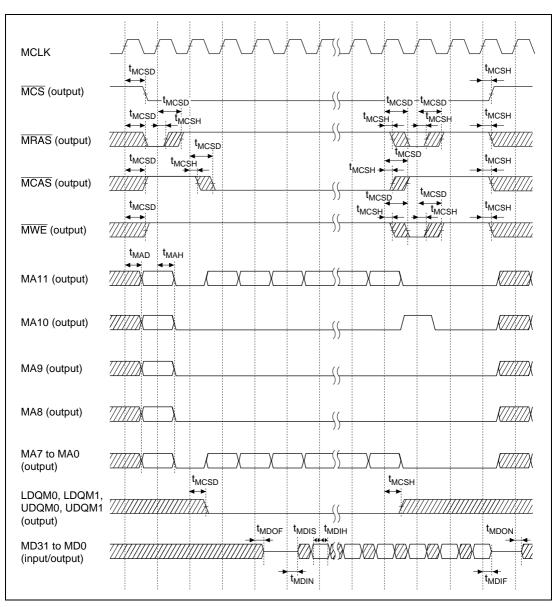

|              | 7.5.7     | UGM Read Cycle Timing                                     | 296 |

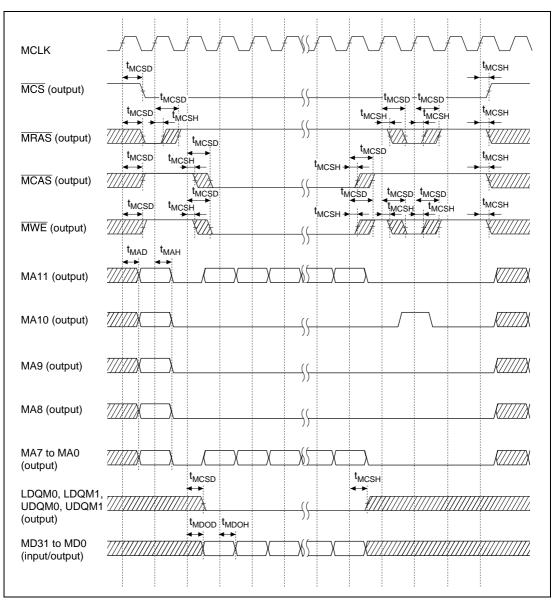

|              | 7.5.8     | UGM Write Cycle Timing                                    | 297 |

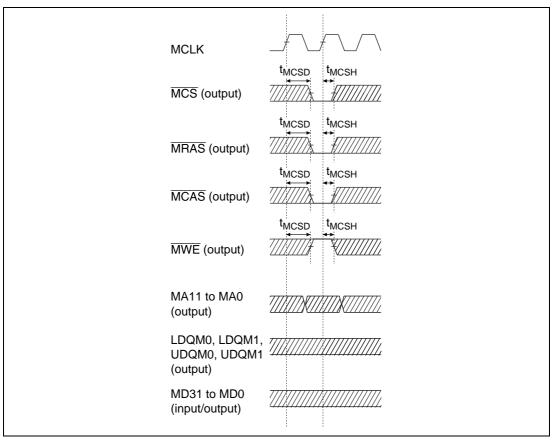

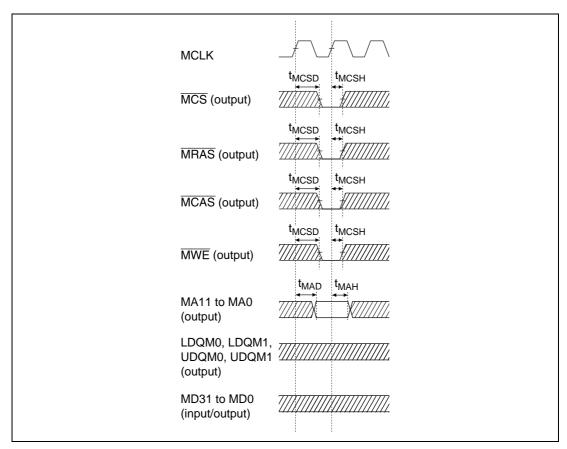

|              | 7.5.9     | UGM Refresh Cycle Timing and Mode Register Setting Timing | 298 |

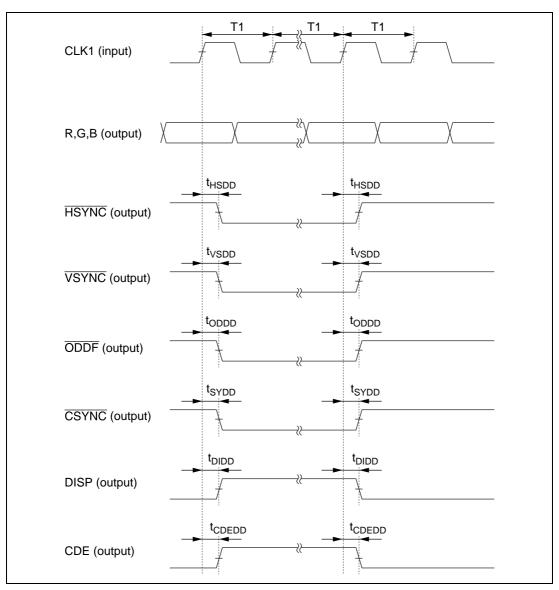

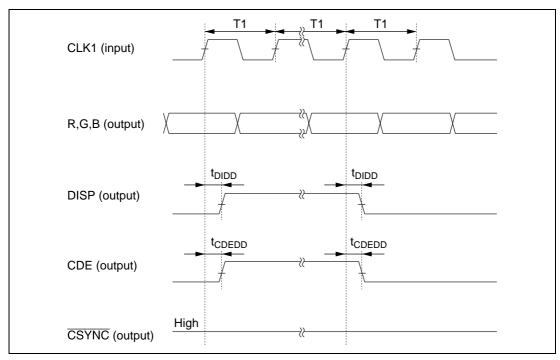

|              | 7.5.10    | Master Mode Display Timing                                |     |

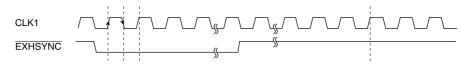

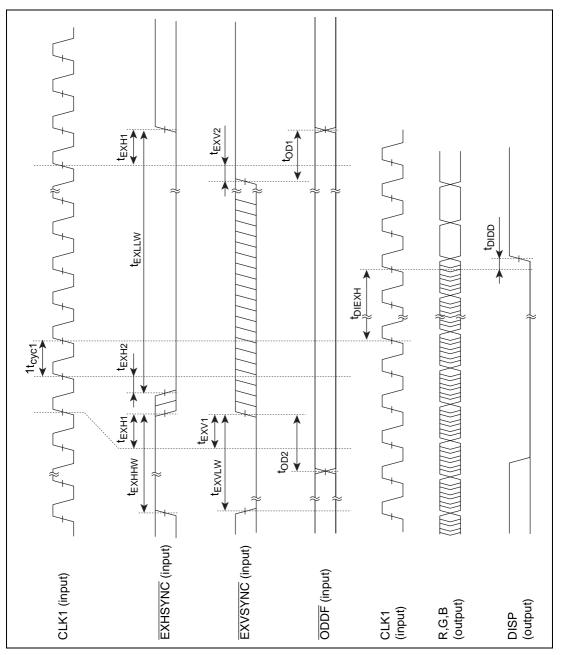

|              | 7.5.11    | TV Sync Mode Display Timing                               |     |

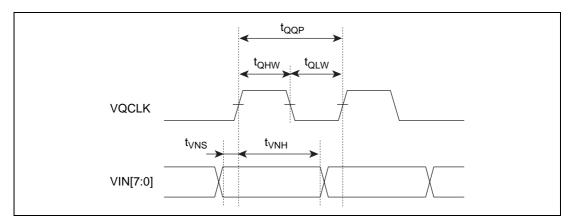

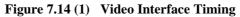

|              | 7.5.12    | Video Interface Timing                                    |     |

|              |           |                                                           |     |

| Appe         | endix A   | Initial Register Values                                   | 305 |

| 11           |           |                                                           |     |

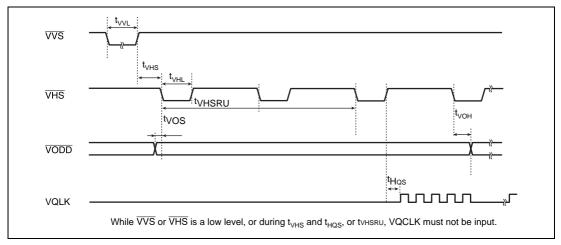

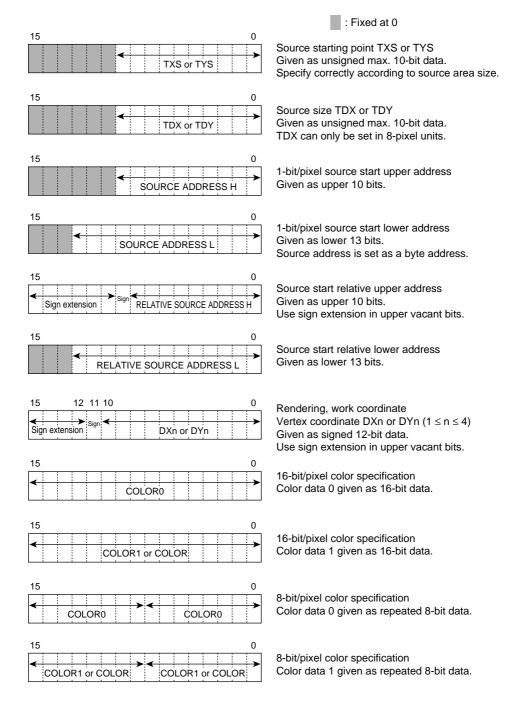

| Appe         | endix B   | Commands and Parameters                                   | 306 |

| B.1          |           | nship between Commands and Rendering Attributes           |     |

| B.2          |           | and Codes                                                 |     |

| B.3          |           | and Parameter Specifications                              |     |

|              |           |                                                           |     |

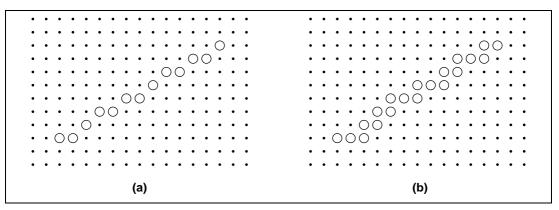

| Appe         | endix C   | Drawing Algorithms                                        | 316 |

| rr ·         |           | 8 8 9                                                     |     |

| Appe         | endix D   | Package Dimensions                                        | 319 |

| <b>r r</b> - |           |                                                           |     |

| Appe         | endix E   | Display Operating Clock and Screen Synthesis              | 320 |

|              |           |                                                           | 0_0 |

| Appe         | endix F   | Example of System Configuration for SuperH                | 325 |

| F.1          |           | ination of Clock                                          |     |

| F.2          |           | of Software Weight                                        |     |

| F.3          |           | Notes on Connection                                       |     |

|              |           |                                                           | 520 |

| Rev. 2       | 2.0, 09/0 | 2, page x of xviii                                        |     |

| F.4  | Initialization Procedures of Address-Mapped Register                | 328  |

|------|---------------------------------------------------------------------|------|

| F.5  | Memory Assignment                                                   | 329  |

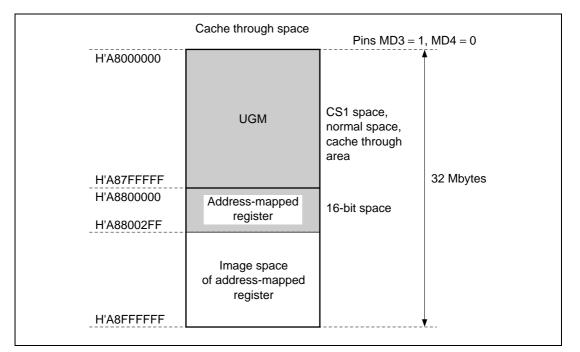

|      | F.5.1 Memory Mapping of HD64413A                                    | 329  |

|      | F.5.2 Example of Area Placement in UGM                              | 330  |

|      | F.5.3 Address Seriation in UGM                                      |      |

| F.6  | Special Notes on Data Transfer to UGM                               |      |

|      | -                                                                   |      |

| Appe | endix G Example of Display Control                                  | 334  |

| G.1  | Determination of Display Size                                       | 334  |

| G.2  | Selection of Display Screen                                         | 335  |

| G.3  | Setting of Synchronous Signal                                       | 336  |

| G.4  | Setting and Changing Register Values related to Display Control     | 340  |

|      | G.4.1 Setting of Color Palette                                      | 340  |

|      | G.4.2 Switching Procedure of Synchronous Mode                       | 340  |

| G.5  | Use of Cursor Display                                               | 340  |

|      |                                                                     |      |

| Appe | endix H Example of Drawing Control                                  | 342  |

| H.1  | Example of Starting Drawing                                         | 342  |

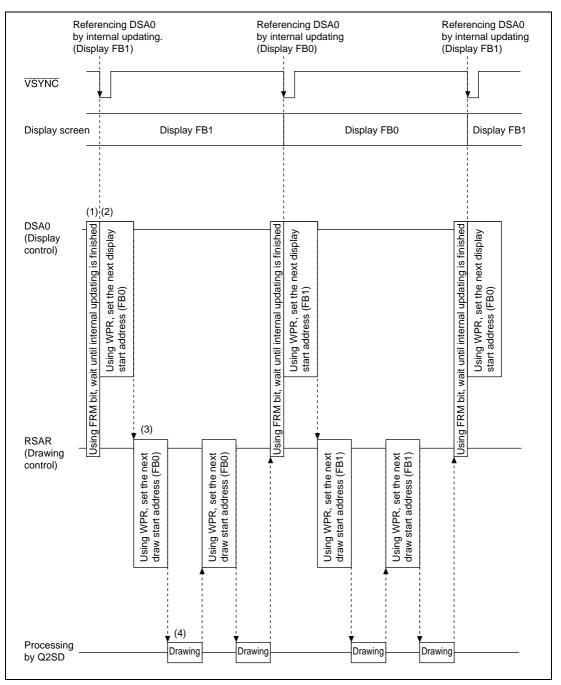

| H.2  | Example of Frame Change by Internal Updating                        | .342 |

| H.3  | Using Example of Draw Commands                                      |      |

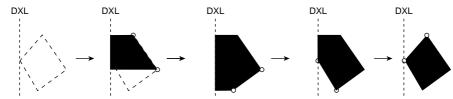

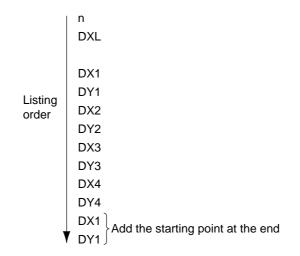

|      | H.3.1 Drawing Polygons                                              | 345  |

|      | H.3.2 Drawing Optional Shapes                                       | 345  |

|      | H.3.3 Drawing Circles and Ellipses                                  | 345  |

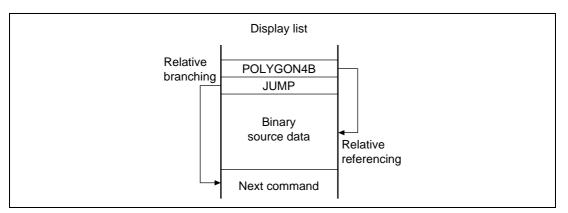

|      | H.3.4 Drawing using Source Data                                     | 345  |

|      | H.3.5 Expressing 3D Space                                           | 346  |

| H.4  | Special Notes on Using Draw Commands                                | 347  |

|      | H.4.1 Notes on the Relationship of Local Offset and Current Pointer | 347  |

|      | H.4.2 Notes on Using Relative-Series Commands                       | .347 |

|      | H.4.3 Notes on Using Source Data                                    | 348  |

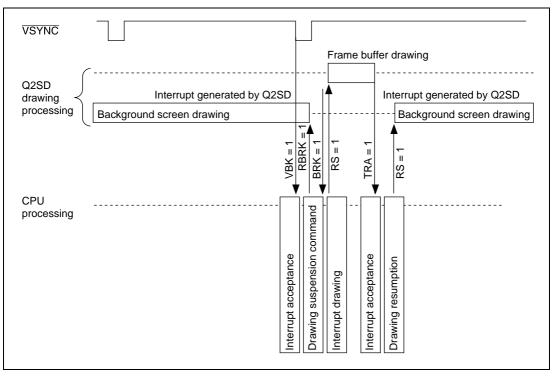

| H.5  | Functions to Support Drawing Processing                             | 349  |

|      | H.5.1 Suspension/Resumption of Drawing                              | 349  |

|      |                                                                     |      |

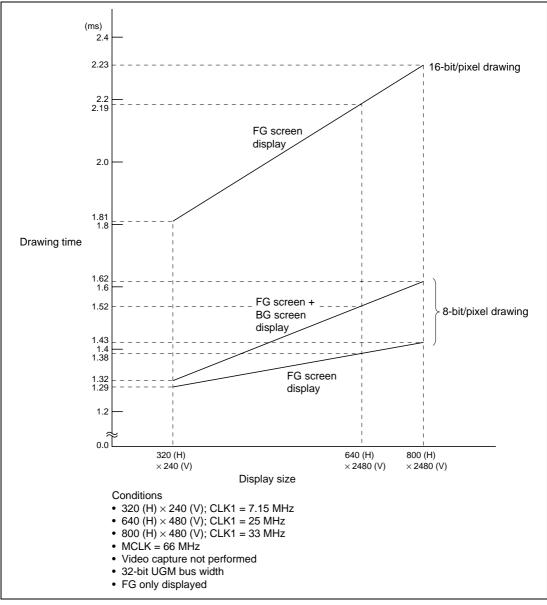

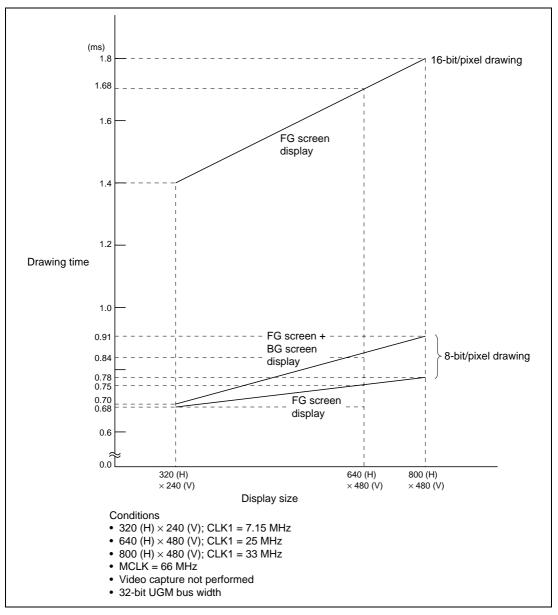

| Appe | endix I Drawing Performance                                         | 351  |

|      |                                                                     |      |

| Appe | endix J Usage of Video Capture Function                             | 354  |

| J.1  | Example of Video Capture Settings                                   | 354  |

|      | J.1.1 Example of Interlace Composite Capture                        | 354  |

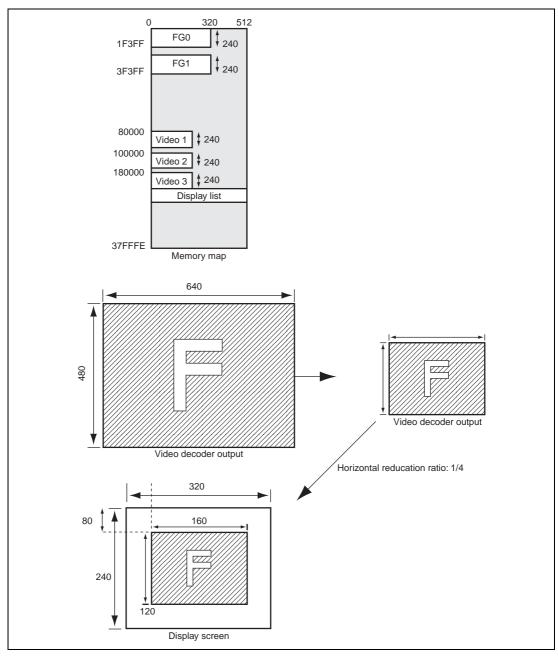

|      | J.1.2 Example of Modifying Video Data Size                          | 355  |

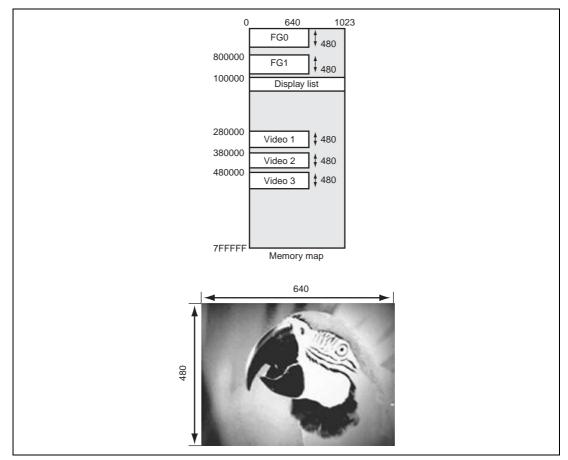

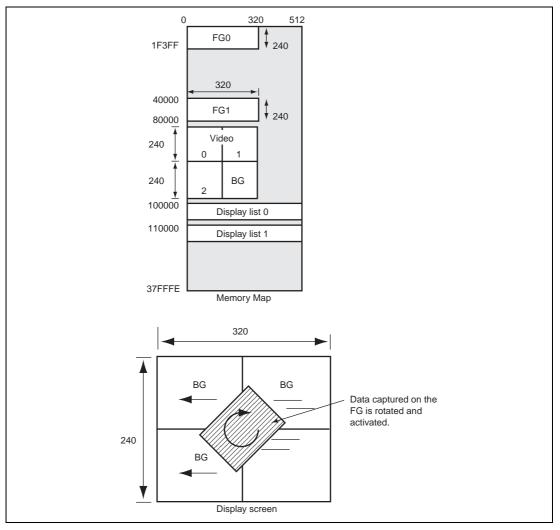

| J.2  | Example of Usage of Captured Data                                   | 358  |

|      | J.2.1 When Displaying Captured Data on Realtime Video Screen        | .358 |

|      | J.2.2 When Handling Captured Data as Multi-Valued Source Data       | 358  |

| J.3  | Video Decoder                                                       | 363  |

|      | J.3.1 Field Control by Video Decoder                                | 363  |

|      |                                                                     |      |

Rev. 2.0, 09/02, page xi of xviii

| J.3.2 Vid  | eo Decoder Settings | <br> |

|------------|---------------------|------|

|            | -                   |      |

| Appendix K | Product Lineup      | <br> |

# Figures

# Section 1 Overview

| Figure 1.1  | Sample System Configuration                                                              | 1   |

|-------------|------------------------------------------------------------------------------------------|-----|

| Figure 1.2  | Reduced System Size Through Use of UGM Architecture                                      | 2   |

| Figure 1.3  | Unified System Bus Interface                                                             | 3   |

| Figure 1.4  | Double-Buffering Architecture                                                            | 4   |

| Figure 1.5  | Graphics Accelerator                                                                     | 5   |

| Figure 1.6  | Pipeline Graphics Processing                                                             | 5   |

| Figure 1.7  | Display Composite Function                                                               | 6   |

| Figure 1.8  | Digital Video Images                                                                     | 6   |

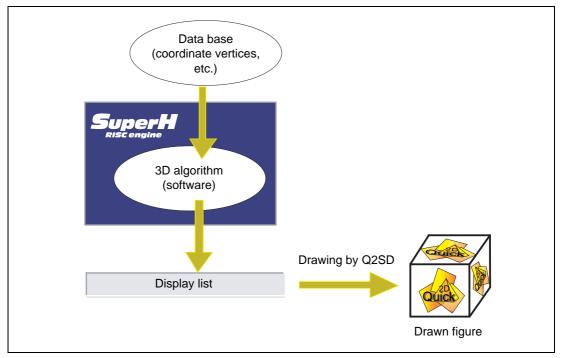

| Figure 1.9  | Data Flow when Using a 3D Algorithm                                                      | 7   |

| Figure 1.10 | Internal Block Diagram                                                                   | 12  |

| Figure 1.11 | State Transition Diagram                                                                 | 13  |

| Section 2   | Pins                                                                                     |     |

|             | Pin Configuration                                                                        | 15  |

|             | Pin Arrangement                                                                          |     |

| -           | Example of Circuit for Connection of Pins CAP1 and CAP2                                  |     |

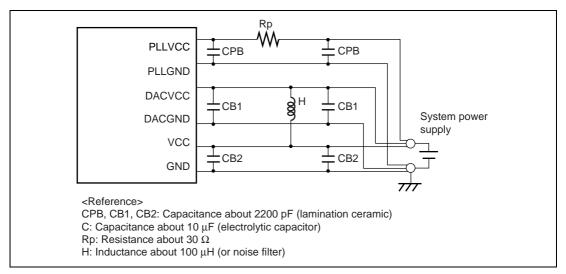

| 0           | Connections of Bypass Capacitors between Power Supplies Near the Pins                    |     |

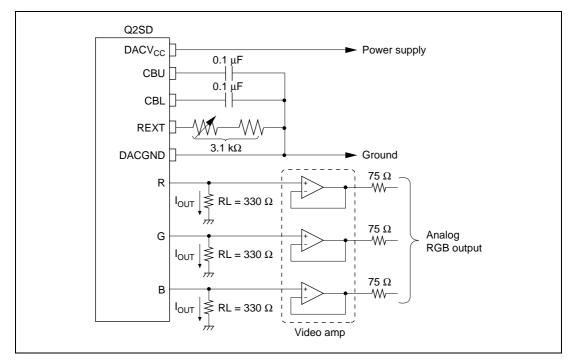

| -           | Example of Circuit for Connection of REXT, CBU, and CBL Pins                             |     |

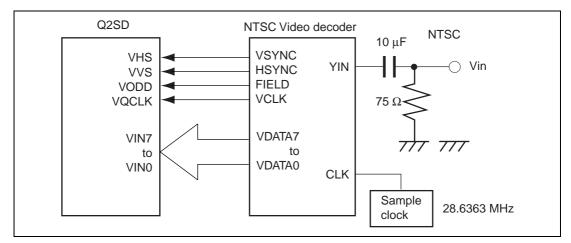

| -           | Example of Connection of Video Input Pins                                                |     |

| •           |                                                                                          |     |

|             | UGM Architecture                                                                         | 24  |

| •           | Example of System Configuration Using UGM                                                |     |

| -           | Example of UGM Mapping onto CPU Memory Space                                             |     |

|             | Byte Exchange Diagram.                                                                   |     |

|             | Image Data Specifications                                                                |     |

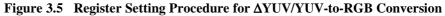

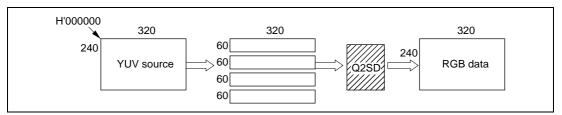

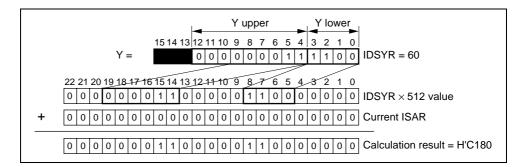

| -           | Register Setting Procedure for $\Delta$ YUV/YUV-to-RGB Conversion                        | 41  |

| -           | Example of Settings for Transferring 320 × 240 YUV Source Data to UGM                    | 40  |

|             | by Means of Four DMA Operations                                                          |     |

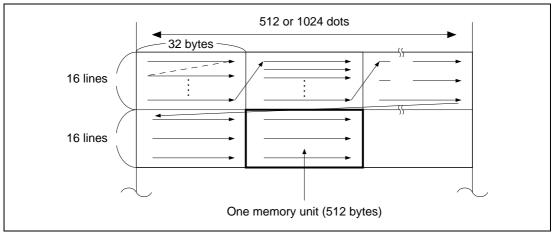

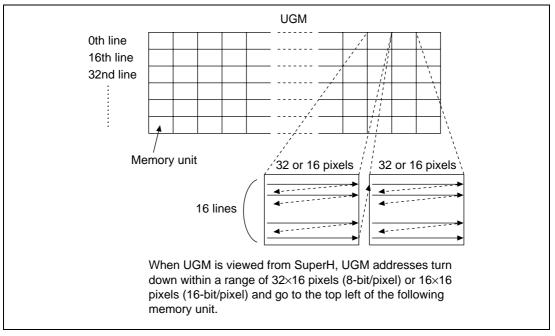

| -           | Configuration of One Memory Unit (512 Bytes)                                             |     |

| U           | UGM Address Transitions                                                                  |     |

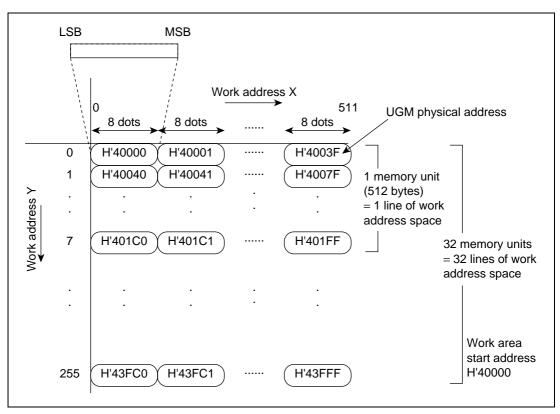

| Figure 3.9  | Correspondence between UGM Physical Addresses (Bytes) and 2-Dimensinal Virtual Addresses | 51  |

| E           |                                                                                          |     |

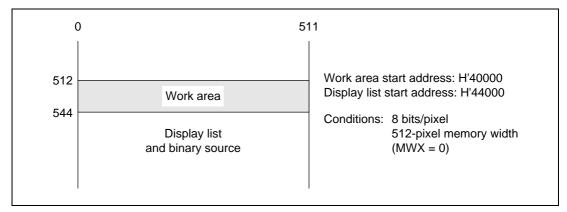

| -           | Work Address Space                                                                       |     |

| -           | Relationship between UGM Physical Addresses (Byte) and Work Addresses                    |     |

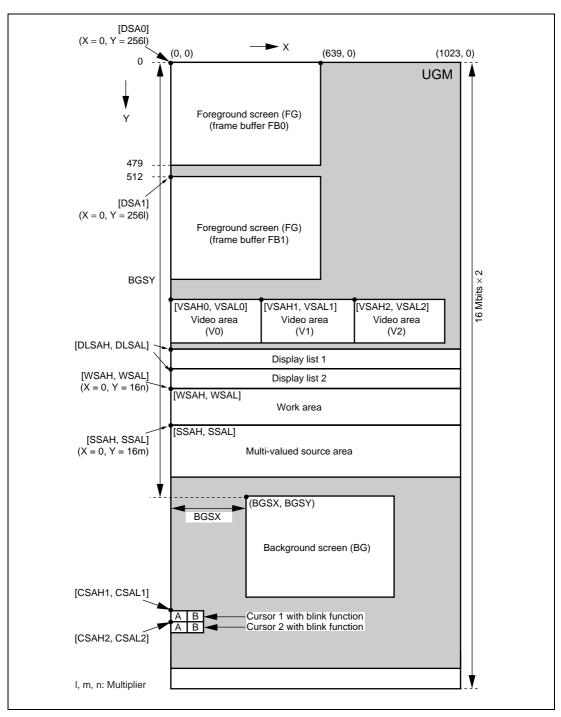

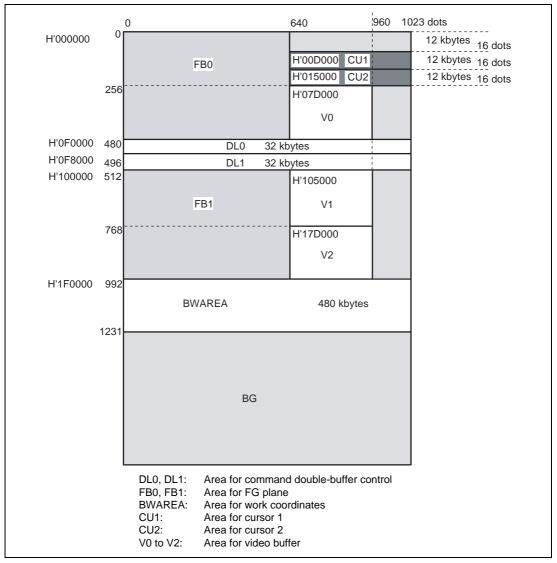

| Figure 3.12 | Sample Memory Map                                                                        | - 7 |

| E' 2.12     | (Corresponding to 640 × 480 Screen Size, with 16 Bits/Pixel)                             |     |

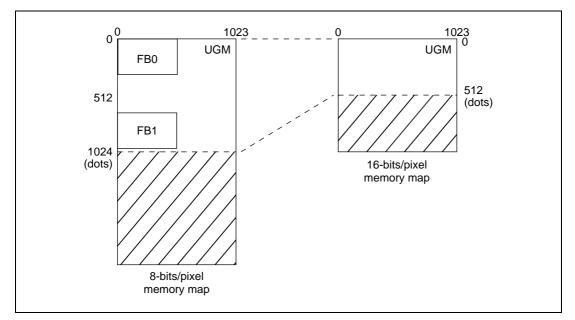

| -           | Relationship between 8-Bits/Pixel and 16-Bits/Pixel Memory Maps                          |     |

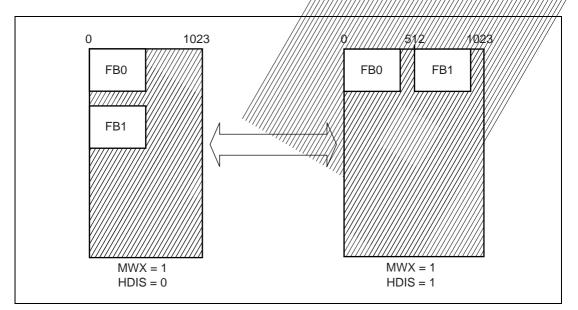

| -           | Example of Frame Buffer FB1 Location When HDIS = 1                                       |     |

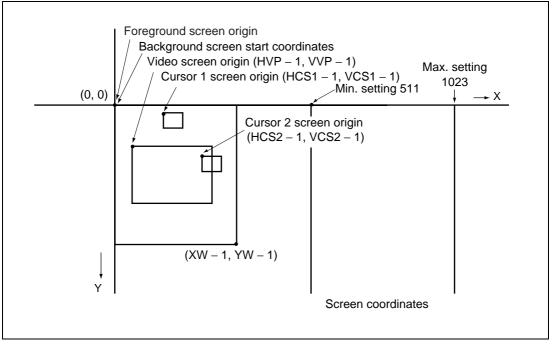

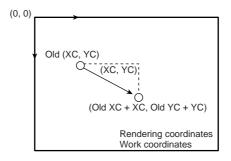

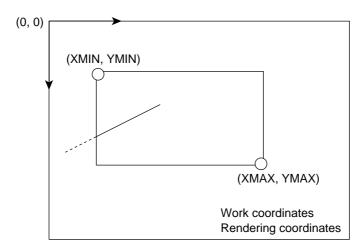

| U           | Screen Coordinates                                                                       |     |

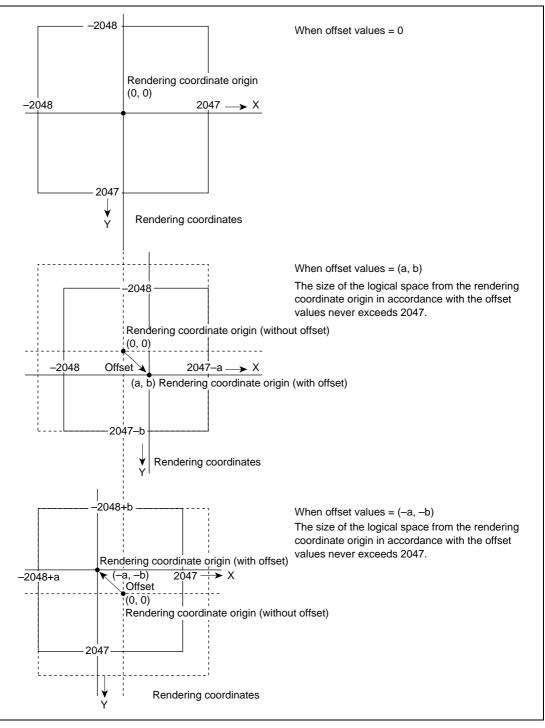

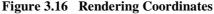

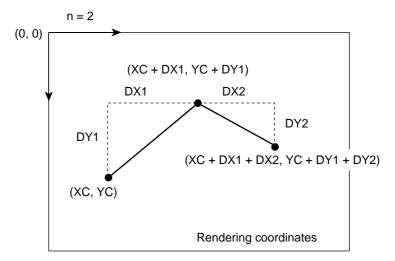

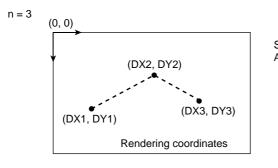

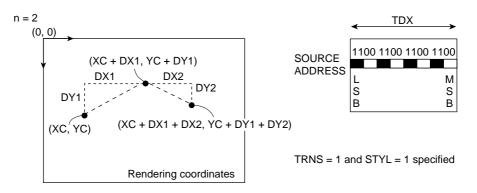

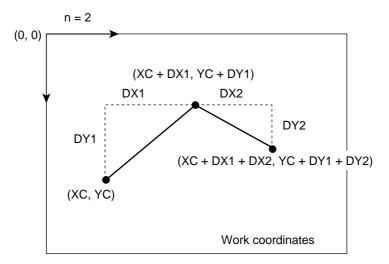

| Figure 3.16 | Rendering Coordinates                                                                    | 62  |

| Figure 3.17 | Multi-Valued Source Coordinates (LNi = 0)                                | 64    |

|-------------|--------------------------------------------------------------------------|-------|

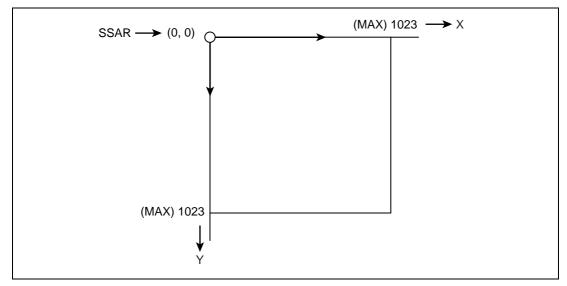

| Figure 3.18 | Multi-Valued Source Coordinates with LNi = 1 Specified (Linear Address)  | 64    |

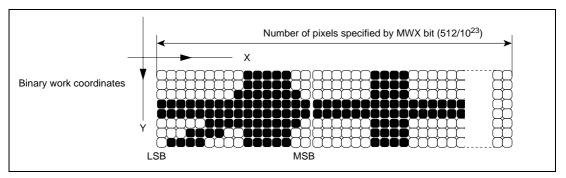

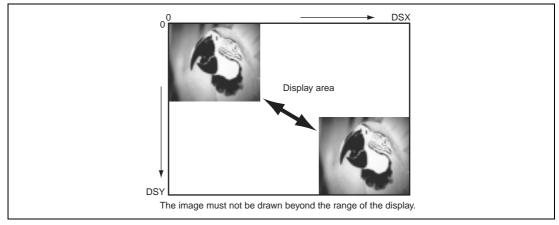

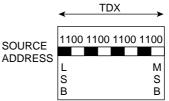

| Figure 3.19 | Binary Source Coordinates                                                | 65    |

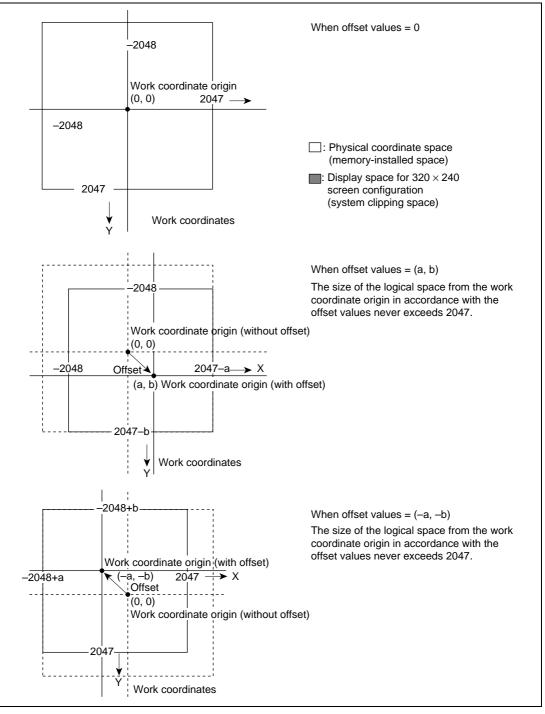

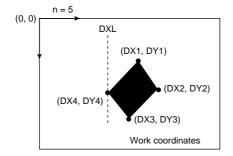

| Figure 3.20 | Work Coordinates                                                         | 66    |

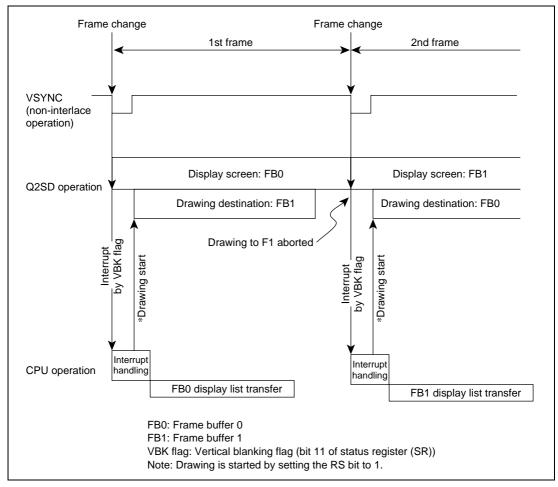

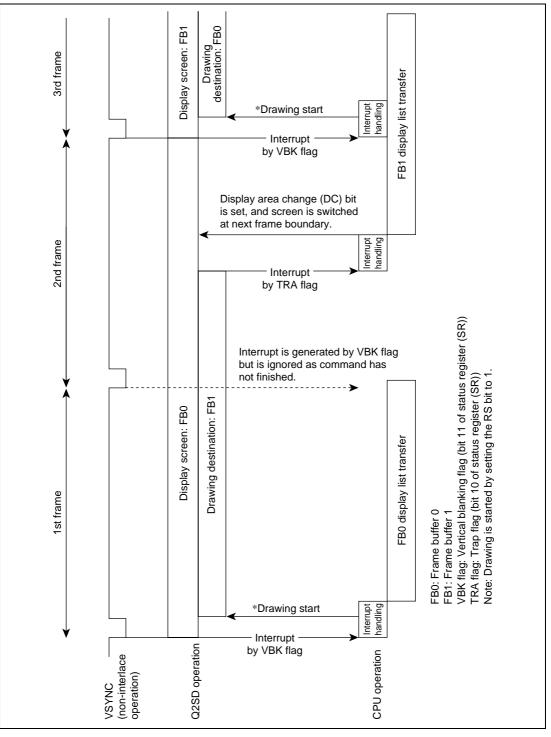

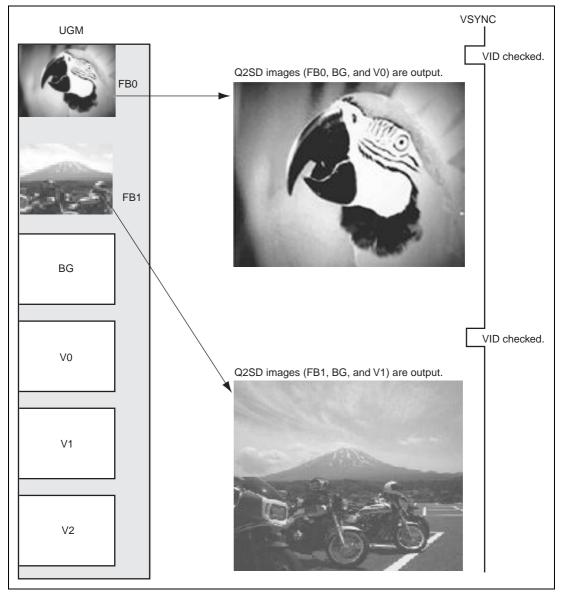

| Figure 3.21 | Operation in Auto Display Change Mode                                    | 69    |

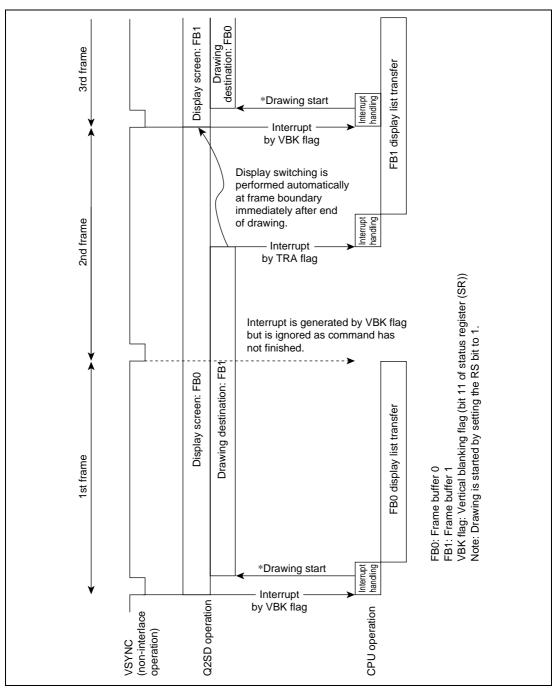

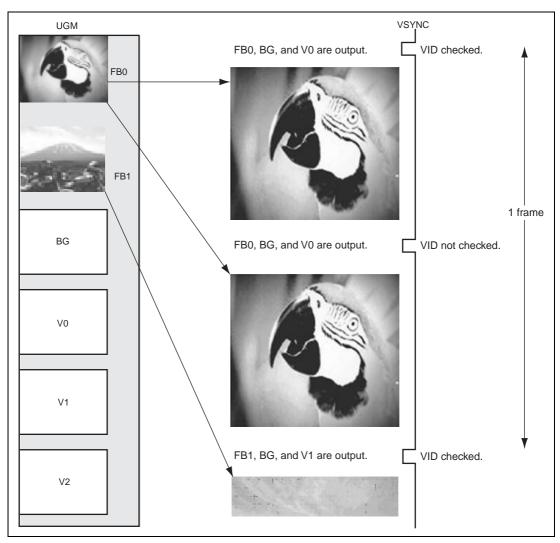

| Figure 3.22 | Operation in Auto Rendering Mode                                         | 70    |

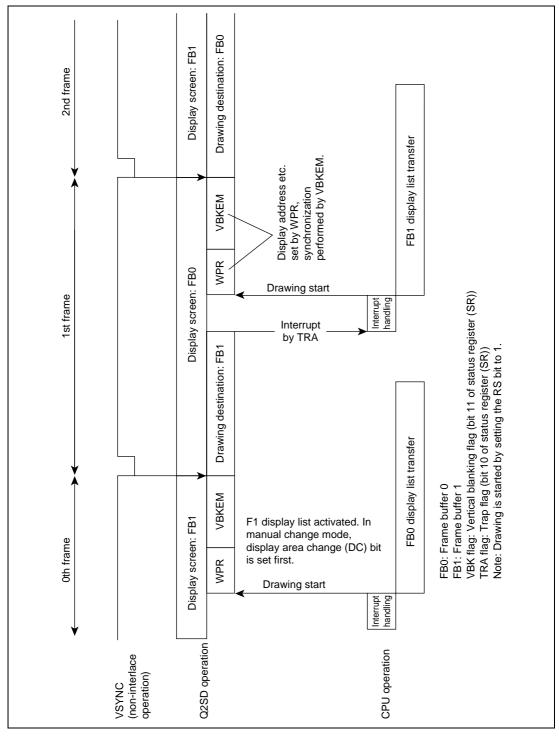

| Figure 3.23 | Operation in Manual Display Change Mode                                  | 72    |

| Figure 3.24 | Operation when Using VBKEM Command                                       | 73    |

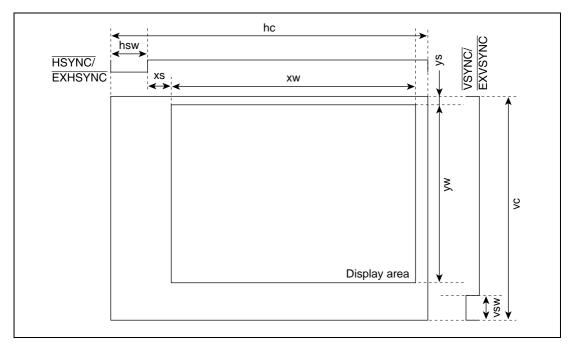

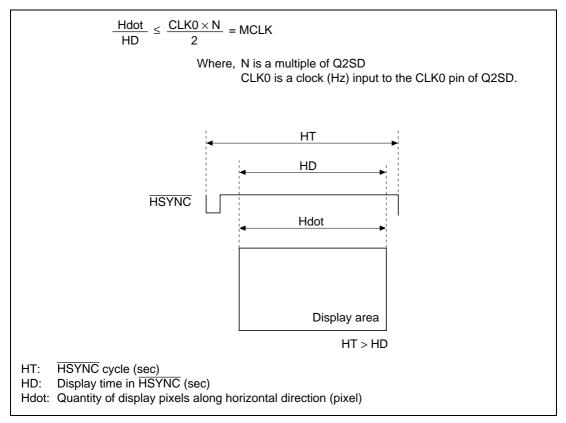

| Figure 3.25 | Display Timing                                                           | 75    |

| Figure 3.26 | Configuration of the Display Screen for Q2SD                             | 78    |

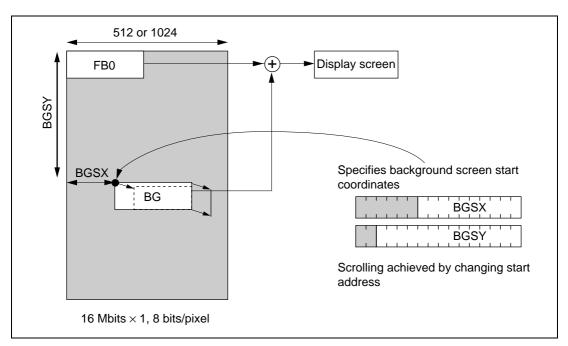

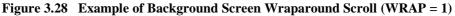

| Figure 3.27 | Example of Background Screen Simple Scroll (WRAP = 0)                    | 80    |

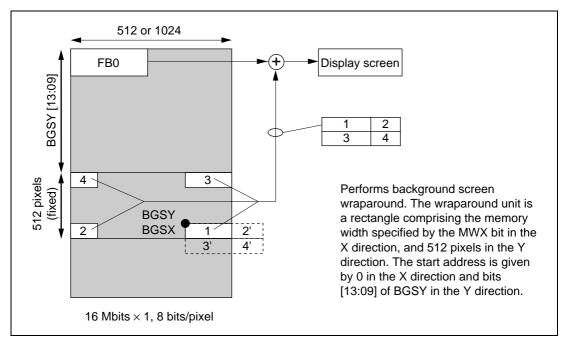

| Figure 3.28 | Example of Background Screen Wraparound Scroll (WRAP = 1)                | 81    |

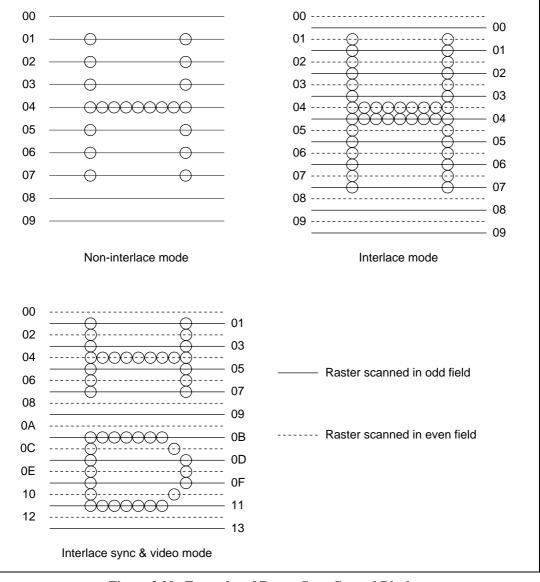

| Figure 3.29 | Examples of Raster Scan Control Display                                  | 82    |

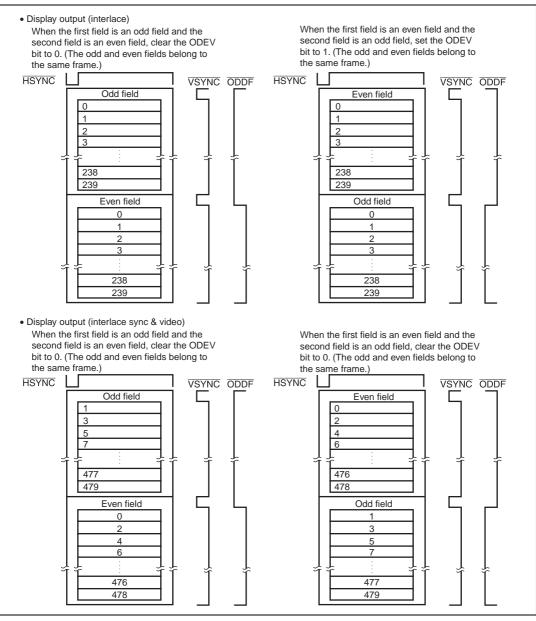

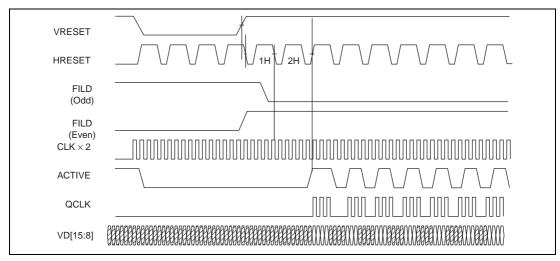

| Figure 3.30 | Display by Interlace Sync Method                                         | 84    |

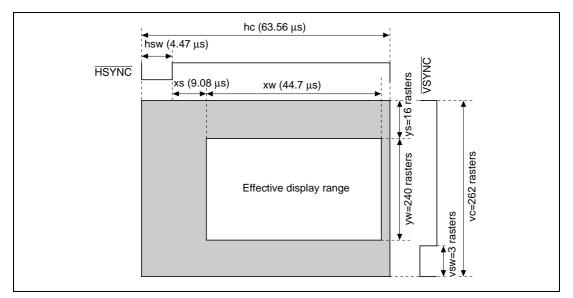

| Figure 3.31 | Display by Non-Interlace Method                                          | 85    |

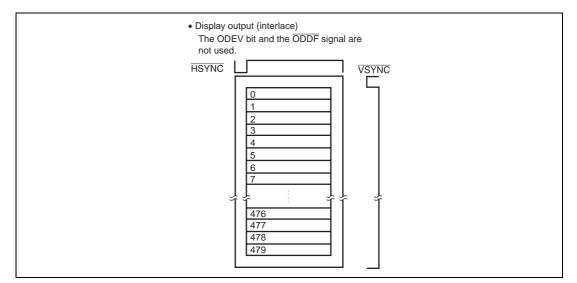

| Figure 3.32 | Non-Interlace Mode Display Output                                        | 86    |

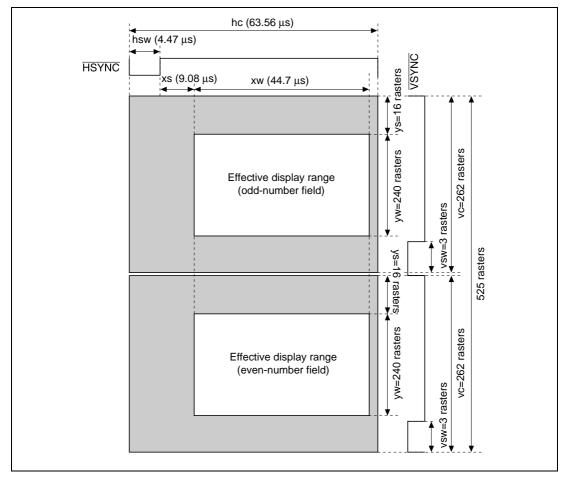

| Figure 3.33 | Interlace Mode Display Output                                            | 87    |

| Figure 3.34 | (1) Interlace Sync & Video Mode Output                                   | 88    |

| Figure 3.34 | (2) Interlace Sync & Video Mode Output                                   | 89    |

| Figure 3.35 | Signal Flow in TV Sync Mode                                              | 91    |

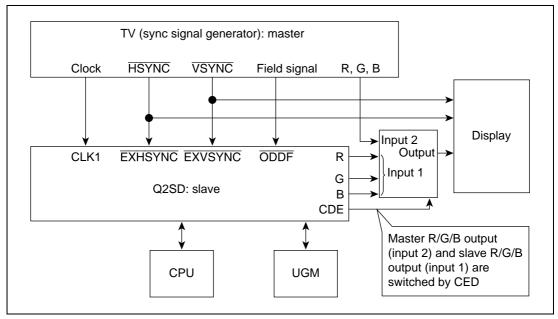

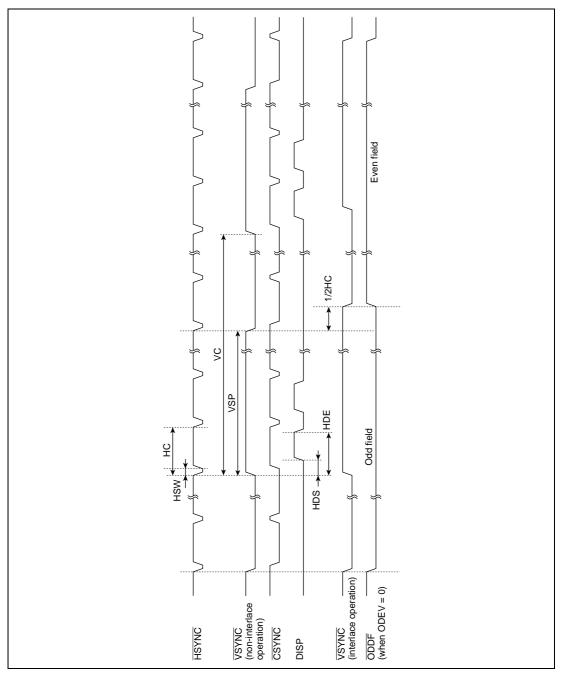

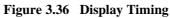

| Figure 3.36 | Display Timing                                                           | 93    |

| Figure 3.37 | CSYNC Output Waveform                                                    | 94    |

| Figure 3.38 | Drawing Functions                                                        | 98    |

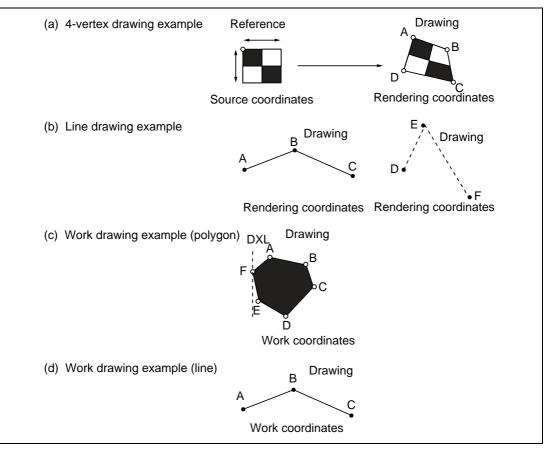

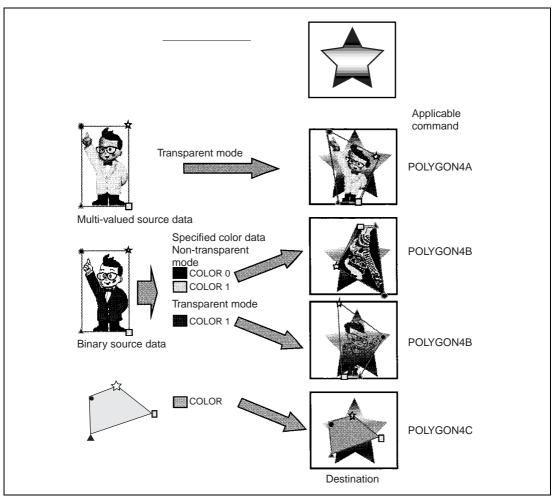

| Figure 3.39 | Example of POLYGON4 Transfer Data Combinations                           | 99    |

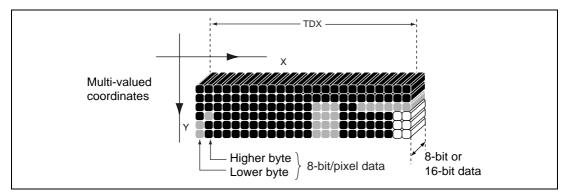

| Figure 3.40 | Multi-Valued Source Data Configuration                                   | . 100 |

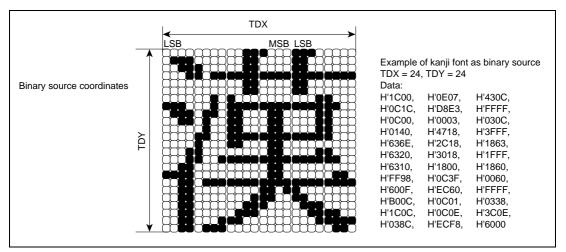

| Figure 3.41 | Example of Kanji Font as Binary Source (TDX = 24, TDY = 24)              | . 100 |

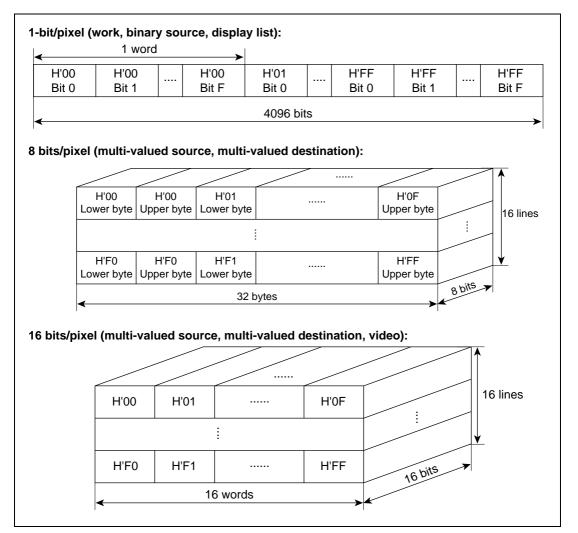

| Figure 3.42 | Binary Work Data Configuration                                           | . 101 |

|             | Rendering Attribute Bit Arrangement                                      |       |

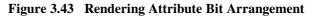

|             | Example of Source Style Specification                                    |       |

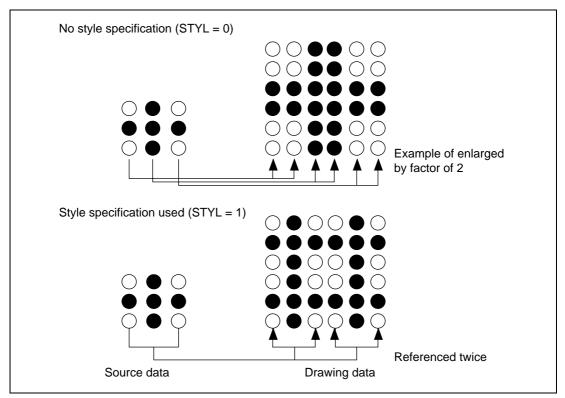

| Figure 3.45 | Example of Clipping Specification                                        | . 104 |

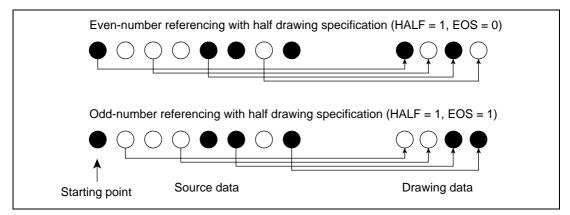

| -           | Examples of Even/Odd Select Specifications                               |       |

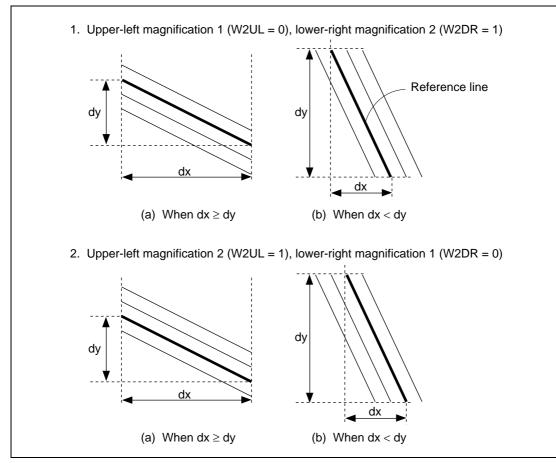

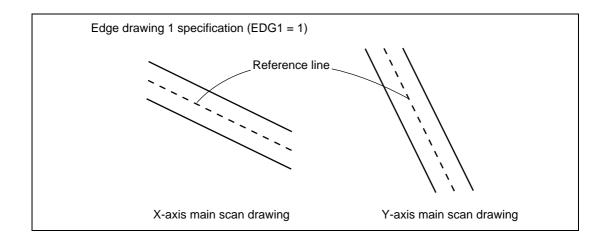

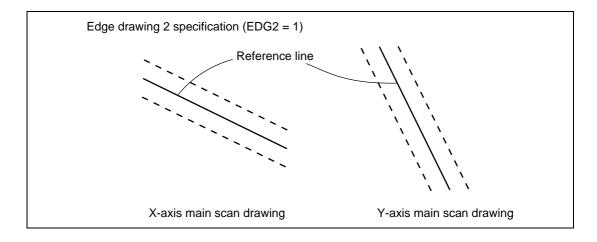

| Figure 3.47 | Examples of Bold Line Drawing                                            | . 107 |

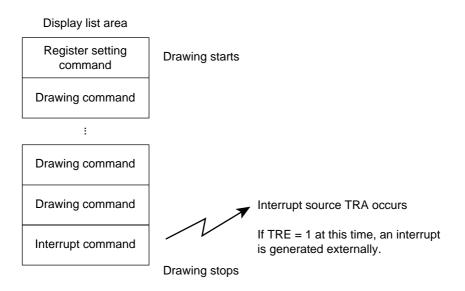

| Figure 3.48 | Example of Display List                                                  | .111  |

|             | Example of Timing for Suspending and Resuming Background Screen Drawing. |       |

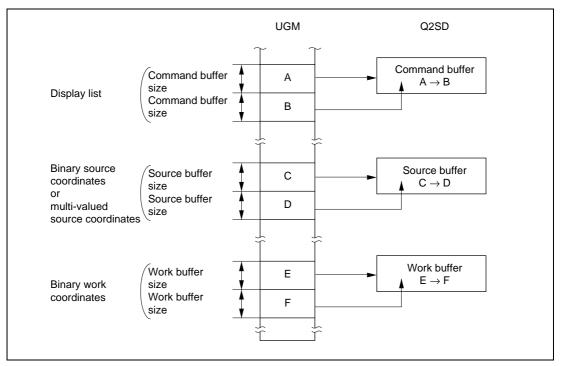

| Figure 3.50 | Updating of Q2SD's Internal Buffers                                      | . 113 |

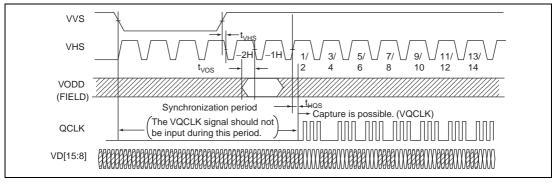

| Figure 3.51 | Video Incorporation Signals                                              | .115  |

|             | Video Capture Timing                                                     |       |

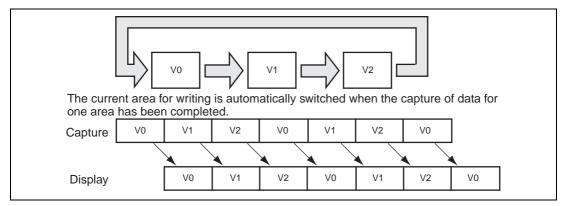

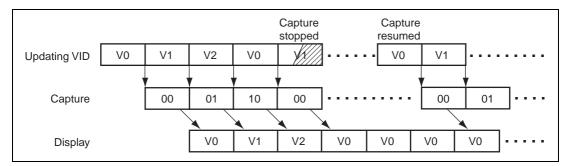

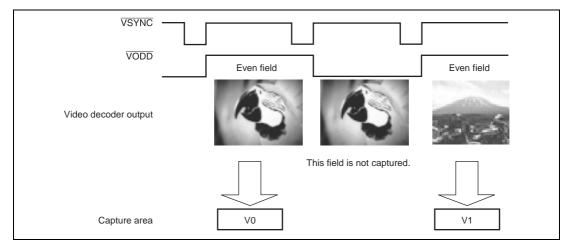

| Figure 3.53 | Capture State                                                            | .116  |

| Figure 3.54 | Display State                                                            | .116  |

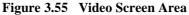

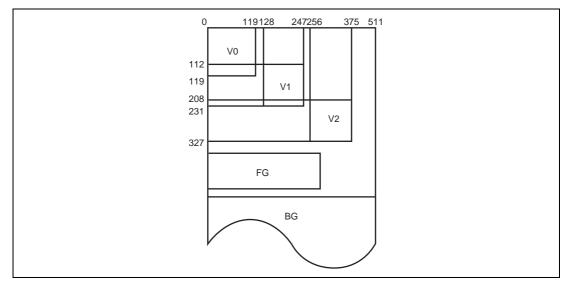

| Figure 3.55 | Video Screen Area                                                        | . 118 |

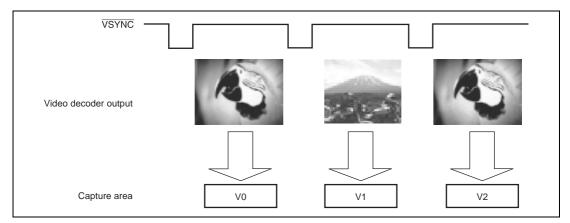

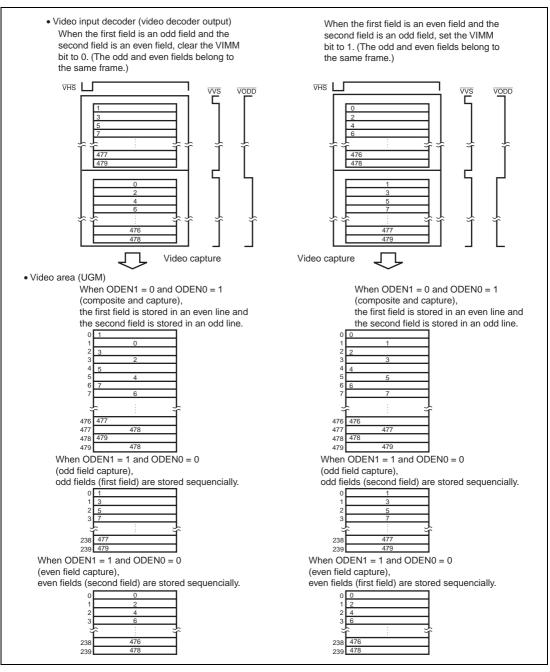

| Figure 3.56 | Interlace Capture                                                        | . 119 |

| Figure 3.57 | Interlace Composite Capture                                              | .119  |

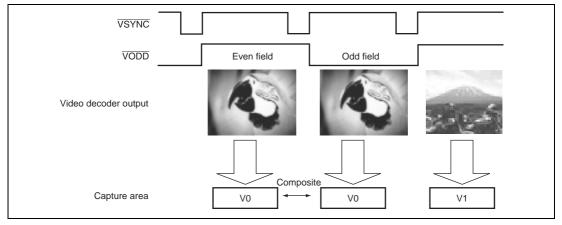

| Figure 3.58 | Interlace Capture (Odd Field)                                            | .120  |

|             |                                                                          |       |

Rev. 2.0, 09/02, page xiv of xviii

| Figure 3.59 Interlace Capture (Even Field)                                      | 120  |

|---------------------------------------------------------------------------------|------|

| Figure 3.60 Interlace Video Input Field Handling Specification                  | 121  |

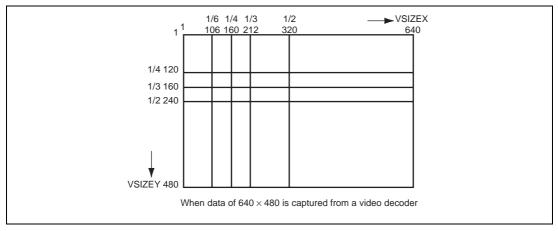

| Figure 3.61 Reducing the Size of the Captured Image                             | 122  |

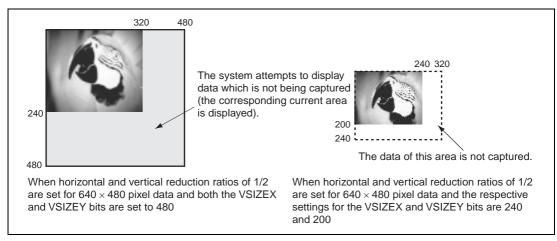

| Figure 3.62 Incorrect Settings for the Reduction Ratios                         | 123  |

| Figure 3.63 Setting up the Capture Area                                         | 124  |

| Figure 3.64 Example of the Settings for Capture Areas                           | 125  |

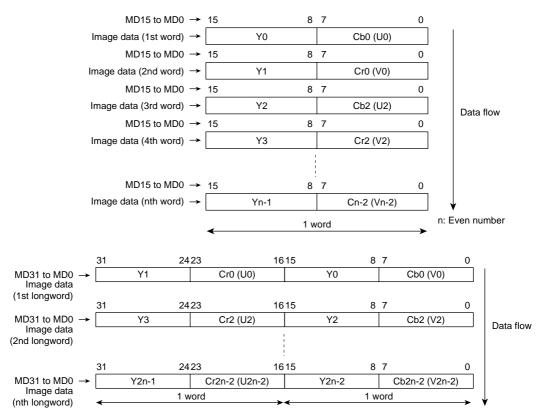

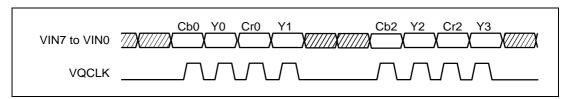

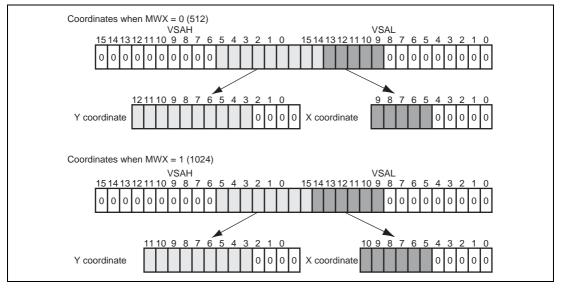

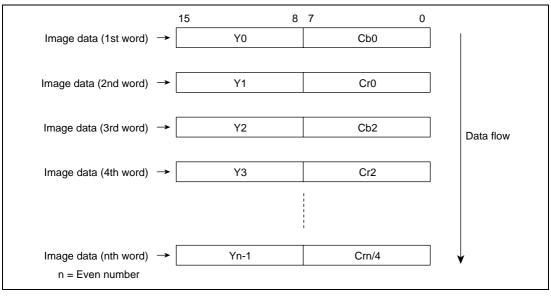

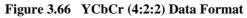

| Figure 3.65 The Flow of YCbCr (4:2:2) Data                                      | 126  |

| Figure 3.66 YCbCr (4:2:2) Data Format                                           | 127  |

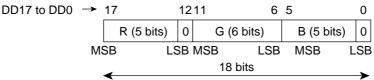

| Figure 3.67 Conversion of YCbCr Data into RGB Format                            | 128  |

| Figure 3.68 The RGB Data Format (16 Bits/Pixel)                                 | 128  |

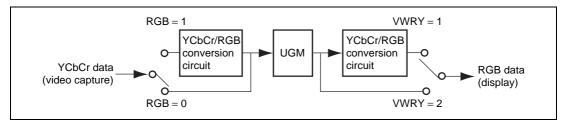

| Figure 3.69 Position of the Video Image                                         | 129  |

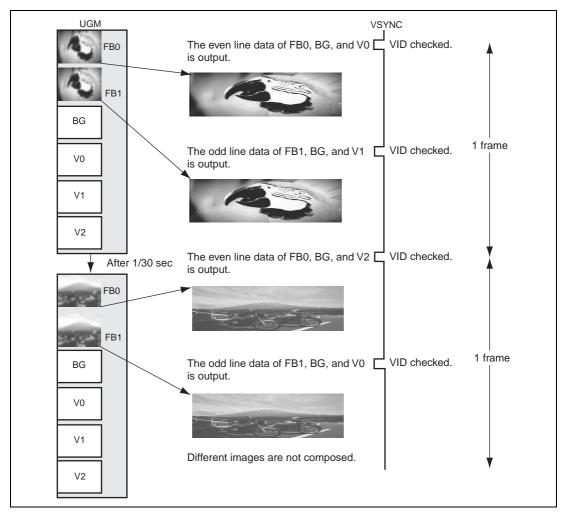

| Figure 3.70 The Display of Data Captured in Interlace Mode and Display          | 130  |

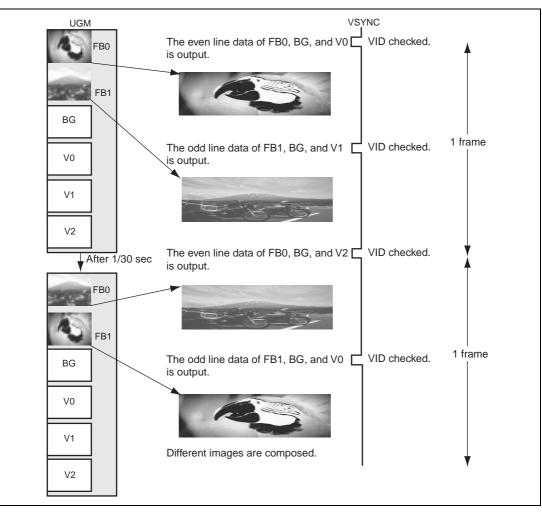

| Figure 3.71 The Display of Data Captured in the Interlace Composite Mode        | 131  |

| Figure 3.72 The Display of Data Captured in the Interlace Odd-Only Mode         | 132  |

| Figure 3.73 The Display of Data Captured in the Interlace Even-Only Mode        | 133  |

| Section 6 Usage Notes                                                           |      |

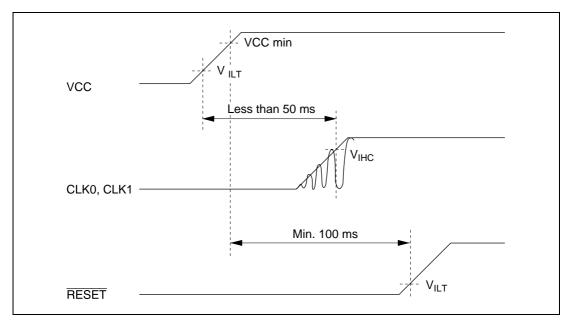

| Figure 6.1 Power-On Sequence                                                    | 269  |

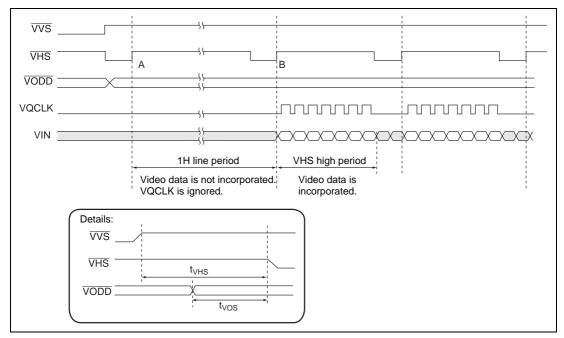

| Figure 6.2 Video Interface Timing                                               |      |

|                                                                                 |      |

| Section 7 Electrical Characteristics                                            | 27.6 |

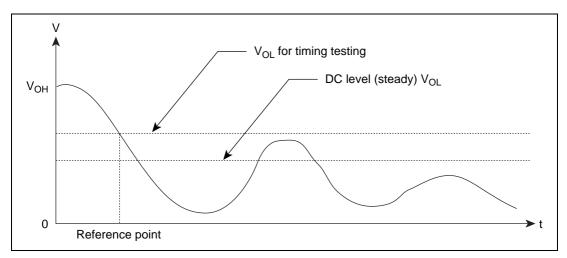

| Figure 7.1 Basis of V <sub>OL</sub> Timing Testing                              |      |

| Figure 7.2 Test Load Circuit                                                    |      |

| Figure 7.3 Input Clocks                                                         |      |

| Figure 7.4 Reset Timing                                                         |      |

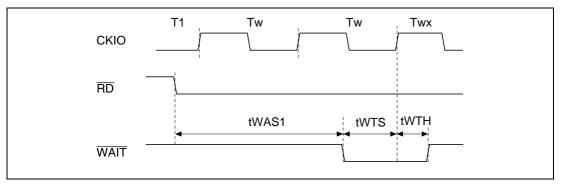

| Figure 7.5 CPU Read Cycle Timing (CPU $\leftarrow$ Q2SD) with Hardware Wait     |      |

| Figure 7.6 CPU Read Cycle Timing (CPU $\rightarrow$ Q2SD) with Hardware Wait    |      |

| Figure 7.7 (1) DMA Write Cycle Timing (Single Address, DMAC $\rightarrow$ Q2SD) |      |

| Figure 7.7 (2) DMA Write Cycle Timing (Single Address, DMAC $\rightarrow$ Q2SD) |      |

| Figure 7.7 (3) DMA Write Cycle Timing (Dual Address, DMAC $\rightarrow$ Q2SD)   |      |

| Figure 7.7 (4) DMA Write Cycle Timing (Dual Address, DMAC $\rightarrow$ Q2SD)   |      |

| Figure 7.8 Interrupt Output Timing                                              |      |

| Figure 7.9 UGM Read Cycle Timing                                                |      |

| Figure 7.10 UGM Write Cycle Timing                                              |      |

| Figure 7.11 (1) UGM Refresh Cycle Timing                                        |      |

| Figure 7.11 (2) UGM Mode Register Setting Cycle Timing                          |      |

| Figure 7.12 Master Mode Display Timing                                          |      |

| Figure 7.13 (1) TV Sync Mode Display Timing                                     |      |

| Figure 7.13 (2) TV Sync Mode Display Timing                                     |      |

| Figure 7.14 (1) Video Interface Timing                                          | 303  |

| Figure 7.14 (2) Video Interface Timing                                          |      |

#### Appendix C Drawing Algorithms

Rev. 2.0, 09/02, page xv of xviii

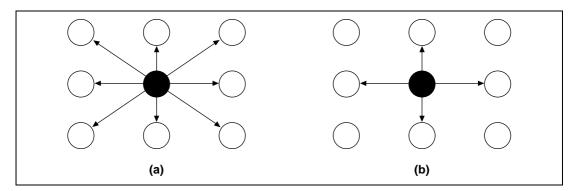

| Figure C.2 Comparison of (a) 8-Point Drawing and (b) 4-Point Draw   | ving    |

|---------------------------------------------------------------------|---------|

| Figure C.3 Drawing Dot Determination Process in (a) 8-Point Drawing | ing and |

| (b) 4-Point Drawing                                                 |         |

| Appendix D Package Dimensions                                       |         |

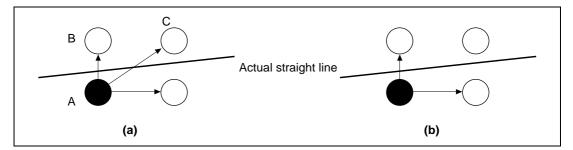

| Figure D.1 Package Dimensions (FP-176)                              | 310     |

|                                                                     |         |

| Appendix F Example of System Configuration for SuperH               |         |

| Figure F.1 Example of System Configuration Overview                 |         |

| Figure F.2 Example of Interface Timing                              |         |

| Figure F.3 Example of Memory Mapping (Using SH7709)                 |         |

| Figure F.4 UGM Memory Map                                           |         |

| Figure F.5 UGM Address Transition Overview                          |         |

| Appendix G Example of Display Control                               |         |

| Figure G.1 Example of Display Timing                                |         |

| Figure G.2 Example of Display Timing under Non-interlace Mode .     |         |

| Figure G.3 Example of Display Timing under Interlace Sink & Vide    | eo Mode |

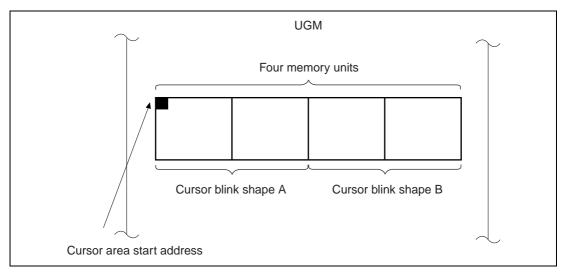

| Figure G.4 Cursor Allocation                                        |         |

| Appendix H Example of Drawing Control                               |         |

| Figure H.1 Display/Drawing Control Timing Chart (DBF = 0)           | 344     |

| Figure H.2 Example of Referencing and Branching                     |         |

|                                                                     |         |

| Appendix I Drawing Performance                                      |         |

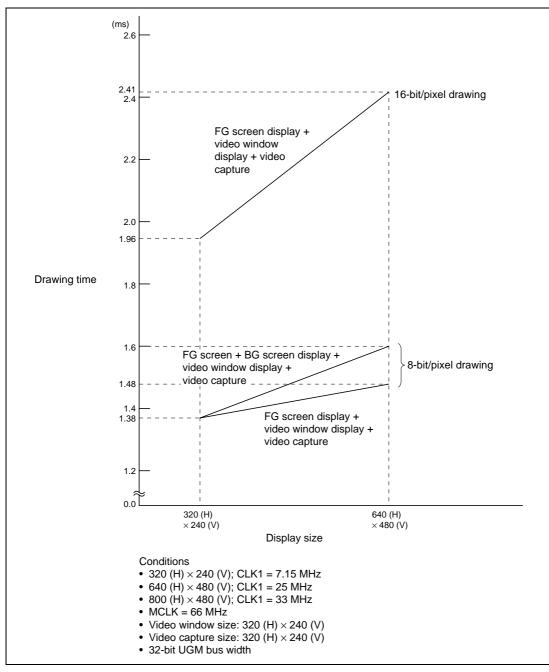

| Figure I.1 POLYGON4C Drawing Performance when $FST = 0$             | 251     |

| (Drawing Range: $320 (H) \times 240 (V)$ )                          |         |

| Figure I.2 POLYGON4C Drawing Performance when $FST = 1$             | 250     |

| (Drawing Range: $320 (H) \times 240 (V)$ )                          |         |

| Figure I.3 POLYGON4C Drawing Performance when $FST = 0$             | 252     |

| (Drawing Range: $320 (H) \times 240 (V)$ )                          |         |

| Appendix J Usage of Video Capture Function                          |         |

| Figure J.1 Interlace Composite Capture                              |         |

| Figure J.2 Interlace Composite Capture (Horizontal and Vertical Red |         |

| Figure J.3 Example of Video Data Usage                              |         |

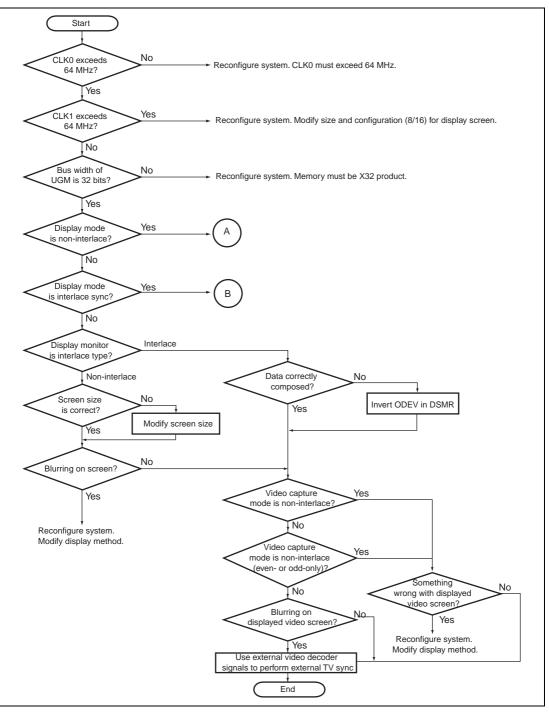

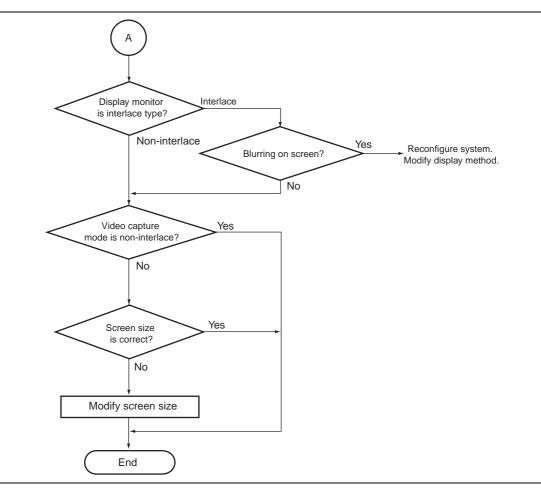

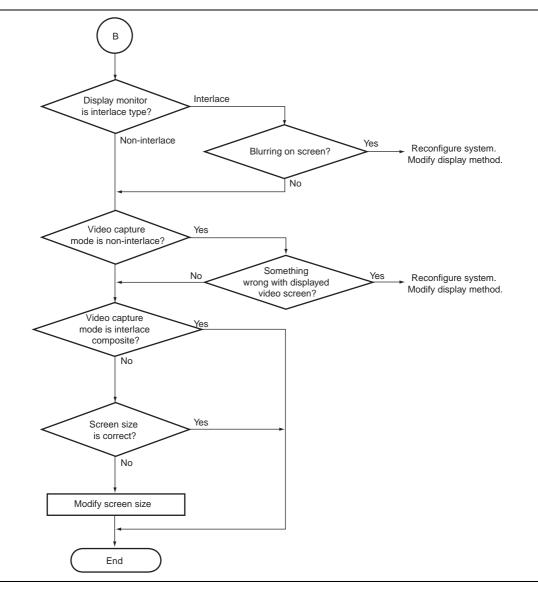

| Figure J.4 Q2SD Video Setting Flow (1)                              |         |

| Figure J.5 Q2SD Video Setting Flow (2)                              |         |

| Figure J.6 Q2SD Video Setting Flow (3)                              |         |

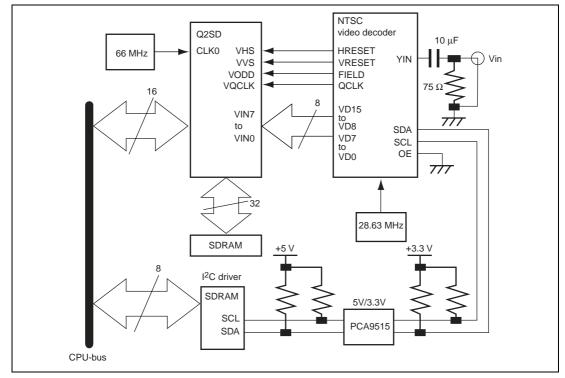

| Figure J.7 Example of Connection of Video Capture Circuit           |         |

| Figure J.8 Example of Interlaced Data Output Timing for Decoder     |         |

# Tables

| Section 1  | Overview                                                             |

|------------|----------------------------------------------------------------------|

| Table 1.1  | A List of Specifications                                             |

| Table 1.2  | Pin States After Reset                                               |

| Section 2  | Pins                                                                 |

| Table 2.1  | Pin Functions                                                        |

| Table 2.2  | Operating Mode Selection                                             |

| Table 2.3  | Input Clocks and Operating Frequencies                               |

| Section 3  | UGM Architecture                                                     |

| Table 3.1  | Registers with Internal Update Function                              |

| Table 3.2  | Interrupt Output Function                                            |

| Table 3.3  | Setting for Number of Refreshes                                      |

| Table 3.4  | Sample Estimations of Number of Refresh Cycles74                     |

| Table 3.5  | Variables Defined by Display Screen76                                |

| Table 3.6  | Register Settings                                                    |

| Table 3.7  | Background Screen Related Register Settings                          |

| Table 3.8  | Combinations of Q2SD Output and Monitor Input Methods                |

| Table 3.9  | Drawing Commands96                                                   |

| Table 3.10 | Bold Line Drawing Settings                                           |

| Table 3.11 | 8-Bit Pixel Interface                                                |

| Table 3.12 | Selecting Modes of Video Capture and Display for the Q2SD134         |

| Section 4  | Display List                                                         |

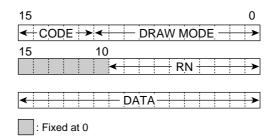

| Table 4.1  | Command List                                                         |

| Section 5  | Registers                                                            |

| Table 5.1  | Registers                                                            |

| Table 5.2  | Bit Configuration                                                    |

| Table 5.3  | YUV Mode Setting                                                     |

| Table 5.4  | Video Incorporation Reduction Ratio                                  |

| Appendix   |                                                                      |

| Table G.1  | Setting Example of Variables ((TVM1,0) = (0,0), (SCM1,0) = (0,0))337 |

| Table G.2  | Register Setting Example ((TVM1,0) = $(0,0)$ , (SCM1,0) = $(0,0)$ )  |

| Table G.3  | Setting Example of Variables $((TVM1,0) = (0,0), (SCM1,0) = (1,1))$  |

| Table G.4  | Register Setting Example ((TVM1,0) = $(0,0)$ , (SCM1,0) = $(1,1)$ )  |

| Appendix   | • •                                                                  |

| Table H.1  | Relationship of DBF and Display Screen (FG)                          |

Rev. 2.0, 09/02, page xviii of xviii

# Section 1 Overview

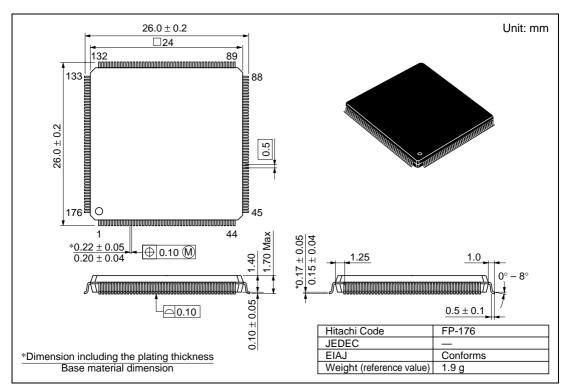

The Q2SD (Quick 2D Graphics Renderer with Synchronous DRAM Interface) is a 2D graphics renderer that supports SDRAM interface in the SH microcomputer graphics accelerator "Quick" series (Q Series), based on the concepts of simplicity, realtime operation, and upgradability.

The use of unified graphics memory (UGM), a double-buffering system that switches drawing and display buffers in frame units, and the video-input function, providing a high-speed drawing performance of 60 screens per second, has made possible minimization of graphics memory (with the minimum configuration of a single 16-Mbit SDRAM memory), unified handling of graphics and natural images, and realtime software 3D graphics drawing. The separation of geometric operations (handled by the CPU) and rendering operations (handled by the Q2SD) has also resulted in improved system bus utilization.

The Q2SD is a high-performance graphics rendering LSI for multimedia applications, which provides both drawing and display, video input functions integrated into a single chip.

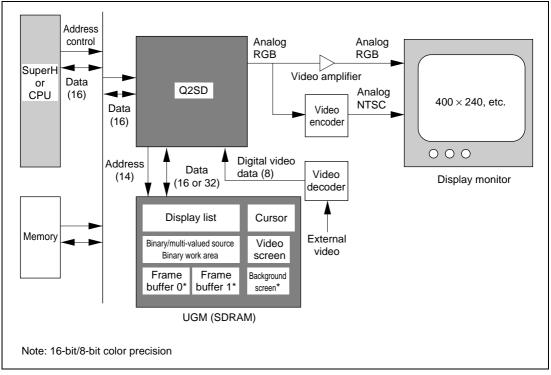

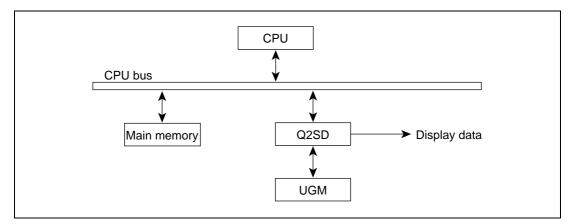

A sample Q2SD system configuration is shown in figure 1.1.

Figure 1.1 Sample System Configuration

# 1.1 Features

# Simple (Optimized System Configuration):

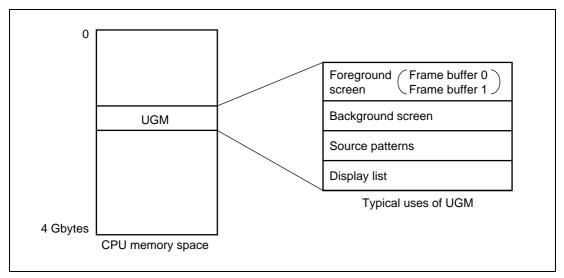

# (1) Use of Unified Graphics Memory (UGM) Architecture

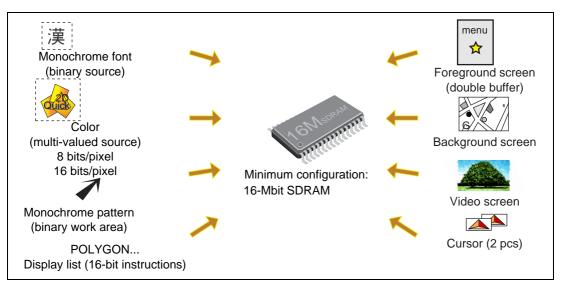

- Unified handling of image data (unified graphics memory (UGM) architecture) Data in various formats can be stored and managed in the same unified graphics memory (see figure 1.2).

- Minimum necessary UGM Minimum UGM configuration: One 16-bit-data-bus type 16-Mbit synchronous DRAM

Figure 1.2 Reduced System Size Through Use of UGM Architecture

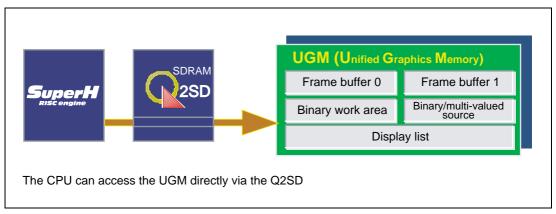

• Allocating the UGM in the CPU's memory space

A CPU interface circuit is incorporated to provide a unified interface. The UGM is allocated in the CPU's memory space (see figure 1.3). This simplifies the UGM management by the CPU.

Figure 1.3 Unified System Bus Interface

#### **Realtime:**

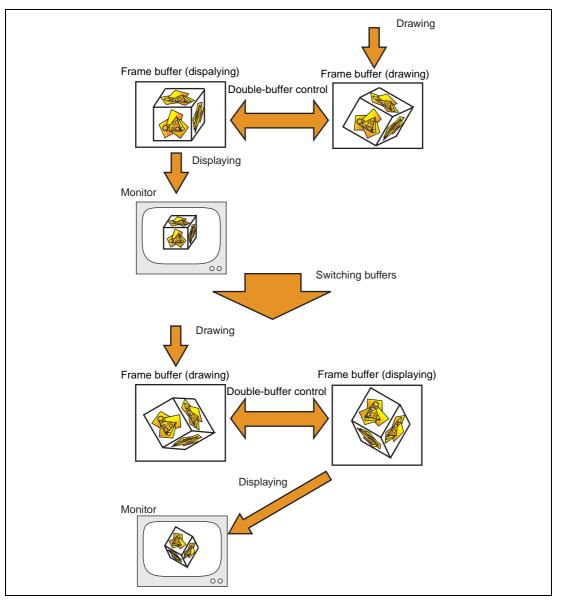

# (1) Use of Double-Buffering Architecture

The use of a double-buffering architecture that allows switching between the drawing buffer and display buffer in frame or field units enables realtime operation by synchronous with display processing with high-speed drawing processing (see figure 1.4).

Figure 1.4 Double-Buffering Architecture

#### Renesas

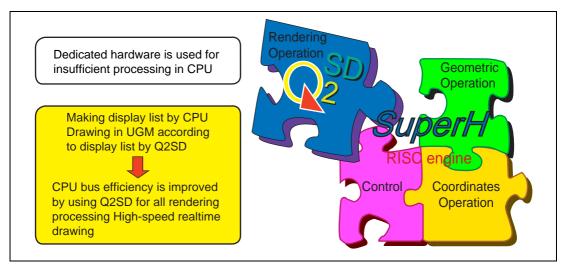

#### (2) Graphics Accelerator

A Dedicated hardware is used for the inefficient processing in the CPU. Thus, CPU bus efficiency is improved and high-speed realtime drawing is realized (see figure 1.5).

Figure 1.5 Graphics Accelerator

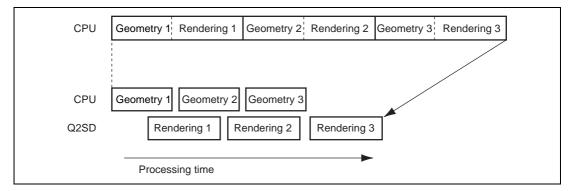

#### (3) Pipeline Graphics Processing:

High-speed graphics processing is enabled by pipelining the CPU geometry processing and Q2SD rendering processing (see figure 1.6).

Figure 1.6 Pipeline Graphics Processing

#### (4) Use of Write-Only Drawing:

Write-only drawing (a drawing method using only write operations) is used to improve drawing performance.

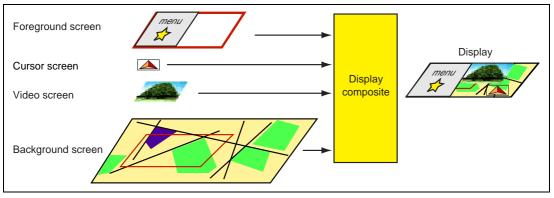

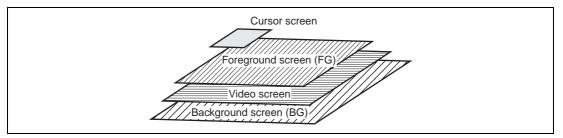

#### (5) Display Composite Function

The drawing time can be reduced by changing only the images that have been modified (see figure 1.7).

Figure 1.7 Display Composite Function

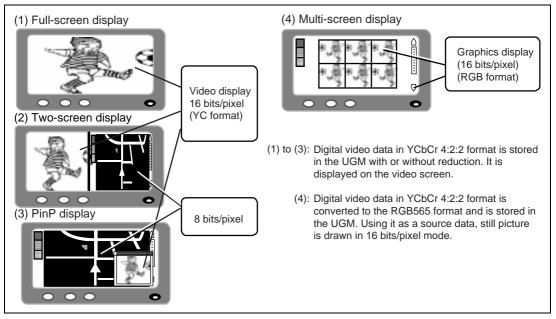

#### (6) Digital Video Capture

Realtime expression of digital video images in various types can be achieved.

Figure 1.8 Digital Video Images

#### Renesas

#### (7) Support for SDRAM

SDRAM can be used for the UGM. This enables the Q2SD to use burst access to the UGM and perform high-speed drawing.

#### Upgradability:

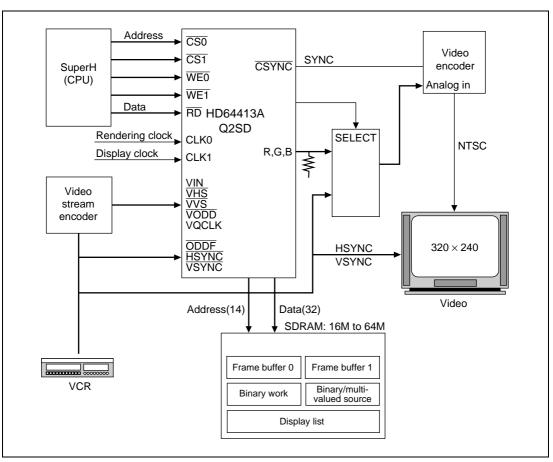

### (1) Algorithm Upgrading

In the Q2SD's drawing system, algorithms for coordinate conversion, etc., are executed by the CPU, using a systematized data base containing coordinates and other data, and the results are represented in graphical form. Thus, the graphics for a variety of shapes can be implemented simply by upgrading the algorithms, without having to modify the data base (see figure 1.9).

Figure 1.9 Data Flow when Using a 3D Algorithm

#### (2) Drawing System Upgrading

The Q2SD has been developed as a member of the Q Series, enabling the user to select the most appropriate model from the series for a particular application. The user's drawing system can also be upgraded as necessary by changing the Q2SD or CPU combination.

#### Renesas

#### (3) Consistency of Application Interface

The Q2SD's carefully selected drawing commands are of four kinds: four-vertex screen drawing, line drawing, work screen drawing, and work line drawing. This makes it possible to reduce the parts dependent upon drawing commands within an application, and so achieve a more consistent interface between applications.

# **1.2** A List of Specifications

Table 1.1 summarizes the specifications of the Q2SD.

# Table 1.1 A List of Specifications

| Item                 |                                                                                                  | Function/Performance                                                                                              |  |  |

|----------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Drawing              | Drawing performance                                                                              | Polygon drawing performance $(20 \times 25 \text{ pixels})$ :<br>91,000/sec (2-screen composite mode: 60,000/sec) |  |  |

|                      |                                                                                                  | Line drawing performance (10 pixels): 1,200,000/sec (2-screen composite mode: 400,000/sec)                        |  |  |

|                      | Color representation                                                                             | Source: 1/8/16 bits/pixel; drawing: 8/16 bits/pixel; work: binary                                                 |  |  |

|                      | Drawing commands                                                                                 | 4-vertex screen drawing, line drawing, work screen drawing, work line drawing                                     |  |  |

|                      | Register setting commands                                                                        | Current pointer setting, local offset setting, clipping, specific address-mapped register setting                 |  |  |

|                      | Sequence control commands                                                                        | Jump, subroutine, vertical blanking interval wait, no operation, display list end                                 |  |  |

| Display<br>functions | Sample screen sizes                                                                              | $320\times240,400\times240,480\times240,640\times480,\text{NTSC},$ PAL, etc.                                      |  |  |

|                      | CRT scanning system                                                                              | Non-interlace, interlace, interlace sync & video                                                                  |  |  |

|                      | External synchronization                                                                         | Master, TV synchronization                                                                                        |  |  |

|                      | Color palette                                                                                    | Simultaneous display of 256 colors out of 260,000                                                                 |  |  |

|                      | Cursors                                                                                          | Two cursors, $32 \times 32$ pixels, display color selectable from color palette                                   |  |  |

|                      | Display screen                                                                                   | Foreground, background, and video screens                                                                         |  |  |

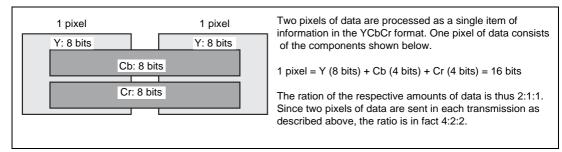

| Video input          |                                                                                                  | 8-bit multiplexed YCbCr 4:2:2 digital input                                                                       |  |  |

| System               | Drawing system<br>internal operation<br>maximum clock<br>frequency (Q2SD<br>operating frequency) | 66 MHz $\times$ 1, 33 MHz $\times$ 2, 16.5 MHz $\times$ 4 (using multiplier)                                      |  |  |

|                      | Display system internal<br>operation clock frequency<br>(display operation clock<br>frequency)   | Operating frequency/2 (max. 33 MHz)                                                                               |  |  |

| Item                                   |                 |                                     | Function/Performance                                                                                                                                      |  |  |

|----------------------------------------|-----------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System                                 |                 | Command/<br>data transfer           | DMA transfer (single address, dual address), or performed by SuperH                                                                                       |  |  |

|                                        |                 | $YUV \rightarrow RGB$               | 16-bit input, 4:2:2 (8 bits each for Y, U, V)                                                                                                             |  |  |

|                                        |                 | conversion                          | 16-bit output (R: 5, G: 6, B: 5 bits)                                                                                                                     |  |  |

|                                        |                 | $\Delta YUV \rightarrow RGB$        | 8-bit input (4 bits each for d-Y, d-U, d-V)                                                                                                               |  |  |

|                                        |                 | conversion                          | 16-bit output (R: 5, G: 6, B: 5 bits)                                                                                                                     |  |  |

|                                        |                 | Interrupt output                    | TV sync signal error flag, frame flag, DMA flag,<br>command error flag, vertical blanking flag, trap flag,<br>command suspend flag, drawing break flag    |  |  |

|                                        |                 | SuperH<br>supported                 | Can be allocated to the SRAM area of the SuperH with 3.3-V power supply.                                                                                  |  |  |

|                                        | UGM<br>interfac | 32/16-bit-<br>ce bus-width<br>SDRAM | Minimum 16 Mbits (choice of one 16-Mbit (×16)<br>memory, two parallel 16-Mbit (×16) memories, one 64-<br>Mbit (×16) memory, or one 64-Mbit (×32) memory)  |  |  |

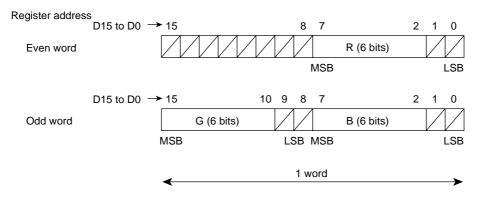

|                                        | DAC             | Analog RGB<br>output                | 6-bit resolution for each of R, G, and B (8-bit resolution<br>for each of R, G, and B for video stored in UGM in<br>YCbCr format)                         |  |  |

| Process/package                        |                 |                                     | 0.35-μ CMOS/176-pin LQFP                                                                                                                                  |  |  |

| Power supply voltage/temperature range |                 | temperature                         | $3.3 V \pm 0.3 V/0^{\circ}C$ to 70°C<br>(Details of a -40°C to 85°C special-specification model<br>are also available from Hitachi sales representatives) |  |  |

#### Table 1.1 Summary of Q2SD Functions (cont)

## **1.3 Block Diagram**

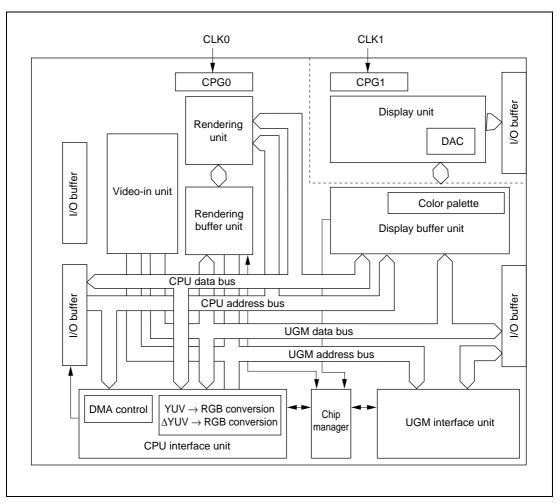

Figure 1.10 shows a block diagram of the Q2SD. The functions of the various blocks in figure 1.10 are as follows.

• CPU interface unit

Performs UGM access by the CPU, Q2SD on-chip register accesses by the CPU, and UGM write access by the external DMAC. Converts input data  $\Delta$ YUV (260,000 colors) or YUV (260,000 colors) to RGB data (60,000 colors), and stores it in the UGM. Interrupts are output.

• UGM interface unit

Controls the connection relating to the SDRAM that is used for the UGM.

• Chip manager

Controls the operation of each unit in the UGM architecture.

Rev. 2.0, 09/02, page 10 of 366

• Clock generator (CPG0, CPG1)

The Q2SD operating clock is generated in the CPG0, and it is provided to each unit excluding the display unit. The display dot clock is generated in the CPG1 and it is provided to the display unit.

• Rendering unit

Performs fetching and interpretation of the display list in the UGM.

• Rendering buffer unit

Buffers data and addresses between the rendering unit and the UGM to improve the efficiency to the UGM access in the rendering unit.

• Display unit

Generates the CRT control signals and outputs analog RGB signals.

• Display buffer unit

Composes the foreground, background, video and cursor screens. Accesses data to be displayed in synchronization with the display timing. By the color palette (6 bits per color), converts 8-bits/pixel data to display data of 256 colors out of 262,144 to the RGB data, based on the color conversion table, and when the video screen data is the YCbCr data, it is converted to the RGB data.

• Video-in unit

Fetches 4:2:2 YCbCr data and stores it in the UGM in YCbCr or RGB format. The image data can also be stored with reduction.

Figure 1.10 Internal Block Diagram

# 1.4 Processing States

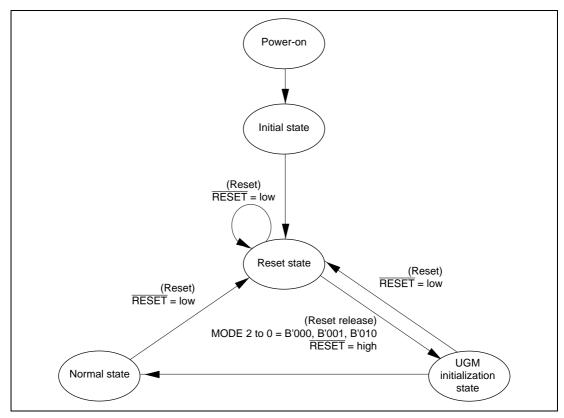

The Q2SD has five main processing states: the power-on state, initial state, reset state, UGM initialization state, and normal states. Figure 1.11 shows the state transitions.

Figure 1.11 State Transition Diagram

#### 1.4.1 Power On

For details, refer to section 6.1, Power-On Sequence.

#### **1.4.2** Initial States (when Specified Power is Supplied)

Initial states are undefined.

Registers:UndefinedI/O pins:UndefinedOutput pins:Low/high-level output

#### Renesas

#### **1.4.3** Reset State (when Low Level is Input to **RESET** Pin)

Table 1.2 shows the Q2SD pin states immediately after a reset. UGM refreshing is not performed when the  $\overline{\text{RESET}}$  pin is low. The levels of pins MODE2 to MODE0 are latched at the rising edge of the  $\overline{\text{RESET}}$  pin. At this time, they must be fixed at a level of B'000, B'001, or B'010. Other levels must not be used because those setting makes the Q2SD enter in test mode.

| I/O Pins    | Input state                     | D0 to D15*, VSYNC/EXVSYNC,<br>HSYNC/ EXHSYNC, ODDF                    |  |  |

|-------------|---------------------------------|-----------------------------------------------------------------------|--|--|

|             | Output state (low-level output) | MD0 to MD31                                                           |  |  |

| Output Pins | Low-level output                | DISP, CDE                                                             |  |  |

|             | High-level output               | DREQ, IRL, WAIT                                                       |  |  |

|             | Low/high-level output           | CSYNC, MA0 to MA13, MWE, MRAS, MCAS, LDQM0, LDQM1, UDQM0, UDQM1, MCLK |  |  |

| Table 1.2 | Pin ( | States | After | Reset |

|-----------|-------|--------|-------|-------|

|           |       |        |       |       |

Note: Pins D0 to D15 are in the output state when  $\overline{RD}$  is a low-level input.

#### 1.4.4 UGM Initialization State

Initializes the SDRAM which is used for the UGM. For details on initialization, refer to section 6.6, SDRAM Mode Register Values for UGM Set by Q2SD.

#### 1.4.5 Normal Operating State

In the normal operating state, the Q2SD executes drawing commands and performs display control.

# Section 2 Pins

# 2.1 Pin Configuration

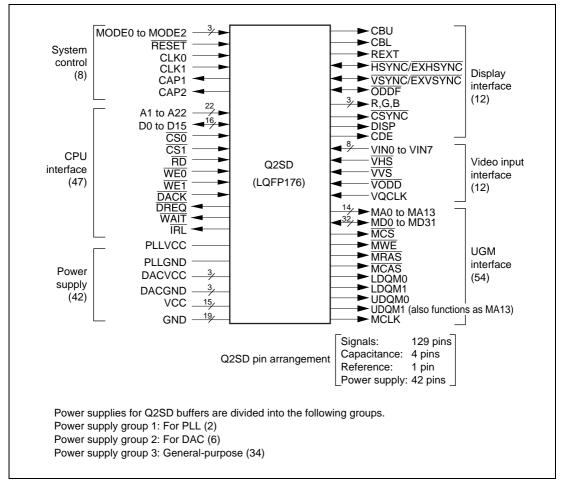

Figure 2.1 Pin Configuration

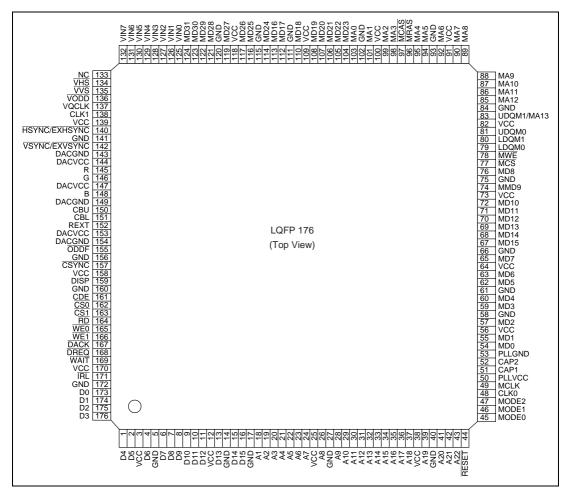

### 2.2 Pin Arrangement

Figure 2.2 shows the pin arrangement of the Q2SD.

Figure 2.2 Pin Arrangement

# 2.3 **Pin Functions**

Table 2.1 shows the Q2SD pin functions.

# Table 2.1Pin Functions

| Туре           | Symbol | Pin No. | I/O    | Function                                        |

|----------------|--------|---------|--------|-------------------------------------------------|

| System control | MODE0  | 45      | Input  | Operating mode pin 0                            |

|                | MODE1  | 46      | Input  | Operating mode pin 1                            |

|                | MODE2  | 47      | Input  | Operating mode pin 2                            |

|                | CLK0   | 48      | Input  | Q2SD operating clock                            |

|                | CLK1   | 138     | Input  | Display operating clock                         |

|                | RESET  | 44      | Input  | Reset                                           |

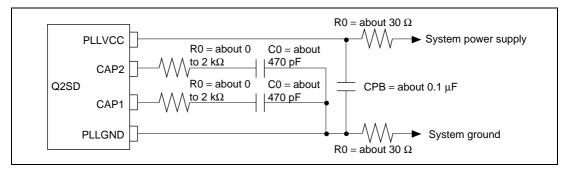

|                | CAP1   | 51      | Output | Multiplication circuit external capacitance pin |

|                | CAP2   | 52      | Output | Multiplication circuit external capacitance pin |

| CPU interface  | A1     | 18      | Input  | CPU address 1                                   |

|                | A2     | 19      | Input  | CPU address 2                                   |

|                | A3     | 20      | Input  | CPU address 3                                   |

|                | A4     | 21      | Input  | CPU address 4                                   |

|                | A5     | 22      | Input  | CPU address 5                                   |

|                | A6     | 23      | Input  | CPU address 6                                   |

|                | A7     | 24      | Input  | CPU address 7                                   |

|                | A8     | 26      | Input  | CPU address 8                                   |

|                | A9     | 28      | Input  | CPU address 9                                   |

|                | A10    | 29      | Input  | CPU address 10                                  |

|                | A11    | 30      | Input  | CPU address 11                                  |

|                | A12    | 31      | Input  | CPU address 12                                  |

|                | A13    | 32      | Input  | CPU address 13                                  |

|                | A14    | 33      | Input  | CPU address 14                                  |

|                | A15    | 34      | Input  | CPU address 15                                  |

|                | A16    | 35      | Input  | CPU address 16                                  |

|                | A17    | 36      | Input  | CPU address 17                                  |

|                | A18    | 37      | Input  | CPU address 18                                  |

|                | A19    | 39      | Input  | CPU address 19                                  |

|                | A20    | 41      | Input  | CPU address 20                                  |

| Туре              | Symbol | Pin No. | I/O    | Function                           |

|-------------------|--------|---------|--------|------------------------------------|

| CPU interface     | A21    | 42      | Input  | CPU address 21                     |

|                   | A22    | 43      | Input  | CPU address 22                     |

|                   | D0     | 173     | I/O    | CPU data 0                         |

|                   | D1     | 174     | I/O    | CPU data 1                         |

|                   | D2     | 175     | I/O    | CPU data 2                         |

|                   | D3     | 176     | I/O    | CPU data 3                         |

|                   | D4     | 1       | I/O    | CPU data 4                         |

|                   | D5     | 2       | I/O    | CPU data 5                         |

|                   | D6     | 4       | I/O    | CPU data 6                         |

|                   | D7     | 6       | I/O    | CPU data 7                         |

|                   | D8     | 7       | I/O    | CPU data 8                         |

|                   | D9     | 8       | I/O    | CPU data 9                         |

|                   | D10    | 9       | I/O    | CPU data 10                        |

|                   | D11    | 10      | I/O    | CPU data 11                        |

|                   | D12    | 11      | I/O    | CPU data 12                        |

|                   | D13    | 13      | I/O    | CPU data 13                        |

|                   | D14    | 15      | I/O    | CPU data 14                        |

|                   | D15    | 16      | I/O    | CPU data 15                        |

|                   | CS0    | 162     | Input  | Chip select 0 (UGM)                |

|                   | CS1    | 163     | Input  | Chip select 1 (internal registers) |

|                   | RD     | 164     | Input  | Read strobe                        |

|                   | WE0    | 165     | Input  | Write pulse 0 (lower)              |

|                   | WE1    | 166     | Input  | Write pulse 1 (upper)              |

|                   | DACK   | 167     | Input  | DMA acknowledge                    |

|                   | DREQ   | 168     | Output | DMA request                        |

|                   | WAIT   | 169     | Output | CPU wait                           |

|                   | IRL    | 171     | Output | Interrupt request                  |

| Display interface | e CBU  | 150     | Output | DAC external capacitance pin       |

|                   | CBL    | 151     | Output | DAC external capacitance pin       |

|                   | REXT   | 152     | Output | DAC external reference pin         |

|                   | R      | 145     | Output | Display data analog output R       |

| Туре              | Symbol            | Pin No. | I/O    | Function                                                      |

|-------------------|-------------------|---------|--------|---------------------------------------------------------------|

| Display interface | G                 | 146     | Output | Display data analog output G                                  |