## **DJT090A0X43-SRPZ: Non-Isolated DC-DC**

7.0 to 14.4 $V_{DC}$  input; 0.5 to  $2V_{DC}$  output; 90A output current

The DJT090A0X43-SRPZ Digital DLynxII<sup>™</sup> power modules are non-isolated dc-dc converters that can deliver up to 90A of output current. These modules operate over a 7 to 14.4V<sub>DC</sub> input range and provide a precisely regulated output voltage from 0.5 to 2V<sub>DC</sub>. The output voltage is programmable via an external resistor and/or PMBus control. Features include a digital interface using the PMBus protocol, remote On/ Off, adjustable output voltage, Power Good signal and overcurrent. overvoltage and overtemperature protection. The module also includes a real time compensation loop that allows optimizing the dynamic response of the converter to match the load with reduced amount of output capacitance leading to savings on cost and PWB area.

### **Application**

- High current voltage rails for ASICs/High-Performance

Processors

- High-Current FPGA Power (e.g. Xilinx, Intel)

- High-Performance ARM Processor Power

- Networking Processors (e.g. Broadcom, Marvell, NXP)

- Artificial intelligence (AI) processors and applications

- Distributed power architectures

- Intermediate bus voltage applications

- Telecommunications equipment

- Servers and storage applications

- Networking equipment

- Industrial equipment

- Test and Measurement equipment

#### **Features**

- Wide Input voltage range: 7.0 to 14.4V<sub>DC</sub>

- Digital output voltage programming 0.5 to 2V<sub>DC</sub>

- Delivers up to 90A output current

- Paralleling up to 8 units, 720A, interleaving and fault spreading

- A single cycle response (ASCR) charge mode controller provides fast transient response, reduced output capacitance and increased stability

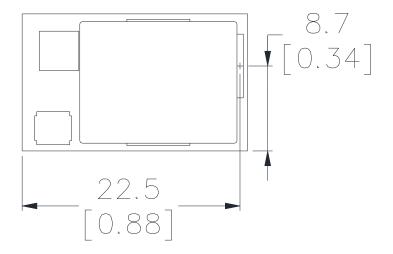

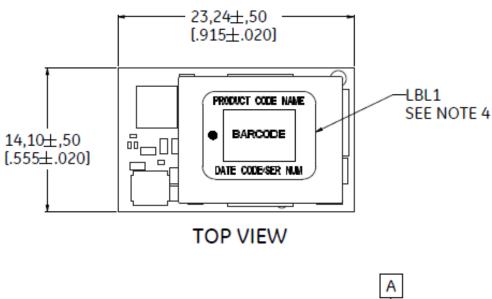

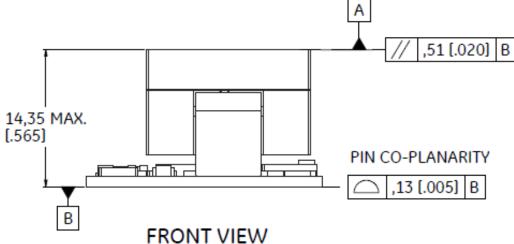

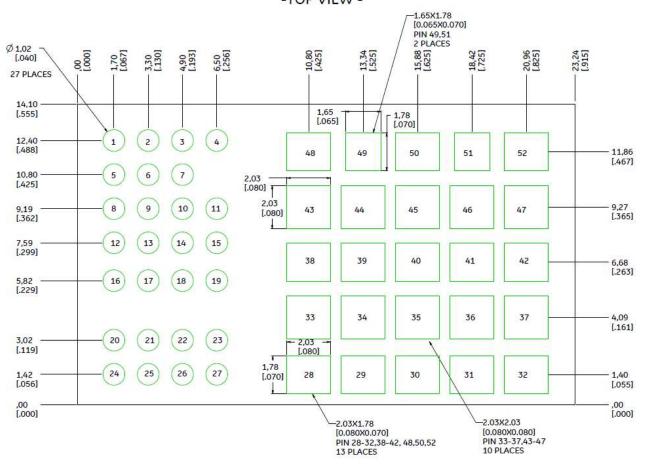

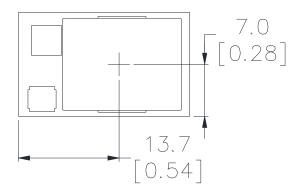

- 328mm² (23.24x14.1mm), height 14.35mm MAX

- 0.508inch<sup>2</sup> (0.915x0.555inch), height 0.565inch MAX

- Output voltage setpoint accuracy +/-0.5% (0 to 85°C)

- Digital telemetry and control with PMBus 1.3

- Frequency synchronization

- Tracking / sequencing

- Protections: OVP, UVP, OCP, OTP

- Remote On/Off, positive logic

- Cycle by cycle output OCP/UCP

- Black Box fault reporting with parametric capture

- Wide operating temperature range -40°C to 85°C

- UL\* 62368-1, 2nd Ed. Recognized, and TUV (EN62368-1, 2nd Ed.) Licensed

- ISO\*\* 9001 and ISO 14001 certified manufacturing facilities

- Compliant to RoHS II EU "Directive 2011/65/EU" and amended "Directive (EU) 2015/863"

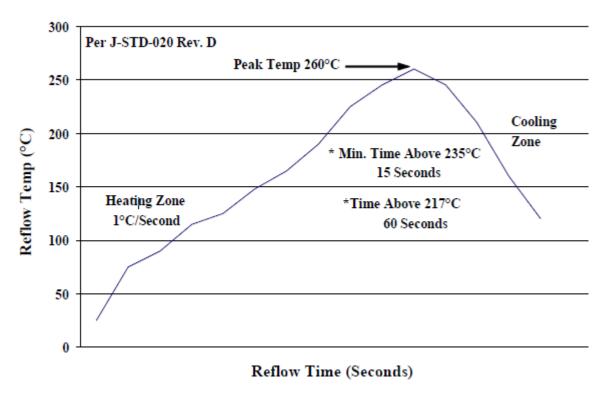

- Compatible in a Pb-free or SnPb reflow environment

- Compliant to IPC-9592 (Sept. 2008), Category 2, Class I, Class II pending

## **Electrical Specifications**

### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only, functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect the device reliability. It is for example only.

| Parameter                                                      | Device    | Min  | Max | Unit |

|----------------------------------------------------------------|-----------|------|-----|------|

| Input Voltage (Continuous)                                     | $V_{in}$  | -0.3 | 15  | V    |

| CLK, DATA, SMBALERT, SYNC, ON/OFF, PG, DDC, V5P, SEQ, VS+, VS- |           | -0.3 | 6   | V    |

| VSET/SA, V1P5, ISHARE Operating Ambient Temperature            | $T_A$     | -40  | 85  | °C   |

| (see Thermal Considerations section)                           | • •       | 10   | 00  | · ·  |

| Storage Temperature                                            | $T_{stg}$ | -55  | 125 | °C   |

#### CAUTION: This power module is not internally fused. An input line fuse must always be used.

This power module can be used in a wide variety of applications, ranging from simple standalone operation to an integrated part of sophisticated power architecture. To preserve maximum flexibility, internal fusing is not included, however, to achieve maximum safety and system protection, always use an input line fuse. The safety agencies require a fuse with a maximum rating of 35A (see Safety Considerations section). Based on the information provided in this Data Sheet on inrush energy and maximum dc input current, the same type of fuse with a lower rating can be used. Refer to the fuse manufacturer's Data Sheet for further information.

### **Recommended Operating Conditions**

| Parameter                                                       | Symbol                | Min | Nominal | Max  | Unit |

|-----------------------------------------------------------------|-----------------------|-----|---------|------|------|

| Input Voltage (continuous)                                      | $V_{in} \ V_{in,nom}$ | 7   | 12      | 14.4 | V    |

| Output voltage                                                  | Vo                    | 0.5 | 1.2     | 2    | V    |

| Output current (continuous), $V_o = V_{o, min}$ to $V_{o, max}$ | l <sub>out</sub>      | 0   |         | 90   | Α    |

| CLK, DATA, SMBALERT, SYNC, ON/OFF, PG, DDC, V5P, SEQ, VS+, VS-  |                       |     |         | 5.0  | V    |

# **Electrical Specifications**

Unless otherwise indicated, specifications apply overall operating input voltage, resistive load, and temperature conditions.

| Parameter                                                                                                                                                                                                                    | Condition                     | Symbol                    | Min  | Typical | Max  | Unit               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|------|---------|------|--------------------|

| Operating Input Voltage                                                                                                                                                                                                      | All                           | $V_{in}$                  | 7    | 12      | 14.4 | Vdc                |

| Maximum Input Current (V <sub>in</sub> =7V to 14V, I <sub>o</sub> =I <sub>o, max</sub> )                                                                                                                                     | All                           | I <sub>in, max</sub>      |      |         | 32   | Adc                |

| Input No Load Current $(V_{in} = 12V, I_o = 0, module enabled)$                                                                                                                                                              | V <sub>o, set</sub> = 0.5 Vdc | I <sub>in, no load</sub>  |      | 113     |      | mA                 |

| Input No Load Current<br>(V <sub>in</sub> = 12V, I <sub>o</sub> = 0, module enabled)                                                                                                                                         | V <sub>o, set</sub> = 2.0 Vdc | I <sub>in, no load</sub>  |      | 177     |      | mA                 |

| Input Stand-by Current (V <sub>in</sub> = 12V, module disabled)                                                                                                                                                              | All                           | I <sub>in, stand-by</sub> |      | 60      |      | mA                 |

| Inrush Transient                                                                                                                                                                                                             | All                           | l²t                       |      |         | 0.1  | A <sup>2</sup> s   |

| Input Reflected Ripple Current, peak-to-peak (5Hz to 20MHz, $1\mu$ H source impedance; $V_{in}$ =7V to $14.4V_{,i}$ I <sub>0</sub> = I <sub>0,max</sub> ; C <sub>in</sub> = 3 x 0.1uF    4 x 10uF    10 x 22uF    4 x 470uF) | All                           |                           |      | 25      | 50   | mA <sub>pk</sub> - |

| Input Ripple Rejection (120Hz)                                                                                                                                                                                               | All                           |                           |      | -43     |      | dB                 |

| Output Voltage Set-point accuracy over entire output range                                                                                                                                                                   | All                           | $V_{o,set}$               | -0.5 |         | +0.5 | $%V_{o,set}$       |

| 0 to 85°C, V <sub>o</sub> = over entire range<br>-40 to 85°C, V <sub>o</sub> = over entire range                                                                                                                             | All                           | $V_{\text{o, set}}$       | -0.7 |         | +0.7 | $%V_{o,set}$       |

| Voltage Regulation <sup>1</sup> Line Regulation (V <sub>in</sub> =V <sub>in, min</sub> to V <sub>in, max</sub> )                                                                                                             | All                           |                           |      | 3       |      | mV                 |

| Load Regulation (I <sub>o</sub> = I <sub>o, min</sub> to I <sub>o, max</sub> )                                                                                                                                               | All                           |                           |      | 3       |      | mV                 |

<sup>&</sup>lt;sup>1</sup>Worst case Line and load regulation data, all temperatures, from design verification testing as per IPC9592.

# **Electrical Specifications (continued)**

Unless otherwise indicated, specifications apply overall operating input voltage, resistive load, and temperature conditions. See Feature Descriptions for additional information.

| Parameter                                                                                                     | Device                       | Symbol               | Min  | Typical | Max   | Unit                    |

|---------------------------------------------------------------------------------------------------------------|------------------------------|----------------------|------|---------|-------|-------------------------|

| Adjustment Range (selected by an external resistor)                                                           | All                          | Vo                   | 0.6  |         | 1.8   | Vdc                     |

| PMBus Adjustable Output Voltage                                                                               | All                          | Vo                   | 0.5  |         | 2.0   | Vdc                     |

| PMBus Output Voltage Adjustment Step Size                                                                     | All                          |                      |      | ±0.05   |       | %V <sub>o, set</sub>    |

| Remote Sense Range                                                                                            | All                          |                      |      |         | 0.1   | Vdc                     |

| Output Ripple and Noise on nominal output                                                                     |                              |                      |      |         |       |                         |

| $(V_{in} = 12V, V_o = V_{o, min} \text{ to } V_{o, max} \text{ and } I_o = I_{o, min} \text{ to } I_{o, max}$ |                              |                      |      | 17      |       | m\/                     |

| $C_o = 3 \times 0.1 \text{uF}    4 \times 22 \text{uF}    10 \times 47 \text{uF}    3 \times 680 \text{uF}$   | All                          |                      |      | 4.2     |       | $mV_{pk-pk}$ $mV_{rms}$ |

| Peak-to-Peak (5Hz to 20MHz bandwidth)                                                                         |                              |                      |      | 4.2     |       | IIIV <sub>rms</sub>     |

| RMS (5Hz to 20MHz bandwidth)                                                                                  |                              |                      |      |         |       |                         |

| External Capacitance                                                                                          |                              |                      |      |         |       |                         |

| $ESR \geq 0.15 \; m\Omega$                                                                                    | All                          | C <sub>o</sub>       | 2600 |         | 20000 | μF                      |

| ESR ≥ 10 mΩ                                                                                                   | All                          | C <sub>o</sub>       | 2600 |         | 20000 | μF                      |

| Output Current (in either sink or source mode)                                                                | All                          | I <sub>o,max</sub>   |      |         | 90    | A <sub>dc</sub>         |

| Output Current Limit Inception (Hiccup Mode),                                                                 | All                          | 1                    |      | 101     |       | Α                       |

| see current measurement accuracy I <sub>ACC</sub>                                                             | All                          | I <sub>o, lim</sub>  |      | 101     |       | Α                       |

|                                                                                                               | $V_{o, set} = 0.5Vdc$        | η                    |      | 80.53   |       | %                       |

| Efficiency                                                                                                    | $V_{o, set} = 0.8Vdc$        | η                    |      | 85.64   |       | %                       |

| $(V_{in}= 12Vdc, T_A=25^{\circ}C, I_o=I_{o, max}, V_o=V_{o, set})$                                            | V <sub>o, set</sub> = 1.2Vdc | η                    |      | 88.51   |       | %                       |

|                                                                                                               | $V_{o, set} = 2Vdc$          | η                    |      | 91.15   |       | %                       |

| Switching Frequency                                                                                           | All                          | $f_sw$               |      | 353     |       | kHz                     |

| Frequency Synchronization                                                                                     |                              |                      |      |         |       |                         |

| Synchronization Frequency Range                                                                               | All                          |                      | -4   |         | 4     | % f <sub>sw</sub>       |

| High-Level Input Voltage                                                                                      | All                          | $V_{IH}$             | 2.0  |         |       | V                       |

| Low-Level Input Voltage                                                                                       | All                          | $V_{IL}$             |      |         | 0.4   | V                       |

| Minimum Pulse Width, SYNC                                                                                     | All                          | $t_{SYNC}$           | 200  |         |       | ns                      |

| Maximum SYNC rise time                                                                                        | All                          | t <sub>SYNC_SH</sub> |      |         | 10    | ns                      |

Unless otherwise indicated, specifications apply overall operating input voltage, resistive load, and temperature conditions. See Feature Descriptions for additional information.

| Parameter                                                                                              | Device | Symbol               | Min  | Typical    | Max  | Unit         |

|--------------------------------------------------------------------------------------------------------|--------|----------------------|------|------------|------|--------------|

| On/Off Signal Interface                                                                                |        |                      |      |            |      |              |

| Logic High (Module ON)                                                                                 |        |                      |      |            |      |              |

| Input High Current                                                                                     | All    | I <sub>IH</sub>      |      |            | 1    | uA           |

| Input High Voltage                                                                                     | All    | V <sub>IH</sub>      | 2.1  |            | 5    | V            |

| Logic Low (Module OFF)                                                                                 |        |                      |      |            |      |              |

| Input Low Current                                                                                      | All    | I <sub>IL</sub>      |      |            | 1    | uA           |

| Input Low Voltage                                                                                      | All    | V <sub>IL</sub>      | 0    |            | 0.8  | V            |

| Input Low Voltage Turn-On Delay and Rise Times                                                         | A.II   |                      |      |            | 0.5  |              |

| $(V_{in}=V_{in, nom}, I_o=I_{o, max}, V_o)$ to within ±1% of steady state)                             | All    | $V_{IL}$             | 0    |            | 0.5  | V            |

| Case I: On/OFF is enabled and then in put power is applied                                             |        |                      |      |            |      |              |

| (delay from instant at which $V_{in} = V_{in,min}$ until $Vo = 10\%$ of                                | All    | $T_{delay}$          |      | 15         |      | msec         |

| $V_{o,set}$                                                                                            |        |                      |      |            |      |              |

| Case II: Input power is applied for at least one second and                                            |        |                      |      |            |      |              |

| then the On/Off input is enabled (delay from instant at                                                | All    | $T_{delay}$          |      | 1.5        |      | msec         |

| which Von/Off is enabled until Vo = 10% of Vo, set)                                                    |        |                      |      |            |      |              |

| Output voltage Rise time                                                                               |        |                      |      |            | 125  |              |

| Time for Vo to rise from 10% of $V_{o, set}$ to 90% of $V_{o, set}$                                    | All    | Trise                |      | 10         | 125  | msec         |

| Output voltage Transient                                                                               |        |                      |      |            |      |              |

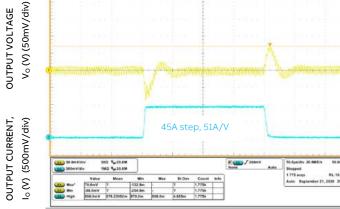

| $T_A = 25$ °C, $V_{in} = V_{in, min}$ to $V_{in, max}$ , ASCR setting = Default                        | All    |                      | -100 |            | +100 | mV           |

| $I_0 = 25\% - 75\%$ of $I_{0, max}$ , slew rate = 10A/us                                               | All    |                      | -100 |            | .100 | 1117         |

| With or without maximum external capacitance                                                           |        |                      |      |            |      |              |

| Over Temperature Protection                                                                            | All    | $T_{OT}$             |      | 110        |      | °C           |

| (See Thermal Considerations section)                                                                   | All    | 101                  |      |            |      |              |

| PMBus Over Temperature Warning Threshold                                                               |        |                      |      |            |      |              |

| Tracking Accuracy ( $V_{in, min}$ to $V_{in, max}$ ; $I_{o, min}$ to $I_{o, max}$ ; $OV < V_{SEQ} < 0$ | All    | $T_{WARN}$           |      | 100        |      | °C           |

| Vo)                                                                                                    |        |                      |      |            |      |              |

| Power-Up: 2V/ms                                                                                        | All    | V <sub>SEQ</sub> –Vo |      |            | 100  | mV           |

| Power-Down: 2V/ms                                                                                      | All    | V <sub>SEQ</sub> –Vo |      |            | 200  | mV           |

| Input Undervoltage Lockout                                                                             |        |                      |      |            |      |              |

| Turn-on Threshold                                                                                      | All    |                      |      | 6.8        |      | Vdc          |

| Turn-off Threshold                                                                                     | All    |                      |      | 5.8        |      | Vdc          |

| Hysteresis                                                                                             | All    |                      |      | 1          |      | Vdc          |

| PMBus Adjustable Input Under Voltage Lockout Thresholds                                                | All    |                      | 5.8  | 6.8        |      | Vdc          |

| Input Overvoltage Lockout                                                                              |        |                      |      |            |      |              |

| Turn-on Threshold                                                                                      | All    |                      |      | 14.5       |      | Vdc          |

| Turn-off Threshold                                                                                     | All    |                      |      | 16         |      | Vdc          |

| Hysteresis                                                                                             | All    |                      |      | 1          |      | Vdc          |

| PMBus Adjustable Input Over Voltage Lockout Thresholds                                                 | All    |                      |      | 14.5       | 16   | Vdc          |

| Resolution of Adjustable Input Under Voltage Threshold                                                 | All    |                      |      | 8          |      | mV           |

| Overvoltage TH for PGOOD ON                                                                            | All    |                      |      | 90         |      | $%V_{o,set}$ |

| Overvoltage TH for PGOOD OFF                                                                           | All    |                      |      | 2.4        |      | V            |

| Undervoltage TH for PGOOD ON                                                                           | All    |                      |      | 90         |      | $%V_{o,set}$ |

| Undervoltage TH for PGOOD OFF                                                                          | All    |                      |      | 0.4        |      | V            |

| Pullup Resistance of PGOOD pin                                                                         | All    |                      |      | 10         |      | kΩ           |

| Sink current capability into PGOOD pin                                                                 | All    |                      | -100 |            | 100  | nA           |

| Calculated MTBF                                                                                        |        |                      |      | 00.000     |      |              |

| (I <sub>o</sub> =0.8I <sub>o,max</sub> T <sub>A</sub> =40°C) Telcordia Issue 3 Method 1 Case 3         | All    |                      |      | 28,032,732 |      | Hours        |

| Weight                                                                                                 | All    |                      |      | 12.7(0.45) |      | g(oz.)       |

|                                                                                                        |        |                      |      |            |      |              |

# Feature Interface Specifications

Unless otherwise indicated, specifications apply overall operating input voltage, resistive load, and temperature conditions. See Feature Descriptions for additional information.

| Parameter                                                                                                                                       | Conditions                       | Symbol                 | Min      | Typical | Max  | Unit       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------|----------|---------|------|------------|

| PMBus Signal Interface Characteristics                                                                                                          |                                  |                        |          |         |      |            |

| Input High Voltage (CLK, DATA)                                                                                                                  |                                  | $V_{IH}$               | 2.1      |         |      | V          |

| Input Low Voltage (CLK, DATA)                                                                                                                   |                                  | $V_{IL}$               |          |         | 8.0  | V          |

| Input high level current (CLK, DATA)                                                                                                            |                                  | I <sub>IH</sub>        | -1       |         | 1    | μΑ         |

| Input low level current (CLK, DATA)                                                                                                             |                                  | I <sub>IL</sub>        | -1       |         | 1    | μΑ         |

| Output Low Voltage (CLK, DATA, SMBALERT#)                                                                                                       | I <sub>OUT</sub> =2mA            | $V_{OL}$               |          |         | 0.5  | V          |

| Output high level open drain leakage current (DATA, SMBALERT#)                                                                                  | V <sub>OUT</sub> =3.6V           | I <sub>он</sub>        | -0.1     |         | 0.1  | μΑ         |

| PMBus Operating frequency range                                                                                                                 | Slave Mode                       | $F_PMB$                | 10       |         | 1000 | kHz        |

| Data hold time                                                                                                                                  | Receive Mode<br>Transmit<br>Mode | t <sub>HD:DAT</sub>    | 0<br>300 |         |      | ns         |

| Data setup time                                                                                                                                 |                                  | $t_{\text{SU:DAT}}$    | 250      |         |      | ns         |

| Measurement System Characteristics                                                                                                              |                                  |                        |          |         |      |            |

| Output current measurement range                                                                                                                |                                  | I <sub>RNG</sub>       | -300     |         | 300  | Α          |

| Output current measurement accuracy 25 to $85^{\circ}C^{1}$<br>$V_{in} = V_{in, min}$ to $V_{in, max}$ , $V_{o} = V_{o, min}$ to $V_{o, max}$   |                                  | I <sub>ACC</sub>       | -5       |         | +10  | % of<br>FL |

| Output current measurement accuracy -40 to $85^{\circ}C^{1}$ $V_{in}$ = $V_{in, min}$ to $V_{in, max}$ , $V_{o}$ = $V_{o, min}$ to $V_{o, max}$ |                                  | I <sub>ACC</sub>       | -5       |         | +20  | % of<br>FL |

| Temperature measurement accuracy @12Vin, 0°C to 85°C                                                                                            |                                  | $T_{ACC}$              |          | ±2      |      | °C         |

| V <sub>OUT</sub> measurement range                                                                                                              |                                  | $V_{OUT(rng)}$         | 0        |         | 2.5  | V          |

| V <sub>OUT</sub> measurement accuracy                                                                                                           |                                  | V <sub>OUT</sub> , ACC | -2       |         | 1    | %          |

<sup>&</sup>lt;sup>1</sup> Output current measurement accuracy is valid for I<sub>out</sub> >=15A

$<sup>^{\</sup>star}$   $\,$   $\mathit{UL}$  is a registered trademark of Underwriters Laboratories, Inc.  $\,$

$<sup>^{\</sup>dagger}~\textit{CSA}$  is a registered trademark of Canadian Standards Association.

<sup>&</sup>lt;sup>‡</sup> VDE is a trademark of Verband Deutscher Elektrotechniker e.V.

<sup>\*\*</sup> ISO is a registered trademark of the International Organization of Standards \* The PMBus name and logo are registered trademarks of the System Management Interface Forum (SMIF)

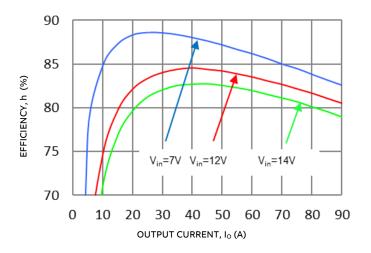

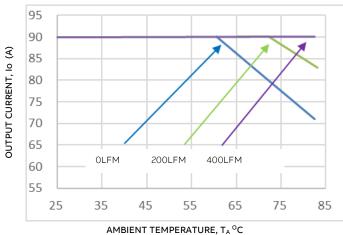

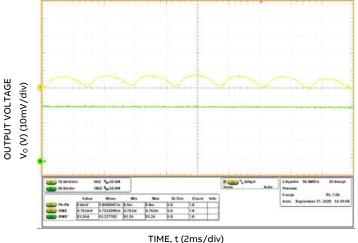

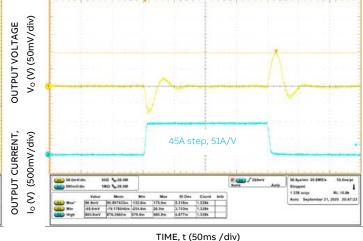

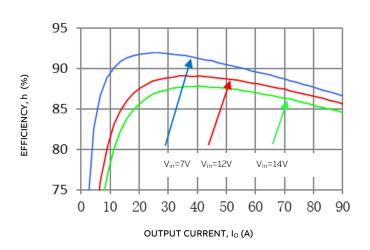

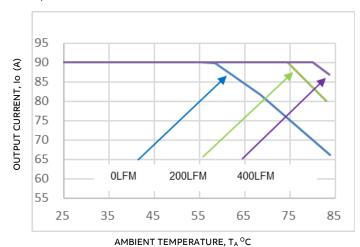

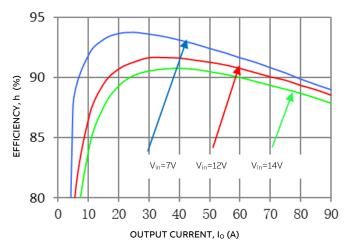

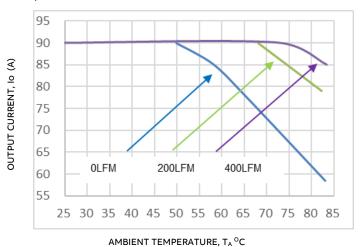

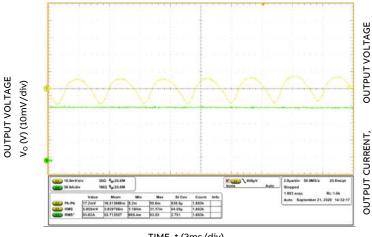

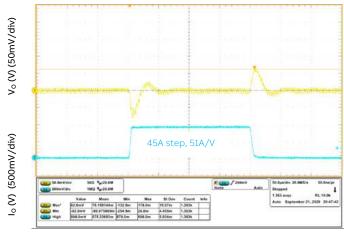

### **Characteristic Curves of 0.5V Output**

The following figures provide typical characteristics for the 90A at 12Vin/0.5Vo 25°C.

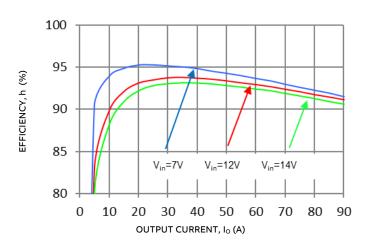

Figure 1. Converter Efficiency versus Output Current.

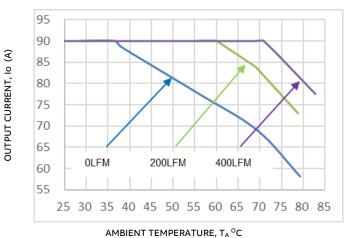

Figure 2. Derating Output Current versus Ambient Temperature and Airflow.

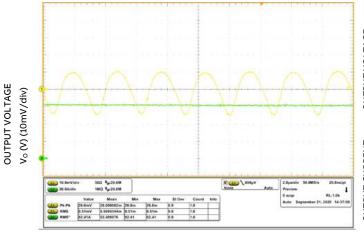

Figure 3. Typical output ripple and noise (C  $_{o}$  = 4 x 22uF + 12 x 47uF + 4 x 680uF,  $V_{\rm in}$  = 12V,  $I_{o}$  =  $I_{o,max}$  ).

Figure 4. Transient Response to Dynamic Load Change from 0% to 50% at  $12V_{in}$  10A/us ( $C_o$  = 4 x 22uF + 12 x 47uF + 4 x 680uF, ASCR Gain = 270, ASCR

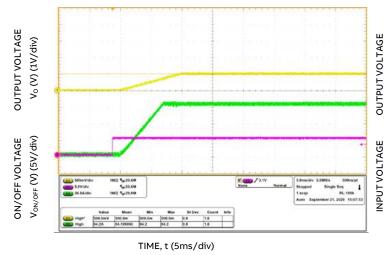

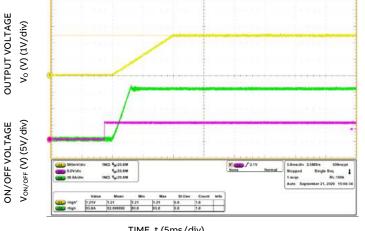

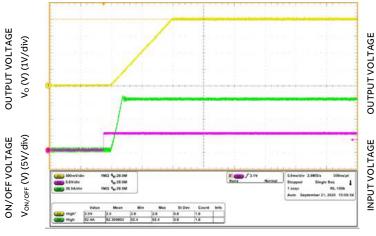

Figure 5. Typical Start-up Using On/Off Voltage ( $I_0 = I_{o,max}$ ).

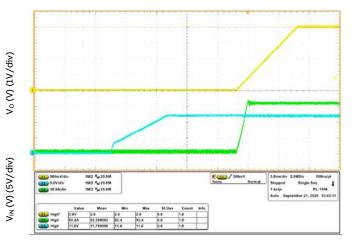

Figure 6. Typical Start-up Using Input Voltage ( $V_{in} = 12V$ ,  $I_o = I_{o,max}$ ).

age 7 Version 2.8

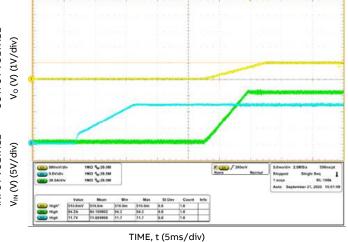

### **Characteristic Curves of 0.8V Output**

The following figures provide typical characteristics for the 90A at 12Vin/0.8Vo 25°C.

Figure 1. Converter Efficiency versus Output Current.

Figure 2. Derating Output Current versus Ambient Temperature and Airflow.

Figure 3. Typical output ripple and noise ( $C_o$  = 4 x 22uF + 12 x 47uF + 4 x 680uF,  $V_{in}$  = 12V,  $I_o$  =  $I_{o,max}$ ,).

Figure 4. Transient Response to Dynamic Load Change from 0% to 50% at  $12V_{in}$  10A/us ( $C_o$  = 4 x 22uF + 12 x 47uF + 4 x 680uF, ASCR Gain = 270, ASCR

Figure 5. Typical Start-up Using On/Off Voltage ( $I_o = I_{o,max}$ ).

Figure 6. Typical Start-up Using Input Voltage ( $V_{in} = 12V$ ,  $I_o = I_{o,max}$ ).

age 8 Version 2.8

### **Characteristic Curves of 1.2V Output**

The following figures provide typical characteristics for the 90A at 12Vin/1.2Vo 25°C.

Figure 1. Converter Efficiency versus Output Current.

Figure 2. Derating Output Current versus Ambient Temperature and Airflow.

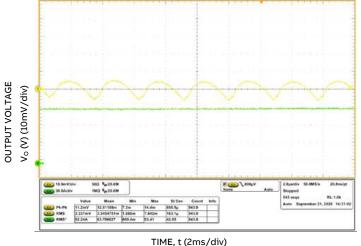

TIME, t (2ms/div)

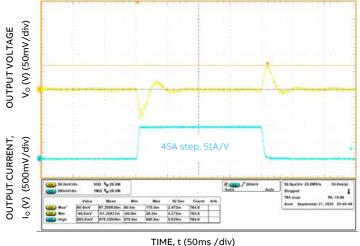

TIME, t (50ms /div)

Figure 3. Typical output ripple and noise ( $C_o = 4 \times 22 uF + 12 \times 47 uF + 4 \times 680 uF$ , V<sub>in</sub> = 12V, I<sub>o</sub> = I<sub>o,max</sub>, ).

Figure 4. Transient Response to Dynamic Load Change from 0% to 50% at 12V<sub>in</sub> 10A/us (C<sub>o</sub> = 4 x 22uF + 12 x 47uF + 4 x 680uF, ASCR Gain = 270, ASCR

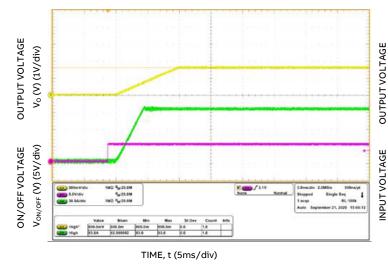

TIME, t (5ms/div)

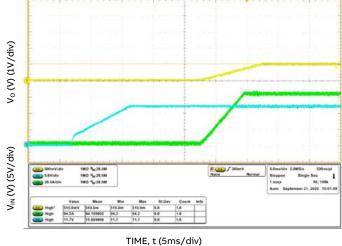

TIME, t (5ms/div)

Figure 5. Typical Start-up Using On/Off Voltage ( $I_o = I_{o,max}$ ).

Figure 6. Typical Start-up Using Input Voltage (Vin = 12V, Io = Io,max).

Version 2.8

### **Characteristic Curves of 2.0V Output**

The following figures provide typical characteristics for the 90A at 12Vin/2.0Vo 25°C.

Figure 1. Converter Efficiency versus Output Current.

Figure 2. Derating Output Current versus Ambient Temperature and Airflow.

TIME, t (2ms/div)

Figure 3. Typical output ripple and noise ( $C_o = 4 \times 22 uF + 12 \times 47 uF + 4 \times 680 uF$ ,

Figure 4. Transient Response to Dynamic Load Change from 0% to 50% at  $12V_{in}$  10A/us ( $C_o = 4 \times 22uF + 12 \times 47uF + 4 \times 680uF$ , ASCR Gain = 270, ASCR

TIME, t (50ms /div)

TIME, t (5ms/div)

TIME, t (5ms/div)

Figure 5. Typical Start-up Using On/Off Voltage ( $I_o = I_{o,max}$ ).

Figure 6. Typical Start-up Using Input Voltage ( $V_{in} = 12V$ ,  $I_o = I_{o,max}$ ).

$V_{in} = 12V$ ,  $I_o = I_{o,max}$ , ).

# Address and Output Voltage

Table I (0.6V-0.9V)

| Vo   |          | 0.6V    |         | 0.7V    |         | V8.0    |         | 0.9V    |         |

|------|----------|---------|---------|---------|---------|---------|---------|---------|---------|

| ADDR | Hex Code | Ra (kΩ) | Rb (kΩ) |

| 16   | 10       | 32.4    | 3.16    | 93.1    | 9.09    | 158     | 15.8    | 232     | 22.6    |

| 17   | 11       | 25.5    | 3.32    | 71.5    | 9.31    | 124     | 16.2    | 178     | 23.2    |

| 18   | 12       | 20.5    | 3.4     | 59      | 9.76    | 100     | 16.5    | 147     | 24.3    |

| 19   | 13       | 17.4    | 3.48    | 49.9    | 10      | 84.5    | 16.9    | 124     | 24.9    |

| 20   | 14       | 15      | 3.57    | 43.2    | 10.5    | 73.2    | 17.8    | 107     | 25.5    |

| 21   | 15       | 13.3    | 3.74    | 38.3    | 10.7    | 64.9    | 18.2    | 93.1    | 26.1    |

| 22   | 16       | 11.8    | 3.83    | 34      | 11      | 57.6    | 18.7    | 84.5    | 27.4    |

| 23   | 17       | 11      | 4.12    | 30.9    | 11.5    | 52.3    | 19.6    | 75      | 28      |

| 24   | 18       | 9.76    | 4.12    | 28      | 11.8    | 47.5    | 20      | 69.8    | 29.4    |

| 25   | 19       | 9.09    | 4.32    | 26.7    | 12.7    | 44.2    | 21      | 64.9    | 30.9    |

| 26   | 1A       | 8.25    | 4.42    | 23.7    | 12.7    | 41.2    | 22.1    | 59      | 31.6    |

| 27   | 1B       | 7.68    | 4.64    | 22.1    | 13.3    | 37.4    | 22.6    | 54.9    | 33.2    |

| 28   | 1C       | 7.32    | 4.87    | 21      | 14      | 34.8    | 23.2    | 52.3    | 34.8    |

| 30   | 1E       | 6.49    | 5.36    | 18.2    | 15      | 31.6    | 26.1    | 45.3    | 37.4    |

| 31   | 1F       | 6.04    | 5.62    | 17.4    | 16.2    | 30.1    | 28      | 42.2    | 39.2    |

| 32   | 20       | 5.76    | 5.9     | 16.5    | 16.9    | 28      | 28.7    | 41.2    | 42.2    |

| 33   | 21       | 5.49    | 6.19    | 15.4    | 17.4    | 27.4    | 30.9    | 38.3    | 43.2    |

| 34   | 22       | 5.11    | 6.49    | 14.7    | 18.7    | 25.5    | 32.4    | 36.5    | 46.4    |

| 35   | 23       | 4.99    | 6.98    | 14.3    | 20      | 24.3    | 34      | 35.7    | 49.9    |

| 36   | 24       | 4.87    | 7.68    | 13.7    | 21.5    | 23.2    | 36.5    | 33.2    | 52.3    |

| 37   | 25       | 4.52    | 7.87    | 13      | 22.6    | 22.6    | 39.2    | 32.4    | 56.2    |

| 38   | 26       | 4.42    | 8.66    | 12.4    | 24.3    | 21.5    | 42.2    | 30.9    | 60.4    |

| 39   | 27       | 4.22    | 9.31    | 12.1    | 26.7    | 20.5    | 45.3    | 30.1    | 66.5    |

| 47   | 2F       | 4.12    | 10.2    | 11.5    | 28.7    | 20      | 49.9    | 28.7    | 71.5    |

| 48   | 30       | 4.02    | 11.5    | 11      | 31.6    | 19.1    | 54.9    | 27.4    | 78.7    |

| 49   | 31       | 3.92    | 12.7    | 11      | 35.7    | 19.1    | 61.9    | 26.7    | 86.6    |

| 50   | 32       | 3.65    | 14      | 10.5    | 40.2    | 17.8    | 68.1    | 26.1    | 100     |

| 51   | 33       | 3.57    | 16.2    | 10      | 45.2    | 17.4    | 78.7    | 25.5    | 115     |

| 52   | 34       | 3.48    | 18.7    | 10      | 53.6    | 16.9    | 93.1    | 24.3    | 133     |

| 53   | 35       | 3.32    | 22.1    | 9.53    | 63.4    | 16.2    | 110     | 23.7    | 158     |

| 54   | 36       | 3.24    | 28      | 9.31    | 80.6    | 16.2    | 133     | 23.2    | 196     |

# Address and Output Voltage

Table II (1.0V-1.8V)

| ADDR<br>16<br>17<br>18<br>19<br>20<br>21 | Hex Code<br>10<br>11<br>12<br>13<br>14 | Ra (kΩ)<br>309<br>237<br>196<br>165 | Rb (kΩ)<br>30.1<br>30.9 | Ra (kΩ)<br>392<br>301 | Rb (kΩ)<br>38.3 | Ra (kΩ) | Rb (kΩ) | Ra (kΩ) | Rb (kΩ) |

|------------------------------------------|----------------------------------------|-------------------------------------|-------------------------|-----------------------|-----------------|---------|---------|---------|---------|

| 17<br>18<br>19<br>20<br>21               | 11<br>12<br>13                         | 237<br>196                          | 30.9                    |                       | 38.3            |         |         |         | , ,     |

| 18<br>19<br>20<br>21                     | 12<br>13                               | 196                                 |                         | 201                   | 50.5            | 475     | 47.5    | 576     | 57.6    |

| 19<br>20<br>21                           | 13                                     |                                     | 22.4                    | 3U1                   | 39.2            | 374     | 48.7    | 453     | 59      |

| 20<br>21                                 |                                        | 165                                 | 32.4                    | 249                   | 41.2            | 301     | 49.9    | 365     | 60.4    |

| 21                                       | 14                                     | 00                                  | 33.2                    | 210                   | 42.2            | 261     | 52.3    | 309     | 61.9    |

|                                          |                                        | 143                                 | 34                      | 182                   | 44.2            | 221     | 53.6    | 267     | 64.9    |

| 22                                       | 15                                     | 127                                 | 35.7                    | 158                   | 44.2            | 196     | 54.9    | 237     | 66.5    |

| <b></b>                                  | 16                                     | 113                                 | 36.5                    | 143                   | 46.4            | 178     | 57.6    | 215     | 69.8    |

| 23                                       | 17                                     | 102                                 | 38.3                    | 130                   | 48.7            | 158     | 59      | 191     | 71.5    |

| 24                                       | 18                                     | 93.1                                | 39.2                    | 118                   | 49.9            | 143     | 60.4    | 174     | 73.2    |

| 25                                       | 19                                     | 86.6                                | 41.2                    | 107                   | 51.1            | 133     | 63.4    | 165     | 78.7    |

| 26                                       | 1A                                     | 78.7                                | 42.2                    | 100                   | 53.6            | 124     | 66.5    | 150     | 80.6    |

| 27                                       | 1B                                     | 73.2                                | 44.2                    | 93.1                  | 56.2            | 113     | 68.1    | 140     | 84.5    |

| 28                                       | 1C                                     | 69.8                                | 46.4                    | 88.7                  | 59              | 107     | 71.5    | 130     | 86.6    |

| 29                                       | 1D                                     | 64.9                                | 48.7                    | 82.5                  | 61.9            | 100     | 75      | 121     | 90.9    |

| 30                                       | 1E                                     | 60.4                                | 49.9                    | 76.8                  | 63.4            | 95.3    | 78.7    | 115     | 95.3    |

| 31                                       | 1F                                     | 57.6                                | 53.6                    | 73.2                  | 68.1            | 90.9    | 84.5    | 110     | 102     |

| 32                                       | 20                                     | 54.9                                | 56.2                    | 69.8                  | 71.5            | 84.5    | 86.6    | 100     | 102     |

| 33                                       | 21                                     | 52.3                                | 59                      | 66.5                  | 75              | 82.5    | 93.1    | 100     | 113     |

| 34                                       | 22                                     | 49.9                                | 63.4                    | 63.4                  | 80.6            | 76.8    | 97.6    | 93.1    | 118     |

| 35                                       | 23                                     | 47.5                                | 66.5                    | 60.4                  | 84.5            | 75      | 105     | 88.7    | 124     |

| 36                                       | 24                                     | 45.3                                | 71.5                    | 57.6                  | 90.9            | 69.8    | 110     | 84.5    | 133     |

| 37                                       | 25                                     | 43.2                                | 75                      | 54.9                  | 95.3            | 69.8    | 121     | 84.5    | 147     |

| 38                                       | 26                                     | 42.2                                | 82.5                    | 53.6                  | 105             | 64.9    | 127     | 78.7    | 154     |

| 39                                       | 27                                     | 40.2                                | 88.7                    | 51.1                  | 113             | 63.4    | 140     | 75      | 165     |

| 47                                       | 2F                                     | 39.2                                | 97.6                    | 49.9                  | 124             | 60.4    | 150     | 73.2    | 182     |

| 48                                       | 30                                     | 37.4                                | 107                     | 46.4                  | 133             | 59      | 169     | 69.8    | 200     |

| 49                                       | 31                                     | 35.7                                | 118                     | 47.5                  | 154             | 57.6    | 187     | 68.1    | 221     |

| 50                                       | 32                                     | 34.8                                | 133                     | 44.2                  | 169             | 54.9    | 210     | 64.9    | 249     |

| 51                                       | 33                                     | 34                                  | 154                     | 42.2                  | 191             | 52.3    | 237     | 63.4    | 287     |

| 52                                       | 34                                     | 33.2                                | 178                     | 42.2                  | 226             | 51.1    | 274     | 61.9    | 332     |

| 53                                       | 35                                     | 31.6                                | 210                     | 40.2                  | 267             | 49.9    | 332     | 60.4    | 402     |

| 54                                       | 36                                     | 30.9                                | 267                     | 39.2                  | 340             | 48.7    | 412     | 57.6    | 499     |

### **Design Consideration**

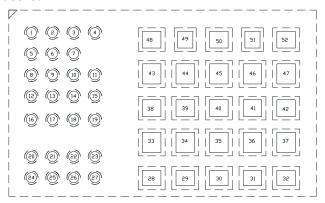

#### Address and Output Voltage Selection

The address and output voltage are set by a 1% resistor divider from V1P5 pin to SIG\_GND pin, the middle point of which is connected to the VSET pin. Varying combinations of resistor values will produce specific address and output voltage combinations. Refer to the Address and Output Voltage Table for possible combinations. Each DJT090A0X43-SRPZ module must have assigned a unique address. There are 32 available addresses and eight discrete output voltage settings from which to choose. The output voltage set point is not limited to the discrete values from the table and can be precisely adjusted by the VOUT\_COMMAND 0x21. See parameter precedence below.

Please be advised that if the address resistors are omitted, resistor pair combination is wrong, or the connection to V1P5, VSET or SIG\_GND pins is compromised, the controller will try to guess the intended address and output voltage settings, and therefor neither of them will be guaranteed. Compromised connections to module pins result in output voltage setting of 1.8V, unless VOUT\_COMMAND value is stored into the non-volatile memory of the module!

#### Start-up Procedure

When the input voltage rises above the internal controller's Power-ON Reset (POR) level, approximately 4.5V, the module initialization begins. VSET and SYNC pins are read. These values along with the nonvolatile FACTORY store are used to initialize the factory settings. Next, the contents of the DEFAULT store are read. Finally, the contents of the USER store are read. Upon completion of initialization routine, the PMBus communication is allowed and the controller begins to monitor the state of ON/OFF pin. Module initialization lasts approximately 15ms. The actual time depends on number of parameters stored into the non-volatile memory stores.

If a parameter is set by more than one mean, the value of the method with highest precedence wins. Assignment method precedence, from lowest to highest, is: pin-strap read, FACTORY store read, DEFAULT store read, USER store read and PMBus command write into volatile memory. The order of precedence could be changed by write protecting a parameter in the lower precedence store and enabling the password protection. See non-volatile memory manage-

ment for details.

#### ON/OFF

The DJT090A0X43-SRPZ is a positive ON/OFF logic power module. The module is ON when the ON/OFF pin is at "logic high" state, and OFF when it is at "logic ON\_OFF\_CONFIG low" state. See parameter procedure below.

The module could be turned ON and OFF from an external enable signal or by the OPERATION 0x01 command. Desired behavior is ON\_OFF\_CONFIG 0x02 command. Use of external enable signal guarantee precise turn-on timing when several modules operate in parallel. For repeatable turn on delay, the enable signal should be asserted high after the controller initialization has been completed and the input voltage is above its undervoltage warning limit. When enabling the device exclusively only via OPERATION command, it is recommended that the ON/OFF pin is tied to any SGND pin. See below Pin Assignment.

The ON/OFF pin is edge triggered to achieve fast turn-on and turn-off times. As a result, minimum enable high and enable low pulse widths must be observed to ensure correct operation. Enable low and enable high times shorter than minimums shown below may result in the module not responding to the trailing edge of the pulse. For example, applying enable high pulse shorter than the minimum pulse width, will turn the module ON, but may not turn the module OFF until a valid enable high pulse is applied to the ON/OFF pin.

TEN\_LOW > TOFF\_DELAY + TOFF\_FALL + 10.5ms

TEN\_HIGH > TON\_DELAY + TON\_RISE + TPOWER\_GOOD\_DELAY + 5.5ms

The delay between the transition edge of enable signal or the receipt of an OPERATION command and the beginning of the change of the output voltage may be adjusted using TON\_DELAY 0x60 and TOFF\_DELAY 0x64 commands. When the Ton-delay time is set to 0ms, the device begins its ramp after the internal circuitry has initialized which takes approximately  $100\mu s$  to complete.

The desired rising and falling slopes of the output voltage can be set by TON\_RISE 0x61 and TOFF\_FALL 0x65 commands. The Ton-rise time can be set to values less than 125ms; however, the Ton-rise time should be set to a value greater than 500µs to pre-

vent inadvertent fault conditions due to excessive inrush current. A lower Ton-rise time limit can be estimated using the formula:

TON\_RISE (MIN) = COUT EXT x VOUT / (N x ILIMIT)

where COUT EXT is the total output capacitance, VOUT is the output voltage, N is the number of phases in parallel, and ILIMIT is the current limit setting for the module(s).

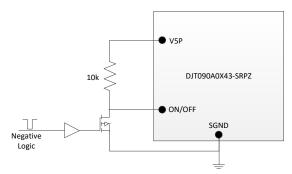

For negative logic control, user is recommended to setup external circuitry to control. See below example.

Figure 25. Negative Logic Setup

#### **Power Good**

The DJT090A0X43-SRPZ provides a power good signal, PG, that indicates the output voltage is within a specified tolerance of its target level and there are no fault conditions within the module. By default, the PG pin asserts if the output is within 10% of the target voltage. These limits and the configuration of the pin can be changed using POWER\_GOOD\_ON 0x5E and USER CONFIG 0xD1 commands.

A PG delay period is defined as the time from when all the conditions within the module for asserting PG are met to when the PG pin is actually asserted. This feature is commonly used instead of using an external reset controller to control external digital logic. The PG delay can be set using POWER\_GOOD\_DELAY 0xD4 command.

#### **Pre-bias Startup**

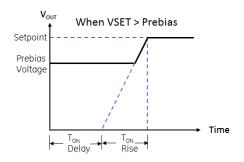

The DJT090A0X43-SRPZ supports pre-biased startup operation in single mode and multi-phase operation mode. An output pre-bias condition exists when an externally applied voltage is present on a power supply's output before the power supply's is ena-

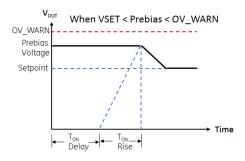

bled. Certain applications require that the POL converter does not sink current during start up, if a prebias condition exists at the output. The module's control IC provides pre-bias protection by sampling the output voltage before initiating an output ramp. If a pre-bias voltage lower than the desired output voltage is present after the TON DELAY 0x60 time the module starts switching with a duty cycle that matches the pre-bias voltage. This ensures that the ramp-up from the pre-bias voltage is monotonic. The output voltage is then ramped to the desired output voltage at the ramp rate set by the TON RISE 0x61 command. The actual output voltage ramp duration vary with the pre-bias voltage level, however the output is always in regulation after a time interval equal to the sum of TON DELAY 0x60 and TON RISE 0x61.

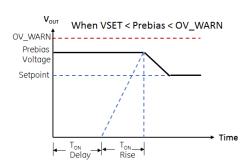

If a pre-bias voltage higher than the target voltage exists after the preconfigured TON\_DELAY 0x60 and TON\_RISE 0x61 time have completed, the DJT090A0X43-SRPZ starts switching with a duty cycle that matches the pre-bias voltage, and then ramped down to the desired output voltage. This ensures that the ramp-down from the pre-bias voltage is monotonic. If a pre-bias voltage higher than the VOUT\_OV\_WARN\_LIMIT 0x57 limit exists, the device does not initiate a turn-on sequence and stays off.

Figure 26a. Pre-bias Turn on

Figure 26b. Pre-bias Turn on

Page 14 Version 2.8

Figure 26c. Pre-bias Turn on

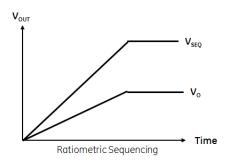

#### Voltage Tracking

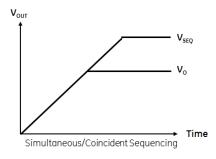

The DJT090A0X43-SRPZ integrates a tracking scheme that allows its output to track a voltage that is applied to the SEQ pin with no external components required. The SEQ pin is an analog input that, when tracking mode is enabled, configures the voltage applied to the SEQ pin to act as a reference for the module's output voltage regulation. The tracking functionality could be configured by TRACK\_CONFIG 0xE1 command.

There are two tracking modes – coincident and ratiometric. In coincident mode the tracking is configured to ramp module's output voltage at the same rate as the voltage applied to the SEQ pin until it reaches module's programmed output voltage. Usually the programmed output voltage of a module that is tracking another output voltage is lower than final level of the tracking signal. In ratiometric mode the module's output voltage is 50% of the signal applied to the SEQ pin. Different ratios may be implemented using external resistor divider.

Figure 27a. Tracking

Figure 27b. Tracking

When tracking mode is enabled the output takes the characteristics of the tracked voltage. Sequencing events like enabling and disabling of the module as well as the soft-start settings TON\_DELAY 0x60 and TON\_RISE 0x61 are ignored. If the module's tracking target limit is chosen, the changes to VOUT\_COMMAND 0x21 and output voltage margins are also ignored. POWER\_GOOD\_DELAY 0xD4 still applies.

The maximum tracking signal slew rate is 1V/ms. The device must be enabled at least 100µs before the tracking signal ramps up. If the voltage at the SEQ pin is greater than 0V prior to the module being enabled, the tracking voltage rises at the rate set by VOUT\_TRANSITION\_RATE 0x27 until it reaches the correct ratio of the tracked voltage. Until the output voltage is completed the initial ramp, the input tracking signal should not ramp up. To properly track during the turn-off ramp down, the TOFF\_DELAY 0x64 must be set be long enough to ensure that the module is turned off after the tracking input signal ramps down to the final value.

#### **Output Sequencing**

A group of DJT090A0X43-SRPZ modules can be configured to power up and down in predetermined sequences. This feature is especially useful when powering advanced processors, FPGAs, and ASICs. Each module, or group of modules operating in parallel, in the sequencing chain is informed for the module or the rail that need to power up before and the one that need to power up after. The ON/OFF pins of all modules in the sequencing group are tied together. When sequencing on, the first device to ramp up, called the "prequel", sends a message through the DDC bus to the next device, called the "sequel" when the prequel's PG signal is driven high. When sequenc-

ing off, the sequel sends a message to the prequel to begin the prequel's ramp down after the sequel has completed its own ramp down. To achieve sequenced turn-off all the modules in the sequencing group should be configured for soft turn-off using the ON\_OFF\_CONFIG 0x02 command. Sequencing can be configured by the SEQUENCE 0xE0 command.

# Input Overvoltage and Undervoltage Protections

The input overvoltage and undervoltage protections prevent the DJT090A0X43-SRPZ from operating when the input is above or falls below preset thresholds. The customers are strongly advised not to increase the preset input overvoltage limit or decrease input undervoltage limit as it may result in compromising product safety, violation of the module's absolute maximum and minimum ratings which will void the product warranty.

The input overvoltage and undervoltage protections could be adjusted by the following commands: VIN\_OV\_FAULT\_RESPONSE 0x56, VIN\_UV\_FAULT\_RESPONSE 0x5A, VIN\_OV\_FAULT\_LIMIT 0x55, VIN\_OV\_WARN\_LIMIT 0x57, VIN\_UV\_WARN\_LIMIT 0x58, VIN\_UV\_FAULT LIMIT 0x59.

See PMBus Commands for more details.

# Output Overvoltage and Undervoltage Protections

The DJT090A0X43-SRPZ offers an internal output overvoltage protection circuit that can be used to protect sensitive load circuitry from being subjected to a voltage higher than its prescribed limits. The output voltage sensed through the VS+ and VS- pins is digitized and then compared to various programmable thresholds. The output undervoltage fault is masked during the module's soft-start output voltage ramp up, before the power good signal is asserted.

The DJT090A0X43-SRPZ overvoltage and undervoltage behavior cabe configured through the following commands: VOUT\_OV\_FAULT\_RESPONSE 0x41, VOUT\_UV\_FAULT\_RESPON SE 0x45, VOUT\_OV\_FAULT\_LIMIT 0x40,

VOUT\_OV\_WARN\_LIMIT 0x42, VOUT\_UV\_WARN\_LIMIT 0x43, VOUT\_UV\_FAULT\_LIMIT 0x44.

See PMBus Commands for more details.

# Output Overcurrent and Undercurrent Protections

The output overcurrent and undercurrent protections prevent excessive forward current through the module and the load during abnormal operation and excessive reverse current through the module when, for example, the output is shorted to higher voltage rail. Overcurrent and undercurrent protections are cycle-by-cycle in nature. The cycle average current IOUT\_AVG\_OC\_FAULT\_LIMIT 0xE7 is set to 101A. If the output cycle average current exceeds this value more than 15 cycle, the OCP will be triggered. The actual cycle by cycle is set to much greater than 101A in order to prevent short time transient current false trigger. If the reverse cycle average current, IOUT\_AVG\_OC\_FAULT\_LIMIT 0xE8 exceeds -99A, UCP will be triggered.

The customers are strongly advised not to operate over these limit as it may result in compromising product safety, violation of the module's absolute maximum and minimum ratings which will void the product warranty.

The output overcurrent and undercurrent warning limits and fault response could be adjusted by the following commands:

IOUT\_OC\_WARN\_LIMIT 0x4A,

IOUT\_UC\_WARN\_LIMIT 0x4B,

MFR\_IOUT\_OC\_FAULT\_RESPONSE 0xE5,

MFR\_IOUT\_UC\_FAULT\_RESPONSE 0xE6.

See PMBus Commands for more details.

# Overtemperature and Under-temperature Protections

The DJT090A0X43-SRPZ overtemperature protection ensures the temperature inside the module is below component's temperature maximum limit. The customers are strongly advised not to increase the preset overtemperature limit as it may result in compromising product safety, violation of the module's absolute maximum ratings which will void the product warranty. In addition to overtemperature protection,

there is also under-temperature protection which although not essential for the product safety may be useful in some applications.

The overtemperature and under-temperature protections could be adjusted by the following commands:

OT\_FAULT\_RESPONSE 0x50, UT\_FAULT\_RESPONSE 0x54, OT\_FAULT\_LIMIT 0x4F, OT\_WARN\_LIMIT 0x51, UT\_WARN\_LIMIT 0x52, UT\_FAULT\_LIMIT 0x53.

See PMBus Commands for more details.

#### Monitoring through SMBus

The DJT090A0X43-SRPZ controller can monitor a wide variety of system parameters through the SMBus interface. The module can be monitor for fault conditions by monitoring the SMBALERT pin, which is asserted when any number of preconfigured fault conditions occur. The module can also be monitored continuously for any number of power conversion parameters. Some of most useful monitoring commands are:

STATUS\_BYTE 0x78, STATUS\_WORD 0x79, STATUS\_VOUT 0x7A, STATUS\_IOUT 0x7B, STATUS\_INPUT 0x7C, STATUS\_TEMPERATURE 0x7D, READ\_VIN 0x88, READ\_VOUT 0x8B, READ\_IOUT 0x8C, READ\_IOUT 0x8D.

See PMBus Commands for more details.

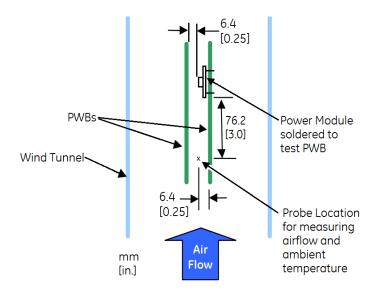

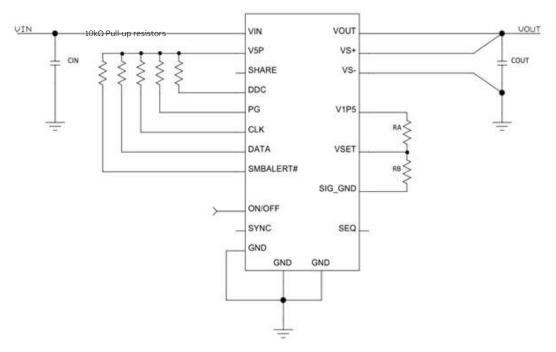

#### Input and Output Filtering

Because of its small size and compact design only a fraction of required input and output capacitance are placed inside the module. The additional external input capacitors must be placed adjacent to the input pins of the module. Combination of low ESR electrolytic and high-quality ceramic capacitors is recommended. To minimize the input-voltage ripple the ceramic capacitors must be placed closest to the input pins of the module. In a typical single-phase application, one should consider using at least two

$470\mu\text{F}/16\text{V}$  electrolytic capacitors, ten  $22\mu\text{F}$  X7R ceramic capacitors and two 0.1  $\mu\text{F}$  X7R high frequency capacitors.

The amount of external output capacitance depends on the output transient and output ripple requirements. Part of the additional external output capacitors must be placed adjacent to the output pins of the module and the other part to the load. Combination of low ESR polymer and high-quality ceramic capacitors is recommended. To minimize the output -voltage ripple part of the ceramic capacitors must be placed closer to the output of the module. To improve the load transient performance the other part of the ceramic capacitors must be placed closer to the load. In a typical single-phase application, see example application circuit. Some demanding applications may require more output capacitance.

For high di/dt application, capacitor equivalent series inductance (ESL) becomes one of dominating factors of transient performance. ABB recommends user to use low ESR tantalum polymer as output bulk capacitor. ABB suggests user to use online Power Module Wizard or simulation tool to estimate the amount of capacitance required for the application, then choose right amount/size/type accordingly.

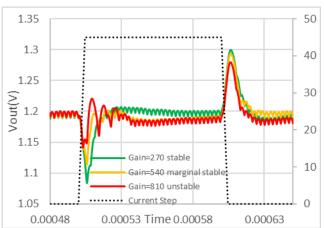

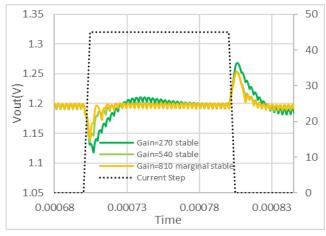

#### **Control Loop Tuning**

The heart of DJT090A0X43-SRPZ is a fully digital controller IC with innovative Charge Mode Control modulation scheme. By default, this control loop is stable for a wide range of output capacitance and loads, however, it may be further tuned to achieve higher performance under more specific application requirements. Since the control scheme is digital from end to end there is no dependence upon external compensation networks. This simplifies the design process by removing such considerations as temperature and process variation of passive com-Control parameters are ASCR CONFIG 0xDF and ASCR ADVANCED 0xD5 commands.

The ASCR gain parameter ASCR\_CONFIG[15:0] represents the scaling of the error voltage as applied to setting the PWM pulse width. Increasing this parameter decreases the time the controller takes to respond to a transient event at the expense of incorporating more high frequency noise into the loop.

This value is the dominant parameter in transient response. We recommend increasing this parameter until the loop response time is sufficient for the application, but no more. Setting the ASCR gain parameter too high can lead to excessive output voltage ripple due to increased PWM jitter.

Integral gain ASCR\_CONFIG[31:24] controls DC accuracy and the time taken to return to the output voltage set point following a transient event. Once ASCR gain is set appropriately, decrease integral gain while output voltage deviation is still acceptable.

Residual gain ASCR\_CONFIG[23:16] is analogous to damping. The residual gain has the effect of removing or adding some fractional portion against the deviation of the PWM pulse width from steady state duty cycle in the next switch cycle created by the gain parameter. Increasing this parameter decreases output overshoot at the expense of prolonging the recovery to the output set point following a load transient. Its effect is delayed by one cycle relative to the gain effect and as such, it does not affect the peak voltage deviation during the transient, only the return to steady state.

In addition to the basic loop parameters, the controller incorporates a digital steady state gain reduction circuit to provide low jitter steady state operation while maintaining fast transient response. This circuit compares the error signal to the threshold set with ASCR ADVANCED[11:0] over a period of time. If the error remains low, the controller begins dividing down the gain parameter according to the setting of ASCR ADVANCED[13:12] to decrease the effect of high frequency noise on PWM pulse width. If the error exceeds the threshold in any cycle, the controller immediately reverts to the full gain setting to handle the transient. Once ASCR CONFIG settings are chosen and output voltage ripple is acceptable in the application steady state conditions, increase the ASCR threshold setting until the gain reduction activates.

In general, ASCR gain should be tuned based on amount of output capacitors used. The default ASCR gain is set to 270 which would accommodate any capacitance above minimum capacitance requirement. In this case, the ASCR gain is already optimized and should not be increased too much. If much greater output capacitance is presented, then

ASCR gain can potentially be tuned up proportional to the output capacitance used. This can achieve much better transient responses. See following simulation examples. Simulation parameters: Vin = 12V, Vout = 1.2V, ASCR Integral = 80(default), ASCR Residual = 80(default). Istep = 45A, slew rate = 10A/us. Combination Cout for Case I is 3000uF, see figure 28a. Combination Cout for Case II is 6000uF, see figure 28b. As shown in the simulation, a larger ASCR gain can achieve better under/overshoot, however it may introduce unwanted oscillation during transient. For common practice, the ASCR gain should be optimized when transient is about to reach marginal stable. Larger output capacitance would allow ASCR gain to be set higher. Note that PCB parasitic is not considered in the simulation. In reality, as the output capacitance increases, equivalent PCB parasitic impedance would increase. Eventually, the effectiveness of the output capacitance would diminish as the equivalent PCB parasitic impedance become significant. Thus choose right amount of capacitors to use.

Figure 28a. Case I: Cout = 3000uF

Figure 28b. Case II: Cout = 6000uF

Page 18 Version 2.8

#### **DDC Bus**

The Digital-DC Communications (DDC) bus provides communication channel between modules for features such as sequencing, fault spreading and current sharing. The DDC pin must be pulled-up to V5P before ON/OFF pin is set high, or to an external 3.3V or 5.0V supply which must be present before powerup. The DDC pull-up resistor must provide transition times shorter than, or equal to, 1µs. Generally, each module connected to the DDC bus presents approximately 12pF of capacitive loading. The ideal design uses a central pull-up resistor that is well-matched to the total load capacitance. The minimum pull-up resistance should be limited to a value that enables any device to assert the bus to a voltage that ensures a Logic Low, typically 0.8V. A  $10k\Omega$  resistor provides good performance on a DDC bus with fewer than 10 devices.

The DJT090A0X43-SRPZ modules can be configured to broadcast a fault event over the DDC bus to the other devices in the group. For details on DDC group ID assignment, addressing and configuration see DDC\_CONFIG 0xD3 and DDC\_GROUP 0xE2 commands.

#### Synchronization

The DJT090A0X43-SRPZ's controller incorporates a precise 30MHz clock and Phase-Locked Loop (PLL) to clock the internal circuit. The switching frequency of the module is generated by dividing the internal clock by the closest integer number of times the value of switching frequency setting. The module is optimized to operate at 353kHz. When using the internal oscillator, the SYNC pin of one module can be configured as a clock source for other modules to accomplish phase spreading or phase interleaving.

The internal PLL circuit can also be synchronized to an external clock source connected to the SYNC pin. When the SYNC pin is configured as an input pin, the incoming clock signal must be in the range of ±4% of nominal switching frequency, must be present and stable within 50ms after POR and when the enable pin is asserted. The operation frequencies are not limited to discrete values as when using the internal clock. The module supports wider synchronization frequency range, contact local ABB FAE for details.

In the event of a loss of the external clock signal, the PLL sets the External Switching Period Fault bit in the STATUS MFR SPECIFIC 0x80 and shut down the module. The module then changes the PLL input to its internal oscillator and commence switching at its programmed frequency upon re-enabling. To resume frequency synchronization, cycle POR with a valid clock signal applied at the SYNC pin or resend the USER\_CONFIG 0xD1 command to "select external clock".

#### **Phase Spreading**

When multiple point-of-load converters share a common DC input supply, setting each converter to start its switching cycle at a different point in time can dramatically reduce the total peak and RMS input current and therefore improve system efficiency and reduce the input capacitance requirements. To enable phase spreading, all converters must be synchronized to the same switching clock. The phase offset can be configured using the INTERLEAVE 0x37 command.

#### Non-volatile Memory (NVM) Management

The DJT090A0X43-SRPZ has internal non-volatile memory where module's configurations are stored. There are three internal memory storage units: the USER store, the DEFAULT store and the FACTORY store. The USER store provides the end-user with ability to modify certain module settings while still protecting him, or her, from mistakes that may lead to a system level fault. The DEFAULT store provides a means to protect DJT090A0X43-SRPZ from damage by preventing the user from modifying certain values that are related to its physical construction, or safety and specification limits.

During the initialization process, the DJT090A0X43-SRPZ checks for stored values contained in its internal non-volatile memory. The parameters in USER store take priority over those in the DEFAULT store. If there are no values set in the USER, DEFAULT or FACTORY stores, the device uses the pin-strap setting value. Integrated security measures ensure that the user can only restore the module's configuration to a level that has been made available to them. For details regarding protection of the USER and DEFAULT stores, see the SECURITY\_CONTROL 0xFA, PASSWORD 0xFB, WRITE\_PROTECT 0xFD com-

mands.

The ON/OFF pin must be driven low whenever a PMBus command that could potentially damage the application circuit is sent to the module. It is always a good practice to turn the module OFF when saving configuration changes into the non-volatile memory.

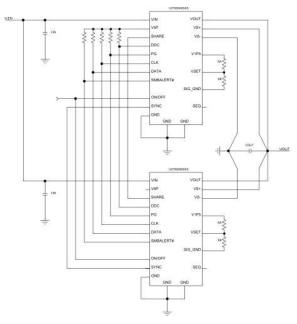

#### Parallel Operation and Active Current Sharing

Up to 8 DJT090A0X43-SRPZ modules can be paralleled together to form a high current rail. The modules will share the current equally within a few percent, assuming output current sensing calibration is adequate. For most applications, factory performed calibration will be sufficient. In some application where the interconnecting impedances between modules are extremely low, in-system calibration may be necessary.

The DJT090A0X43-SRPZ employs "Master – Slave" active current sharing. The master in the current sharing rail continuously transmits its most recent output current reading through the SHARE bus, which the slave modules use as a reference for the purpose of the current balancing.

Only one master is allowed per current sharing rail. A simplified parallel operation schematic is shown blow figure. For several modules to form a current sharing group, the ON/OFF, SHARE, DDC and SYNC pins of one module must be connected to the same pin of all other modules. In addition, the output voltage sensing pins, VS+ and VS-, of each module in the group must be connected to the same output voltage regulation point. Often the ON/OFF bus would be configured for fault-spreading to ensure fast,  $20\mu s$  typical delay time, fault response. In that scenario the ON/OFF bus would need a single  $10k\Omega$  pullup resistor to V5P. When a module detects a fault condition, it will pull down the ON/OFF bus to disable the other modules in the current sharing group.

Figure 29. Example connection for two devices

A current sharing rail may be configured using the following commands: USER\_CONFIG, DDC\_CONFIG, DDC GROUP and INTERLEAVE. The first step is to select a Rail ID number for the current sharing rail, establish the number of modules (phases) in the rail, and assign Phase IDs to each of the module. The Phase ID "0" identifies the master; all Phase ID settings in a rail must be sequential. All that could be configured by DDC CONFIG 0xD3 command. Users must pay attention that every module in a multiphase rail share the same BROADCAST\_VOUT COM-MAND and BROACAST OPERATION DDC Group ID settings, which are distinct from DDC Rail IDs. DDC Group ID settings are configured with the DDC\_GROUP 0xE2 command. By default, the phase interleaving of the modules in the current sharing rail is accomplished automatically. The controller of each module will choose its phase offset by the last four bits of its PMBus address. Therefore, it is a good practice, the addresses selected for the modules in a current sharing group to be sequential and to begin with the master of the group. The phase offset of the modules in the current sharing group could be altered by INTERLEAVE 0x37 command. For phase interleaving to work, all modules must be synchronized to an external clock, or to the clock of the master in the group. SYNC pin configuration could be set by USER\_CONFIG 0xD1. The same command is used to configure the use of ON/OFF pin for fast faultspreading.

#### **Layout Considerations**

DJT090A0X43-SRPZ uses PCB to conduct both current and heat because PCB is a better thermal heatsink material than any top side cooling materials. Thus, proper PCB layout is required to successfully deliver full power while reduce switching noise mitigation, improve thermal performance and maximize the efficiency. ABB supplies two reference design along with PCB files for optimized layout. Refer to following application note:

- DJT090\_DLynxII\_Series\_Single\_Unit\_Evaluation\_ Board\_Application\_Note

- DJT090\_DLynxII\_Series\_Paralleling\_Evaluation\_B oard\_Application\_Note

#### Common recommendations:

- Place multiple ceramic capacitors directly below the DJT090A0X43-SRPZ especially in between VIN and VIN\_GND. This is the most critical decoupling capacitor which will improve efficiency and reduce noise, see Figure 30b, 31d.

- Use large on-pad filled-via array to distribute current into different layer. Evenly distribute current into different layer, see Figure 30a

- Identify input power flow path and output power flow path. Provide strong connection between input ground and output ground right below the DJT090A0X43-SRPZ

- Separate control signal ground with power grounds to avoid potential noise. Control signal ground is internally connected to the power grounds

- Orientation of the DJT090A0X43 may affect component population density. Match the best orientation for the application.

- <u>Do not place any via under the EPAD48, 50, 52 or</u> route any sensitive signal under it

For single DJT090A0X43-SRPZ unit layout, 6 powerplane with minimum 3-oz is recommended for deliver full power up to 90A.

Use differential pair to route VS+ and VS-, connect them to the decoupling capacitor, which is closest to the load, see Figure 30b.

For parallel DJT090A0X43-SRPZ unit layout, 8 power-plane with minimum 2-oz is recommended for deliver full power up to 720A.

- Match the output impedance of each channel

- Use differential pair to route VS+ and VS-, con-

- nect to a single decoupling capacitor which is closest to the load see Figure 32.

- SGND 20-27 can be used along with GND to conduct current and thermal stress, see Figure 31a.

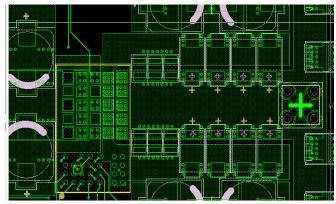

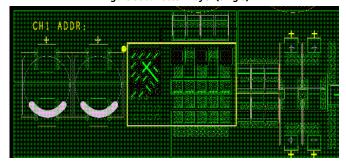

Figure 30a. Top layer (single)

Figure 30b. Bottom layer (single)

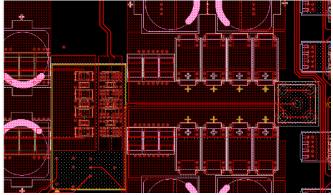

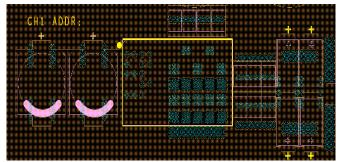

Figure 31a. Top layer (parallel)

Figure 31b. Top layer (parallel)

Page 21 Version 2.8

Figure 31c. Mid-Layer (parallel)

Figure 31d. Bottom layer (parallel)

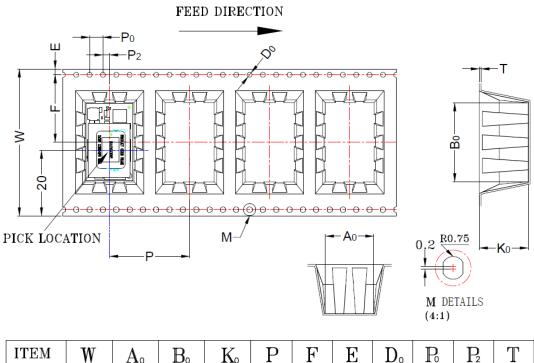

#### Stencil Considerations

Solder volume is critical to the production process. Below table show the suggested stencil size for each pad based on 5mil stencil thickness of customer board.

Figure 34. Stencil example