## **General Description**

The MAX5070/MAX5071 BiCMOS, high-performance, current-mode PWM controllers have all the features required for wide input voltage range isolated/nonisolated power supplies. These controllers are used for low- and high-power universal input voltage and telecom power supplies.

The MAX5070/MAX5071 contain a fast comparator with only 60ns typical delay from current sense to the output for overcurrent protection. The MAX5070A/MAX5070B have an integrated error amplifier with the output at COMP. Soft-start is achieved by controlling the COMP voltage rise using external components.

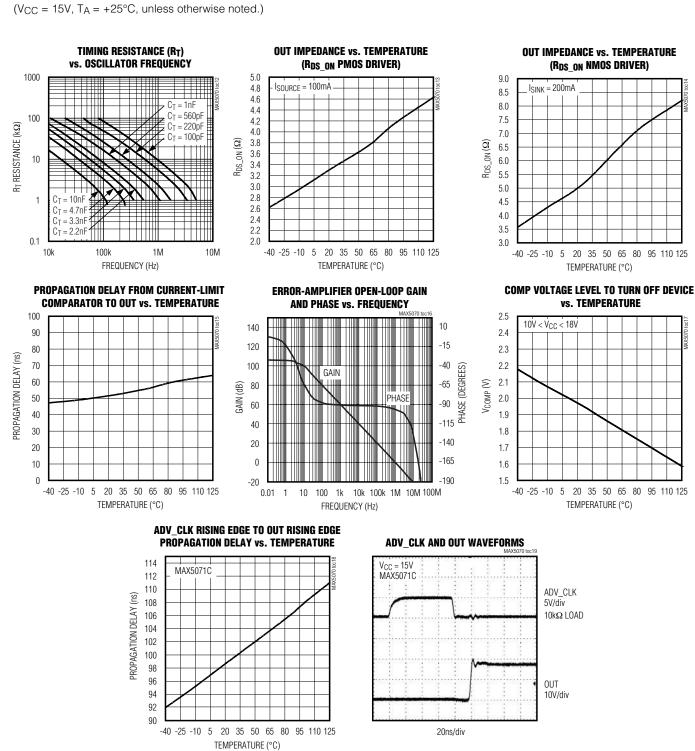

The frequency is adjustable from 20kHz to 1MHz with an external resistor and capacitor. The timing capacitor discharge current is trimmed allowing for programmable dead time and maximum duty cycle for a given frequency. The available saw-toothed waveform at  $R_TC_T$  can be used for slope compensation when needed.

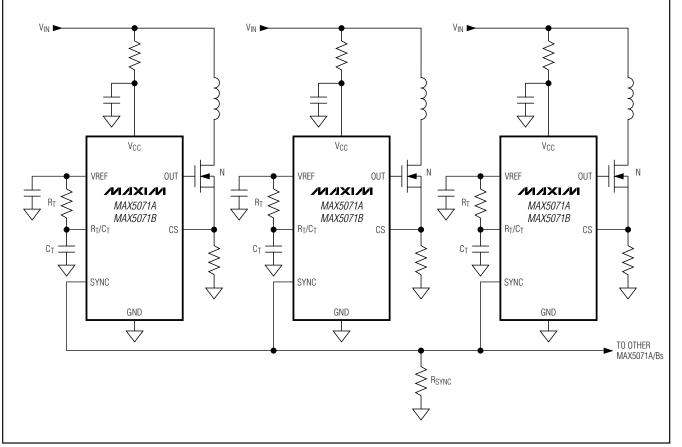

The MAX5071A/MAX5071B include a bidirectional synchronization circuit allowing for multiple controllers to run at the same frequency to avoid beat frequencies. Synchronization is accomplished by simply connecting the SYNC pins of all devices together. When synchronizing with other devices, the MAX5071A/MAX5071B with the highest frequency synchronizes the other devices. Alternatively, the MAX5071A/MAX5071B can be synchronized to an external clock with an opendrain output stage running at a higher frequency.

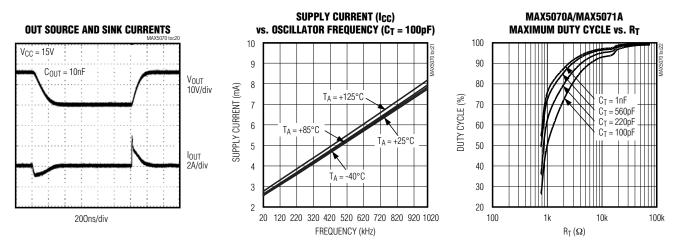

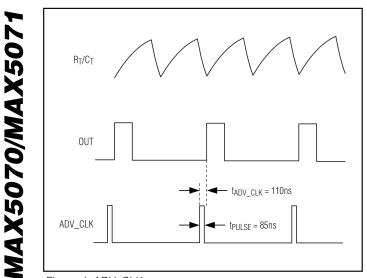

The MAX5071C provides a clock output pulse (ADV\_CLK) that leads the driver output (OUT) by 110ns. The advanced clock signal is used to drive the secondary-side synchronous rectifiers.

The MAX5070/MAX5071 are available in 8-pin  $\mu MAX^{@}$  and SO packages and operate over the automotive temperature range of -40°C to +125°C.

## Applications

- Universal Input AC/DC Power Supplies

- Isolated Telecom Power Supplies

- Isolated Power-Supply Modules

- Networking Systems

- Computer Systems/Servers

- Industrial Power Conversion

- Isolated Keep-Alive Circuits

$\mu$ MAX is a registered trademark of Maxim Integrated Products, Inc.

## \_\_ Features

Pin-for-Pin Replacement for UC2842 (MAX5070A) and UC2844 (MAX5070B)

///XI///

- ♦ 2A Drive Source and 1A Sink Capability

- Up to 1MHz Switching Frequency Operation

- Bidirectional Synchronization (MAX5071A/MAX5071B)

- Advanced Output Drive for Secondary-Side Synchronous Rectification (MAX5071C)

- ♦ Fast 60ns Cycle-by-Cycle Current Limit

- Trimmed Oscillator Capacitor Discharge Current Sets Maximum Duty Cycle Accurately

- Accurate 5% Start and Stop Voltage with 6V Hysteresis

- Low 32µA Startup Current

- ♦ 5V Regulator Output (VREF) with 20mA Capability

- Overtemperature Shutdown

## \_Ordering Information

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX5070AASA | -40°C to +125°C | 8 SO        |

| MAX5070AAUA | -40°C to +125°C | 8 µMAX      |

| MAX5070BASA | -40°C to +125°C | 8 SO        |

| MAX5070BAUA | -40°C to +125°C | 8 µMAX      |

Specify lead-free by adding the + symbol at the end of the part number when ordering.

Ordering Information continued at end of data sheet. Selector Guide appears at end of data sheet.

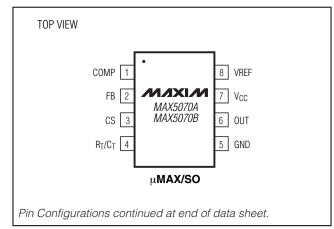

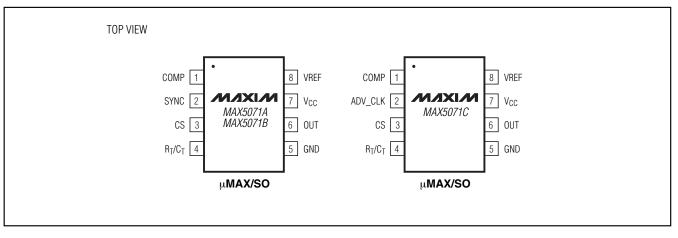

## **Pin Configurations**

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> (Low-Impedance Source) to GND                    | 0.3V to +30V                       |

|------------------------------------------------------------------|------------------------------------|

| V <sub>CC</sub> (I <sub>CC</sub> < 30mA)                         | Self Limiting                      |

| OUT to GND(                                                      | $0.3V \text{ to } (V_{CC} + 0.3V)$ |

| OUT Current                                                      | ±1A for 10µs                       |

| FB, SYNC, COMP, CS, R <sub>T</sub> /C <sub>T</sub> , VREF to GND | 00.3V to +6V                       |

| COMP Sink Current (MAX5070)                                      | 10mA                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

$(V_{CC} = +15V, R_T = 10k\Omega, C_T = 3.3nF, V_{VREF} = OPEN, C_{VREF} = 0.1\mu F, COMP = OPEN, V_{FB} = 2V, CS = GND, T_A = -40^{\circ}C \text{ to } +85^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                      | SYMBOL             | CONDITIONS                                                  | MIN   | ТҮР   | MAX   | UNITS |

|--------------------------------|--------------------|-------------------------------------------------------------|-------|-------|-------|-------|

| REFERENCE                      | -                  | ·                                                           |       |       |       |       |

| Output Voltage                 | VVREF              | $T_A = +25^{\circ}C$ , $I_{VREF} = 1mA$                     | 4.950 | 5.000 | 5.050 | V     |

| Line Regulation                | ΔV <sub>LINE</sub> | 12V < V <sub>CC</sub> < 25V, I <sub>VREF</sub> = 1mA        |       | 0.4   | 4     | mV    |

| Load Regulation                | $\Delta V_{LOAD}$  | 1mA < I <sub>VREF</sub> < 20mA                              |       | 6     | 25    | mV    |

| Total Output Variation         | VREFT              | 1mA < I <sub>VREF</sub> < 20mA, 12V < V <sub>CC</sub> < 25V | 4.9   |       | 5.1   | V     |

| Reference Output-Noise Voltage | V <sub>NOISE</sub> | 10Hz < f < 10kHz, T <sub>A</sub> = +25°C                    |       | 50    |       | μV    |

| Reference Output Short Circuit | Is_sc              | $V_{VREF} = 0V$                                             | -30   | -100  | -180  | mA    |

| OSCILLATOR                     |                    |                                                             |       |       |       |       |

| Initial Accuracy               |                    | $T_A = +25^{\circ}C$                                        | 51    | 54    | 57    | kHz   |

| Voltage Stability              |                    | 12V < V <sub>CC</sub> < 25V                                 |       | 0.2   | 0.5   | %     |

| Temp Stability                 |                    | $-40^{\circ}C < T_{A} < +85^{\circ}C$                       |       | 0.5   |       | %     |

| RT/CT Voltage Ramp (P-P)       | VRAMP              |                                                             |       | 1.7   |       | V     |

| RT/CT Voltage Ramp Valley      | VRAMP_VALLEY       |                                                             |       | 1.1   |       | V     |

| Discharge Current              | I <sub>DIS</sub>   | $V_{RT/CT} = 2V, T_A = +25^{\circ}C$                        | 7.9   | 8.3   | 8.7   | mA    |

| Frequency Range                | fosc               |                                                             | 20    |       | 1000  | kHz   |

| ERROR AMPLIFIER (MAX5070A      | /MAX5070B)         |                                                             |       |       |       |       |

| FB Input Voltage               | VFB                | FB shorted to COMP                                          | 2.465 | 2.5   | 2.535 | V     |

| FB Input Bias Current          | I <sub>B(FB)</sub> |                                                             |       | -0.01 | -0.1  | μA    |

| Open-Loop Voltage Gain         | Avol               | $2V \le V_{COMP} \le 4V$                                    |       | 100   |       | dB    |

| Unity-Gain Bandwidth           | fgbw               |                                                             |       | 1     |       | MHz   |

| Power-Supply Rejection Ratio   | PSRR               | 12V ≤ V <sub>CC</sub> ≤ 25V (Note 2)                        | 60    | 80    |       | dB    |

| COMP Sink Current              | ISINK              | $V_{FB} = 2.7V, V_{COMP} = 1.1V$                            | 2     | 6     |       | mA    |

| COMP Source Current            | ISOURCE            | $V_{FB} = 2.3V, V_{COMP} = 5V$                              | -0.5  | -1.2  | -1.8  | mA    |

| COMP Output High Voltage       | VCOMPH             | $V_{FB} = 2.3V, R_{COMP} = 15k\Omega$ to GND                | 5     | 5.8   |       | V     |

| COMP Output Low Voltage        | VCOMPL             | $V_{FB} = 2.7V, R_{COMP} = 15k\Omega$ to VREF               |       | 0.1   | 0.5   | V     |

| CURRENT-SENSE AMPLIFIER        |                    |                                                             |       |       |       |       |

| Gain                           | A <sub>CS</sub>    | (Notes 3, 4)                                                | 2.85  | 3     | 3.26  | V/V   |

| Maximum Current Sanaa Signal   |                    | MAX5070A/B (Note 3)                                         | 0.95  | 1     | 1.05  | V     |

| Maximum Current-Sense Signal   | VCS_MAX            | V <sub>COMP</sub> = 5V, MAX5071_                            | 0.95  | 1     | 1.05  | v     |

## ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +15V, R_T = 10k\Omega, C_T = 3.3nF, V_{VREF} = OPEN, C_{VREF} = 0.1\mu F, COMP = OPEN, V_{FB} = 2V, CS = GND, T_A = -40^{\circ}C to +85^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                                  | SYMBOL               | CONDITIONS                 | MIN  | ТҮР  | MAX  | UNITS |

|--------------------------------------------|----------------------|----------------------------|------|------|------|-------|

| Power-Supply Rejection Ratio               | PSRR                 | $12V \le V_{CC} \le 25V$   |      | 70   |      | dB    |

| Input Bias Current                         | ICS                  | V <sub>COMP</sub> = 0V     |      | -1   | -2.5 | μA    |

| Delay From CS to OUT                       | tCS_DELAY            | 50mV overdrive             |      | 60   |      | ns    |

| MOSFET DRIVER                              |                      | 1                          |      |      |      | l     |

| OUT Low-Side On-Resistance                 | VRDS_ONL             | I <sub>SINK</sub> = 200mA  |      | 4.5  | 10   | Ω     |

| OUT High-Side On-Resistance                | VRDS_ONH             | ISOURCE = 100mA            |      | 3.5  | 7    | Ω     |

| ISOURCE (Peak)                             | ISOURCE              | C <sub>OUT</sub> = 10nF    |      | 2    |      | А     |

| I <sub>SINK</sub> (Peak)                   | ISINK                | C <sub>OUT</sub> = 10nF    |      | 1    |      | А     |

| Rise Time                                  | tr                   | C <sub>OUT</sub> = 1nF     |      | 15   |      | ns    |

| Fall Time                                  | tf                   | C <sub>OUT</sub> = 1nF     |      | 22   |      | ns    |

| UNDERVOLTAGE LOCKOUT/STA                   | RTUP                 |                            |      |      |      |       |

| Startup Voltage Threshold                  | VCC_START            |                            | 15.2 | 16   | 16.8 | V     |

| Minimum Operating Voltage After<br>Turn-On | V <sub>CC</sub> _MIN |                            | 9.2  | 10   | 10.8 | V     |

| Undervoltage-Lockout Hysteresis            | UVLO <sub>HYST</sub> |                            |      | 6    |      | V     |

| PWM                                        |                      |                            |      |      |      |       |

| Meximum Duty Quele                         | Deres                | MAX5070A/MAX5071A          | 94.5 | 96   | 97.5 | %     |

| Maximum Duty Cycle                         | DMAX                 | MAX5070B/MAX5071B/MAX5071C | 48   | 49.8 | 50   | /0    |

| Minimum Duty Cycle                         | D <sub>MIN</sub>     |                            |      |      | 0    | %     |

| SUPPLY CURRENT                             |                      |                            |      |      |      |       |

| Startup Supply Current                     | ISTART               |                            |      | 32   | 65   | μA    |

| Operating Supply Current                   | Icc                  | $V_{FB} = V_{CS} = 0V$     |      | 3    | 5    | mA    |

| Zener Bias Voltage at $V_{CC}$             | VZ                   | $I_{CC} = 25 \text{mA}$    | 24   | 26.5 |      | V     |

| THERMAL SHUTDOWN                           |                      |                            |      |      |      |       |

| Thermal Shutdown                           | T <sub>SHDN</sub>    |                            |      | +150 |      | °C    |

| Thermal-Shutdown Hysteresis                | T <sub>HYST</sub>    |                            |      | 4    |      | °C    |

| SYNCHRONIZATION (MAX5071A                  | /MAX5071B or         | lly) (Note 5)              |      |      |      |       |

| SYNC Frequency Range                       | <b>f</b> SYNC        |                            | 20   |      | 1000 | kHz   |

| SYNC Clock Input High<br>Threshold         | Vsyncinh             |                            | 3.5  |      |      | V     |

| SYNC Clock Input Low Threshold             | VSYNCINL             |                            |      |      | 0.8  | V     |

| SYNC Clock Input Minimum<br>Pulse Width    | tpw_syncin           |                            | 200  |      |      | ns    |

| SYNC Clock Output High Level               | VSYNCOH              | 1mA external pulldown      | 4.0  | 4.7  |      | V     |

| SYNC Clock Output Low Level                | VSYNCOL              | $R_{SYNC} = 5k\Omega$      |      | 0    | 0.1  | V     |

| SYNC Leakage Current                       | ISYNC                | V <sub>SYNC</sub> = 0V     |      | 0.01 | 0.1  | μA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +15V, R_T = 10k\Omega, C_T = 3.3nF, V_{VREF} = OPEN, C_{VREF} = 0.1\mu F, COMP = OPEN, V_{FB} = 2V, CS = GND, T_A = -40^{\circ}C to +85^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                                 | SYMBOL         | CONDITIONS                       | MIN | ТҮР | MAX | UNITS |

|-------------------------------------------|----------------|----------------------------------|-----|-----|-----|-------|

| ADV_CLK (MAX5071C only)                   |                |                                  |     |     |     |       |

| ADV_CLK High Voltage                      | Vadv_clkh      | IADV_CLK = 10mA source           | 2.4 | 3   |     | V     |

| ADV_CLK Low Voltage                       | VADV_CLKL      | I <sub>ADV_CLK</sub> = 10mA sink |     |     | 0.4 | V     |

| ADV_CLK Output Pulse Width                | <b>t</b> PULSE |                                  |     | 85  |     | ns    |

| ADV_CLK Rising Edge to OUT<br>Rising Edge | tadv_clk       |                                  |     | 110 |     | ns    |

| ADV_CLK Source and Sink<br>Current        | Iadv_clk       |                                  | 10  |     |     | mA    |

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +15V, R_T = 10k\Omega, C_T = 3.3nF, V_{VREF} = OPEN, C_{VREF} = 0.1\mu F, COMP = OPEN, V_{FB} = 2V, CS = GND, T_A = -40^{\circ}C to +125^{\circ}C, unless otherwise noted.) (Note 1)$

| PARAMETER                                          | SYMBOL             | CONDITIONS                                                         | MIN   | ТҮР   | MAX   | UNITS |

|----------------------------------------------------|--------------------|--------------------------------------------------------------------|-------|-------|-------|-------|

| REFERENCE                                          | ·                  |                                                                    |       |       |       |       |

| Output Voltage                                     | VVREF              | $T_A = +25^{\circ}C$ , $I_{VREF} = 1mA$                            | 4.950 | 5.000 | 5.050 | V     |

| Line Regulation                                    | ΔVLINE             | 12V < V <sub>CC</sub> < 25V, I <sub>VREF</sub> = 1mA               |       | 0.4   | 4     | mV    |

| Load Regulation                                    | ΔVLOAD             | 1mA < I <sub>VREF</sub> < 20mA                                     |       | 6     | 25    | mV    |

| Total Output Variation                             | VREFT              | 1mA < I <sub>VREF</sub> < 20mA, 12V < V <sub>CC</sub> < 25V        | 4.9   |       | 5.1   | V     |

| Reference Output Noise Voltage                     | VNOISE             | $10Hz < f < 10kHz, T_A = +25^{\circ}C$                             |       | 50    |       | μV    |

| Reference Output Short Circuit                     | Is_sc              | $V_{VREF} = 0V$                                                    | -30   | -100  | -180  | mA    |

| OSCILLATOR                                         | ·                  |                                                                    |       |       |       |       |

| Initial Accuracy                                   |                    | $T_A = +25^{\circ}C$                                               | 51    | 54    | 57    | kHz   |

| Voltage Stability                                  |                    | 12V < V <sub>CC</sub> < 25V                                        |       | 0.2   | 0.5   | %     |

| Temp Stability                                     |                    | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$ |       | 1     |       | %     |

| R <sub>T</sub> /C <sub>T</sub> Voltage Ramp (P-P)  | VRAMP              |                                                                    |       | 1.7   |       | V     |

| R <sub>T</sub> /C <sub>T</sub> Voltage Ramp Valley | VRAMP_VALLEY       |                                                                    |       | 1.1   |       | V     |

| Discharge Current                                  | I <sub>DIS</sub>   | $V_{\text{RT/CT}} = 2V, T_{\text{A}} = +25^{\circ}\text{C}$        | 7.9   | 8.3   | 8.7   | mA    |

| Frequency Range                                    | fosc               |                                                                    | 20    |       | 1000  | kHz   |

| ERROR AMPLIFIER (MAX5070A                          | /MAX5070B)         |                                                                    |       |       |       |       |

| FB Input Voltage                                   | VFB                | FB shorted to COMP                                                 | 2.465 | 2.5   | 2.535 | V     |

| FB Input Bias Current                              | I <sub>B(FB)</sub> |                                                                    |       | -0.01 | -0.1  | μΑ    |

| Open-Loop Voltage Gain                             | Avol               | $2V \le V_{COMP} \le 4V$                                           |       | 100   |       | dB    |

| Unity-Gain Bandwidth                               | fgbw               |                                                                    |       | 1     |       | MHz   |

| Power-Supply Rejection Ratio                       | PSRR               | 12V ≤ V <sub>CC</sub> ≤ 25V (Note 2)                               | 60    | 80    |       | dB    |

| COMP Sink Current                                  | ISINK              | $V_{FB} = 2.7V, V_{COMP} = 1.1V$                                   | 2     | 6     |       | mA    |

| COMP Source Current                                | ISOURCE            | $V_{FB} = 2.3V, V_{COMP} = 5V$                                     | -0.5  | -1.2  | -1.8  | mA    |

| COMP Output High Voltage                           | VCOMPH             | $V_{FB} = 2.3V$ , $R_{COMP} = 15k\Omega$ to GND                    | 5     | 5.8   |       | V     |

| COMP Output Low Voltage                            | VCOMPL             | $V_{FB} = 2.7V, R_{COMP} = 15k\Omega$ to VREF                      |       | 0.1   | 0.5   | V     |

## ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +15V, R_T = 10k\Omega, C_T = 3.3nF, V_{VREF} = OPEN, C_{VREF} = 0.1\mu F, COMP = OPEN, V_{FB} = 2V, CS = GND, T_A = -40^{\circ}C to +125^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                                  | SYMBOL                | CONDITIONS                 | MIN  | ТҮР  | МАХ  | UNITS |

|--------------------------------------------|-----------------------|----------------------------|------|------|------|-------|

| CURRENT-SENSE AMPLIFIER                    | •                     | •                          |      |      |      |       |

| Gain                                       | Acs                   | (Notes 3, 4)               | 2.85 | 3    | 3.26 | V/V   |

| Maying Current Canad Cinnal                |                       | MAX5070A/B (Note 3)        | 0.95 | 1    | 1.05 | V     |

| Maximum Current-Sense Signal               | VCS_MAX               | $V_{COMP} = 5V, MAX5071_$  | 0.95 | 1    | 1.05 | v     |

| Power-Supply Rejection Ratio               | PSRR                  | $12V \le V_{CC} \le 25V$   |      | 70   |      | dB    |

| Input Bias Current                         | ICS                   |                            |      | -1   | -2.5 | μA    |

| Delay From CS to OUT                       | tcs_delay             | 50mV overdrive             |      | 60   |      | ns    |

| MOSFET DRIVER                              | •                     |                            |      |      |      |       |

| OUT Low-Side On-Resistance                 | VRDS_ONL              | I <sub>SINK</sub> = 200mA  |      | 4.5  | 12   | Ω     |

| OUT High-Side On-Resistance                | VRDS_ONH              | ISOURCE = 100mA            |      | 3.5  | 9    | Ω     |

| ISOURCE (Peak)                             | ISOURCE               | $C_{OUT} = 10nF$           |      | 2    |      | А     |

| I <sub>SINK</sub> (Peak)                   | Isink                 | $C_{OUT} = 10nF$           |      | 1    |      | А     |

| Rise Time                                  | tr                    | C <sub>OUT</sub> = 1nF     |      | 15   |      | ns    |

| Fall Time                                  | tf                    | C <sub>OUT</sub> = 1nF     |      | 22   |      | ns    |

| UNDERVOLTAGE LOCKOUT/ST                    | ARTUP                 |                            |      |      |      |       |

| Startup Voltage Threshold                  | V <sub>CC_START</sub> |                            | 15.2 | 16   | 16.8 | V     |

| Minimum Operating Voltage After<br>Turn-On | V <sub>CC_MIN</sub>   |                            | 9.2  | 10   | 10.8 | V     |

| Undervoltage-Lockout Hysteresis            | UVLOHYST              |                            |      | 6    |      | V     |

| PWM                                        | •                     |                            |      |      |      |       |

|                                            | 5                     | MAX5070A/MAX5071A          | 94.5 | 96   | 97.5 | 0/    |

| Maximum Duty Cycle                         | DMAX                  | MAX5070B/MAX5071B/MAX5071C | 48   | 49.8 | 50   | %     |

| Minimum Duty Cycle                         | D <sub>MIN</sub>      |                            |      |      | 0    | %     |

| SUPPLY CURRENT                             | •                     |                            |      |      |      |       |

| Startup Supply Current                     | ISTART                |                            |      | 32   | 65   | μA    |

| Operating Supply Current                   | ICC                   | $V_{FB} = V_{CS} = 0V$     |      | 3    | 5    | mA    |

| Zener Bias Voltage at V <sub>CC</sub>      | Vz                    | I <sub>CC</sub> = 25mA     | 24   | 26.5 |      | V     |

| THERMAL SHUTDOWN                           |                       |                            |      |      |      |       |

| Thermal Shutdown                           | T <sub>SHDN</sub>     |                            |      | +150 |      | °C    |

| Thermal-Shutdown Hysteresis                | THYST                 |                            |      | 4    |      | °C    |

| SYNCHRONIZATION (MAX5071A                  | /MAX5071B or          | nly, Note 5)               |      |      |      |       |

| SYNC Frequency Range                       | <b>f</b> SYNC         |                            | 20   |      | 1000 | kHz   |

| SYNC Clock Input High<br>Threshold         | Vsyncinh              |                            | 3.5  |      |      | V     |

| SYNC Clock Input Low Threshold             | VSYNCINL              |                            |      |      | 0.8  | V     |

| SYNC Clock Input Minimum<br>Pulse Width    | tpw_syncin            |                            | 200  |      |      | ns    |

| SYNC Clock Output High Level               | VSYNCOH               | 1mA external pulldown      | 4.0  | 4.7  |      | V     |

| SYNC Clock Output Low Level                | VSYNCOL               | $R_{SYNC} = 5k\Omega$      |      | 0    | 0.1  | V     |

## ELECTRICAL CHARACTERISTICS (continued)

(V<sub>CC</sub> = +15V, R<sub>T</sub> = 10kΩ, C<sub>T</sub> = 3.3nF, V<sub>VREF</sub> = OPEN, C<sub>VREF</sub> = 0.1µF, COMP = OPEN, V<sub>FB</sub> = 2V, CS = GND, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.) (Note 1)

| PARAMETER                                 | SYMBOL         | CONDITIONS                       | MIN | ТҮР  | MAX | UNITS |  |

|-------------------------------------------|----------------|----------------------------------|-----|------|-----|-------|--|

| SYNC Leakage Current                      | ISYNC          | V <sub>SYNC</sub> = 0V           |     | 0.01 | 0.1 | μA    |  |

| ADV_CLK (MAX5071C only)                   |                |                                  |     |      |     |       |  |

| ADV_CLK High Voltage                      | Vadv_clkh      | IADV_CLK = 10mA source           | 2.4 | 3    |     | V     |  |

| ADV_CLK Low Voltage                       | VADV_CLKL      | I <sub>ADV_CLK</sub> = 10mA sink |     |      | 0.4 | V     |  |

| ADV_CLK Output Pulse Width                | <b>t</b> PULSE |                                  |     | 85   |     | ns    |  |

| ADV_CLK Rising Edge to OUT<br>Rising Edge | tadv_clk       |                                  |     | 110  |     | ns    |  |

| ADV_CLK Source and Sink<br>Current        | IADV_CLK       |                                  | 10  |      |     | mA    |  |

Note 1: All devices are 100% tested at +25°C. All limits over temperature are guaranteed by design, not production tested.

Note 2: Guaranteed by design, not production tested.

Note 3: Parameter measured at trip point of latch with VFB = 0V (MAX5070A/MAX5070B only).

**Note 4:** Gain is defined as  $A = \Delta V_{COMP} / \Delta V_{CS}$ ,  $0 \le V_{CS} \le 0.8 V$ .

Note 5: Output Frequency equals oscillator frequency for MAX5070A/MAX5071A. Output frequency is one-half oscillator frequency for MAX5070B/MAX5071B/MAX5071C.

$(V_{CC} = 15V, T_A = +25^{\circ}C, unless otherwise noted.)$

TEMPERATURE (°C)

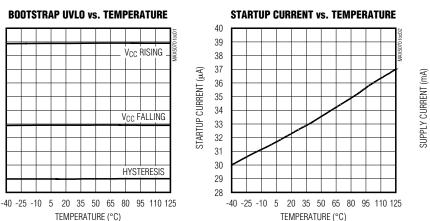

## **Typical Operating Characteristics**

**OPERATING SUPPLY CURRENT (ICC)**

M/IXI/M

17

16

15

14

13

12 V<sub>CC</sub> (V)

11

10

9

8

7

6

5

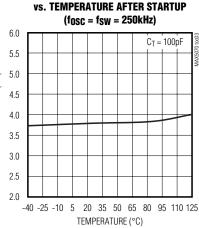

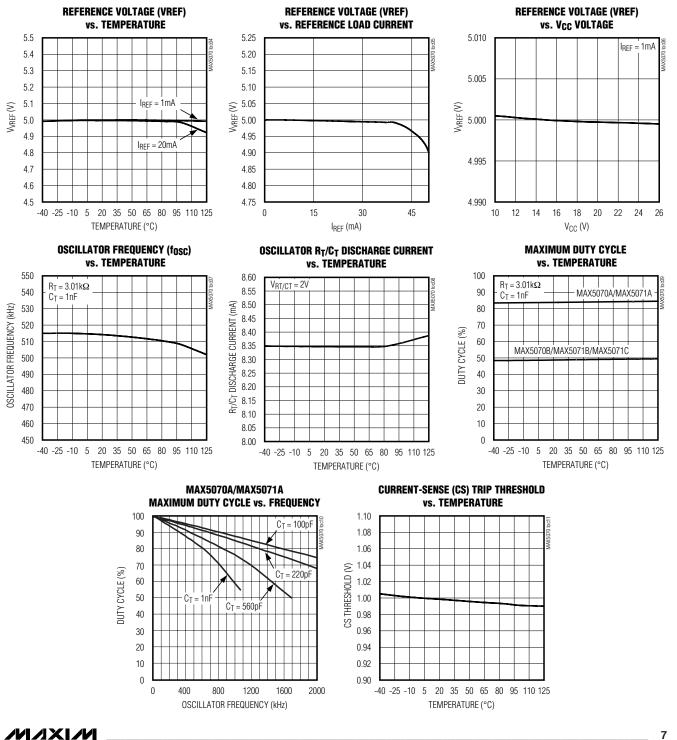

## **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 15V,  $T_A$  = +25°C, unless otherwise noted.)

MAX5070/MAX5071

**Typical Operating Characteristics (continued)**

/N/XI/N

MAX5070/MAX507

8

## **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 15V,  $T_A$  = +25°C, unless otherwise noted.)

Pin Descriptions

## MAX5070A/MAX5070B

| PIN | NAME                                                                                                                 | FUNCTION                                                                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | COMP                                                                                                                 | Error-Amplifier Output. COMP can be used for soft-start.                                                                                                                |

| 2   | FB                                                                                                                   | Error-Amplifier Inverting Input                                                                                                                                         |

| 3   | CS                                                                                                                   | Input to the PWM Comparator and Overcurrent Protection Comparator. The current-sense signal is compared to a signal proportional to the error-amplifier output voltage. |

| 4   | R <sub>T</sub> /C <sub>T</sub>                                                                                       | Timing Resistor and Capacitor Connection. A resistor $R_T$ from $R_T/C_T$ to VREF and capacitor $C_T$ from $R_T/C_T$ to GND set the oscillator frequency.               |

| 5   | GND Power-Supply Ground. Place the V <sub>CC</sub> and VREF bypass capacitors close to the IC to minin ground loops. |                                                                                                                                                                         |

| 6   | OUT                                                                                                                  | MOSFET Driver Output. OUT connects to the gate of the external n-channel MOSFET.                                                                                        |

| 7   | V <sub>CC</sub>                                                                                                      | Power-Supply Input for MAX5070. Bypass $V_{CC}$ to GND with a 0.1µF ceramic capacitor or a parallel combination of a 0.1µF and a higher value ceramic capacitor.        |

| 8   | 5V Beference Output, Bypass VBEE to GND with a 0 1µE ceramic capacitor or a parall                                   |                                                                                                                                                                         |

## Pin Descriptions (continued)

| PIN                   |             |                                |                                                                                                                                                                                                                       |

|-----------------------|-------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX5071A/<br>MAX5071B | MAX5071C    |                                | FUNCTION                                                                                                                                                                                                              |

| 1                     | 1           | COMP                           | COMP is level-shifted and connected to the inverting input of the PWM comparator. Pull up COMP to VREF through a resistor and connect an optocoupler from COMP to GND for proper operation.                           |

| 2                     | _           | SYNC                           | Bidirectional Synchronization Input. When synchronizing with other MAX5071A/MAX5071Bs, the higher frequency part synchronizes all other devices.                                                                      |

|                       | - 2 ADV_CLK |                                | ADV_CLK is an 85ns clock output pulse preceding the rising edge of OUT (see Figure 4). Use the pulse to drive the secondary-side synchronous rectifiers through a pulse transformer or an optocoupler (see Figure 8). |

| 3                     | 3           | CS                             | Input to the PWM Comparator and Overcurrent Protection Comparator. The current-<br>sense signal is compared to the voltage at COMP.                                                                                   |

| 4                     | 4           | R <sub>T</sub> /C <sub>T</sub> | Timing Resistor and Capacitor Connection. A resistor $R_T$ from $R_T/C_T$ to VREF and capacitor $C_T$ from $R_T/C_T$ to GND set the oscillator frequency.                                                             |

| 5                     | 5           | GND                            | Power-Supply Ground. Place the $V_{\mbox{CC}}$ and VREF bypass capacitors close to the IC to minimize ground loops.                                                                                                   |

| 6                     | 6           | OUT                            | MOSFET Driver Output. OUT connects to the gate of the external n-channel MOSFET.                                                                                                                                      |

| 7                     | 7           | V <sub>CC</sub>                | Power-Supply Input for MAX5071. Bypass $V_{CC}$ to GND with a 0.1 $\mu F$ ceramic capacitor or a parallel combination of a 0.1 $\mu F$ and a higher value ceramic capacitor.                                          |

| 8                     | 8           | V <sub>REF</sub>               | 5V Reference Output. Bypass VREF to GND with a 0.1 $\mu$ F ceramic capacitor or a parallel combination of a 0.1 $\mu$ F and a higher value ceramic capacitor.                                                         |

## MAX5071A/MAX5071B/MAX5071C

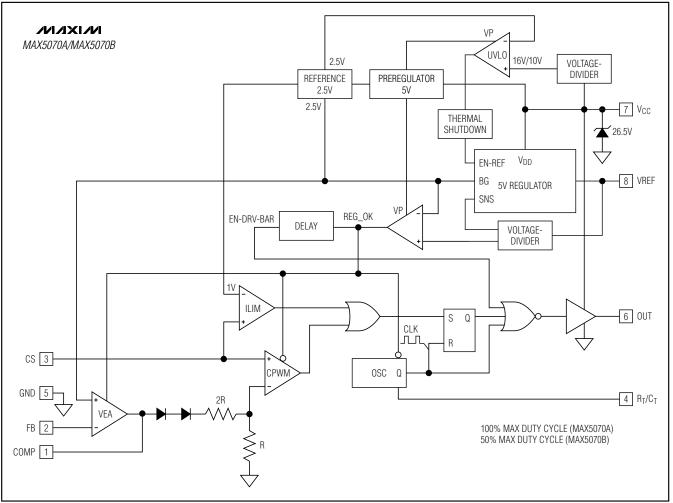

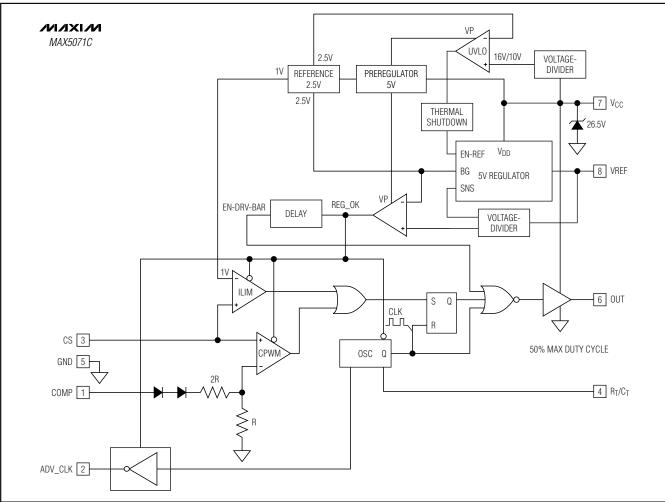

Figure 1. MAX5070A/MAX5070B Functional Diagram

## **Detailed Description**

The MAX5070/MAX5071 current-mode PWM controllers are designed for use as the control and regulation core of flyback or forward topology switching power supplies. These devices incorporate an integrated low-side driver, adjustable oscillator, error amplifier (MAX5070A/MAX5070B only), current-sense amplifier, 5V reference, and external synchronization capability (MAX5071A/MAX5071B only). An internal +26.5V current-limited V<sub>CC</sub> clamp prevents overvoltage during startup.

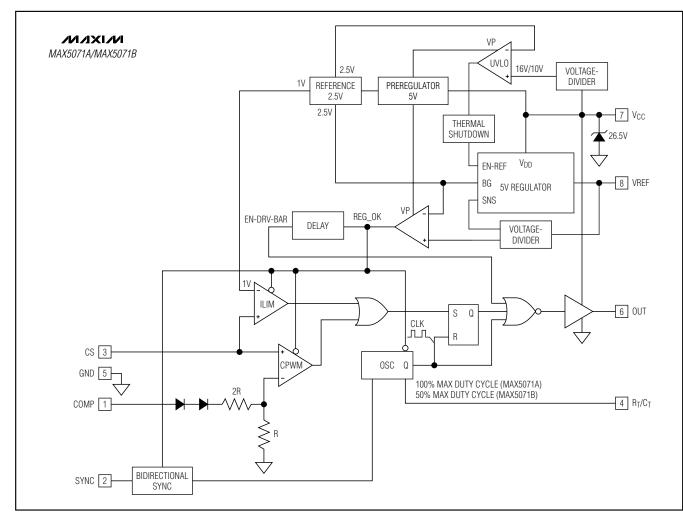

Five different versions of the MAX5070/MAX5071 are available. The MAX5070A/MAX5070B are the standard

versions with a feedback input (FB) and internal error amplifier. The MAX5071A/MAX5071B include bidirectional synchronization (SYNC). This enables multiple MAX5071A/MAX5071Bs to be connected and synchronized to the device with the highest frequency. The MAX5071C includes an ADV\_CLK output, which precedes the MAX5071C's drive output (OUT) by 110ns. Figures 1, 2, and 3 show the internal functional diagrams of the MAX5070A/MAX5070B, MAX5071A/MAX5071B, and MAX5071C, respectively. The MAX5070A/ MAX5071A are capable of 100% maximum duty cycle. The MAX5070B/MAX5071B/MAX5071C are designed to limit the maximum duty cycle to 50%.

Figure 2. MAX5071A/MAX5071B Functional Diagram

## **Current-Mode Control Loop**

The advantages of current-mode control over voltagemode control are twofold. First, there is the feed-forward characteristic brought on by the controller's ability to adjust for variations in the input voltage on a cycle-bycycle basis. Secondly, the stability requirements of the current-mode controller are reduced to that of a singlepole system unlike the double pole in the voltage-mode control scheme. The MAX5070/MAX5071 use a current-mode control loop where the output of the error amplifier is compared to the current-sense voltage (VCS). When the current-sense signal is lower than the noninverting input of the PWM comparator, the output of the CPWM comparator is low and the switch is turned on at each clock pulse. When the current-sense signal is higher than the inverting input of the CPWM, the output of the CPWM comparator is high and the switch is turned off.

Figure 3. MAX5071C Functional Diagram

## **Vcc and Startup**

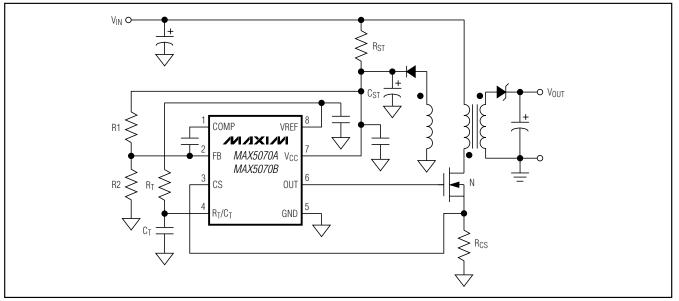

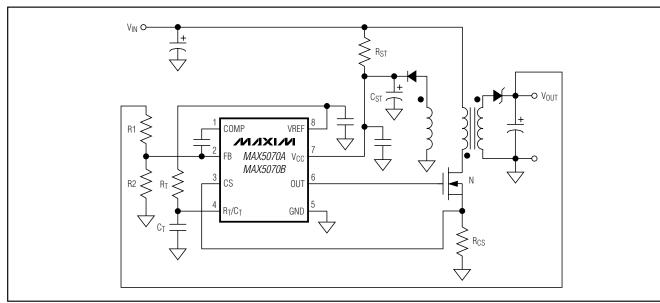

In normal operation, V<sub>CC</sub> is derived from a tertiary winding of the transformer. However, at startup there is no energy delivered through the transformer, thus a resistor must be connected from V<sub>CC</sub> to the input power source (see R<sub>ST</sub> and C<sub>ST</sub> in Figures 5 to 8). During startup, C<sub>ST</sub> charges up through R<sub>ST</sub>. The 5V reference generator, comparator, error amplifier, oscillator, and drive circuit remain off during UVLO to reduce startup current below  $65\mu$ A. When V<sub>CC</sub> reaches the undervoltage-lockout threshold of 16V, the output driver begins to switch and the tertiary winding will supply power to V<sub>CC</sub>. V<sub>CC</sub> has an internal 26.5V current-limited clamp at its input to protect the device from overvoltage during startup. Size the startup resistor, R<sub>ST</sub>, to supply both the maximum startup bias (I<sub>START</sub>) of the device ( $65\mu$ A max) and the charging current for C<sub>ST</sub>. The startup capacitor C<sub>ST</sub> must charge to 16V within the desired time period t<sub>ST</sub> (for example, 500ms). The size of the startup capacitor depends on:

- 1) IC operating supply current at a programmed oscillator frequency (f<sub>OSC</sub>).

- 2) The time required for the bias voltage, derived from a bias winding, to go from 0 to 11V.

- 3) The MOSFET total gate charge.

- 4) The operating frequency of the converter ( $f_{SW}$ ).

# MAX5070/MAX5071

## M AXI M

To calculate the capacitance required, use the following formula:

where:

## $I_G = Q_G f_{SW}$

ICC is the MAX5070/MAX5071s' maximum internal supply current after startup (see the Typical Operating Characteristics to find the IIN at a given fOSC). QG is the total gate charge for the MOSFET, fsw is the converter switching frequency, V<sub>HYST</sub> is the bootstrap UVLO hysteresis (6V), and tss is the soft-start time, which is set by external circuitry.

Size the resistor RST according to the desired startup time period, tst, for the calculated Cst. Use the following equations to calculate the average charging current (ICST) and the startup resistor (RST).

$$I_{CST} = \frac{V_{SUVR} \times C_{ST}}{t_{ST}}$$

$$R_{ST} \approx \frac{\left(V_{\rm INMIN} - \frac{V_{\rm SUVR}}{2}\right)}{I_{\rm CST} + I_{\rm START}}$$

Where VINMIN is the minimum input supply voltage for the application (36V for telecom), V<sub>SUVR</sub> is the bootstrap UVLO wake-up level (16V), and ISTART is the VIN supply current at startup (65µA, max). Choose a higher value for RST than the one calculated above if longer startup times can be tolerated in order to minimize power loss in RST.

The above startup method is applicable to circuits where the tertiary winding has the same phase as the output windings. Thus, the voltage on the tertiary winding at any given time is proportional to the output voltage and goes through the same soft-start period as the output voltage. The minimum discharge time of CST from 16V to 10V must be greater than the soft-start time (tss).

## Undervoltage Lockout (UVLO)

The minimum turn-on supply voltage for the MAX5070/MAX5071 is 16V. Once VCC reaches 16V, the reference powers up. There is 6V of hysteresis from the minimum turn-on voltage to the UVLO threshold. Once VCC reaches 16V, the MAX5070/MAX5071 will operate with V<sub>CC</sub> down to 10V. Once V<sub>CC</sub> goes below 10V the device is in UVLO. When in UVLO, the quiescent supply current into V<sub>CC</sub> falls back to 37µA (typ), and OUT and VREF are pulled low.

## **MOSFET Driver**

OUT drives an external n-channel MOSFET and swings from GND to V<sub>CC</sub>. Ensure that V<sub>CC</sub> remains below the absolute maximum VGS rating of the external MOSFET. OUT is a push-pull output with the on-resistance of the PMOS typically  $3.5\Omega$  and the on-resistance of the NMOS typically 4.5Ω. The driver can source 2A typically and sink 1A typically. This allows for the MAX5070/MAX5071 to quickly turn on and off high gate-charge MOSFETs.

Bypass Vcc with one or more 0.1µF ceramic capacitors to GND, placed close to the MAX5070/MAX5071. The average current sourced to drive the external MOSFET depends on the total gate charge (Q<sub>G</sub>) and operating frequency of the converter. The power dissipation in the MAX5070/MAX5071 is a function of the average output drive current (IDRIVE). Use the following equation to calculate the power dissipation in the device due to IDRIVE:

$$PD = (I_{DRIVE} + I_{CC}) \times V_{CC}$$

where ICC is the operating supply current. See the Typical Operating Characteristics for the operating supply current at a given frequency.

## Error Amplifier (MAX5070A/MAX5070B)

The MAX5070 includes an internal error amplifier. The inverting input is at FB and the noninverting input is internally connected to a 2.5V reference. The internal error amplifier is useful for nonisolated converter design (see Figure 6) and isolated design with primary-side regulation through a bias winding (see Figure 5). In the case of a nonisolated power supply, the output voltage will be:

$$V_{OUT} = \left(1 + \frac{R1}{R2}\right) \times 2.5V$$

where R1 and R2 are from Figure 6.

MAX5070/MAX507

## MAX5071A/MAX5071B/MAX5071C Feedback

The MAX5071A/MAX5071B/MAX5071C are designed to be used with either an external error amplifier when designed into a nonisolated converter or an error amplifier and optocoupler when designed into an isolated power supply. The COMP input is level-shifted and connected to the inverting terminal of the PWM comparator (CPWM). Connect the COMP pin to the output of the external error amplifier for nonisolated design. Pull COMP high externally to at least 5V (or VREF) and connect the optocoupler transistor as shown in Figures 7 and 8. COMP can be used for soft-start and also as a shutdown. See the Typical Operating Characteristics to find the turn-off COMP voltage at different temperatures. If the maximum external COMP voltage is below 4.9V, it may reduce the PWM current-limit threshold below 1V. Use the following equation to calculate minimum COMP voltage (VCOMP) required for a guaranteed peak primary current (IP-P):

$$V_{COMP} = (3 \times I_{P-P} \times R_{CS}) + 1.95V$$

where RCs is a current-sense resistor.

## Oscillator

The oscillator frequency is adjusted by adding an external capacitor and resistor at  $R_T/C_T$  (see  $R_T$  and  $C_T$  in the *Typical Application Circuits*).  $R_T$  is connected from  $R_T/C_T$  to the 5V reference (VREF) and  $C_T$  is connected from  $R_T/C_T$  to GND. VREF charges  $C_T$  through  $R_T$  until its voltage reaches 2.8V.  $C_T$  then discharges through an 8.3mA internal current sink until  $C_T$ 's voltage reaches 1.1V, at which time  $C_T$  is allowed to charge through  $R_T$  again. The oscillator's period will be the sum of the charge and discharge times of  $C_T$ . Calculate the charge time as:

$$t_{\rm C} = 0.57 \times R_{\rm T} \times C_{\rm T}$$

The discharge time is then:

$$t_{\rm D} = \frac{R_{\rm T} \times C_{\rm T} \times 10^3}{4.88 \times R_{\rm T} - 1.8 \times 10^3}$$

The oscillator frequency will then be:

$$f_{OSC} = \frac{1}{t_C + t_D}$$

For the MAX5070A/MAX5071A, the converter output switching frequency ( $f_{SW}$ ) is the same as the oscillator frequency ( $f_{OSC}$ ). For the MAX5070B/MAX5071B/MAX5071C, the output switching frequency is 1/2 the oscillator frequency.

## **Reference Output**

VREF is a 5V reference output that can source 20mA. Bypass VREF to GND with a  $0.1\mu$ F capacitor.

## **Current Limit**

The MAX5070/MAX5071 include a fast current-limit comparator to terminate the ON cycle during an overload or a fault condition. The current-sense resistor (R<sub>CS</sub>), connected between the source of the MOSFET and GND, sets the current limit. The CS input has a voltage trip level (V<sub>CS</sub>) of 1V. Use the following equation to calculate R<sub>CS</sub>:

$$R_{CS} = \frac{V_{CS}}{I_{P-P}}$$

IP-P is the peak current in the primary that flows through the MOSFET. When the voltage produced by this current (through the current-sense resistor) exceeds the currentlimit comparator threshold, the MOSFET driver (OUT) will turn the switch off within 60ns. In most cases, a small RC filter is required to filter out the leading-edge spike on the sense waveform. Set the time constant of the RC filter at 50ns. Use a current transformer to limit the losses in the current-sense resistor and achieve higher efficiency especially at low input-voltage operation.

## Synchronization (MAX5071A/MAX5071B) SYNC

SYNC is a bidirectional input/output that outputs a synchronizing pulse and accepts a synchronizing pulse from other MAX5071A/MAX5071Bs (see Figures 7 and 9). As an output, SYNC is an open-drain p-channel MOSFET driven from the internal oscillator and requires an external pulldown resistor (R<sub>SYNC</sub>) from between 500 $\Omega$  and 5k $\Omega$ . As an input, SYNC accepts the output pulses from other MAX5071A/MAX5071Bs.

Synchronize multiple MAX5071A/MAX5071Bs by connecting their SYNC pins together. All devices connected together will synchronize to the one operating at the highest frequency. The rising edge of SYNC will precede the rising edge of OUT by approximately the discharge time (t<sub>D</sub>) of the oscillator (see the *Oscillator* section). The pulse width of the SYNC output is equal to the time required to discharge the stray capacitance at SYNC through R<sub>SYNC</sub> plus the C<sub>T</sub> discharge time t<sub>D</sub>. Adjust R<sub>T</sub>/C<sub>T</sub> such that the minimum discharge time t<sub>D</sub> is 200ns.

Figure 4. ADV\_CLK

## Advance Clock Output (ADV\_CLK) (MAX5071C)

ADV\_CLK is an advanced pulse output provided to facilitate the easy implementation of secondary-side synchronous rectification using the MAX5071C. The ADV\_CLK pulse width is 85ns (typically) with its rising edge leading the rising edge of OUT by 110ns. Use this leading pulse to turn off the secondary-side synchronous-rectifier MOSFET (QS) before the voltage appears on the secondary (see Figure 8). Turning off the secondary-side synchronous MOSFET earlier avoids the shorting of the secondary in the forward converter. The ADV\_CLK pulse can be propagated to the secondary side using a pulse transformer or highspeed optocoupler. The 85ns pulse, with 3V drive voltage (10mA source), significantly reduces the volt-second requirement of the pulse transformer and the advanced pulse alleviates the need for a highspeed optocoupler.

### **Thermal Shutdown**

When the MAX5070/MAX5071s' die temperature goes above +150°C, the thermal-shutdown circuitry will shut down the 5V reference and pull OUT low.

## **Typical Application Circuits**

Figure 5. MAX5070A/MAX5070B Typical Application Circuit (Isolated Flyback with Primary-Side Regulation)

## **Typical Application Circuits (continued)**

Figure 6. MAX5070A/MAX5070B Typical Application Circuit (Non-Isolated Flyback)

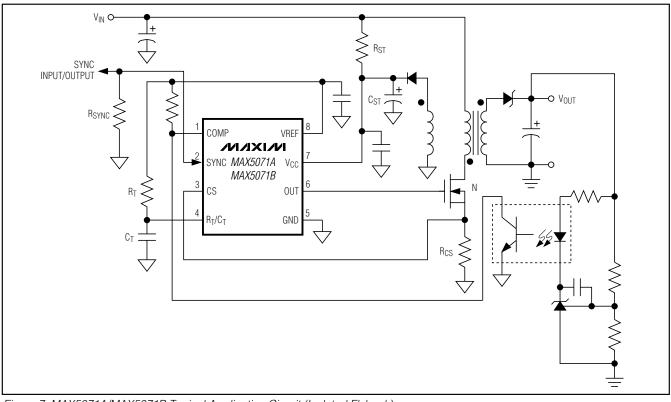

Figure 7. MAX5071A/MAX5071B Typical Application Circuit (Isolated Flyback)

MAX5070/MAX5071

**Typical Application Circuits (continued)**

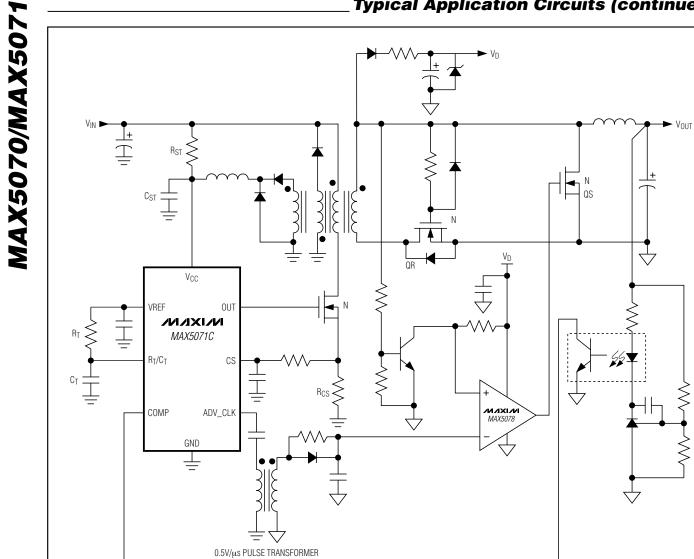

Figure 8. MAX5071C Typical Application Circuit (Isolated Forward with Secondary-Side Synchronous Rectification)

Figure 9. Synchronization of MAX5071s

MAX5070/MAX5071

## **Selector Guide**

| PART        | FEEDBACK/<br>ADVANCED CLOCK | MAXIMUM DUTY<br>CYCLE (%) | PIN-PACKAGE | PIN COMPATIBLE |

|-------------|-----------------------------|---------------------------|-------------|----------------|

| MAX5070AASA | Feedback                    | 100                       | 8 SO        | UC2842/UCC2842 |

| MAX5070AAUA | Feedback                    | 100                       | 8 µMAX      | UC2842/UCC2842 |

| MAX5070BASA | Feedback                    | 50                        | 8 SO        | UC2844/UCC2844 |

| MAX5070BAUA | Feedback                    | 50                        | 8 µMAX      | UC2844/UCC2844 |

| MAX5071AASA | Sync.                       | 100                       | 8 SO        | —              |

| MAX5071AAUA | Sync.                       | 100                       | 8 µMAX      | —              |

| MAX5071BASA | Sync.                       | 50                        | 8 SO        | —              |

| MAX5071BAUA | Sync.                       | 50                        | 8 µMAX      | —              |

| MAX5071CASA | ADV_CLK                     | 50                        | 8 SO        | _              |

| MAX5071CAUA | ADV_CLK                     | 50                        | 8 µMAX      | _              |

## **Pin Configurations (continued)**

## \_Ordering Information (continued)

| TEMP RANGE      | PIN-PACKAGE                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------|

| -40°C to +125°C | 8 SO                                                                                                           |

| -40°C to +125°C | 8 µMAX                                                                                                         |

| -40°C to +125°C | 8 SO                                                                                                           |

| -40°C to +125°C | 8 µMAX                                                                                                         |

| -40°C to +125°C | 8 SO                                                                                                           |

| -40°C to +125°C | 8 µMAX                                                                                                         |

|                 | -40°C to +125°C<br>-40°C to +125°C<br>-40°C to +125°C<br>-40°C to +125°C<br>-40°C to +125°C<br>-40°C to +125°C |

Specify lead-free by adding the + symbol at the end of the part number when ordering.

## Chip Information

TRANSISTOR COUNT: 1987 PROCESS: BICMOS

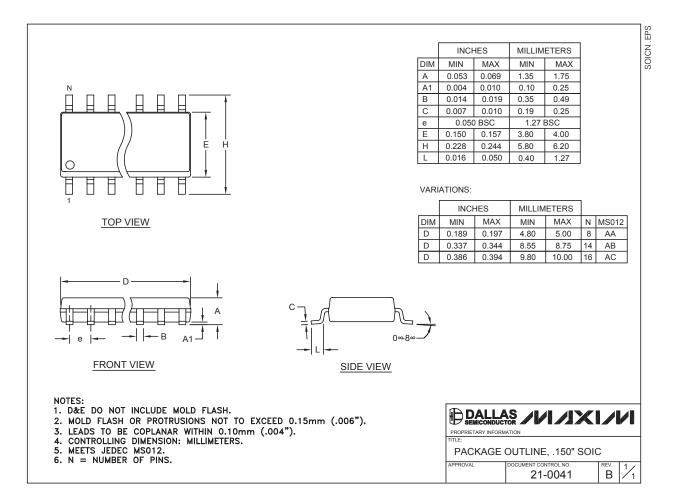

## \_Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

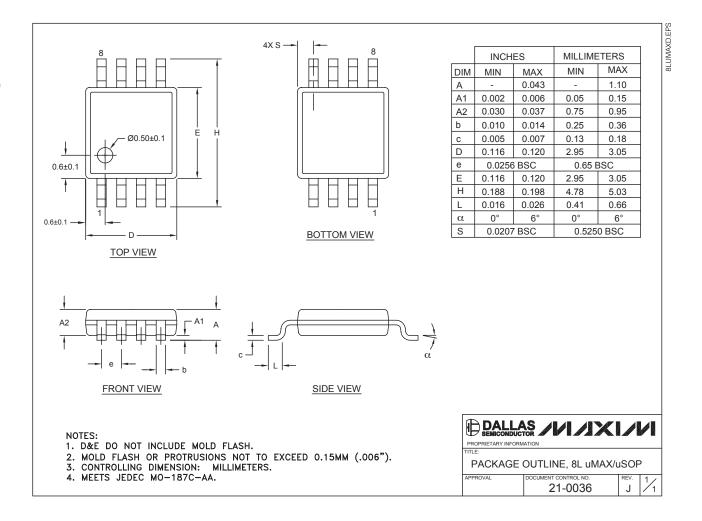

## \_Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

22

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

is a registered trademark of Maxim Integrated Products, Inc.