# onsemi

# Dual Supply, 2-Bit Voltage Translator / Isolator for I<sup>2</sup>C Applications

# **FXMAR2102**

#### Description

The FXMAR2102 is a high-performance configurable dual-voltage-supply translator for bi-directional voltage translation over a wide range of input and output voltages levels. The FXMAR2102 also works in a push- pull environment.

It is intended for use as a voltage translator between  $I^2C$ -Bus compliant masters and slaves. Internal 10 k $\Omega$  pull-up resistors are provided.

The device is designed so the A port tracks the V<sub>CCA</sub> level and the B port tracks the V<sub>CCB</sub> level. This allows for bi–directional A/B–port voltage translation between any two levels from 1.65 V to 5.5 V. V<sub>CCA</sub> can equal V<sub>CCB</sub> from 1.65 V to 5.5 V. Either V<sub>CC</sub> can be powered–up first. Internal power–down control circuits place the device in 3–state if either V<sub>CC</sub> is removed.

The two ports of the device have automatic direction-sense capability. Either port may sense an input signal and transfer it as an output signal to the other port.

#### Features

- Bi-Directional Interface between Any Two Levels: 1.65 V to 5.5 V

- No Direction Control Needed

- Internal 10 kΩ Pull–Up Resistors

- System GPIO Resources Not Required when OE Tied to V<sub>CCA</sub>

- I<sup>2</sup>C Bus Isolation

- A/B Port  $V_{OL}$  = 175 mV (Typical),  $V_{IL}$  = 150 mV,  $I_{OL}$  = 6 mA

- Open-Drain Inputs / Outputs

- Works in Push Pull Environment

- Accommodates Standard–Mode and Fast–Mode I<sup>2</sup>C–Bus Devices

- Supports I<sup>2</sup>C Clock Stretching & Multi–Master

- Fully Configurable: Inputs and Outputs Track V<sub>CC</sub>

- Non-Preferential Power-Up; Either V<sub>CC</sub> Can Power-Up First

- Outputs Switch to 3–State if Either V<sub>CC</sub> is at GND

- Tolerant Output Enable: 5 V

- Packaged in 8–Terminal Leadless MicroPak<sup>™</sup> (1.6 mm x 1.6 mm) and Ultrathin MLP (1.2 mm x 1.4 mm)

- ESD Protection Exceeds:

- B Port: 8 kV HBM ESD (vs. GND & vs. V<sub>CCB</sub>)

- ◆ All Pins: 4 kV HBM ESD (per JESD22-A114)

- 2 kV CDM (per JESD22–C101)

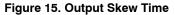

UQFN8, 1.4x1.2, 0.4P CASE 523AS

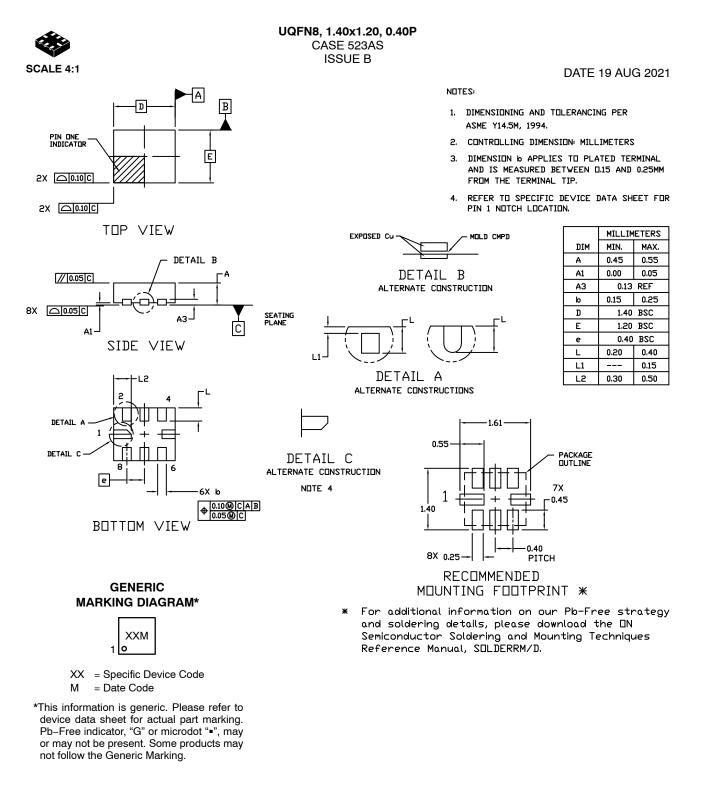

UQFN8 1.6X1.6, 0.5P CASE 523AY

#### MARKING DIAGRAM

- BU = Device Code

- &K = 2-Digits Lot Run Traceability Code

- &2 = 2-Digit Date Code

- &Z = Assembly Plant Code

1

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 13 of this data sheet.

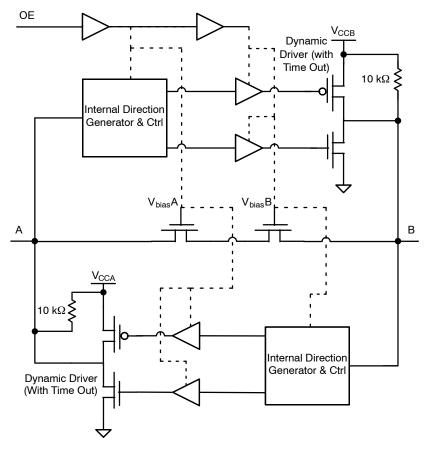

#### **BLOCK DIAGRAM**

Figure 1. Block Diagram, 1 of 2 Channels

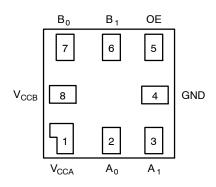

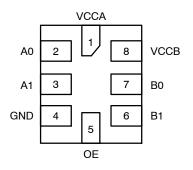

## **PIN CONFIGURATION**

Figure 2. MicroPak (Top-Through View)

Figure 3. UMLP (Top-Through View)

# **PIN DEFINITIONS**

| Pin No. | Name                            | Description                      |  |  |

|---------|---------------------------------|----------------------------------|--|--|

| 1       | V <sub>CCA</sub>                | A-Side Power Supply              |  |  |

| 2, 3    | A <sub>0</sub> , A <sub>1</sub> | A-Side Inputs or 3-State Outputs |  |  |

| 4       | GND                             | Ground                           |  |  |

| 5       | OE                              | Output Enable Input              |  |  |

| 6, 7    | B <sub>1</sub> , B <sub>0</sub> | B-Side Inputs or 3-State Outputs |  |  |

| 8       | V <sub>CCB</sub>                | B-Side Power Supply              |  |  |

#### TRUTH TABLE

| Control          |                  |

|------------------|------------------|

| OE (Note 1)      | Outputs          |

| LOW Logic Level  | 3-State          |

| HIGH Logic Level | Normal Operation |

If the OE pin is driven LOW, the FXMAR2102 is disabled and the A<sub>0</sub>, A<sub>1</sub>, B<sub>0</sub>, and B<sub>1</sub> pins (including dynamic drivers) are forced into 3-state and all four 10 kΩ internal pull-up resisters are decoupled from their respective V<sub>CC</sub>.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                              | Pa                                     | Min                                         | Мах  | Unit                     |    |

|-------------------------------------|----------------------------------------|---------------------------------------------|------|--------------------------|----|

| V <sub>CCA</sub> , V <sub>CCB</sub> | Supply Voltage                         |                                             | -0.5 | 7.0                      | V  |

| V <sub>IN</sub>                     | DC Input Voltage                       | A Port                                      | -0.5 | 7.0                      |    |

|                                     |                                        | B Port                                      | -0.5 | 7.0                      |    |

|                                     |                                        | Control Input (OE)                          | -0.5 | 7.0                      |    |

| Vo                                  | Output Voltage (Note 2)                | A <sub>n</sub> Outputs 3-State              | -0.5 | 7.0                      | V  |

|                                     |                                        | B <sub>n</sub> Outputs 3-State              | -0.5 | 7.0                      |    |

|                                     |                                        | A <sub>n</sub> Outputs Active               | -0.5 | V <sub>CCA</sub> + 0.5 V |    |

|                                     |                                        | B <sub>n</sub> Outputs Active               | -0.5 | V <sub>CCB</sub> + 0.5 V |    |

| I <sub>IK</sub>                     | DC Input Diode Current                 | At V <sub>IN</sub> < 0 V                    | -    | -50                      | mA |

| I <sub>OK</sub>                     | DC Output Diode Current                | At $V_0 < 0 V$                              | -    | -50                      | mA |

|                                     |                                        | At $V_O > V_{CC}$                           | -    | +50                      |    |

| I <sub>OH</sub> / I <sub>OL</sub>   | DC Output Source/Sink Current          | •                                           | -50  | +50                      | mA |

| Icc                                 | DC $V_{CC}$ or Ground Current per Supp | oly Pin                                     | -    | ±100                     | mA |

| PD                                  | Power Dissipation                      | At 400 KHz                                  | -    | 0.129                    | mW |

| T <sub>STG</sub>                    | Storage Temperature Range              |                                             | -65  | +150                     | °C |

| ESD                                 | Electrostatic Discharge Capability     | Human Body Model, B-Port Pins               | -    | 8                        | kV |

|                                     |                                        | Human Body Model, All Pins<br>(JESD22-A114) | -    | 4                        |    |

|                                     |                                        | Charged Device Mode, JESD22-C101            | -    | 2                        |    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2.  $I_O$  absolute maximum rating must be observed.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                              | Р                              | Min                  | Max  | Unit             |      |

|-------------------------------------|--------------------------------|----------------------|------|------------------|------|

| V <sub>CCA</sub> , V <sub>CCB</sub> | Power Supply Operating         |                      | 1.65 | 5.50             | V    |

| V <sub>IN</sub>                     | Input Voltage (Note 3)         | A-Port               | 0    | 5.5              | V    |

|                                     |                                | B-Port               | 0    | 5.5              |      |

|                                     |                                | Control Input (OE)   | 0    | V <sub>CCA</sub> |      |

| $\Theta_{JA}$                       | Thermal Resistance             | 8-Lead MicroPak      | -    | 279              | °C/W |

|                                     |                                | 8-Lead Ultrathin MLP | -    | 302              |      |

| Τ <sub>Α</sub>                      | Free Air Operating Temperature | -40                  | +85  | °C               |      |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

3. All unused inputs and I/O pins must be held at V<sub>CCI</sub> or GND. V<sub>CCI</sub> is the V<sub>CC</sub> associated with the input side.

# FUNCTIONAL DESCRIPTION

#### Power-Up / Power-Down Sequencing

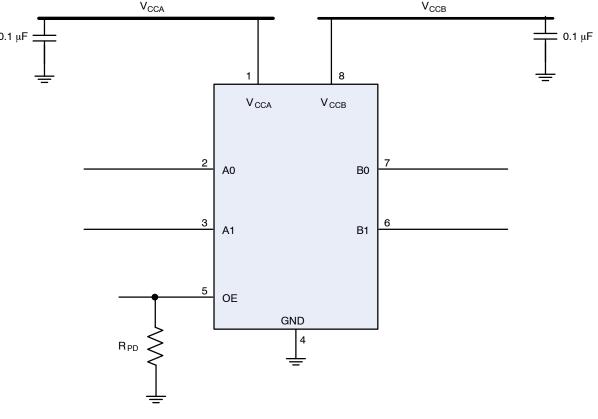

FXM translators offer an advantage in that either  $V_{CC}$  may be powered up first. This benefit derives from the chip design. When either  $V_{CC}$  is at 0 V, outputs are in a high-impedance state. The control input (OE) is designed to track the  $V_{CCA}$  supply. A pull-down resistor tying OE to GND should be used to ensure that bus contention, excessive currents, or oscillations do not occur during power-up/-down. The size of the pull-down resistor is based upon the current-sinking capability of the device driving the OE pin.

- *The recommended power-up sequence is:*

- 1. Apply power to the first  $V_{CC}$ .

- 2. Apply power to the second  $V_{CC}$ .

- 3. Drive the OE input HIGH to enable the device.

- The recommended power-down sequence is:

- 1. Drive OE input LOW to disable the device.

- 2. Remove power from either  $V_{CC}$ .

- 3. Remove power from the other  $V_{CC}$ .

#### NOTE:

4. Alternatively, the OE pin can be hardwired to  $V_{CCA}$  to save GPIO pins. If OE is hardwired to  $V_{CCA}$ , either  $V_{CC}$  can be powered up or down first.

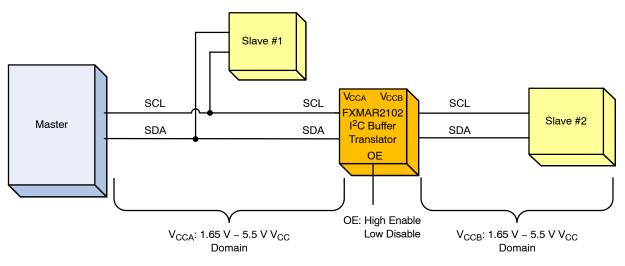

## APPLICATION CIRCUIT

Figure 4. Application Circuit

#### **APPLICATION NOTES**

The FXMAR2102 has open-drain I/Os and includes a total of four 10 k $\Omega$  internal pull-up resistors (R<sub>PU</sub>) on each of the four data I/O pins, as shown in Figure 4. If a pair of data I/O pins (An/Bn) is not used, both pins should disconnected, eliminating unwanted current flow through the internal RPUs. External RPUs can be added to the I/Os to reduce the total RPU value, depending on the total bus capacitance. The designer is free to lower the total pull-up resistor value to meet the maximum I<sup>2</sup>C edge rate per the I<sup>2</sup>C specification (UM10204 rev. 03, June 19, 2007). For example, according to the I<sup>2</sup>C specification, the maximum edge rate (30% - 70%) during Fast Mode (400 kbit/s) is 300 ns. If the bus capacitance is approaching the maximum 400 pF, a lower total R<sub>PU</sub> value helps keep the rise time below 300 ns (Fast Mode). Likewise, the I<sup>2</sup>C specification also specifies a minimum Serial Clock Line High Time of 600 ns during Fast Mode (400 kHz). Lowering the total RPU also helps increase the SCL High Time. If the bus capacitance approaches 400 pF, it may make sense to use the FXMA2102, which does not contain internal RPUs. Then calculate the ideal external R<sub>PU</sub> value.

#### NOTE:

5. Section 7.1 of the I<sup>2</sup>C specification provides an excellent guideline for pull–up resistor sizing.

#### **Theory of Operation**

The FXMAR2102 is designed for high-performance level shifting and buffer / repeating in an  $I^2C$  application. Figure 1 shows that each bi-directional channel contains two series-Npassgates and two dynamic drivers. This hybrid architecture is highly beneficial in an  $I^2C$  application where auto-direction is a necessity.

For example, during the following three I<sup>2</sup>C protocol events:

- Clock Stretching

- Slave's ACK Bit (9<sup>th</sup> bit = 0) following a Master's Write Bit (8<sup>th</sup> bit = 0)

- Clock Synchronization and Multi-Master Arbitration

The bus direction needs to change from master-to-slave to slave-to-master without the occurrence of an edge. If there is an I<sup>2</sup>C translator between the master and slave in these examples, the I<sup>2</sup>C translator must change direction when both A and B ports are LOW. The Npassgates can accomplish this task very efficiently because, when both A and B ports are LOW, the Npassgates act as a low-resistive short between the A and B ports.

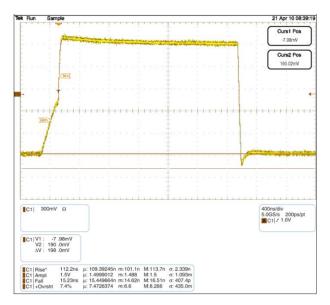

Due to  $I^2C$ 's open-drain topology,  $I^2C$  masters and slaves are not push/pull drivers. Logic LOWs are "pulled down" (Isink), while logic HIGHs are "let go" (3-state). For example, when the master lets go of SCL (SCL always comes from the master), the rise time of SCL is largely determined by the RC time constant, where R = RPU and C = the bus capacitance. If the FXMAR2102 is attached to the master [on the A port] and there is a slave on the B port, the Npassgates act as a low-resistive short between both ports until either of the port's  $V_{CC}/2$  thresholds are reached. After the RC time constant has reached the  $V_{CC}/2$  threshold of either port, the port's edge detector triggers both dynamic drivers to drive their respective ports in the LOW-to-HIGH (LH) direction, accelerating the rising edge. The resulting rise time resembles the scope shot in Figure 5. Effectively, two distinct slew rates appear in rise time. The first slew rate (slower) is the RC time constant of the bus. The second slew rate (much faster) is the dynamic driver accelerating the edge.

If both the A and B ports of the translator are HIGH, a high–impedance path exists between the A and B ports because both the Npassgates are turned off. If a master or slave device decides to pull SCL or SDA LOW, that device's driver pulls down ( $I_{sink}$ ) SCL or SDA until the edge reaches the A or B port  $V_{CC}/2$  threshold. When either the A or B port threshold is reached, the port's edge detector triggers both dynamic drivers to drive their respective ports in the HIGH–to–LOW (HL) direction, accelerating the falling edge.

Figure 5. Waveform C: 600 pF, Total R<sub>PU</sub>: 2.2 k $\Omega$

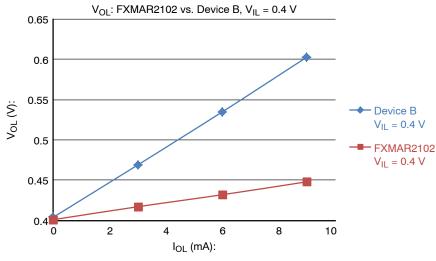

## V<sub>OL</sub> vs. I<sub>OL</sub>

The I<sup>2</sup>C specification mandates a maximum  $V_{IL}$  (I<sub>OL</sub> of 3 mA) of  $V_{CC} \cdot 0.3$  and a maximum  $V_{OL}$  of 0.4 V. If there is a master on the A port of an I<sup>2</sup>C translator with a  $V_{CC}$  of 1.65 V and a slave on the I<sup>2</sup>C translator B port with a  $V_{CC}$  of 3.3 V, the maximum  $V_{IL}$  of the master is (1.65 V x 0.3) 495 mV. The slave could legally transmit a valid logic LOW of 0.4 V to the master.

If the I<sup>2</sup>C translator's channel resistance is too high, the voltage drop across the translator could present a  $V_{IL}$  to the master greater than 495 mV. To complicate matters, the I<sup>2</sup>C specification states that 6 mA of I<sub>OL</sub> is recommended for bus

capacitances approaching 400 pF. More  $I_{OL}$  increases the voltage drop across the  $I^2C$  translator. The  $I^2C$  application benefits when  $I^2C$  translators exhibit low  $V_{OL}$  performance.

Figure 6 depicts typical FXMAR2102  $V_{OL}$  performance vs. the competition, given a 0.4 V  $V_{IL}.$

Figure 6. Device Comparison

#### I<sup>2</sup>C-Bus Isolation

The FXMAR2102 supports I<sup>2</sup>C–Bus isolation for the following conditions:

- Bus isolation if bus clear

- Bus isolation if either V<sub>CC</sub> goes to ground

#### Bus Clear

Because the I<sup>2</sup>C specification defines the minimum SCL frequency of DC, the SCL signal can be held LOW forever; however, this condition shuts down the I<sup>2</sup>C bus. The I<sup>2</sup>C specification refers to this condition as "Bus Clear". In Figure 7; if slave #2 holds down SCL forever, the master and slave #1 are not able to communicate because the FXMAR2102 passes the SCL stuck–LOW condition from

slave #2 to slave #1 and as the master. However, if the OE pin is pulled LOW (disabled), both ports (A and B) are 3-stated. This results in the FXMAR2102 isolating slave #2 from the master and slave #1, allowing full communication between the master and slave #1.

#### $V_{CC}$ to GND

If slave #2 is a camera that is suddenly removed from the I<sup>2</sup>C bus, resulting in V<sub>CCB</sub> transitioning from a valid V<sub>CC</sub> (1.65 V – 5.5 V) to 0 V; the FXMAR2102 automatically forces SCL and SDA on both its A and B ports into 3–state. Once V<sub>CCB</sub> has reached 0 V, full I<sup>2</sup>C communication between the master and slave #1 remains undisturbed.

Figure 7. Bus Isolation

| Symbol              | Parameter                               |                                       | Condition                                           | V <sub>CCA</sub> (V) | V <sub>CCB</sub> (V) | Min                   | Тур | Max                  | Unit |

|---------------------|-----------------------------------------|---------------------------------------|-----------------------------------------------------|----------------------|----------------------|-----------------------|-----|----------------------|------|

| V <sub>IHA</sub>    | High Level Input                        | Data Inp                              | outs A <sub>n</sub>                                 | 1.65 – 5.50          | 1.65 – 5.50          | V <sub>CCA</sub> -0.4 | -   | -                    | V    |

|                     | Voltage A                               | Control                               | Control Input OE                                    |                      | 1.65 – 5.50          | $0.7 \times V_{CCA}$  | -   | -                    |      |

| V <sub>IHB</sub>    | High Level Input<br>Voltage B           | Data Inp                              | outs B <sub>n</sub>                                 | 1.65 – 5.50          | 1.65 – 5.50          | V <sub>CCB</sub> -0.4 | -   | -                    | V    |

| V <sub>ILA</sub>    | Low Level Input                         | Data Inp                              | outs A <sub>n</sub>                                 | 1.65 – 5.50          | 1.65 – 5.50          | -                     | -   | 0.4                  | V    |

|                     | Voltage A                               | Control                               | Input OE                                            | 1.65 - 5.50          | 1.65 – 5.50          | -                     | -   | $0.3 \times V_{CCA}$ |      |

| V <sub>ILB</sub>    | Low Level Input<br>Voltage B            | Data Inp                              | outs B <sub>n</sub>                                 | 1.65 – 5.50          | 1.65 – 5.50          | -                     | -   | 0.4                  | V    |

| V <sub>OL</sub>     | Low Level Output                        | $V_{IL} = 0.7$                        | 15 V                                                | 1.65–5.50            | 1.65–5.50            | -                     | -   | 0.4                  | V    |

|                     | Voltage                                 | l <sub>OL</sub> = 6 I                 | mA                                                  |                      |                      |                       | -   |                      |      |

| ۱L                  | Input Leakage<br>Current                | Control<br>or GND                     | Input OE, V <sub>IN</sub> = V <sub>CCA</sub>        | 1.65 – 5.50          | 1.65 – 5.50          | -                     | -   | ±1.0                 | μΑ   |

| I <sub>OFF</sub>    | Power-Off Leakage<br>Current            | A <sub>n</sub>                        | $V_{IN}$ or $V_O = 0$ V to 5.5 V                    | 0                    | 5.50                 | -                     | -   | ±2.0                 | μA   |

|                     |                                         | B <sub>n</sub>                        | V <sub>IN</sub> or V <sub>O</sub> = 0 V to<br>5.5 V | 5.50                 | 0                    | -                     | -   | ±2.0                 |      |

| I <sub>OZ</sub>     | 3-State Output<br>Leakage               | A <sub>n</sub> , B <sub>n</sub>       | $V_{O} = 0 V \text{ to } 5.5 V,$<br>OE = $V_{IL}$   | 5.50                 | 5.50                 | -                     | -   | ±2.0                 | μΑ   |

|                     | (Note 7)                                | A <sub>n</sub>                        | V <sub>O</sub> = 0 V to 5.5 V,<br>OE = Don't Care   | 5.50                 | 0                    | -                     | -   | ±2.0                 |      |

|                     |                                         | B <sub>n</sub>                        | V <sub>O</sub> = 0 V to 5.5 V,<br>OE = Don't Care   | 0                    | 5.50                 | -                     | -   | ±2.0                 |      |

| I <sub>CCA</sub> /B | Quiescent Supply<br>Current (Note 8, 9) | $V_{IN} = V_0$                        | $_{CCI}$ or Floating, $I_{O} = 0$                   | 1.65 – 5.50          | 1.65 – 5.50          | -                     | -   | 5.0                  | μA   |

| I <sub>CCZ</sub>    | Quiescent Supply<br>Current (Note 8)    | $V_{IN} = V_0$<br>OE = V <sub>I</sub> | <sub>CCI</sub> or GND, I <sub>O</sub> = 0,<br>L     | 1.65 – 5.50          | 1.65 – 5.50          | -                     | -   | 5.0                  | μA   |

| I <sub>CCA</sub>    | Quiescent Supply                        |                                       | 5 V or GND, I <sub>O</sub> = 0,                     | 0                    | 1.65 – 5.50          | -                     | -   | -2.0                 | μA   |

|                     | Current (Note 7)                        | OE = D                                | on't Care, B <sub>n</sub> to A <sub>n</sub>         | 1.65 - 5.50          | 0                    | -                     | -   | 2.0                  |      |

| I <sub>CCB</sub>    | Quiescent Supply                        | $V_{IN} = 5.$                         | 5 V or GND, I <sub>O</sub> = 0,                     | 1.65 – 5.50          | 0                    | _                     | _   | -2.0                 | μA   |

|                     | Current (Note 7)                        | UE = D                                | on't Care, A <sub>n</sub> to B <sub>n</sub>         | 0                    | 1.65 – 5.50          | -                     | -   | 2.0                  |      |

| R <sub>PU</sub>     | Resistor Pull–up<br>Value               | VCCA 8                                | VCCB Sides                                          | 1.65–5.50            | 1.65 – 5.50          | -                     | 10  | -                    | Ω    |

#### DC ELECTRICAL CHARACTERISTICS ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ )

6. This table contains the output voltage for static conditions. Dynamic drive specifications are given in Dynamic Output Electrical Characteristics.

"Don't Care" indicates any valid logic level.

V<sub>CCI</sub> is the V<sub>CC</sub> associated with the input side.

Reflects current per supply, V<sub>CCA</sub> or V<sub>CCB</sub>.

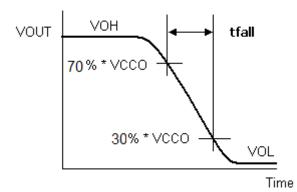

#### DYNAMIC OUTPUT ELECTRICAL CHARACTERISTICS

**OUTPUT RISE** / FALL TIME (Note 10) (Output load:  $C_L = 50 \text{ pF}$ ,  $R_{PU} = NC$ , push / pull driver, and  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .)

|                   |                                            |              | V <sub>CCO</sub> (N | lote 11)     |                |      |

|-------------------|--------------------------------------------|--------------|---------------------|--------------|----------------|------|

|                   |                                            | 4.5 to 5.5 V | 3.0 to 3.6 V        | 2.3 to 2.7 V | 1.65 to 1.95 V |      |

| Symbol            | Parameter                                  | Тур          | Тур                 | Тур          | Тур            | Unit |

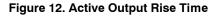

| t <sub>rise</sub> | Output Rise Time; A Port, B Port (Note 12) | 3            | 4                   | 5            | 7              | ns   |

| t <sub>fall</sub> | Output Fall Time; A Port, B Port (Note 13) | 1            | 1                   | 1            | 1              | ns   |

10. Output rise and fall times guaranteed by design simulation and characterization; not production tested.

11.  $V_{CCO}$  is the  $V_{CC}$  associated with the output side. 12. See Figure 12.

13. See Figure 13.

#### DYNAMIC OUTPUT ELECTRICAL CHARACTERISTICS

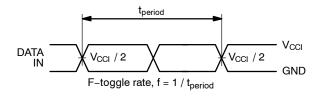

**MAXIMUM DATA RATE** (Note 14) (Output load:  $C_L = 50 \text{ pF}$ ,  $R_{PU} = NC$ , push / pull driver, and  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .)

|                  |           |              | Vc           | СВ           |                |      |

|------------------|-----------|--------------|--------------|--------------|----------------|------|

|                  |           | 4.5 to 5.5 V | 3.0 to 3.6 V | 2.3 to 2.7 V | 1.65 to 1.95 V |      |

| V <sub>CCA</sub> | Direction |              | Minir        | nums         |                | Unit |

| 4.5 V to 5.5 V   | A to B    | 50           | 50           | 40           | 30             | MHz  |

|                  | B to A    | 50           | 50           | 40           | 40             |      |

| 3.0 V to 3.6 V   | A to B    | 50           | 50           | 40           | 19             | MHz  |

|                  | B to A    | 50           | 50           | 40           | 40             |      |

| 2.3 V to 2.7 V   | A to B    | 40           | 40           | 30           | 19             | MHz  |

|                  | B to A    | 40           | 40           | 30           | 30             |      |

| 1.65 V to 1.95 V | A to B    | 40           | 40           | 30           | 19             | MHz  |

|                  | B to A    | 30           | 30           | 19           | 19             |      |

14.F-toggle guaranteed by design simulation; not production tested.

|                        |                          |        |       |        | vc   | СВ           |      |         |        |      |

|------------------------|--------------------------|--------|-------|--------|------|--------------|------|---------|--------|------|

|                        |                          | 4.5 to | 5.5 V | 3.0 to |      | 2.3 to 2.7 V |      | 1.65 to | 1.95 V | 1    |

| Symbol                 | Parameter                | Тур    | Max   | Тур    | Max  | Тур          | Max  | Тур     | Max    | Unit |

| CCA = 4.5              | to 5.5 V                 |        |       |        |      |              |      |         |        |      |

| t <sub>PLH</sub>       | A to B                   | 1      | 3     | 1      | 3    | 1            | 3    | 1       | 3      | ns   |

|                        | B to A                   | 1      | 3     | 2      | 4    | 3            | 5    | 4       | 7      | 1    |

| t <sub>PHL</sub>       | A to B                   | 2      | 4     | 3      | 5    | 4            | 6    | 5       | 7      | ns   |

|                        | B to A                   | 2      | 4     | 2      | 5    | 2            | 6    | 5       | 7      | 1    |

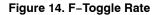

| t <sub>PZL</sub>       | OE to A                  | 4      | 5     | 6      | 10   | 5            | 9    | 7       | 15     | ns   |

|                        | OE to B                  | 3      | 5     | 4      | 7    | 5            | 8    | 10      | 15     | 1    |

| t <sub>PLZ</sub>       | OE to A                  | 65     | 100   | 65     | 105  | 65           | 105  | 65      | 105    | ns   |

|                        | OE to B                  | 5      | 9     | 6      | 10   | 7            | 12   | 9       | 16     | 1    |

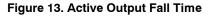

| t <sub>skew</sub>      | A Port, B Port (Note 16) | 0.50   | 1.50  | 0.50   | 1.00 | 0.50         | 1.00 | 0.50    | 1.00   | ns   |

| / <sub>CCA</sub> = 3.0 | to 3.6 V                 |        |       | •      |      | •            | •    | •       |        |      |

| t <sub>PLH</sub>       | A to B                   | 2.0    | 5.0   | 1.5    | 3.0  | 1.5          | 3.0  | 1.5     | 3.0    | ns   |

|                        | B to A                   | 1.5    | 3.0   | 1.5    | 4.0  | 2.0          | 6.0  | 3.0     | 9.0    | 1    |

| t <sub>PHL</sub>       | A to B                   | 2.0    | 4.0   | 2.0    | 4.0  | 2.0          | 5.0  | 3.0     | 5.0    | ns   |

|                        | B to A                   | 2.0    | 4.0   | 2.0    | 4.0  | 2.0          | 5.0  | 3.0     | 5.0    | 1    |

| t <sub>PZL</sub>       | OE to A                  | 4.0    | 8.0   | 5.0    | 9.0  | 6.0          | 11.0 | 7.0     | 15.0   | ns   |

|                        | OE to B                  | 4.0    | 8.0   | 6.0    | 9.0  | 8.0          | 11.0 | 10.0    | 14.0   | 1    |

| t <sub>PLZ</sub>       | OE to A                  | 100    | 115   | 100    | 115  | 100          | 115  | 100     | 115    | ns   |

|                        | OE to B                  | 5      | 10    | 4      | 8    | 5            | 10   | 9       | 15     | 1    |

| t <sub>skew</sub>      | A Port, B Port (Note 16) | 0.5    | 1.5   | 0.5    | 1.0  | 0.5          | 1.0  | 0.5     | 1.0    | ns   |

| / <sub>CCA</sub> = 2.3 | to 2.7 V                 | •      | -     | •      |      | •            | •    | •       | -      |      |

| t <sub>PLH</sub>       | A to B                   | 2.5    | 5.0   | 2.5    | 5.0  | 2.0          | 4.0  | 1.0     | 3.0    | ns   |

|                        | B to A                   | 1.5    | 3.0   | 2.0    | 4.0  | 3.0          | 6.0  | 5.0     | 10.0   | 1    |

| t <sub>PHL</sub>       | A to B                   | 2.0    | 5.0   | 2.0    | 5.0  | 2.0          | 5.0  | 3.0     | 6.0    | ns   |

|                        | B to A                   | 2.0    | 5.0   | 2.0    | 5.0  | 2.0          | 5.0  | 3.0     | 6.0    | 1    |

| t <sub>PZL</sub>       | OE to A                  | 5.0    | 10.0  | 5.0    | 10.0 | 6.0          | 12.0 | 9.0     | 18.0   | ns   |

|                        | OE to B                  | 4.0    | 8.0   | 4.5    | 9.0  | 5.0          | 10.0 | 9.0     | 18.0   | 1    |

| t <sub>PLZ</sub>       | OE to A                  | 100    | 115   | 100    | 115  | 100          | 115  | 100     | 115    | ns   |

|                        | OE to B                  | 65     | 110   | 65     | 110  | 65           | 115  | 12      | 25     | 1    |

| t <sub>skew</sub>      | A Port, B Port (Note 16) | 0.5    | 1.5   | 0.5    | 1.0  | 0.5          | 1.0  | 0.5     | 1.0    | ns   |

| / <sub>CCA</sub> = 1.6 | 5 to 1.95 V              |        |       |        | -    |              |      |         |        | -    |

| t <sub>PLH</sub>       | A to B                   | 4      | 7     | 4      | 7    | 5            | 8    | 5       | 10     | ns   |

|                        | B to A                   | 1.0    | 2.0   | 1.0    | 2.0  | 1.5          | 3.0  | 5.0     | 10.0   |      |

| t <sub>PHL</sub>       | A to B                   | 5      | 8     | 3      | 7    | 3            | 7    | 3       | 7      | ns   |

|                        | B to A                   | 4      | 8     | 3      | 7    | 3            | 7    | 3       | 7      | 1    |

| t <sub>PZL</sub>       | OE to A                  | 11     | 15    | 11     | 14   | 14           | 28   | 14      | 23     | ns   |

|                        | OE to B                  | 6      | 14    | 6      | 14   | 6            | 14   | 9       | 16     | 1    |

| t <sub>PLZ</sub>       | OE to A                  | 75     | 115   | 75     | 115  | 75           | 115  | 75      | 115    | ns   |

|                        | OE to B                  | 75     | 115   | 75     | 115  | 75           | 115  | 75      | 115    | 1    |

| t <sub>skew</sub>      | A Port, B Port (Note 16) | 0.5    | 1.5   | 0.5    | 1.0  | 0.5          | 1.0  | 0.5     | 1.0    | ns   |

AC CHARACTERISTICS (Note 15) (Output load: C. NC push / pull driver and  $T_{4} = -40^{\circ}$ C to  $\pm 85^{\circ}$ C ) - 50 nF B

15. AC characteristics are guaranteed by design and characterization.

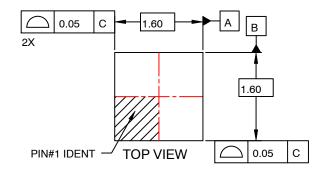

16. Skew is the variation of propagation delay between output signals and applies only to output signals on the same port (A<sub>n</sub> or B<sub>n</sub>) and switching with the same polarity (LOW-to-HIGH or HIGH-to-LOW) *(see Figure 15)*. Skew is guaranteed; not production tested.

#### CAPACITANCE (T<sub>A</sub> = +25°C.)

| Symbol           | Parameter                                                 | Condition                                                    | Тур | Unit |

|------------------|-----------------------------------------------------------|--------------------------------------------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance Control Pin (OE)                        | $V_{CCA} = V_{CCB} = GND$                                    | 2.2 | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance, A <sub>n</sub> , B <sub>n</sub> | $V_{CCA} = V_{CCB} = 5.0 \text{ V}, \text{ OE} = \text{GND}$ | 13  | pF   |

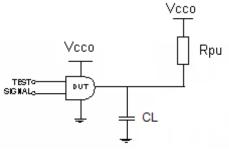

# Figure 8. AC Test Circuit

#### Table 1. PROPAGATION DELAY TABLE (Note 17)

| Test                                                      | Input Signal | Output Enable Control |

|-----------------------------------------------------------|--------------|-----------------------|

| t <sub>PLH</sub> , t <sub>PHL</sub>                       | Data Pulses  | V <sub>CCA</sub>      |

| t <sub>PZL</sub> (OE to A <sub>n</sub> , B <sub>n</sub> ) | 0 V          | LOW to HIGH Switch    |

| t <sub>PLZ</sub> (OE to A <sub>n</sub> , B <sub>n</sub> ) | 0 V          | HIGH to LOW Switch    |

17. For t<sub>PZL</sub> and t<sub>PLZ</sub> testing, an external 2.2 kΩ pull–up resister to V<sub>CCO</sub> is required in order to force the I/O pins high while OE is Low because when OE is low, the internal 10 kΩ RPUs are decoupled from their respective VCC's.

#### Table 2. AC LOAD TABLE

| V <sub>cco</sub> | CL    | RL |

|------------------|-------|----|

| 1.8 ±0.15 V      | 50 pF | NC |

| 2.5 ±0.2 V       | 50 pF | NC |

| 3.3 ±0.3 V       | 50 pF | NC |

| 5.0 ±0.5 V       | 50 pF | NC |

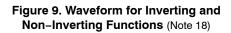

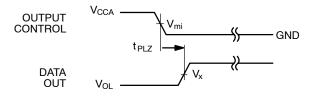

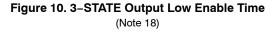

#### **TIMING DIAGRAMS**

#### NOTES:

$\begin{array}{l} \mbox{18. Input } t_R = t_F = 2.0 \ \mbox{ns}, \ \mbox{10\% to } 90\% \ \mbox{at } V_{IN} = 1.65 \ \mbox{V to } 1.95 \ \mbox{V}; \\ \mbox{Input } t_R = t_F = 2.0 \ \mbox{ns}, \ \mbox{10\% to } 90\% \ \mbox{at } V_{IN} = 2.3 \ \mbox{V to } 2.7 \ \mbox{V}; \\ \mbox{Input } t_R = t_F = 2.5 \ \mbox{ns}, \ \mbox{10\% to } 90\%, \ \mbox{at } V_{IN} = 3.0 \ \mbox{V to } 3.6 \ \mbox{V only}; \\ \mbox{Input } t_R = t_F = 2.5 \ \mbox{ns}, \ \mbox{10\% to } 90\%, \ \mbox{at } V_{IN} = 4.5 \ \mbox{V to } 5.5 \ \mbox{V only}. \\ \mbox{19. } V_{CCI} = V_{CCA} \ \mbox{for control pin OE or } V_{mi} = (V_{CCA} \ \ \mbox{2)}. \end{array}$

| Symbol                    | V <sub>CC</sub>        |

|---------------------------|------------------------|

| V <sub>mi</sub> (Note 19) | V <sub>CCI</sub> / 2   |

| V <sub>mo</sub>           | V <sub>CCO</sub> / 2   |

| V <sub>X</sub>            | 0.5 x V <sub>CCO</sub> |

| V <sub>Y</sub>            | 0.1 x V <sub>CCO</sub> |

#### **ORDERING INFORMATION**

| Part Number  | Operating Temperature Range | Top Mark | Package                                            | Packing Method <sup>†</sup> |

|--------------|-----------------------------|----------|----------------------------------------------------|-----------------------------|

| FXMAR2102L8X | −40 to +85°C                | BU       | 8-Lead MicroPak, 1.6 mm Wide<br>(Pb-Free)          | 5000 / Tape & Reel          |

| FXMAR2102UMX |                             |          | 8-Lead Ultrathin MLP, 1.2 mm x 1.4 mm<br>(Pb-Free) |                             |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

MicroPak is trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. **onsemi** is licensed by the Philips Corporation to carry the I<sup>2</sup>C bus protocol.

# **ONSEM**<sup>1</sup>.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98AON58906E             | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UQFN8, 1.40x1.20, 0.40P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

| onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |                         |                                                                                                                                                                                     |             |  |  |

DATE 31 AUG 2016

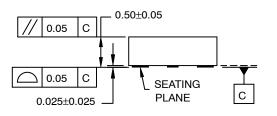

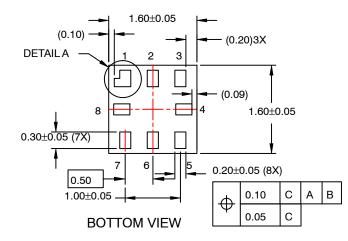

SIDE VIEW

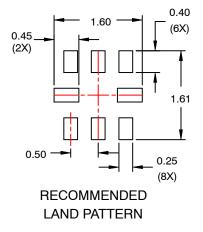

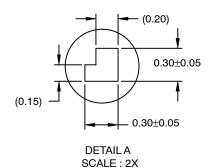

NOTES:

- A. PACKAGE CONFORMS TO JEDEC MO-255 VARIATION UAAD.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009.

- D. LAND PATTERN RECOMMENDATION IS EXISTING INDUSTRY LAND PATTERN.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98AON13591G         | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UQFN8 1.6X1.6, 0.5P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |

| ON Semiconductor and 📖 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                     |                                                                                                                                                                                     |             |  |  |  |

© Semiconductor Components Industries, LLC, 2019

rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales