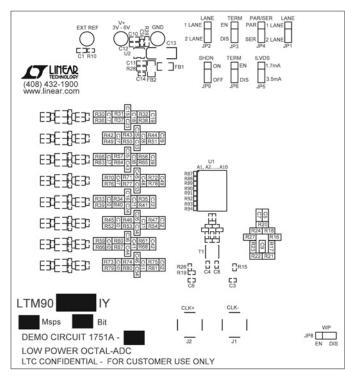

### LTM9008-14/ LTM9007-14/LTM9006-14

14-Bit, 65Msps/40Msps/ 25Msps Low Power Octal ADCs

### FEATURES

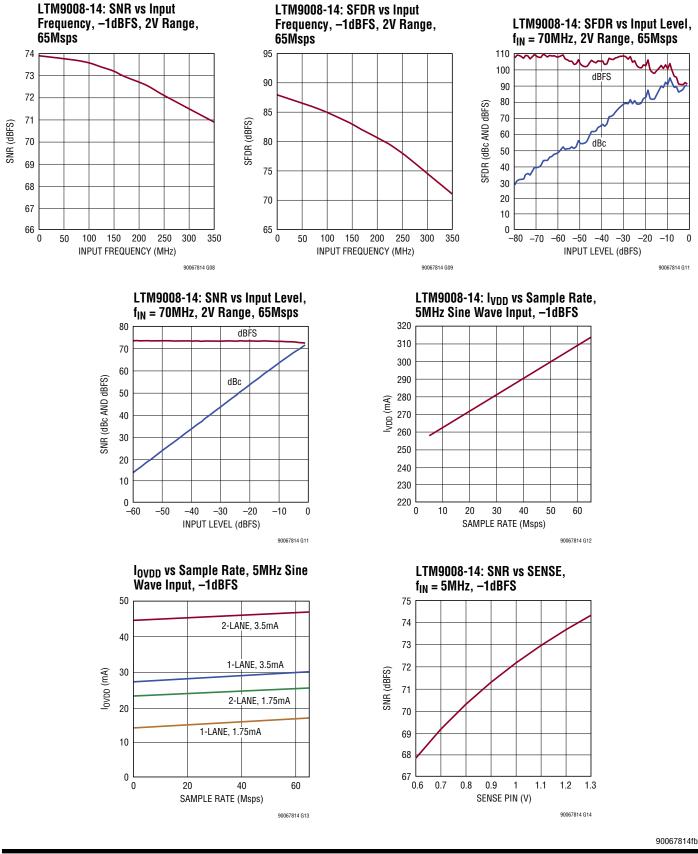

- 8-Channel Simultaneous Sampling ADC

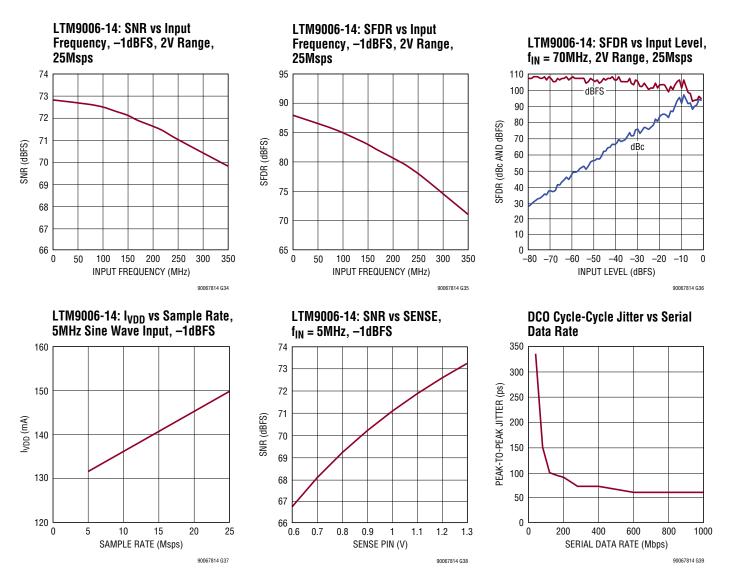

- 73dB SNR

- 90dB SFDR

- Low Power: 88mW/59mW/46mW per Channel

- Single 1.8V Supply

- Serial LVDS Outputs: 1 or 2 Bits per Channel

- Selectable Input Ranges: 1V<sub>P-P</sub> to 2V<sub>P-P</sub>

- 800MHz Full Power Bandwidth S/H

- Shutdown and Nap Modes

- Serial SPI Port for Configuration

- Internal Bypass Capacitance, No External Components

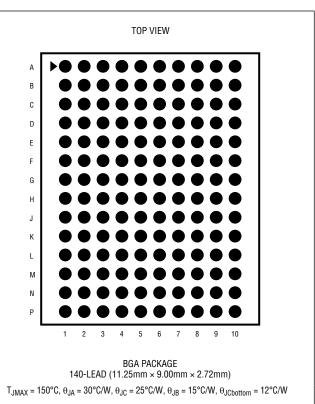

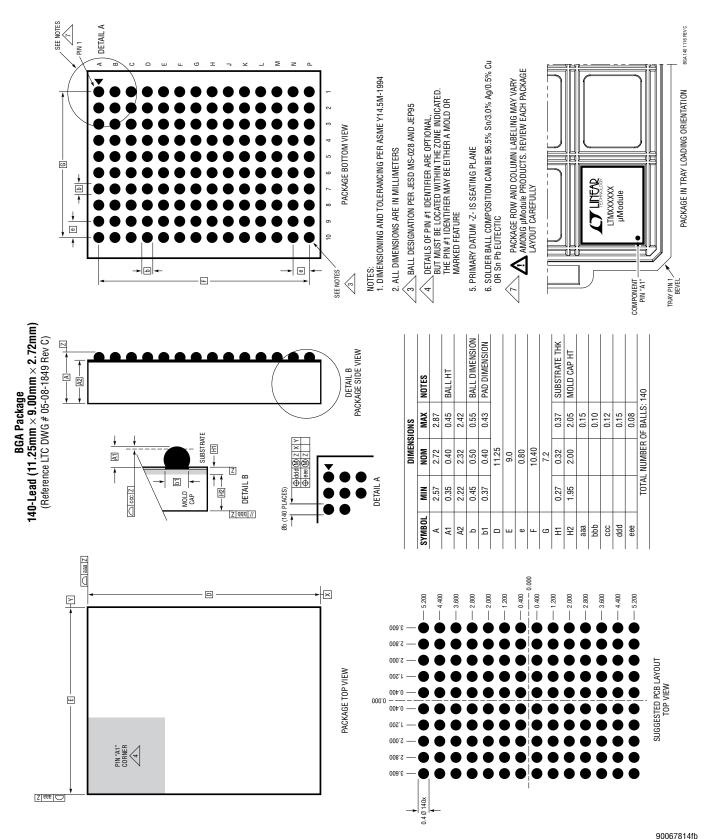

- 140-Pin (11.25mm × 9mm) BGA Package

## **APPLICATIONS**

- Communications

- Cellular Base Stations

- Software Defined Radios

- Portable Medical Imaging

- Multichannel Data Acquisition

- Nondestructive Testing

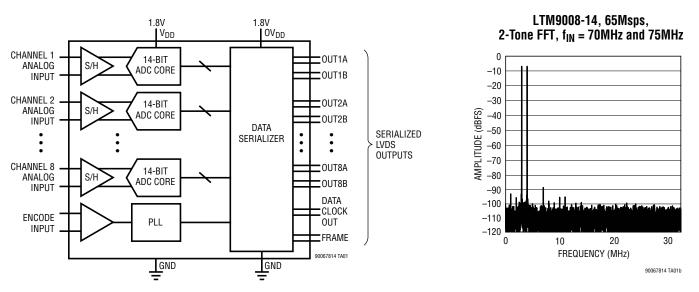

### DESCRIPTION

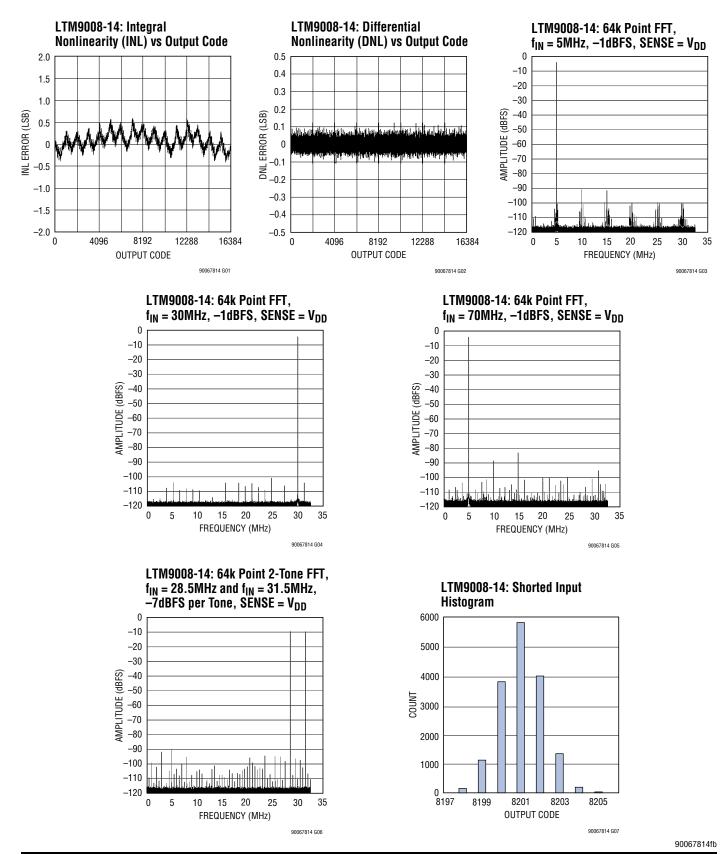

The LTM<sup>®</sup>9008-14/LTM9007-14/LTM9006-14 are 8-channel, simultaneous sampling 14-bit A/D converters designed for digitizing high frequency, wide dynamic range signals. AC performance includes 73dB SNR and 90dB spurious free dynamic range (SFDR). Low power consumption per channel reduces heat in high channel count applications. Integrated bypass capacitance and flowthrough pinout reduces overall board space requirements.

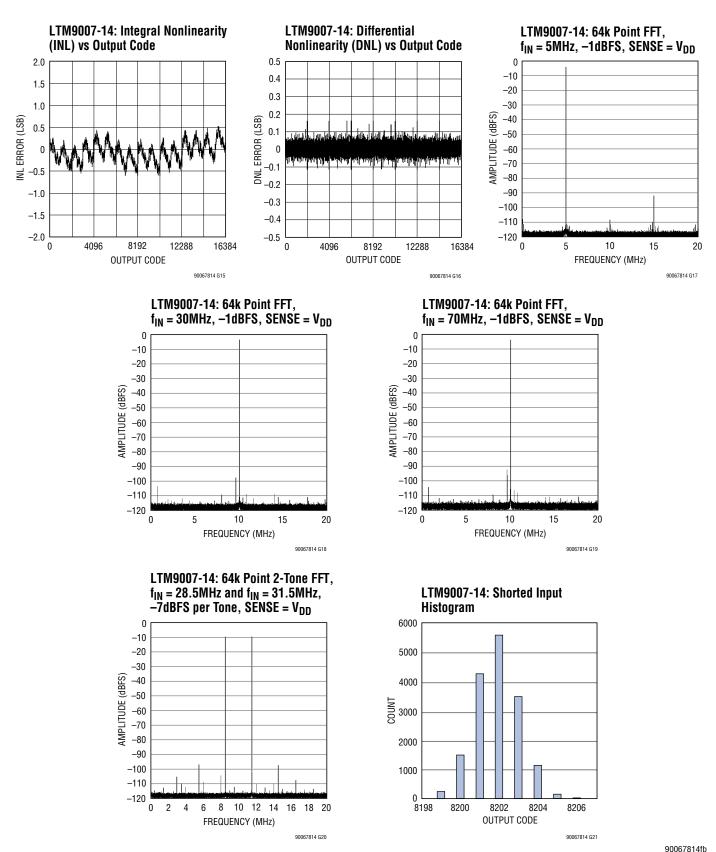

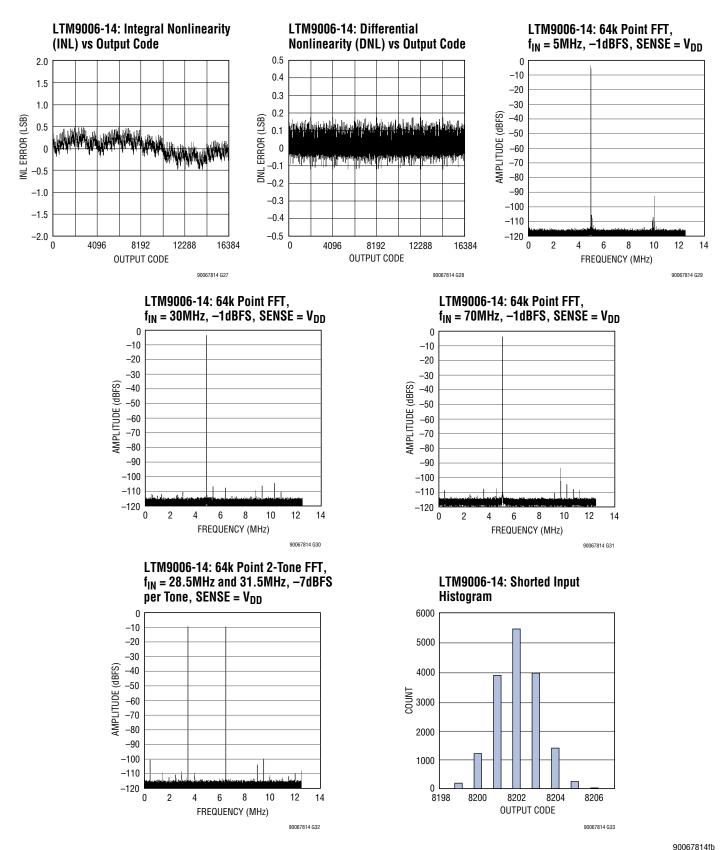

DC specs include  $\pm 1LSB$  INL (typ),  $\pm 0.3LSB$  DNL (typ) and no missing codes over temperature. The transition noise is a low  $1.2LSB_{RMS}$ .

The digital outputs are serial LVDS to minimize the number of data lines. Each channel outputs two bits at a time (2-lane mode). At lower sampling rates there is a one bit per channel option (1-lane mode).

The ENC<sup>+</sup> and ENC<sup>-</sup> inputs may be driven differentially or single-ended with a sine wave, PECL, LVDS, TTL, or CMOS inputs. An internal clock duty cycle stabilizer allows high performance at full speed for a wide range of clock duty cycles.

$\sigma$ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

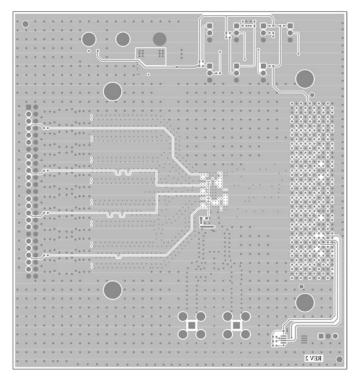

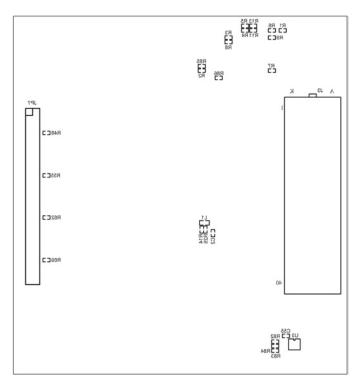

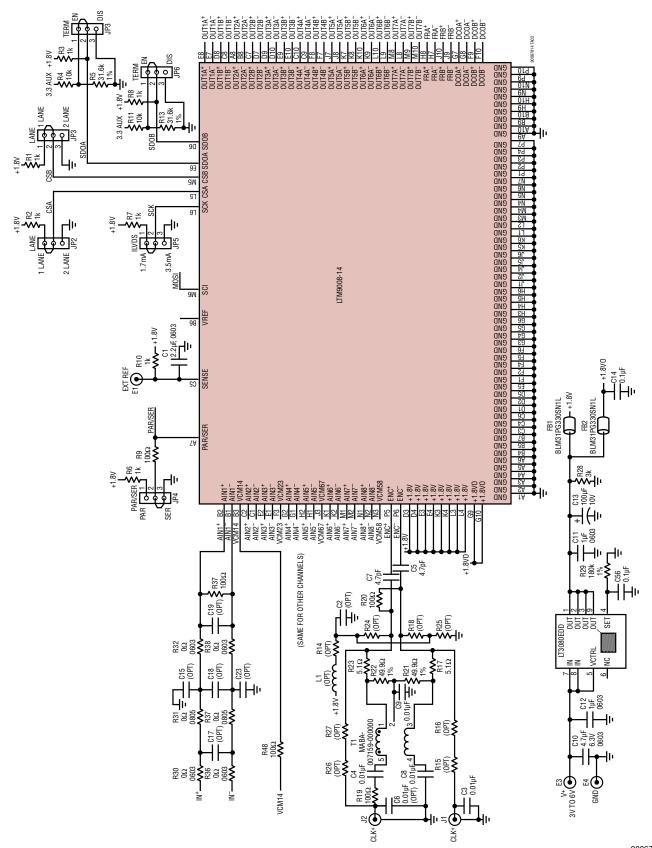

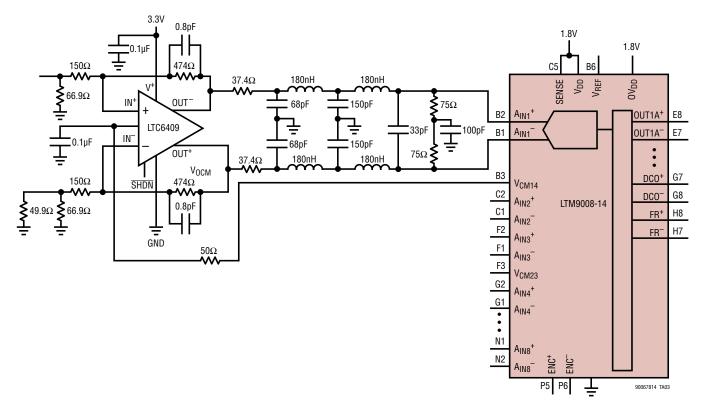

## TYPICAL APPLICATION

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1, 2)

| Supply Voltages                                                                     |

|-------------------------------------------------------------------------------------|

| V <sub>DD</sub> , OV <sub>DD</sub>                                                  |

| Analog Input Voltage (A <sub>IN</sub> <sup>+</sup> , A <sub>IN</sub> <sup>-</sup> , |

| PAR/SER, SENSE) (Note 3) –0.3V to (V <sub>DD</sub> + 0.2V)                          |

| Digital Input Voltage (ENC+, ENC <sup>-</sup> , <del>CS</del> ,                     |

| SDI, SCK) (Note 4)0.3V to 3.9V                                                      |

| SDO (Note 4)0.3V to 3.9V                                                            |

| Digital Output Voltage $-0.3V$ to $(OV_{DD} + 0.3V)$                                |

| Operating Temperature Range                                                         |

| LTM9008C, LTM9007C, LTM9006C 0°C to 70°C                                            |

| LTM9008I, LTM9007I, LTM9006I40°C to 85°C                                            |

| Storage Temperature Range –55°C to 125°C                                            |

#### PIN CONFIGURATION

#### ORDER INFORMATION http://www.linear.com/product/LTM9008-14#orderinfo

| LEAD FREE FINISH | TRAY             | PART MARKING* | PACKAGE DESCRIPTION                   | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------------|-------------------|

| LTM9008CY-14#PBF | LTM9008CY-14#PBF | LTM9008Y14    | 140-Lead (11.25mm × 9mm × 2.72mm) BGA | 0°C to 70°C       |

| LTM9008IY-14#PBF | LTM9008IY-14#PBF | LTM9008Y14    | 140-Lead (11.25mm × 9mm × 2.72mm) BGA | –40°C to 85°C     |

| LTM9007CY-14#PBF | LTM9007CY-14#PBF | LTM9007Y14    | 140-Lead (11.25mm × 9mm × 2.72mm) BGA | 0°C to 70°C       |

| LTM9007IY-14#PBF | LTM9007IY-14#PBF | LTM9007Y14    | 140-Lead (11.25mm × 9mm × 2.72mm) BGA | –40°C to 85°C     |

| LTM9006CY-14#PBF | LTM9006CY-14#PBF | LTM9006Y14    | 140-Lead (11.25mm × 9mm × 2.72mm) BGA | 0°C to 70°C       |

| LTM9006IY-14#PBF | LTM9006IY-14#PBF | LTM9006Y14    | 140-Lead (11.25mm × 9mm × 2.72mm) BGA | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

|                               |                                          |   |      | M9008-       |     | LTM9007-14 |              | LTM9006-14 |       |              | UNITO |                    |

|-------------------------------|------------------------------------------|---|------|--------------|-----|------------|--------------|------------|-------|--------------|-------|--------------------|

| PARAMETER                     | CONDITIONS                               |   | MIN  | TYP          | MAX | MIN        | TYP          | MAX        | MIN   | TYP          | MAX   | UNITS              |

| Resolution (No Missing Codes) |                                          | • | 14   |              |     | 14         |              |            | 14    |              |       | Bits               |

| Integral Linearity Error      | Differential Analog Input (Note 6)       |   | -4.1 | ±1.2         | 4.1 | -2.75      | ±1           | 2.75       | -2.75 | ±1           | 2.75  | LSB                |

| Differential Linearity Error  | Differential Analog Input                | • | -0.9 | ±0.3         | 0.9 | -0.8       | ±0.3         | 0.8        | -0.8  | ±0.3         | 0.8   | LSB                |

| Offset Error                  | (Note 7)                                 | • | -12  | ±3           | 12  | -12        | ±3           | 12         | -12   | ±3           | 12    | mV                 |

| Gain Error                    | Internal Reference<br>External Reference | • | -2.5 | -1.3<br>-1.3 | 0.5 | -2.5       | -1.3<br>-1.3 | 0.5        | -2.6  | -1.3<br>-1.3 | 0.5   | %FS<br>%FS         |

| Offset Drift                  |                                          |   |      | ±20          |     |            | ±20          |            |       | ±20          |       | μV/°C              |

| Full-Scale Drift              | Internal Reference<br>External Reference |   |      | ±35<br>±25   |     |            | ±35<br>±25   |            |       | ±35<br>±25   |       | ppm/°C<br>ppm/°C   |

| Gain Matching                 | External Reference                       |   |      | ±0.2         |     |            | ±0.2         |            |       | ±0.2         |       | %FS                |

| Offset Matching               |                                          |   |      | ±3           |     |            | ±3           |            |       | ±3           |       | mV                 |

| Transition Noise              | External Reference                       |   |      | 1.2          |     |            | 1.2          |            |       | 1.2          |       | LSB <sub>RMS</sub> |

# **ANALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

| SYMBOL              | PARAMETER                                                                         | CONDITIONS                                            |   | MIN                     | ТҮР             | MAX                     | UNITS             |

|---------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------|---|-------------------------|-----------------|-------------------------|-------------------|

| V <sub>IN</sub>     | Analog Input Range (A <sub>IN</sub> <sup>+</sup> – A <sub>IN</sub> <sup>-</sup> ) | 1.7V < V <sub>DD</sub> < 1.9V                         | ٠ |                         | 1 to 2          |                         | V <sub>P-P</sub>  |

| V <sub>IN(CM)</sub> | Analog Input Common Mode $(A_{IN}^{+} + A_{IN}^{-})/2$                            | Differential Analog Input (Note 8)                    | ٠ | V <sub>CM</sub> – 100mV | V <sub>CM</sub> | V <sub>CM</sub> + 100mV | V                 |

| V <sub>SENSE</sub>  | External Voltage Reference Applied to SENSE                                       | External Reference Mode                               | ٠ | 0.625                   | 1.250           | 1.300                   | V                 |

| IINCM               | Analog Input Common Mode Current                                                  | Per Pin, 65Msps<br>Per Pin, 40Msps<br>Per Pin, 25Msps |   |                         | 81<br>50<br>31  |                         | μΑ<br>μΑ<br>μΑ    |

| I <sub>IN1</sub>    | Analog Input Leakage Current                                                      | $0 < A_{IN}^+$ , $A_{IN}^- < V_{DD}$ , No Encode      | ٠ | -1                      |                 | 1                       | μA                |

| I <sub>IN2</sub>    | PAR/SER Input Leakage Current                                                     | 0 < PAR/ <del>SER</del> < V <sub>DD</sub>             | ٠ | -3                      |                 | 3                       | μA                |

| I <sub>IN3</sub>    | SENSE Input Leakage Current                                                       | 0.625 < SENSE < 1.3V                                  | ٠ | -6                      |                 | 6                       | μA                |

| t <sub>AP</sub>     | Sample-and-Hold Acquisition Delay Time                                            |                                                       |   |                         | 0               |                         | ns                |

| t <sub>JITTER</sub> | Sample-and-Hold Acquisition Delay Jitter                                          |                                                       |   |                         | 0.15            |                         | ps <sub>RMS</sub> |

| CMRR                | Analog Input Common Mode Rejection Ratio                                          |                                                       |   |                         | 80              |                         | dB                |

| BW-3B               | Full-Power Bandwidth                                                              | Figure 6 Test Circuit                                 |   |                         | 800             |                         | MHz               |

# **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. A<sub>IN</sub> = -1dBFS. (Note 5)

|         |                                                       |                                                          |   |      | M9008-                       |     |      | M9007-                       |     | LTM9006-14 |                              |     |                              |

|---------|-------------------------------------------------------|----------------------------------------------------------|---|------|------------------------------|-----|------|------------------------------|-----|------------|------------------------------|-----|------------------------------|

| SYMBOL  | PARAMETER                                             | CONDITIONS                                               |   | MIN  | TYP                          | MAX | MIN  | TYP                          | MAX | MIN        | TYP                          | MAX | UNITS                        |

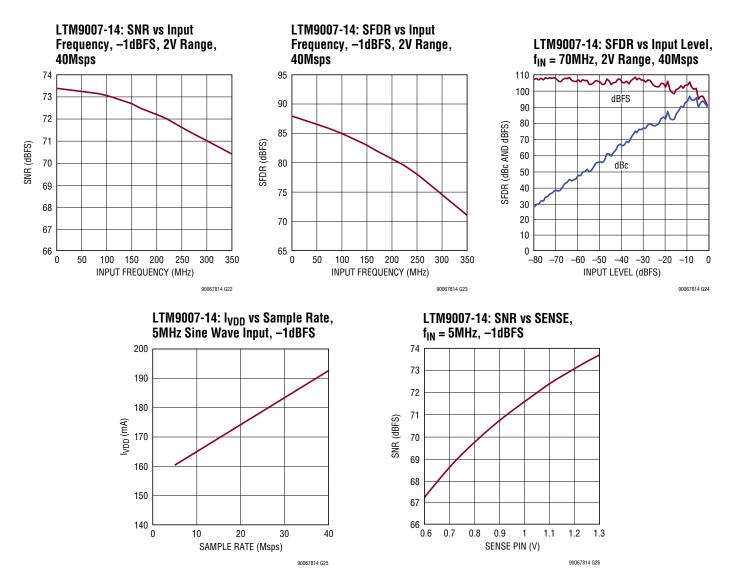

| SNR     | Signal-to-Noise Ratio                                 | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | • | 71.8 | 73.7<br>73.7<br>73.5<br>73   |     | 69.6 | 73.5<br>73.4<br>73.4<br>72.8 |     | 69.6       | 72.9<br>72.9<br>72.8<br>72.3 |     | dBFS<br>dBFS<br>dBFS<br>dBFS |

| SFDR    | Spurious Free Dynamic Range<br>2nd or 3rd Harmonic    | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | • | 74   | 90<br>90<br>89<br>84         |     | 76.8 | 90<br>90<br>89<br>84         |     | 76.8       | 90<br>90<br>89<br>84         |     | dBFS<br>dBFS<br>dBFS<br>dBFS |

|         | Spurious Free Dynamic Range<br>4th Harmonic or Higher | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | • | 84   | 90<br>90<br>90<br>90         |     | 84   | 90<br>90<br>90<br>90         |     | 84         | 90<br>90<br>90<br>90         |     | dBFS<br>dBFS<br>dBFS<br>dBFS |

| S/(N+D) | Signal-to-Noise Plus<br>Distortion Ratio              | 5MHz Input<br>30MHz Input<br>70MHz Input<br>140MHz Input | • | 71   | 73.6<br>73.5<br>73.2<br>72.5 |     | 69.5 | 73.3<br>73.2<br>73.1<br>72.3 |     | 69.5       | 72.8<br>72.7<br>72.5<br>71.9 |     | dBFS<br>dBFS<br>dBFS<br>dBFS |

|         | Crosstalk, Near Channel                               | 10MHz Input (Note 12)                                    |   |      | -90                          |     |      | -90                          |     |            | -90                          |     | dBc                          |

|         | Crosstalk, Far Channel                                | 10MHz Input (Note 12)                                    |   |      | -105                         |     |      | -105                         |     |            | -105                         |     | dBc                          |

# **INTERNAL REFERENCE CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. A<sub>IN</sub> = -1dBFS. (Note 5)

| PARAMETER                                 | CONDITIONS                      | MIN                          | ТҮР                   | MAX                          | UNITS  |

|-------------------------------------------|---------------------------------|------------------------------|-----------------------|------------------------------|--------|

| V <sub>CM</sub> Output Voltage            | I <sub>OUT</sub> = 0            | 0.5 • V <sub>DD</sub> – 25mV | 0.5 • V <sub>DD</sub> | 0.5 • V <sub>DD</sub> + 25mV | V      |

| V <sub>CM</sub> Output Temperature Drift  |                                 |                              | ±25                   |                              | ppm/°C |

| V <sub>CM</sub> Output Resistance         | –600μA < I <sub>OUT</sub> < 1mA |                              | 4                     |                              | Ω      |

| V <sub>REF</sub> Output Voltage           | I <sub>OUT</sub> = 0            | 1.225                        | 1.250                 | 1.275                        | V      |

| V <sub>REF</sub> Output Temperature Drift |                                 |                              | ±25                   |                              | ppm/°C |

| V <sub>REF</sub> Output Resistance        | -400μA < I <sub>OUT</sub> < 1mA |                              | 7                     |                              | Ω      |

| V <sub>REF</sub> Line Regulation          | 1.7V < V <sub>DD</sub> < 1.9V   |                              | 0.6                   |                              | mV/V   |

# **DIGITAL INPUTS AND OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

| SYMBOL            | PARAMETER                                                | CONDITIONS                                                                           |          | MIN            | ТҮР            | MAX            | UNITS    |

|-------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|----------|----------------|----------------|----------------|----------|

| ENCODE            | INPUTS (ENC+, ENC <sup>-</sup> )                         |                                                                                      | I        |                |                |                |          |

|                   | ial Encode Mode (ENC <sup>-</sup> Not Tied to GND)       |                                                                                      |          |                |                |                |          |

| V <sub>ID</sub>   | Differential Input Voltage                               | (Note 8)                                                                             |          | 0.2            |                |                | V        |

| V <sub>ICM</sub>  | Common Mode Input Voltage                                | Internally Set<br>Externally Set (Note 8)                                            | •        | 1.1            | 1.2            | 1.6            | V<br>V   |

| V <sub>IN</sub>   | Input Voltage Range                                      | ENC <sup>+</sup> , ENC <sup>-</sup> to GND                                           |          | 0.2            |                | 3.6            | V        |

| R <sub>IN</sub>   | Input Resistance                                         | (See Figure 10)                                                                      |          |                | 10             |                | kΩ       |

| CIN               | Input Capacitance                                        |                                                                                      |          |                | 3.5            |                | pF       |

| Single-E          | nded Encode Mode (ENC <sup>-</sup> Tied to GND)          |                                                                                      |          |                |                |                |          |

| V <sub>IH</sub>   | High Level Input Voltage                                 | V <sub>DD</sub> = 1.8V                                                               |          |                | 1.26           |                | V        |

| VIL               | Low Level Input Voltage                                  | V <sub>DD</sub> = 1.8V                                                               |          |                | 0.54           |                | V        |

| V <sub>IN</sub>   | Input Voltage Range                                      | ENC <sup>+</sup> to GND                                                              |          |                | 0 to 3.6       |                | V        |

| R <sub>IN</sub>   | Input Resistance                                         | (See Figure 11)                                                                      |          |                | 30             |                | kΩ       |

| CIN               | Input Capacitance                                        |                                                                                      |          |                | 3.5            |                | pF       |

| DIGITAL           | INPUTS ( $\overline{CS}$ , SDI, SCK in Serial or Paralle | l Programming Mode. SDO in Parallel Progra                                           | amming   | ı Mode)        |                |                |          |

| V <sub>IH</sub>   | High Level Input Voltage                                 | V <sub>DD</sub> = 1.8V                                                               |          | 1.3            |                |                | V        |

| V <sub>IL</sub>   | Low Level Input Voltage                                  | V <sub>DD</sub> = 1.8V                                                               |          |                |                | 0.6            | V        |

| I <sub>IN</sub>   | Input Current                                            | V <sub>IN</sub> = 0V to 3.6V                                                         |          | -10            |                | 10             | μA       |

| CIN               | Input Capacitance                                        |                                                                                      |          |                | 3              |                | pF       |

| SDO OUT           | PUT (Serial Programming Mode. Open-D                     | rain Output. Requires 2k ${f \Omega}$ Pull-Up Resistor i                             | f SDO Is | : Used)        |                |                |          |

| R <sub>OL</sub>   | Logic Low Output Resistance to GND                       | V <sub>DD</sub> = 1.8V, SDO = 0V                                                     |          |                | 200            |                | Ω        |

| I <sub>OH</sub>   | Logic High Output Leakage Current                        | SDO = 0V to 3.6V                                                                     |          | -10            |                | 10             | μA       |

| C <sub>OUT</sub>  | Output Capacitance                                       |                                                                                      |          |                | 3              |                | pF       |

| DIGITAL           | DATA OUTPUTS                                             |                                                                                      |          |                |                |                |          |

| V <sub>OD</sub>   | Differential Output Voltage                              | $100\Omega$ Differential Load, 3.5mA Mode $100\Omega$ Differential Load, 1.75mA Mode | •        | 247<br>125     | 350<br>175     | 454<br>250     | mV<br>mV |

| V <sub>OS</sub>   | Common Mode Output Voltage                               | $100\Omega$ Differential Load, 3.5mA Mode $100\Omega$ Differential Load, 1.75mA Mode | •        | 1.125<br>1.125 | 1.250<br>1.250 | 1.375<br>1.375 | V<br>V   |

| R <sub>TERM</sub> | On-Chip Termination Resistance                           | Termination Enabled, OV <sub>DD</sub> = 1.8V                                         |          |                | 100            |                | Ω        |

# **POWER REQUIREMENTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 9)

|                    |                                                                                      |                                                                                                            |   | LT  | M9008-                   | 14         | L1  | M9007-                   | 14         | LTM9006-14 |                          |            |                      |

|--------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---|-----|--------------------------|------------|-----|--------------------------|------------|------------|--------------------------|------------|----------------------|

| SYMBOL             | PARAMETER                                                                            | CONDITIONS                                                                                                 |   | MIN | TYP                      | MAX        | MIN | TYP                      | MAX        | MIN        | TYP                      | MAX        | UNITS                |

| V <sub>DD</sub>    | Analog Supply Voltage                                                                | (Note 10)                                                                                                  |   | 1.7 | 1.8                      | 1.9        | 1.7 | 1.8                      | 1.9        | 1.7        | 1.8                      | 1.9        | V                    |

| OV <sub>DD</sub>   | Output Supply Voltage                                                                | (Note 10)                                                                                                  | • | 1.7 | 1.8                      | 1.9        | 1.7 | 1.8                      | 1.9        | 1.7        | 1.8                      | 1.9        | V                    |

| I <sub>VDD</sub>   | Analog Supply Current                                                                | Sine Wave Input                                                                                            | • |     | 357                      | 400        |     | 232                      | 275        |            | 175                      | 250        | mA                   |

| I <sub>OVDD</sub>  | Digital Supply Current                                                               | 1-Lane Mode, 1.75mA Mode<br>1-Lane Mode, 3.5mA Mode<br>2-Lane Mode, 1.75mA Mode<br>2-Lane Mode, 3.5mA Mode | • |     | 32<br>60<br>50<br>94     | 58<br>104  |     | 32<br>58<br>48<br>92     | 54<br>102  |            | 30<br>56<br>48<br>90     | 54<br>100  | mA<br>mA<br>mA<br>mA |

| P <sub>DISS</sub>  | Power Dissipation                                                                    | 1-Lane Mode, 1.75mA Mode<br>1-Lane Mode, 3.5mA Mode<br>2-Lane Mode, 1.75mA Mode<br>2-Lane Mode, 3.5mA Mode | • |     | 700<br>751<br>733<br>812 | 824<br>907 |     | 475<br>522<br>504<br>583 | 592<br>679 |            | 369<br>416<br>401<br>477 | 547<br>630 | mW<br>mW<br>mW<br>mW |

| P <sub>SLEEP</sub> | Sleep Mode Power                                                                     |                                                                                                            |   |     | 2                        |            |     | 2                        |            |            | 2                        |            | mW                   |

| P <sub>NAP</sub>   | Nap Mode Power                                                                       |                                                                                                            |   |     | 170                      |            |     | 170                      |            |            | 170                      |            | mW                   |

| PDIFFCLK           | Power Decrease With Single-Ended Encode Mode Enabled<br>(No Decrease for Sleep Mode) |                                                                                                            |   |     | 40                       |            |     | 40                       |            |            | 40                       |            | mW                   |

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

LTM9008-14 LTM9007-14 LTM9006-14

| SYMBOL            | PARAMETER                                 | CONDITIONS                                            |   | MIN      | ТҮР          | MAX        | MIN        | TYP          | MAX        | MIN     | TYP      | MAX        | UNITS    |

|-------------------|-------------------------------------------|-------------------------------------------------------|---|----------|--------------|------------|------------|--------------|------------|---------|----------|------------|----------|

| f <sub>S</sub>    | Sampling Frequency                        | (Notes 10,11)                                         |   | 5        |              | 65         | 5          |              | 40         | 5       |          | 25         | MHz      |

| t <sub>ENCL</sub> | ENC Low Time (Note 8)                     | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On | • | 7.3<br>2 | 7.69<br>7.69 | 100<br>100 | 11.88<br>2 | 12.5<br>12.5 | 100<br>100 | 19<br>2 | 20<br>20 | 100<br>100 | ns<br>ns |

| t <sub>ENCH</sub> | ENC High Time (Note 8)                    | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On | • | 7.3<br>2 | 7.69<br>7.69 | 100<br>100 | 11.88<br>2 | 12.5<br>12.5 | 100<br>100 | 19<br>2 | 20<br>20 | 100<br>100 | ns<br>ns |

| t <sub>AP</sub>   | Sample-and-Hold<br>Acquisition Delay Time |                                                       |   |          | 0            |            |            | 0            |            |         | 0        |            | ns       |

| SYMBOL             | PARAMETER                                         | CONDITIONS                                                                                                                                                                                      |   | MIN                         | ТҮР                                                                                                                                                              | MAX                         | UNITS                                  |

|--------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------|

| Digital Da         | ita Outputs (R <sub>TERM</sub> = 100 $\Omega$ Dif | ferential, $C_L = 2pF$ to GND on Each Output)                                                                                                                                                   |   |                             |                                                                                                                                                                  |                             |                                        |

| t <sub>SER</sub>   | Serial Data Bit Period                            | 2-Lanes, 16-Bit Serialization<br>2-Lanes, 14-Bit Serialization<br>2-Lanes, 12-Bit Serialization<br>1-Lane, 16-Bit Serialization<br>1-Lane, 14-Bit Serialization<br>1-Lane, 12-Bit Serialization |   |                             | $\frac{1/(8 \cdot f_S)}{1/(7 \cdot f_S)}$<br>$\frac{1}{(6 \cdot f_S)}$<br>$\frac{1}{(16 \cdot f_S)}$<br>$\frac{1}{(14 \cdot f_S)}$<br>$\frac{1}{(12 \cdot f_S)}$ |                             | \$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$ |

| t <sub>FRAME</sub> | FR to DCO Delay                                   | (Note 8)                                                                                                                                                                                        | • | 0.35 • t <sub>SER</sub>     | 0.5 • t <sub>SER</sub>                                                                                                                                           | 0.65 • t <sub>SER</sub>     | S                                      |

| t <sub>DATA</sub>  | DATA to DCO Delay                                 | (Note 8)                                                                                                                                                                                        | • | 0.35 • t <sub>SER</sub>     | 0.5 • t <sub>SER</sub>                                                                                                                                           | 0.65 • t <sub>SER</sub>     | S                                      |

| t <sub>PD</sub>    | Propagation Delay                                 | (Note 8)                                                                                                                                                                                        | • | 0.7n + 2 • t <sub>SER</sub> | 1.1n + 2 • t <sub>SER</sub>                                                                                                                                      | 1.5n + 2 • t <sub>SER</sub> | S                                      |

| t <sub>R</sub>     | Output Rise Time                                  | Data, DCO, FR, 20% to 80%                                                                                                                                                                       |   |                             | 0.17                                                                                                                                                             |                             | ns                                     |

| t <sub>F</sub>     | Output Fall Time                                  | Data, DCO, FR, 20% to 80%                                                                                                                                                                       |   |                             | 0.17                                                                                                                                                             |                             | ns                                     |

|                    | DCO Cycle-Cycle Jitter                            | t <sub>SER</sub> = 1ns                                                                                                                                                                          |   |                             | 60                                                                                                                                                               |                             | ps <sub>P-P</sub>                      |

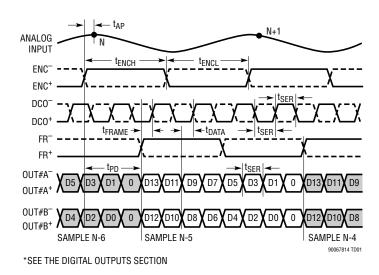

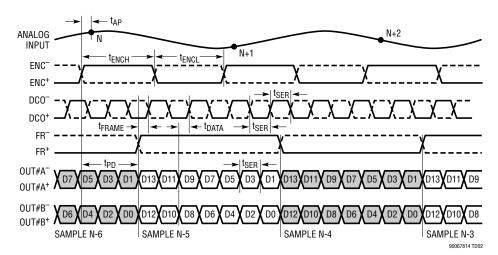

|                    | Pipeline Latency                                  |                                                                                                                                                                                                 |   |                             | 6                                                                                                                                                                |                             | Cycles                                 |

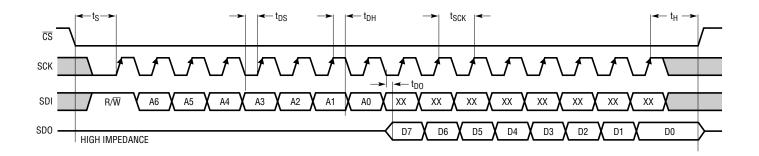

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

| SYMBOL           | PARAMETER                | CONDITIONS                                                                         |   | MIN       | ТҮР | MAX | UNITS |

|------------------|--------------------------|------------------------------------------------------------------------------------|---|-----------|-----|-----|-------|

| SPI Port T       | Timing (Note 8)          |                                                                                    |   |           |     |     |       |

| t <sub>SCK</sub> | SCK Period               | Write Mode<br>Read Back Mode, C <sub>SDO</sub> = 20pF,<br>R <sub>PULLUP</sub> = 2k | • | 40<br>250 |     |     | ns    |

| t <sub>S</sub>   | CS to SCK Setup Time     |                                                                                    | • | 5         |     |     | ns    |

| t <sub>H</sub>   | SCK to CS Setup Time     |                                                                                    | • | 5         |     |     | ns    |

| t <sub>DS</sub>  | SDI Setup Time           |                                                                                    | • | 5         |     |     | ns    |

| t <sub>DH</sub>  | SDI Hold Time            |                                                                                    |   | 5         |     |     | ns    |

| t <sub>DO</sub>  | SCK Falling to SDO Valid | Read Back Mode, C <sub>SDO</sub> = 20pF,<br>R <sub>PULLUP</sub> = 2k               | • |           |     | 125 | ns    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All voltage values are with respect to GND (unless otherwise noted).

**Note 3:** When these pin voltages are taken below GND or above  $V_{DD}$ , they will be clamped by internal diodes. This product can handle input currents of greater than 100mA below GND or above  $V_{DD}$  without latchup.

**Note 4:** When these pin voltages are taken below GND they will be clamped by internal diodes. When these pin voltages are taken above  $V_{DD}$  they will not be clamped by internal diodes. This product can handle input currents of greater than 100mA below GND without latchup.

**Note 5:**  $V_{DD} = 0V_{DD} = 1.8V$ ,  $f_{SAMPLE} = 65MHz$  (LTM9008), 40MHz (LTM9007), or 25MHz (LTM9006), 2-lane output mode, differential ENC<sup>+</sup>/ ENC<sup>-</sup> =  $2V_{P-P}$  sine wave, input range =  $2V_{P-P}$  with differential drive, unless otherwise noted.

**Note 6:** Integral nonlinearity is defined as the deviation of a code from a best fit straight line to the transfer curve. The deviation is measured from the center of the quantization band.

**Note 7:** Offset error is the offset voltage measured from -0.5 LSB when the output code flickers between 00 0000 0000 0000 and 11 1111 1111 1111 in 2's complement output mode.

Note 8: Guaranteed by design, not subject to test.

**Note 9:**  $V_{DD} = 0V_{DD} = 1.8V$ ,  $f_{SAMPLE} = 65MHz$  (LTM9008), 40MHz (LTM9007), or 25MHz (LTM9006), 2-lane output mode, differential ENC<sup>+</sup>/ENC<sup>-</sup> =  $2V_{P-P}$  sine wave, input range =  $2V_{P-P}$  with differential drive, unless otherwise noted. The supply current and power dissipation specifications are totals for the entire device, not per channel.

Note 10: Recommended operating conditions.

**Note 11:** The maximum sampling frequency depends on the speed grade of the part and also which serialization mode is used. The maximum serial data rate is 1000Mbps so  $t_{SER}$  must be greater than or equal to 1ns.

**Note 12:** Near-channel crosstalk refers to Ch. 1 to Ch.2, and Ch.7 to Ch.8. Far-channel crosstalk refers to Ch.1 to Ch.7, Ch.1 to Ch.8, Ch.2 to Ch.7, and Ch.2 to Ch.8.

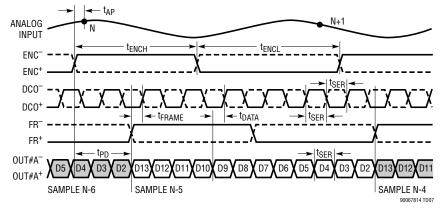

### TIMING DIAGRAMS

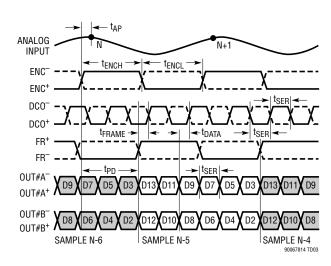

2-Lane Output Mode, 16-Bit Serialization\*

2-Lane Output Mode, 14-Bit Serialization

NOTE THAT IN THIS MODE FR<sup>+</sup>/FR<sup>-</sup> HAS TWO TIMES THE PERIOD OF ENC<sup>+</sup>/ENC<sup>-</sup>

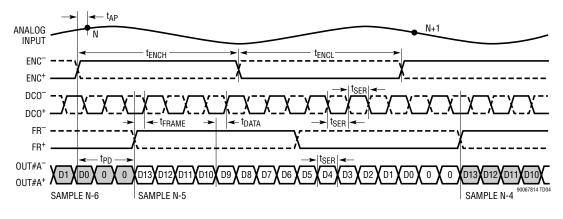

#### TIMING DIAGRAMS

2-Lane Output Mode, 12-Bit Serialization

1-Lane Output Mode, 16-Bit Serialization

OUT#B<sup>+</sup>, OUT#B<sup>-</sup> ARE DISABLED

LINEAR TECHNOLOGY

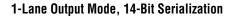

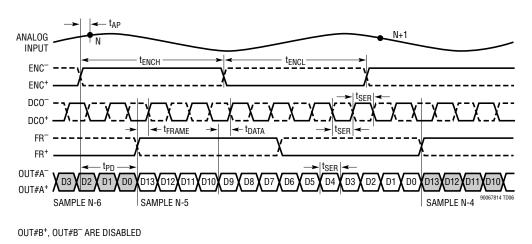

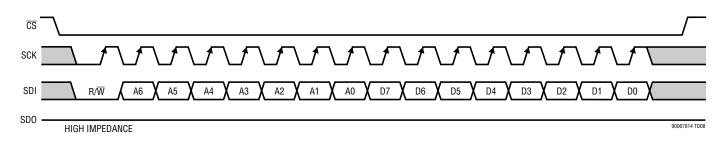

### TIMING DIAGRAMS

1-Lane Output Mode, 12-Bit Serialization

OUT#B<sup>+</sup>, OUT#B<sup>-</sup> ARE DISABLED

SPI Port Timing (Readback Mode)

SPI Port Timing (Write Mode)

15

### PIN FUNCTIONS

A<sub>IN1</sub><sup>+</sup> (B2): Channel 1 Positive Differential Analog Input.

A<sub>IN1</sub><sup>-</sup> (B1): Channel 1 Negative Differential Analog Input.

$V_{CM14}$  (B3): Common Mode Bias Output, Nominally Equal to  $V_{DD}/2$ .  $V_{CM}$  should be used to bias the common mode of the analog inputs of channels 1 and 4.  $V_{CM}$  is internally bypassed to ground with a 0.1µF ceramic capacitor. No external capacitance is required.

AIN2<sup>+</sup> (C2): Channel 2 Positive Differential Analog Input.

AIN2<sup>-</sup> (C1): Channel 2 Negative Differential Analog Input.

AIN3<sup>+</sup> (E2): Channel 3 Positive Differential Analog Input.

AIN3<sup>-</sup> (E1): Channel 3 Negative Differential Analog Input.

$V_{CM23}$  (F3): Common Mode Bias Output, Nominally Equal to  $V_{DD}/2$ .  $V_{CM}$  should be used to bias the common mode of the analog inputs of channels 2 and 3.  $V_{CM}$  is internally bypassed to ground with a 0.1µF ceramic capacitor. No external capacitance is required.

AIN4<sup>+</sup> (G2): Channel 4 Positive Differential Analog Input.

AIN4<sup>-</sup> (G1): Channel 4 Negative Differential Analog Input.

AIN5<sup>+</sup> (H1): Channel 5 Positive Differential Analog Input.

A<sub>IN5</sub><sup>-</sup> (H2): Channel 5 Negative Differential Analog Input.

$V_{CM67}$  (J3): Common Mode Bias Output, Nominally Equal to  $V_{DD}/2$ .  $V_{CM}$  should be used to bias the common mode of the analog inputs of channels 6 and 7.  $V_{CM}$  is internally bypassed to ground with a 0.1µF ceramic capacitor. No external capacitance is required.

**A<sub>IN6</sub><sup>+</sup> (K1):** Channel 6 Positive Differential Analog Input.

AIN6<sup>-</sup> (K2): Channel 6 Negative Differential Analog Input.

AIN7<sup>+</sup> (M1): Channel 7 Positive Differential Analog Input.

AIN7<sup>-</sup> (M2): Channel 7 Negative Differential Analog Input.

$V_{CM58}$  (N3): Common Mode Bias Output, Nominally Equal to  $V_{DD}/2$ .  $V_{CM}$  should be used to bias the common mode of the analog inputs of channels 5 and 8.  $V_{CM}$  is internally bypassed to ground with a 0.1µF ceramic capacitor. No external capacitance is required.

A<sub>IN8</sub><sup>+</sup> (N1): Channel 8 Positive Differential Analog Input.

**A<sub>IN8</sub><sup>-</sup> (N2):** Channel 8 Negative Differential Analog Input

$V_{DD}$  (D3, D4, E3, E4, K3, K4, L3, L4): 1.8V Analog Power Supply.  $V_{DD}$  is internally bypassed to ground with 0.1 $\mu F$  ceramic capacitors.

**ENC+ (P5):** Encode Input. Conversion starts on the rising edge.

**ENC<sup>-</sup> (P6):** Encode Complement Input. Conversion starts on the falling edge.

**CSA (L5):** In serial programming mode, (PAR/SER = 0V), CSA is the serial interface chip select input for registers controlling channels 1, 4, 5 and 8. When  $\overline{CS}$  is low, SCK is enabled for shifting data on SDI into the mode control registers. In parallel programming mode (PAR/SER = V<sub>DD</sub>), CS selects 2-lane or 1-lane output mode.  $\overline{CS}$  can be driven with 1.8V to 3.3V logic.

**CSB** (M5): In serial programming mode, (PAR/SER = 0V), CSB is the serial interface chip select input for registers controlling channels 2, 3, 6 and 7. When  $\overline{CS}$  is low, SCK is enabled for shifting data on SDI into the mode control registers. In parallel programming mode (PAR/SER = V<sub>DD</sub>),  $\overline{CS}$  selects 2-lane or 1-lane output mode.  $\overline{CS}$  can be driven with 1.8V to 3.3V logic.

**SCK (L6):** In serial programming mode, (PAR/SER = 0V), SCK is the serial interface clock input. In parallel programming mode (PAR/SER =  $V_{DD}$ ), SCK selects 3.5mA or 1.75mA LVDS output currents. SCK can be driven with 1.8V to 3.3V logic.

**SDI (M6):** In serial programming mode, (PAR/ $\overline{SER} = 0V$ ), SDI is the serial interface data Input. Data on SDI is clocked into the mode control registers on the rising edge of SCK. In parallel programming mode (PAR/ $\overline{SER} = V_{DD}$ ), SDI can be used to power down the part. SDI can be driven with 1.8V to 3.3V logic.

**GND (See Pin Configuration Table):** ADC Power Ground. Use multiple vias close to pins.

### **PIN FUNCTIONS**

**OV<sub>DD</sub> (G9, G10):** Output Driver Supply. OV<sub>DD</sub> is internally bypassed to ground with a 0.1µF ceramic capacitor.

**SDOA (E6):** In serial programming mode, (PAR/ $\overline{SER} = 0V$ ), SDOA is the optional serial interface data output for registers controlling channels 1, 4, 5 and 8. Data on SDO is read back from the mode control registers and can be latched on the falling edge of SCK. SDO is an open-drain N-channel MOSFET output that requires an external 2k pull-up resistor from 1.8V to 3.3V. If read back from the mode control registers is not needed, the pull-up resistor is not necessary and SDO can be left unconnected. In parallel programming mode (PAR/SER =  $V_{DD}$ ), SDOA is an input that enables internal  $100\Omega$  termination resistors on the digital outputs of channels 1, 4, 5 and 8. When used as an input, SDO can be driven with 1.8V to 3.3V logic through a 1k series resistor.

**SDOB (D6):** Serial Data Output Pin for Channels 2, 3, 6 and 7. See description for SDOA.

PAR/SER (A7): Programming Mode Selection Pin. Connect to ground to enable the serial programming mode.  $\overline{CSA}$ . CSB, SCK, SDI, SDOA and SDOB become a serial interface that control the A/D operating modes. Connect to V<sub>DD</sub> to enable parallel programming mode where CSA, CSB, SCK, SDI, SDOA and SDOB become parallel logic inputs that control a reduced set of the A/D operating modes. PAR/ SER should be connected directly to ground or the V<sub>DD</sub> of the part and not be driven by a logic signal.

**V**<sub>REF</sub> (**B6**): Reference Voltage Output. V<sub>REF</sub> is internally bypassed to ground with a 1µF ceramic capacitor, nominally 1.25V.

**SENSE (C5):** Reference Programming Pin. Connecting SENSE to  $V_{DD}$  selects the internal reference and a  $\pm 1V$ input range. Connecting SENSE to ground selects the internal reference and a  $\pm 0.5V$  input range. An external reference between 0.625V and 1.3V applied to SENSE selects an input range of ±0.8 • V<sub>SENSE</sub>. SENSE is internally bypassed to ground with a 0.1µF ceramic capacitor.

#### LVDS Outputs

All pins in this section are differential LVDS outputs. The output current level is programmable. There is an optional internal 100 $\Omega$  termination resistor between the pins of each LVDS output pair.

OUT1A<sup>-</sup>/OUT1A<sup>+</sup>, OUT1B<sup>-</sup>/OUT1B<sup>+</sup> (E7/E8, C8/D8): Serial Data Outputs for Channel 1. In 1-lane output mode only OUT1A<sup>-</sup>/OUT1A<sup>+</sup> are used.

OUT2A<sup>-</sup>/OUT2A<sup>+</sup>, OUT2B<sup>-</sup>/OUT2B<sup>+</sup> (B8/A8, D7/C7): Serial Data Outputs for Channel 2. In 1-lane output mode only OUT2A<sup>-</sup>/OUT2A<sup>+</sup> are used.

OUT3A<sup>-</sup>/OUT3A<sup>+</sup>, OUT3B<sup>-</sup>/OUT3B<sup>+</sup> (D10/D9, E10/E9): Serial Data Outputs for Channel 3. In 1-lane output mode only OUT3A<sup>-</sup>/OUT3A<sup>+</sup> are used.

OUT4A<sup>-</sup>/OUT4A<sup>+</sup>, OUT4B<sup>-</sup>/OUT4B<sup>+</sup> (C9/C10, F7/F8): Serial Data Outputs for Channel 4. In 1-lane output mode only OUT4A<sup>-</sup>/OUT4A<sup>+</sup> are used.

OUT5A<sup>-</sup>/OUT5A<sup>+</sup>, OUT5B<sup>-</sup>/OUT5B<sup>+</sup> (J8/J7, K8/K7): Serial Data Outputs for Channel 5. In 1-lane output mode only OUT5A<sup>-</sup>/OUT5A<sup>+</sup> are used.

OUT6A<sup>-</sup>/OUT6A<sup>+</sup>, OUT6B<sup>-</sup>/OUT6B<sup>+</sup> (K9/K10, L9/L10): Serial Data Outputs for Channel 6. In 1-lane output mode only OUT6A<sup>-</sup>/OUT6A<sup>+</sup> are used.

OUT7A<sup>-</sup>/OUT7A<sup>+</sup>, OUT7B<sup>-</sup>/OUT7B<sup>+</sup> (M7/L7, P8/N8): Serial Data Outputs for Channel 7. In 1-lane output mode only OUT7A<sup>-</sup>/OUT7A<sup>+</sup> are used.

OUT8A<sup>-</sup>/OUT8A<sup>+</sup>, OUT8B<sup>-</sup>/OUT8B<sup>+</sup> (L8/M8, M10/M9): Serial Data Outputs for Channel 8. In 1-lane output mode only OUT8A<sup>-</sup>/OUT8A<sup>+</sup> are used.

FRA<sup>-</sup>/FRA<sup>+</sup> (H7/H8): Frame Start Outputs for Channels 1, 4, 5 and 8.

FRB<sup>-</sup>/FRB<sup>+</sup> (J9/J10): Frame Start Outputs for Channels 2, 3, 6 and 7.

DCOA<sup>-</sup>/DCOA<sup>+</sup> (G8/G7): Data Clock Outputs for Channels 1, 4, 5 and 8.

DCOB<sup>-</sup>/DCOB<sup>+</sup> (F10, F9): Data Clock Outputs for Channels 2, 3, 6 and 7.

# LTM9008-14/ LTM9007-14/LTM9006-14

|   | 1                             | 2                             | 3                 | 4               | 5           | 6                | 7                  | 8                  | 9                  | 10                 |

|---|-------------------------------|-------------------------------|-------------------|-----------------|-------------|------------------|--------------------|--------------------|--------------------|--------------------|

| Α | GND                           | GND                           | GND               | GND             | GND         | GND              | PAR/SER            | OUT2A <sup>+</sup> | GND                | GND                |

| В | A <sub>IN1</sub> <sup>-</sup> | A <sub>IN1</sub> +            | V <sub>CM14</sub> | GND             | GND         | V <sub>REF</sub> | GND                | OUT2A <sup>-</sup> | GND                | GND                |

| C | A <sub>IN2</sub> <sup>-</sup> | A <sub>IN2</sub> +            | GND               | GND             | SENSE       | GND              | OUT2B+             | OUT1B <sup>-</sup> | OUT4A-             | OUT4A+             |

| D | GND                           | GND                           | V <sub>DD</sub>   | V <sub>DD</sub> | GND         | SDOB             | OUT2B-             | OUT1B+             | OUT3A+             | OUT3A-             |

| Е | A <sub>IN3</sub> <sup>-</sup> | A <sub>IN3</sub> +            | V <sub>DD</sub>   | V <sub>DD</sub> | GND         | SDOA             | OUT1A <sup>-</sup> | OUT1A <sup>+</sup> | OUT3B <sup>+</sup> | OUT3B <sup>-</sup> |

| F | GND                           | GND                           | V <sub>CM23</sub> | GND             | GND         | GND              | OUT4B-             | OUT4B+             | DCOB+              | DCOB-              |

| G | A <sub>IN4</sub> <sup>-</sup> | A <sub>IN4</sub> +            | GND               | GND             | GND         | GND              | DCOA+              | DCOA-              | OV <sub>DD</sub>   | OV <sub>DD</sub>   |

| Н | A <sub>IN5</sub> +            | A <sub>IN5</sub> <sup>-</sup> | GND               | GND             | GND         | GND              | FRA <sup>−</sup>   | FRA+               | GND                | GND                |

| J | GND                           | GND                           | V <sub>CM67</sub> | GND             | GND         | GND              | OUT5A <sup>+</sup> | OUT5A <sup>-</sup> | FRB <sup>−</sup>   | FRB <sup>+</sup>   |

| K | A <sub>IN6</sub> +            | A <sub>IN6</sub> <sup>-</sup> | V <sub>DD</sub>   | V <sub>DD</sub> | GND         | GND              | OUT5B+             | OUT5B-             | OUT6A-             | OUT6A+             |

| L | GND                           | GND                           | V <sub>DD</sub>   | V <sub>DD</sub> | <b>CS</b> A | SCK              | OUT7A+             | OUT8A <sup>-</sup> | OUT6B <sup>-</sup> | OUT6B <sup>+</sup> |

| М | A <sub>IN7</sub> +            | A <sub>IN7</sub> <sup>-</sup> | GND               | GND             | <u>CS</u> B | SDI              | OUT7A-             | OUT8A+             | OUT8B+             | OUT8B-             |

| Ν | A <sub>IN8</sub> +            | A <sub>IN8</sub> <sup>-</sup> | V <sub>CM58</sub> | GND             | GND         | GND              | GND                | OUT7B <sup>+</sup> | GND                | GND                |

| Р | GND                           | GND                           | GND               | GND             | ENC+        | ENC <sup>-</sup> | GND                | OUT7B-             | GND                | GND                |

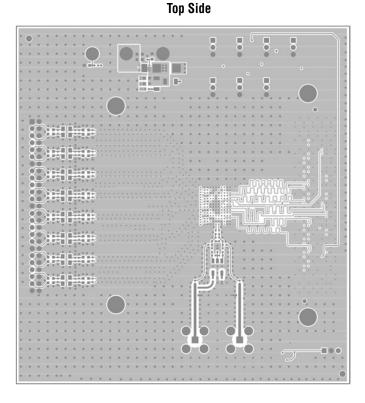

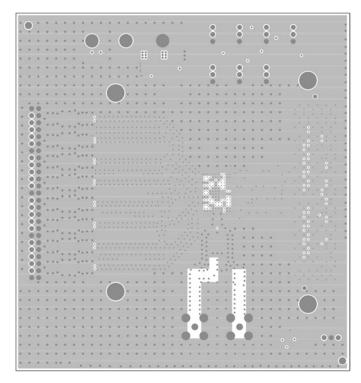

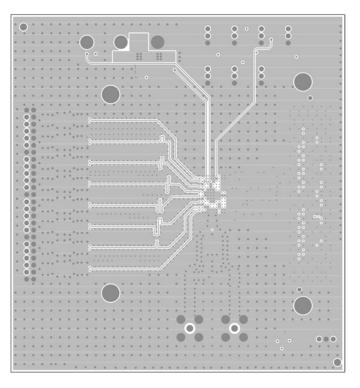

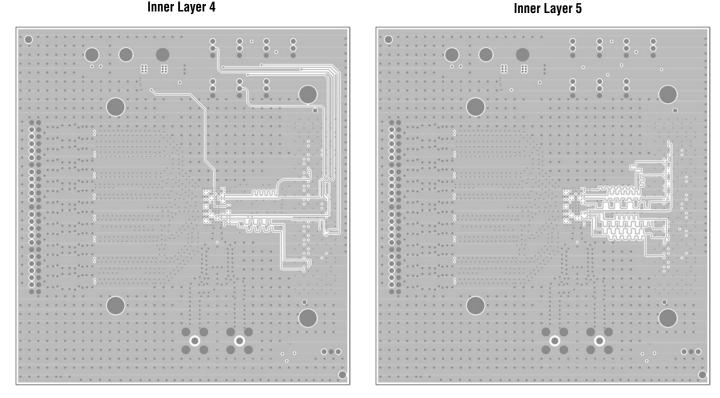

### PIN CONFIGURATION TABLE

Top View of BGA Package (Looking Through Component).

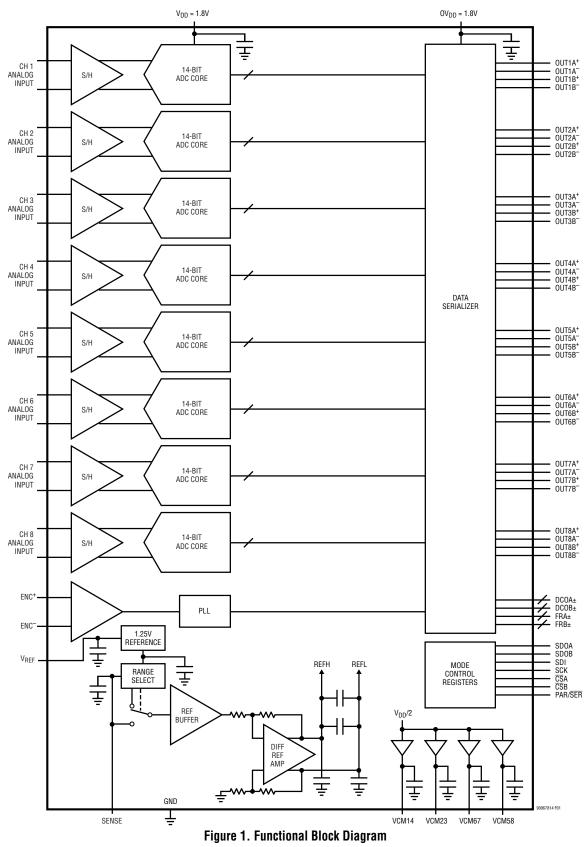

## FUNCTIONAL BLOCK DIAGRAM

#### **CONVERTER OPERATION**

The LTM9008-14/LTM9007-14/LTM9006-14 are low power, 8-channel, 14-bit, 65Msps/40Msps/25Msps A/D converters that are powered by a single 1.8V supply. The analog inputs should be driven differentially. The encode input can be driven differentially for optimal jitter performance, or single-ended for lower power consumption. The digital outputs are serial LVDS to minimize the number of data lines. Each channel outputs two bits at a time (2-lane mode) or one bit at a time (1-lane mode). Many additional features can be chosen by programming the mode control registers through a serial SPI port.

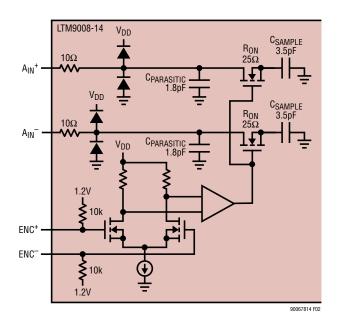

#### ANALOG INPUT

The analog inputs are differential CMOS sample-and-hold circuits (Figure 2). The inputs should be driven differentially around a common mode voltage set by the appropriate  $V_{CM}$  output pins, which are nominally  $V_{DD}/2$ . For the 2V input range, the inputs should swing from  $V_{CM} - 0.5V$  to  $V_{CM} + 0.5V$ . There should be 180° phase difference between the inputs.

The eight channels are simultaneously sampled by a shared encode circuit (Figure 2).

Figure 2. Equivalent Input Circuit. Only One of the Eight Analog Channels Is Shown

#### **INPUT DRIVE CIRCUITS**

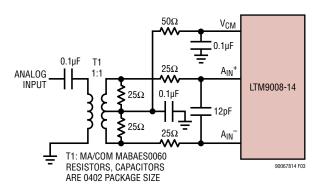

#### Input Filtering

If possible, there should be an RC low pass filter right at the analog inputs. This lowpass filter isolates the drive circuitry from the A/D sample-and-hold switching, and also limits wideband noise from the drive circuitry. Figure 3 shows an example of an input RC filter. The RC component values should be chosen based on the application's input frequency.

#### **Transformer Coupled Circuits**

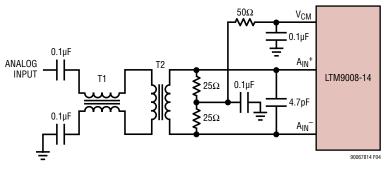

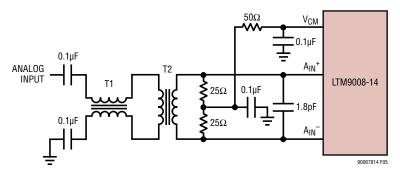

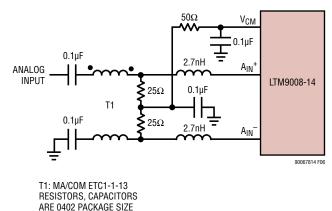

Figure 3 shows the analog input being driven by an RF transformer with a center-tapped secondary. The center tap is biased with  $V_{CM}$ , setting the A/D input at its optimal DC level. At higher input frequencies a transmission line balun transformer (Figures 4 to 6) has better balance, resulting in lower A/D distortion.

Figure 3. Analog Input Circuit Using a Transformer. Recommended for Input Frequencies from 5MHz to 70MHz

#### **Amplifier Circuits**

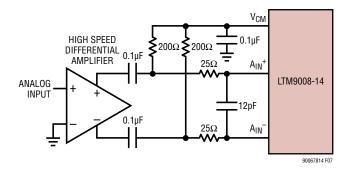

Figure 7 shows the analog input being driven by a high speed differential amplifier. The output of the amplifier is AC-coupled to the A/D so the amplifier's output common mode voltage can be optimally set to minimize distortion. See back page for a DC-coupled example.

At very high frequencies an RF gain block will often have lower distortion than a differential amplifier. If the gain block is single-ended, then a transformer circuit (Figures 4 to 6) should convert the signal to differential before driving the A/D.

T1: MA/COM MABA-007159-000000 T2: MA/COM MABAES0060 RESISTORS, CAPACITORS ARE 0402 PACKAGE SIZE

Figure 4. Recommended Front End Circuit for Input Frequencies from 70MHz to 170MHz

T1: MA/COM MABA-007159-000000 T2: COILCRAFT WBC1-1LB RESISTORS, CAPACITORS ARE 0402 PACKAGE SIZE

Figure 5. Recommended Front End Circuit for Input Frequencies from 170MHz to 300MHz

Figure 6. Recommended Front End Circuit for Input Frequencies Above 300MHz

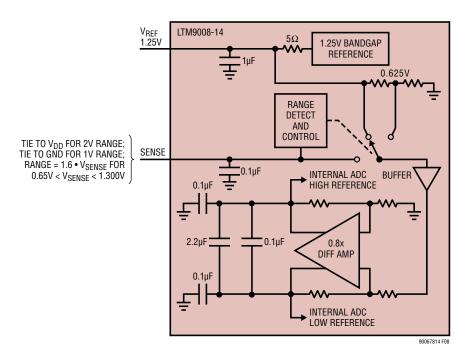

#### Reference

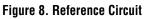

The LTM9008-14/LTM9007-14/LTM9006-14 has an internal 1.25V voltage reference. For a 2V input range using the internal reference, connect SENSE to  $V_{DD}$ . For a 1V input range using the internal reference, connect SENSE to ground. For a 2V input range with an external reference, apply a 1.25V reference voltage to SENSE (Figure 9).

The input range can be adjusted by applying a voltage to SENSE that is between 0.625V and 1.30V. The input range will then be  $1.6 \cdot V_{\text{SENSE}}$ . The reference is shared by all eight ADC channels, so it is not possible to independently adjust the input range of individual channels.

The  $V_{\text{REF}},$  SENSE, REFH and REFL pins are internally bypassed, as shown in Figure 8.

Figure 9. Using an External 1.25V Reference

#### **Encode Input**

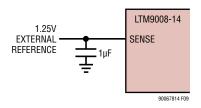

The signal quality of the encode inputs strongly affects the A/D noise performance. The encode inputs should be treated as analog signals—do not route them next to digital traces on the circuit board. There are two modes of operation for the encode inputs: the differential encode mode (Figure 10), and the single-ended encode mode (Figure 11).

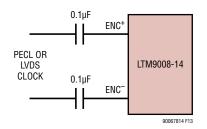

The differential encode mode is recommended for sinusoidal, PECL, or LVDS encode inputs (Figures 12 and 13).

Figure 10. Equivalent Encode Input Circuit for Differential Encode Mode

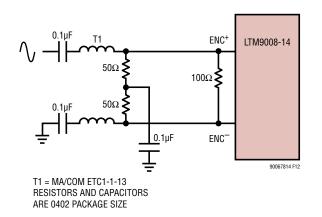

Figure 12. Sinusoidal Encode Drive

The encode inputs are internally biased to 1.2V through 10k equivalent resistance. The encode inputs can be taken above  $V_{DD}$  (up to 3.6V), and the common mode range is from 1.1V to 1.6V. In the differential encode mode, ENC<sup>-</sup> should stay at least 200mV above ground to avoid falsely triggering the single-ended encode mode. For good jitter performance ENC<sup>+</sup> should have fast rise and fall times.

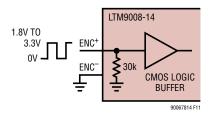

The single-ended encode mode should be used with CMOS encode inputs. To select this mode, ENC<sup>-</sup> is connected to ground and ENC<sup>+</sup> is driven with a square wave encode

Figure 11. Equivalent Encode Input Circuit for Single-Ended Encode Mode

Figure 13. PECL or LVDS Encode Drive

input. ENC<sup>+</sup> can be taken above  $V_{DD}$  (up to 3.6V) so 1.8V to 3.3V CMOS logic levels can be used. The ENC<sup>+</sup> threshold is 0.9V. For good jitter performance ENC<sup>+</sup> should have fast rise and fall times.

#### **Clock PLL and Duty Cycle Stabilizer**

The encode clock is multiplied by an internal phase-locked loop (PLL) to generate the serial digital output data. If the encode signal changes frequency or is turned off, the PLL requires 25µs to lock onto the input clock.

A clock duty cycle stabilizer circuit allows the duty cycle of the applied encode signal to vary from 30% to 70%. In the serial programming mode it is possible to disable the duty cycle stabilizer, but this is not recommended. In the parallel programming mode the duty cycle stabilizer is always enabled.

#### **DIGITAL OUTPUTS**

The digital outputs of the LTM9008-14/LTM9007-14/ LTM9006-14 are serialized LVDS signals. Each channel outputs two bits at a time (2-lane mode) or one bit at a time (1-lane mode). The data can be serialized with 16, 14, or 12-bit serialization (see the Timing Diagrams section for details). Note that with 12-bit serialization the two LSBs are not available—this mode is included for compatibility with 12-bit versions of these parts.

The output data should be latched on the rising and falling edges of the data clock out (DCO). A data frame output (FR) can be used to determine when the data from a new conversion result begins. In the 2-lane, 14-bit serialization mode, the frequency of the FR output is halved.

The maximum serial data rate for the data outputs is 1Gbps, so the maximum sample rate of the ADC will depend on the serialization mode as well as the speed grade of the ADC (see Table 1). The minimum sample rate for all serialization modes is 5Msps.

By default the outputs are standard LVDS levels: 3.5mA output current and a 1.25V output common mode voltage. An external  $100\Omega$  differential termination resistor is required for each LVDS output pair. The termination resistors should be located as close as possible to the LVDS receiver.

The outputs are powered by  $OV_{DD}$  which is independent from the A/D core power.

Table 1. Maximum Sampling Frequency for All Serialization Modes. Note That These Limits Are for the LTM9008-14. The Sampling Frequency for the Slower Speed Grades Cannot Exceed 40MHz (LTM9007-14) or 25MHz (LTM9006-14)

| SERIALIZAT | TION MODE            | MAXIMUM SAMPLING<br>Frequency, f <sub>s</sub> (MHz) | DCO FREQUENCY        | FR FREQUENCY         | SERIAL DATA RATE    |

|------------|----------------------|-----------------------------------------------------|----------------------|----------------------|---------------------|

| 2-Lane     | 16-Bit Serialization | 65                                                  | 4 • f <sub>S</sub>   | f <sub>S</sub>       | 8 • f <sub>S</sub>  |

| 2-Lane     | 14-Bit Serialization | 65                                                  | 3.5 • f <sub>S</sub> | 0.5 • f <sub>S</sub> | 7 • f <sub>S</sub>  |

| 2-Lane     | 12-Bit Serialization | 65                                                  | 3 • f <sub>S</sub>   | f <sub>S</sub>       | 6 • f <sub>S</sub>  |

| 1-Lane     | 16-Bit Serialization | 62.5                                                | 8 • f <sub>S</sub>   | f <sub>S</sub>       | 16 • f <sub>S</sub> |

| 1-Lane     | 14-Bit Serialization | 65                                                  | 7 • f <sub>S</sub>   | fs                   | 14 • f <sub>S</sub> |

| 1-Lane     | 12-Bit Serialization | 65                                                  | 6 • f <sub>S</sub>   | f <sub>S</sub>       | 12 • f <sub>S</sub> |

#### Programmable LVDS Output Current

The default output driver current is 3.5mA. This current can be adjusted by control register A2 in the serial programming mode. Available current levels are 1.75mA, 2.1mA, 2.5mA, 3mA, 3.5mA, 4mA and 4.5mA. In the parallel programming mode, the SCK pin can select either 3.5mA or 1.75mA.

#### **Optional LVDS Driver Internal Termination**

In most cases, using just an external  $100\Omega$  termination resistor will give excellent LVDS signal integrity. In addition, an optional internal  $100\Omega$  termination resistor can be enabled by serially programming mode control register A2. The internal termination helps absorb any reflections caused by imperfect termination at the receiver. When the internal termination is enabled, the output driver current is doubled to maintain the same output voltage swing. In the parallel programming mode the SDO pin enables internal termination. Internal termination should only be used with 1.75mA, 2.1mA or 2.5mA LVDS output current modes.

#### DATA FORMAT

Table 2 shows the relationship between the analog input voltage and the digital data output bits. By default the output data format is offset binary. The 2's complement format can be selected by serially programming mode control register A1.

| A <sub>IN</sub> + – A <sub>IN</sub> <sup>–</sup><br>(2V RANGE) | D13-D0<br>(Offset Binary) | D13-D0<br>(2's COMPLEMENT) |

|----------------------------------------------------------------|---------------------------|----------------------------|

| >1.000000V                                                     | 11 1111 1111 1111         | 01 1111 1111 1111          |

| +0.999878V                                                     | 11 1111 1111 1111         | 01 1111 1111 1111          |

| +0.999756V                                                     | 11 1111 1111 1110         | 01 1111 1111 1110          |

| +0.000122V                                                     | 10 0000 0000 0001         | 00 0000 0000 0001          |

| +0.000000V                                                     | 10 0000 0000 0000         | 00 0000 0000 0000          |

| -0.000122V                                                     | 01 1111 1111 1111         | 11 1111 1111 1111          |

| -0.000244V                                                     | 01 1111 1111 1110         | 11 1111 1111 1110          |

| -0.999878V                                                     | 00 0000 0000 0001         | 10 0000 0000 0001          |

| -1.000000V                                                     | 00 0000 0000 0000         | 10 0000 0000 0000          |

| <-1.000000V                                                    | 00 0000 0000 0000         | 10 0000 0000 0000          |

#### Table 2. Output Codes vs Input Voltage

#### **Digital Output Randomizer**

Interference from the A/D digital outputs is sometimes unavoidable. Digital interference may be from capacitive or inductive coupling or coupling through the ground plane. Even a tiny coupling factor can cause unwanted tones in the ADC output spectrum. By randomizing the digital output before it is transmitted off chip, these unwanted tones can be randomized which reduces the unwanted tone amplitude.

The digital output is randomized by applying an exclusive-OR logic operation between the LSB and all other data output bits. To decode, the reverse operation is applied —an exclusive-OR operation is applied between the LSB and all other bits. The FR and DCO outputs are not affected. The output randomizer is enabled by serially programming mode control register A1.

#### Digital Output Test Pattern

To allow in-circuit testing of the digital interface to the A/D, there is a test mode that forces the A/D data outputs (D13-D0) of all channels to known values. The digital output test patterns are enabled by serially programming mode control registers A3 and A4. When enabled, the test patterns override all other formatting modes: 2's complement and randomizer.

#### **Output Disable**

The digital outputs may be disabled by serially programming mode control register A2. The current drive for all digital outputs including DCO and FR are disabled to save power or enable in-circuit testing. When disabled the common mode of each output pair becomes high impedance, but the differential impedance may remain low.

#### **Sleep and Nap Modes**

The A/D may be placed in sleep or nap modes to conserve power. In sleep mode the entire device is powered down, resulting in 2mW power consumption. Sleep mode is enabled by mode control register A1 (serial programming mode), or by SDI (parallel programming mode). The time required to recover from sleep mode is about 2ms.

In nap mode any combination of A/D channels can be powered down while the internal reference circuits and the PLL stay active, allowing faster wakeup than from sleep mode. Recovering from nap mode requires at least 100 clock cycles. If the application demands very accurate DC settling then an additional 50µs should be allowed so the on-chip references can settle from the slight temperature shift caused by the change in supply current as the A/D leaves nap mode. Nap mode is enabled by mode control register A1 in the serial programming mode.

#### **DEVICE PROGRAMMING MODES**

The operating modes of the LTM9008-14/LTM9007-14/ LTM9006-14 can be programmed by either a parallel interface or a simple serial interface. The serial interface has more flexibility and can program all available modes. The parallel interface is more limited and can only program some of the more commonly used modes.

#### **Parallel Programming Mode**

To use the parallel programming mode, PAR/SER should be tied to  $V_{DD}$ . The  $\overline{CS}$ , SCK, SDI and SDO pins are binary logic inputs that set certain operating modes. These pins can be tied to  $V_{DD}$  or ground, or driven by 1.8V, 2.5V, or 3.3V CMOS logic. When used as an input, SDO should be driven through a 1k series resistor. Table 3 shows the modes set by  $\overline{CS}$ , SCK, SDI and SDO.

| Table 3. Parallel P             | Programming | Mode | <b>Control Bits</b> |

|---------------------------------|-------------|------|---------------------|

| $(PAR/\overline{SER} = V_{DD})$ |             |      |                     |

| Pin | DESCRIPTION                                  |

|-----|----------------------------------------------|

| CS  | 2-Lane / 1-Lane Selection Bit                |

|     | 0 = 2-Lane, 16-Bit Serialization Output Mode |

|     | 1 = 1-Lane, 14-Bit Serialization Output Mode |

| SCK | LVDS Current Selection Bit                   |

|     | 0 = 3.5mA LVDS Current Mode                  |

|     | 1 = 1.75mA LVDS Current Mode                 |

| SDI | Power Down Control Bit                       |

|     | 0 = Normal Operation                         |

|     | 1 = Sleep Mode                               |

| SDO | Internal Termination Selection Bit           |

|     | 0 = Internal Termination Disabled            |

|     | 1 = Internal Termination Enabled             |

#### Serial Programming Mode

To use the serial programming mode, PAR/SER should be tied to ground. The CS, SCK, SDI and SDO pins become a serial interface that program the A/D mode control registers. Data is written to a register with a 16-bit serial word. Data can also be read back from a register to verify its contents.

Serial data transfer starts when  $\overline{\text{CS}}$  is taken low. The data on the SDI pin is latched at the first 16 rising edges of SCK. Any SCK rising edges after the first 16 are ignored. The data transfer ends when  $\overline{\text{CS}}$  is taken high again.

The first bit of the 16-bit input word is the  $R/\overline{W}$  bit. The next seven bits are the address of the register (A6:A0). The final eight bits are the register data (D7:D0).

If the  $R/\overline{W}$  bit is low, the serial data (D7:D0) will be written to the register set by the address bits (A6:A0). If the  $R/\overline{W}$  bit is high, data in the register set by the address bits (A6:A0) will be read back on the SDO pin (see the Timing Diagrams section). During a read back command the register is not updated and data on SDI is ignored.

The SDO pin is an open-drain output that pulls to ground with a 200 $\Omega$  impedance. If register data is read back through SDO, an external 2k pull-up resistor is required. If serial data is only written and read back is not needed, then SDO can be left floating and no pull-up resistor is needed. Table 4 shows a map of the mode control registers.

D1

D٥

| Table 4. Serial Pr | ogramming Mod    | le Register Map ( | PAR/SER = GND) |  |

|--------------------|------------------|-------------------|----------------|--|

| REGISTER AO: RES   | ET REGISTER (ADD | RESS 00h)         |                |  |

| D7                 | D6               | D5                | D4             |  |

| D                                                                                   | 1 D0                                                                                                                                                                                                                                                        | D5                 | D4 | 05 | DZ | DI | DU |  |  |  |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|----|----|----|----|--|--|--|

| RES                                                                                 | SET X                                                                                                                                                                                                                                                       | Х                  | Х  | Х  | Х  | Х  | Х  |  |  |  |

| Note That CSA Controls Channels 1, 4, 5 and 8, CSB Controls Channels 2, 3, 6 and 7. |                                                                                                                                                                                                                                                             |                    |    |    |    |    |    |  |  |  |

| Bit 7                                                                               | RESET                                                                                                                                                                                                                                                       | Software Reset Bit |    |    |    |    |    |  |  |  |

|                                                                                     | 0 = Not Used<br>1 = Software Reset. All Mode Control Registers Are Reset to 00h. The ADC Is Momentarily Placed in SLEEP Mode.<br>After the Reset SPI Write Command Is Complete, Bit D7 Is Automatically Set Back to Zero. The Reset Register Is Write Only. |                    |    |    |    |    |    |  |  |  |

| Bits 6-0                                                                            | Unused, Don't Ca                                                                                                                                                                                                                                            | re Bits.           |    |    |    |    |    |  |  |  |

D3

ר2

#### REGISTER A1 ( $\overline{CSA}$ ): FORMAT AND POWER-DOWN REGISTER (ADDRESS 01h with $\overline{CSA}$ = GND)

| D7               | D6                                                                                                                                                                                                                                                                                                                                                                                                                               | D5       | D4              | D3    | D2    | D1    | D0       |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-------|-------|-------|----------|--|--|

| DCSOFF           | RAND                                                                                                                                                                                                                                                                                                                                                                                                                             | TWOSCOMP | SLEEP           | NAP_8 | NAP_5 | NAP_4 | NAP_1    |  |  |

| Note That CSA Co | Note That CSA Controls Channels 1, 4, 5 and 8, CSB Controls Channels 2, 3, 6 and 7.                                                                                                                                                                                                                                                                                                                                              |          |                 |       |       |       |          |  |  |

| Bit 7            | Bit 7 DCSOFF Clock Duty Cycle Stabilizer Bit<br>0 = Clock Duty Cycle Stabilizer On<br>1 = Clock Duty Cycle Stabilizer Off. This Is Not Recommended.                                                                                                                                                                                                                                                                              |          |                 |       |       |       |          |  |  |

| Bit 6            | <b>RAND</b> Data Output Randomizer Mode Control Bit<br>0 = Data Output Randomizer Mode Off<br>1 = vData Output Randomizer Mode On                                                                                                                                                                                                                                                                                                |          |                 |       |       |       |          |  |  |

| Bit 5            | 0 = Offset Binary E                                                                                                                                                                                                                                                                                                                                                                                                              |          | ode Control Bit |       |       |       |          |  |  |

| Bits 4-0         | 1 = Two's Complement Data Format   Bits 4-0 SLEEP: NAP_X Sleep/Nap Mode Control Bits   00000 = Normal Operation 0XXX1 = Channel 1 in Nap Mode   0XX11 = Channel 4 in Nap Mode 0X1X2 = Channel 4 in Nap Mode   0X1XX = Channel 5 in Nap Mode 01XXX = Channel 5 in Nap Mode   01XXX = Channel 8 in Nap Mode 1XXXX = Sleep Mode. Channels 1, 4, 5 and 8 Are Disabled   Note: Any Combination of Channels Can Be Placed in Nap Mode. |          |                 |       |       |       |          |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                 |       |       |       | 00067814 |  |  |

#### **REGISTER A1** ( $\overline{CSB}$ ): FORMAT AND POWER-DOWN REGISTER (ADDRESS 01h with $\overline{CSB}$ = GND)

| D7                                                                                                                                                                                                                                                                                                                                                                  | D6                                                                                                                                                   | D5                                                   | D4                  | D3       | D2    | D1    | D0    |