# **CL8800**

# **Sequential Linear LED Driver**

#### Features

- Minimal component count (base config: CL8800 + 6 resistors + diode bridge)

- · No magnetics, no capacitors

- Up to 7.5W output (13W w/ heat sink)

- >110Lm/W using efficient LEDs

- · 85% typical electrical efficiency

- >0.95 power factor

- <20% THD line current

- · Low conducted EMI w/o filters

- 85% LED luminous utilization

- · Phase dimmer compatible with an RC network

#### Applications

- Fluorescent tube retrofit

- · Incandescent & CFL bulb replacement

- · General LED lighting

#### Description

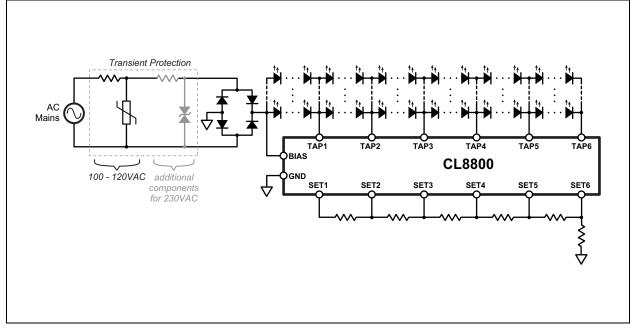

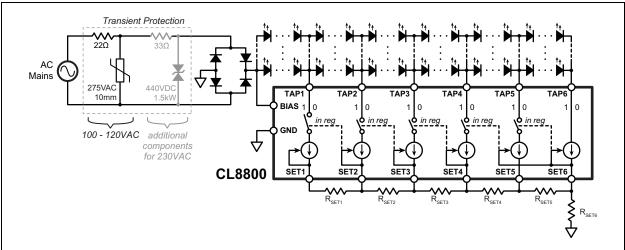

CL8800 is designed to drive a long string of inexpensive, low-current LEDs directly from the AC mains. A basic driver circuit consists of CL8800, six resistors, and a bridge rectifier. Two to four additional components are optional for various levels of transient protection. No capacitors, EMI filters, or power factor correction circuits are needed.

A string of series/parallel LEDs is tapped at six locations. Six linear current regulators sink current at each tap and are sequentially turned on and off. Thereby tracking the input sine wave voltage. Voltage across each regulator is minimized when conducting, providing high efficiency. Output current at each tap is individually resistor-adjustable. Cross-regulation, as the CL8800 switches from one regulator to another, provides smooth transitions. The current waveform can be tailored to optimize for input voltage range, line/load regulation, output power/current, efficiency, power factor, THD, dimmer compatibility, and LED utilization.

With the addition of an RC network, the driver is compatible with phase dimming.

# CL8800

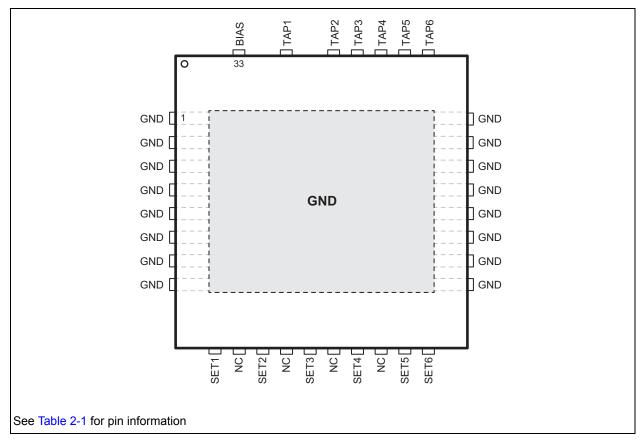

#### Package Type

#### **Typical Application Circuit**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>BIAS</sub> , V <sub>TAP1</sub> | 0.5V to +550V  |

|---------------------------------------|----------------|

| V <sub>TAP2-6</sub>                   | 50V to +320V   |

| V <sub>SFT1-6</sub>                   | 4.0V           |

| Operating temperature                 | 55°C to +125°C |

| Storage temperature, T <sub>S</sub>   | 65°C to +150°C |

**Note**: Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### 1.1 ELECTRICAL SPECIFICATIONS

| Symbol            | Parameter            |        | Min | Тур | Max                 | Units | Conditions     |

|-------------------|----------------------|--------|-----|-----|---------------------|-------|----------------|

|                   |                      | TAP1   |     |     | 60                  | mA    |                |

|                   |                      | TAP2   |     |     | 90                  | mA    |                |

|                   | Output Current       | TAP3   |     |     | 115                 | mA    |                |

| IOUT              | Output Current       | TAP4   |     |     | 115                 | mA    |                |

|                   |                      | TAP5   |     |     | 115                 | mA    |                |

|                   |                      | TAP6   |     |     | 115                 | mA    |                |

|                   |                      | TAP1   |     |     | 400                 | V     | Non-conducting |

| V <sub>OUT</sub>  | Output Voltage       | TAP2-6 |     |     | 300                 | V     | Non-conducting |

|                   |                      | TAP1-6 |     |     | varies <sup>1</sup> | V     | Conducting     |

| V <sub>BIAS</sub> | Applied BIAS voltage |        |     |     | 440                 | V     |                |

#### TABLE 1-1: RECOMMENDED OPERATING CONDITIONS

1 Voltage capability is determined by power dissipation (V \* I).

#### TABLE 1-2: ELECTRICAL CHARACTERISTICS<sup>1</sup>

| Symbol                | Parameter              | Min    | Тур  | Max  | Units | Conditions               |                                                    |

|-----------------------|------------------------|--------|------|------|-------|--------------------------|----------------------------------------------------|

| I <sub>BIAS</sub>     | BIAS pin input current |        | 250  | 410  | μA    | V <sub>BIAS</sub> = 340V |                                                    |

|                       |                        | TAP1   | 60   |      |       | mA                       | V <sub>TAP1</sub> = 30V, V <sub>SET1-6</sub> = GND |

|                       | Output current, on     | TAP2   | 90   |      |       | mA                       | V <sub>TAP2</sub> = 17V, V <sub>SET1-6</sub> = GND |

|                       |                        | TAP3   | 115  |      |       | mA                       | V <sub>TAP3</sub> = 17V, V <sub>SET1-6</sub> = GND |

| I <sub>TAP</sub> (ON) |                        | TAP4   | 115  |      |       | mA                       | V <sub>TAP4</sub> = 17V, V <sub>SET1-6</sub> = GND |

|                       |                        | TAP5   | 115  |      |       | mA                       | V <sub>TAP5</sub> = 17V, V <sub>SET1-6</sub> = GND |

|                       |                        | TAP6   | 115  |      |       | mA                       | V <sub>TAP6</sub> = 17V, V <sub>SET1-6</sub> = GND |

| I <sub>TAP(OFF)</sub> | Output current, off    |        |      | 0    | 10    | μA                       | Tap 1-5, V <sub>BIAS</sub> = 312V                  |

| V <sub>REG</sub>      | Regulation voltage at  | SET1-5 | 1.80 | 2.00 | 2.20  | V                        |                                                    |

|                       | SET pins               | SET6   | 1.89 | 2.10 | 2.31  | V                        |                                                    |

1 Over recommended operating conditions at 25°C, unless specified otherwise.

#### TABLE 1-3: THERMAL RESISTANCE

| Package     | θ <sub>ja</sub> 1 | θ <sub>jc</sub> <sup>2</sup> |

|-------------|-------------------|------------------------------|

| 33-Lead QFN | 24°C/W            | 2.5°C/W                      |

1 1.0 oz Cu 4-layer board, 3x4" PCB with thermal pad and thermal via array.

2 Junction to exposed heat slug.

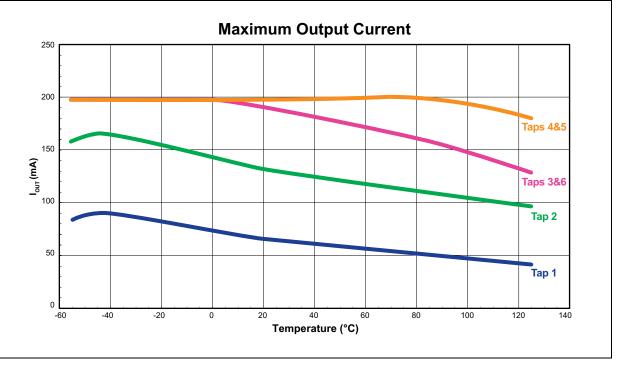

#### FIGURE 1-1: OUTPUT CURRENT THERMAL CHARACTERISTICS

#### 2.0 PIN DESCRIPTION

The locations of the pins are listed in Package Type.

| IABLE 2-1:               | PIN DESCRIP | TION                                                                                                                                                |

|--------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                    | Function    | Description                                                                                                                                         |

| 1 - 8                    | GND         | Circuit common (use for heat sink ground plane pass through).                                                                                       |

| 9                        | SET1        | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                            |

| 10                       | NC          | No internal connection.                                                                                                                             |

| 11                       | SET2        | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                            |

| 12                       | NC          | No internal connection.                                                                                                                             |

| 13                       | SET3        | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                            |

| 14                       | NC          | No internal connection.                                                                                                                             |

| 15                       | SET4        | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                            |

| 16                       | NC          | No internal connection.                                                                                                                             |

| 17                       | SET5        | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                            |

| 18                       | SET6        | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                            |

| 19 - 20                  | GND         | Circuit common (use for heat sink ground plane pass through).                                                                                       |

| 21                       | GND         | Circuit common. Connect to bridge rectifier return (use for heat sink ground plane pass through).                                                   |

| 22 - 26                  | GND         | Circuit common (use for heat sink ground plane pass through).                                                                                       |

| 27                       | TAP6        |                                                                                                                                                     |

| 28                       | TAP5        |                                                                                                                                                     |

| 29                       | TAP4        | Current regulator outputs. Connect to tang along the LED string                                                                                     |

| 30                       | TAP3        | Current regulator outputs. Connect to taps along the LED string.                                                                                    |

| 31                       | TAP2        |                                                                                                                                                     |

| 32                       | TAP1        |                                                                                                                                                     |

| 33                       | BIAS        | Provides bias for driver. Connect to rectified AC.                                                                                                  |

| Underside plate<br>(GND) |             | For heat sinking purposes, it should be soldered to a 4.0cm2 exposed copper area. It should also be electrically connected to circuit common (GND). |

#### TABLE 2-1: PIN DESCRIPTION

#### 3.0 APPLICATION INFORMATION

#### 3.1 Overview

Designing a driver to meet particular requirements may be a difficult task considering the 18 design variables: tap current (6), number of series-connected LEDs per segment (6), and the number of parallel-connected LEDs per segment (6). Manually selecting values will provide light, but the chosen values may be far from optimal in regards to efficiency, LED utilization, and line regulation.

Contact your nearest Microchip Field Applications Engineer for design assistance.

In addition to configuring the driver, several circuits may be employed to increase reliability, performance, and cost. The following sections briefly describe these circuits.

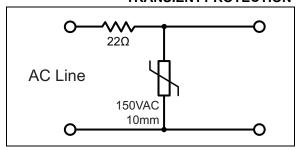

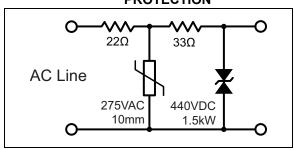

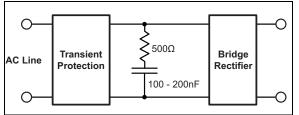

#### 3.2 Transient Protection

The driver circuits have no need for capacitors that could otherwise absorb transient energy, nor is there a need for EMI filters that would block transients. Therefore, the full burden of transient protection is borne by the protection circuit. The two-stage approach in the following schematics provide 2.5kV protection, both pulse and ring per EN 61000-4-5 and EN 61000-4-12, six hits each.

#### FIGURE 3-1: 100 TO 120 VAC TRANSIENT PROTECTION

FIGURE 3-2:

230VAC TRANSIENT PROTECTION

#### 3.3 Zener Diode Substitution

Zener diodes may be substituted for LEDs in the bottom stages of the design. The last 1 or 2 stages of LEDs contribute little to the light output - they are mainly present to off-load the adjacent upstream regulator at high line voltages to minimize losses. The advantages of Zener substitution includes minimizing unlit LEDs at low line for better light uniformity, better line regulation at high line, fewer LEDs for lower cost and less PCB area, and fewer board-to-board connections. Disadvantages include slightly-reduced efficiency at high line, and additional heat load on the driver board.

#### 3.4 Phase Dimming

As with any light load, the LED lamp might not draw enough current to ensure proper dimmer operation. This is especially true for 230VAC dimmers. Triodes for Alternating Current (TRIAC) used in dimmers require a minimum latching current when triggered to place the TRIAC in the latched-on state. Once latched, a minimum holding current is required to maintain the TRIAC in the on state. Latching current is many times greater than the holding current, and is the main concern with dimmer compatibility.

Higher latching current can be provided by a simple series RC network across the AC line. A short time constant provides a current spike at the turn-on edge.

Less common is inadequate holding current. The minimum dimmer holding current is typically 10-20mA. Tap1 at 60mA (max) exceeds the minimum.

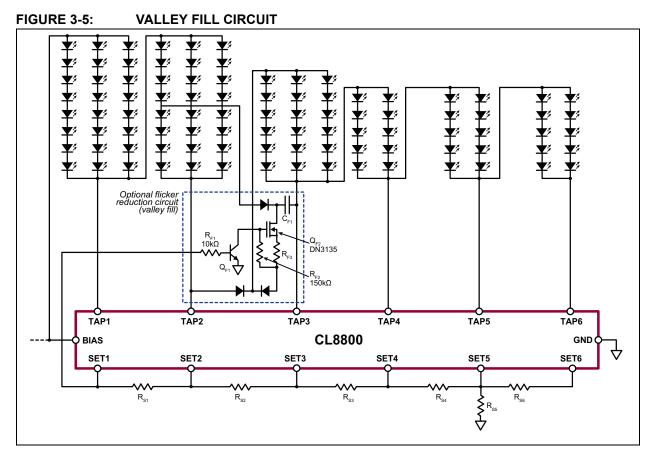

#### 3.5 Strobing

Twice per AC line cycle the line voltage crosses zero volts, during which time there is no light output.

The circuit in Figure 3-4 can provide 5-10% valley fill. It has little effect on input current wave shape (THD, PF) and efficiency.

This circuit is intended to prevent the output from reaching zero. It will not significantly reduce output ripple.

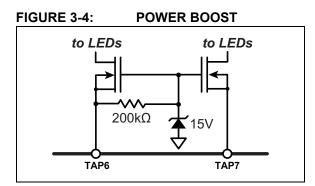

#### 3.6 Power Boost

Higher output power can be achieved by off-loading a portion of the power dissipation from the CL8800 to external Field-Effect Transistors (FET). The circuit below drops most of the tap voltage across the FETs, thereby shifting the bulk of the dissipation to the FET.

# CL8800

#### 4.0 PACKAGING INFORMATION

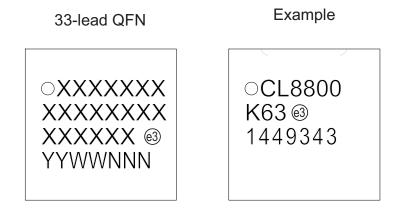

#### 4.1 Package Marking Information

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>e3<br>* | Product Code or Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((23))<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carried<br>characters                  | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for product code or customer-specific information. Package may or<br>include the corporate logo.                                                                                                                                                             |

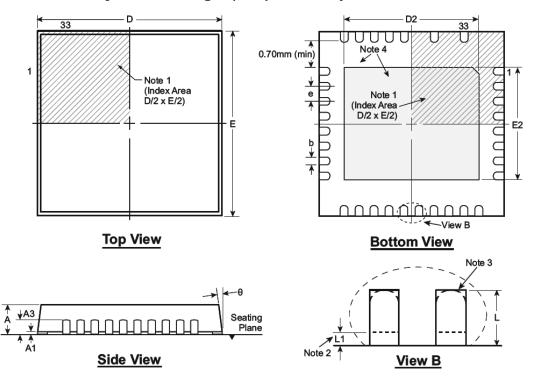

### 33-Lead QFN Package Outline (K6)

6.00x6.00mm body, 1.00mm height (max), 0.50mm pitch

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- The inner tip of the lead may be either rounded or square.

There will be an exposed DAP. A minimum of 0.7mm spacing will be maintained between the leads and the DAP.

| Symb              | ol  | А    | A1   | A3          | b    | D    | D2   | E    | E2   | e           | L    | L1   | θο |

|-------------------|-----|------|------|-------------|------|------|------|------|------|-------------|------|------|----|

|                   | MIN | 0.80 | 0.00 |             | 0.18 | 5.85 | 4.00 | 5.85 | 3.60 |             | 0.30 | 0.00 | 0  |

| Dimension<br>(mm) | NOM | 0.90 | 0.02 | 0.20<br>REF | 0.25 | 6.00 | 4.15 | 6.00 | 3.75 | 0.50<br>BSC | 0.40 | -    | -  |

| (mm)              | MAX | 1.00 | 0.05 |             | 0.30 | 6.15 | 4.25 | 6.15 | 3.85 |             | 0.50 | 0.15 | 14 |

Drawings not to scale.

#### APPENDIX A: REVISION HISTORY

#### Revision A (January 2015)

Update file to new format

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.      | <u>xx - x - x</u>                           | Exa | amples:          |                                   |

|---------------|---------------------------------------------|-----|------------------|-----------------------------------|

| Device        | Package Environmental Media<br>Options Type | a)  | CL8800K63-G:     | 33-lead QFN package,<br>490/Tray. |

|               |                                             | b)  | CL8800K63-G-M935 | 33-lead QFN package,<br>3000/Reel |

| Device:       | CL8800 = Sequential Linear LED Driver       |     |                  |                                   |

| Package:      | K6(3) = QFN (6x6 mm body), 33-lead          |     |                  |                                   |

| Environmental | G = Lead (Pb)-free/ROHS-compliant package   |     |                  |                                   |

| Media Type:   | (blank) = 490/Tray                          |     |                  |                                   |

|               | M935 = 3000/Reel                            |     |                  |                                   |

|               |                                             |     |                  |                                   |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-63276-957-2

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205 China - Shanghai Tel: 86-21 5407 5533

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

03/25/14