## MIC26901

## 28V, 9A Hyper Speed Control™ Synchronous DC/DC Buck Regulator

#### SuperSwitcher II™

## **General Description**

The Micrel MIC26901 is a constant-frequency, synchronous buck regulator featuring a unique adaptive on-time control architecture. The MIC26901 operates over an input supply range of 4.5V to 28V and provides a regulated output of up to 9A of output current. The output voltage is adjustable down to 0.8V with a guaranteed accuracy of  $\pm 1\%$ , and the device operates at a switching frequency of 600kHz.

Micrel's Hyper Speed Control<sup>TM</sup> architecture allows for ultrafast transient response while reducing the output capacitance and also makes (High  $V_{\text{IN}}$ )/(Low  $V_{\text{OUT}}$ ) operation possible. This adaptive  $t_{\text{ON}}$  ripple control architecture combines the advantages of fixed-frequency operation and fast transient response in a single device.

The MIC26901 offers a full suite of protection features to ensure protection of the IC during fault conditions. These include undervoltage lockout to ensure proper operation under power-sag conditions, internal soft-start to reduce inrush current, foldback current limit, "hiccup mode" short-circuit protection and thermal shutdown. An open-drain Power Good (PG) pin is provided.

All support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

- Hyper Speed Control<sup>™</sup> architecture enables

- High Delta V operation ( $V_{IN} = 28V$  and  $V_{OUT} = 0.8V$ )

- Small output capacitance

- 4.5V to 28V voltage input

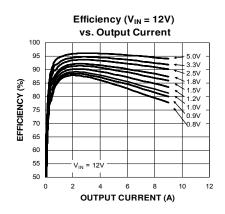

- 9A output current capability, up to 95% efficiency

- Adjustable output from 0.8V to 5.5V

- ±1% feedback accuracy

- Any Capacitor™ stable –zero-to-high ESR

- 600kHz switching frequency

- No external compensation

- Power Good (PG) output

- Foldback current-limit and "hiccup mode" short-circuit protection

- Supports safe startup into a pre-biased load

- -40°C to +125°C junction temperature range

- 28-pin 5mm × 6mm MLF® package

## **Applications**

- Distributed power systems

- Communications/networking infrastructure

- Set-top box, gateways and routers

- Printers, scanners, graphic cards and video cards

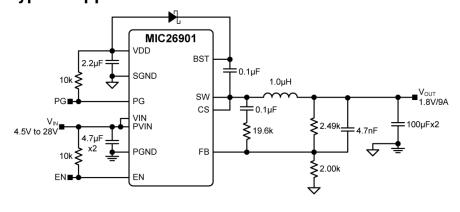

# Typical Application

Hyper Speed Control, SuperSwitcher II, and Any Capacitor are trademarks of Micrel, Inc. MLF and *Micro*LeadFrame are registered trademarks of Amkor Technology, Inc.

July 2011 M9999-071311-A

**Ordering Information**

| Part Number | Voltage    | Switching Frequency | Junction Temperature<br>Range | Package               | Lead Finish |

|-------------|------------|---------------------|-------------------------------|-----------------------|-------------|

| MIC26901YJL | Adjustable | 600kHz              | −40°C to +125°C               | 28-Pin 5mm × 6mm MLF® | Pb-Free     |

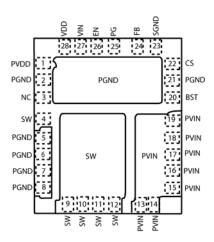

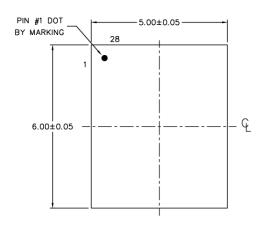

# **Pin Configuration**

28-Pin 5mm  $\times$  6mm MLF<sup>®</sup> (YJL)

# **Pin Description**

| Pin Number               | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | PVDD     | 5V Internal Linear Regulator (Output): PVDD supply is the power MOSFET gate drive supply voltage and created by internal LDO from $V_{IN}$ . When $V_{IN}$ < +5.5V, PVDD should be tied to PVIN pins. A 2.2µF ceramic capacitor from the PVDD pin to PGND (pin 2) must be place next to the IC.                                                                                                                     |

| 3                        | NC       | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4, 9, 10, 11,<br>12      | SW       | Switch Node (Output): Internal connection for the high-side MOSFET source and low-side MOSFET drain. Due to the high speed switching on this pin, the SW pin should be routed away from sensitive nodes.                                                                                                                                                                                                            |

| 2, 5, 6, 7, 8, 21        | PGND     | Power Ground. PGND is the ground path for the MIC26903 buck converter power stage. The PGND pins connect to the low-side N-Channel internal MOSFET gate drive supply ground, the sources of the MOSFETs, the negative terminals of input capacitors, and the negative terminals of output capacitors. The loop for the power ground should be as small as possible and separate from the Signal ground (SGND) loop. |

| 13,14,15,<br>16,17,18,19 | PVIN     | High-Side N-internal MOSFET Drain Connection (Input): The $PV_{IN}$ operating voltage range is from 4.5V to 28V. Input capacitors between the PVIN pins and the power ground (PGND) are required and keep the connection short.                                                                                                                                                                                     |

| 20                       | BST      | Boost (Output): Bootstrapped voltage to the high-side N-channel MOSFET driver. A Schottky diode is connected between the PVDD pin and the BST pin. A boost capacitor of 0.1µF is connected between the BST pin and the SW pin. Adding a small resistor at the BST pin can slow down the turn-on time of high-side N-Channel MOSFETs.                                                                                |

# **Pin Description (Continued)**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | CS       | Current Sense (input): The CS pin senses current by monitoring the voltage across the low-side MOSFET during the OFF-time. The current sensing is necessary for short circuit protection. In order to sense the current accurately, connect the low-side MOSFET drain to SW using a Kelvin connection. The CS pin is also the high-side MOSFET's output driver return. |

| 23         | SGND     | Signal ground. SGND must be connected directly to the ground planes. Do not route the SGND pin to the PGND Pad on the top layer, see PCB layout guidelines for details.                                                                                                                                                                                                |

| 24         | FB       | Feedback (Input): Input to the transconductance amplifier of the control loop. The FB pin is regulated to 0.8V. A resistor divider connecting the feedback to the output is used to adjust the desired output voltage.                                                                                                                                                 |

| 25         | PG       | Power Good (Output): Open Drain Output. The PG pin is externally tied with a resistor to VDD. A high output is asserted when $V_{\text{OUT}} > 92\%$ of nominal.                                                                                                                                                                                                       |

| 26         | EN       | Enable (Input): A logic level control of the output. The EN pin is CMOS-compatible. Logic high = enable, logic low = shutdown. In the off state, supply current of the device is greatly reduced (typically 5µA). The EN pin should not be left open.                                                                                                                  |

| 27         | VIN      | Power Supply Voltage (Input): Requires bypass capacitor to SGND.                                                                                                                                                                                                                                                                                                       |

| 28         | VDD      | 5V Internal Linear Regulator (Output): VDD supply is the power MOSFET gate drive supply voltage and the supply bus for the IC. VDD is created by internal LDO from $V_{IN}$ . When $V_{IN} < +5.5V$ , VDD should be tied to PVIN pins. A 1.0µF ceramic capacitor from the VDD pin to PGND pins must be place next to the IC.                                           |

# Absolute Maximum Ratings<sup>(1,2)</sup>

| PV <sub>IN</sub> to PGND                   | _0 3\/ to +29\/               |

|--------------------------------------------|-------------------------------|

|                                            |                               |

| V <sub>IN</sub> to PGND                    | $-0.3V$ to $PV_{IN}$          |

| PV <sub>DD</sub> , V <sub>DD</sub> to PGND | 0.3V to +6V                   |

| V <sub>SW</sub> , V <sub>CS</sub> to PGND  | $-0.3V$ to $(PV_{IN} + 0.3V)$ |

| V <sub>BST</sub> to V <sub>SW</sub>        | 0.3V to 6V                    |

| V <sub>BST</sub> to PGND                   | 0.3V to 35V                   |

| V <sub>FB</sub> , V <sub>PG</sub> to PGND  | $-0.3V$ to $(V_{DD} + 0.3V)$  |

| V <sub>EN</sub> to PGND                    | $-0.3V$ to $(V_{IN} + 0.3V)$  |

| PGND to SGND                               | 0.3V to +0.3V                 |

| Junction Temperature                       | +150°C                        |

| Storage Temperature (T <sub>S</sub> )      | 65°C to +150°C                |

| Lead Temperature (soldering, 10sec).       | 260°C                         |

|                                            |                               |

# Operating Ratings<sup>(3)</sup>

| Supply Voltage (PV <sub>IN</sub> , V <sub>IN</sub> ) | 4.5V to 28V                                    |

|------------------------------------------------------|------------------------------------------------|

| PVDD, VDD Supply Voltage (PV                         | <sub>DD</sub> , V <sub>DD</sub> ) 4.5V to 5.5V |

| Enable Input (V <sub>EN</sub> )                      | 0V to V <sub>IN</sub>                          |

| Junction Temperature (T <sub>J</sub> )               | 40°C to +125°C                                 |

| Maximum Power Dissipation                            | Note 4                                         |

| Package Thermal Resistance <sup>(4)</sup>            |                                                |

| 5mm x 6mm MLF $^{\mathbb{R}}$ ( $\theta_{JA}$ )      | 28°C/W                                         |

|                                                      |                                                |

# **Electrical Characteristics**(5)

$PV_{IN} = V_{IN} = V_{EN} = 12V, \ V_{BST} - V_{SW} = 5V; \ T_A = 25^{\circ}C, \ unless \ noted. \ \textbf{Bold} \ values \ indicate \ -40^{\circ}C \leq T_J \leq +125^{\circ}C.$

| Parameter                                                 | Condition                                            | Min.  | Тур. | Max.  | Units |

|-----------------------------------------------------------|------------------------------------------------------|-------|------|-------|-------|

| Power Supply Input                                        |                                                      |       |      |       |       |

| Input Voltage Range (V <sub>IN</sub> , PV <sub>IN</sub> ) |                                                      | 4.5   |      | 28    | V     |

| Quiescent Supply Current                                  | V <sub>FB</sub> = 1.5V (non-switching)               |       | 730  | 1500  | μΑ    |

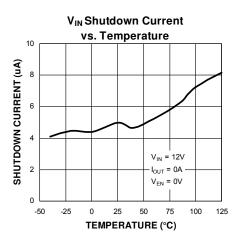

| Shutdown Supply Current                                   | V <sub>EN</sub> = 0V                                 |       | 5    | 10    | μΑ    |

| V <sub>DD</sub> Supply Voltage                            |                                                      | ·     |      |       |       |

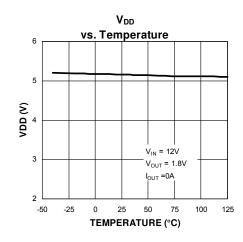

| V <sub>DD</sub> Output Voltage                            | V <sub>IN</sub> = 7V to 28V, I <sub>DD</sub> = 40mA  | 4.8   | 5    | 5.4   | V     |

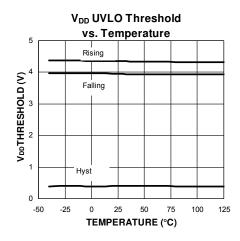

| V <sub>DD</sub> UVLO Threshold                            | V <sub>DD</sub> Rising                               | 3.7   | 4.2  | 4.5   | V     |

| V <sub>DD</sub> UVLO Hysteresis                           |                                                      |       | 400  |       | mV    |

| Dropout Voltage (V <sub>IN</sub> – V <sub>DD</sub> )      | $I_{DD} = 25\text{mA}$                               |       | 380  | 600   | mV    |

| DC-DC Controller                                          |                                                      |       |      |       |       |

| Output-Voltage Adjust Range (Vout)                        |                                                      | 0.8   |      | 5.5   | ٧     |

| Reference                                                 |                                                      |       |      |       |       |

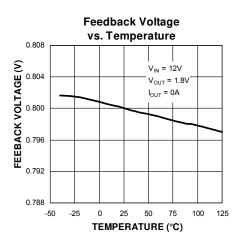

|                                                           | $0^{\circ}C \le T_{J} \le 85^{\circ}C \ (\pm 1.0\%)$ | 0.792 | 0.8  | 0.808 | V     |

|                                                           | -40°C ≤ T <sub>J</sub> ≤ 125°C (±1.5%)               | 0.788 | 0.8  | 0.812 | ľ     |

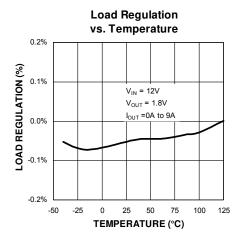

| Load Regulation                                           | I <sub>OUT</sub> = 0A to 9A (Continuous Mode)        |       | 0.25 |       | %     |

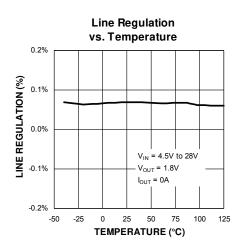

| Line Regulation                                           | V <sub>IN</sub> = 4.5V to 28V                        |       | 0.25 |       | %     |

| FB Bias Current                                           | V <sub>FB</sub> = 0.8V                               |       | 50   |       | nA    |

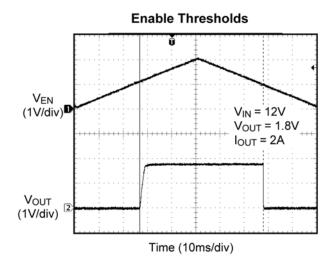

| Enable Control                                            |                                                      |       |      |       |       |

| EN Logic Level High                                       |                                                      | 1.8   |      |       | V     |

| EN Logic Level Low                                        |                                                      |       |      | 0.6   | V     |

| EN Bias Current                                           | V <sub>EN</sub> = 12V                                |       | 6    | 30    | μA    |

| Oscillator                                                |                                                      |       |      |       |       |

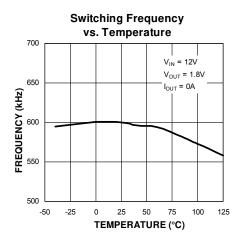

| Switching Frequency (6)                                   | V <sub>FB</sub> = 0V                                 | 450   | 600  | 750   | kHz   |

| Maximum Duty Cycle (7)                                    | V <sub>FB</sub> = 1.0V                               |       | 82   |       | %     |

| Minimum Duty Cycle                                        |                                                      |       | 0    |       | %     |

| Minimum Off-Time                                          |                                                      |       | 300  |       | Ns    |

# Electrical Characteristics<sup>(5)</sup> (Continued)

$PV_{IN} = V_{IN} = V_{EN} = 12V$ ,  $V_{BST} - V_{SW} = 5V$ ;  $T_A = 25^{\circ}C$ , unless noted. **Bold** values indicate -40°C  $\leq T_J \leq +125^{\circ}C$ .

| Parameter                               | Condition                                            | Min.  | Тур. | Max. | Units             |

|-----------------------------------------|------------------------------------------------------|-------|------|------|-------------------|

| Soft-Start                              |                                                      |       |      |      |                   |

| Soft-Start time                         |                                                      |       | 5    |      | ms                |

| Short-Circuit Protection                |                                                      |       |      |      |                   |

| Current-Limit Threshold                 | V <sub>FB</sub> = 0.8V, T <sub>J</sub> = 25°C        | 12.5  | 15   | 20   | Α                 |

| Current-Limit Threshold                 | V <sub>FB</sub> = 0.8V, T <sub>J</sub> = 125°C       | 11.25 | 15   | 20   | Α                 |

| Short-Circuit Current                   | V <sub>FB</sub> = 0V                                 |       | 4    |      | Α                 |

| Internal FETs                           |                                                      |       |      |      |                   |

| Top-MOSFET R <sub>DS (ON)</sub>         | I <sub>SW</sub> = 3A                                 |       | 27   |      | mΩ                |

| Bottom-MOSFET R <sub>DS (ON)</sub>      | I <sub>SW</sub> = 3A                                 |       | 10.5 |      | mΩ                |

| SW Leakage Current                      | V <sub>EN</sub> = 0V                                 |       |      | 60   | μA                |

| V <sub>IN</sub> Leakage Current         | V <sub>EN</sub> = 0V                                 |       |      | 25   | μA                |

| Power Good (PG)                         | •                                                    | ·     |      |      |                   |

| PG Threshold Voltage                    | Sweep V <sub>FB</sub> from Low to High               | 85    | 92   | 95   | %V <sub>OUT</sub> |

| PG Hysteresis                           | Sweep V <sub>FB</sub> from High to Low               |       | 5.5  |      | %V <sub>OUT</sub> |

| PG Delay Time                           | Sweep V <sub>FB</sub> from Low to High               |       | 100  |      | μs                |

| PG Low Voltage                          | Sweep $V_{FB} < 0.9 \times V_{NOM}$ , $I_{PG}$ = 1mA |       | 70   | 200  | mV                |

| Thermal Protection                      |                                                      |       |      |      |                   |

| Over-Temperature Shutdown               | $T_JRising$                                          |       | 160  |      | °C                |

| Over-Temperature Shutdown<br>Hysteresis |                                                      |       | 15   |      | °C                |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

- 3. The device is not guaranteed to function outside operating range.

- 4.  $PD_{(MAX)} = (T_{J(MAX)} T_A)/\theta_{JA}$ , where  $\theta_{JA}$  depends upon the printed circuit layout. A 5 square inch 4 layer, 0.62", FR-4 PCB with 2oz finish copper weight per layer is used for the  $\theta_{JA}$ .

- 5. Specification for packaged product only.

- 6. Measured in test mode.

- 7. The maximum duty-cycle is limited by the fixed mandatory off-time  $t_{\text{OFF}}$  of typically 300ns.

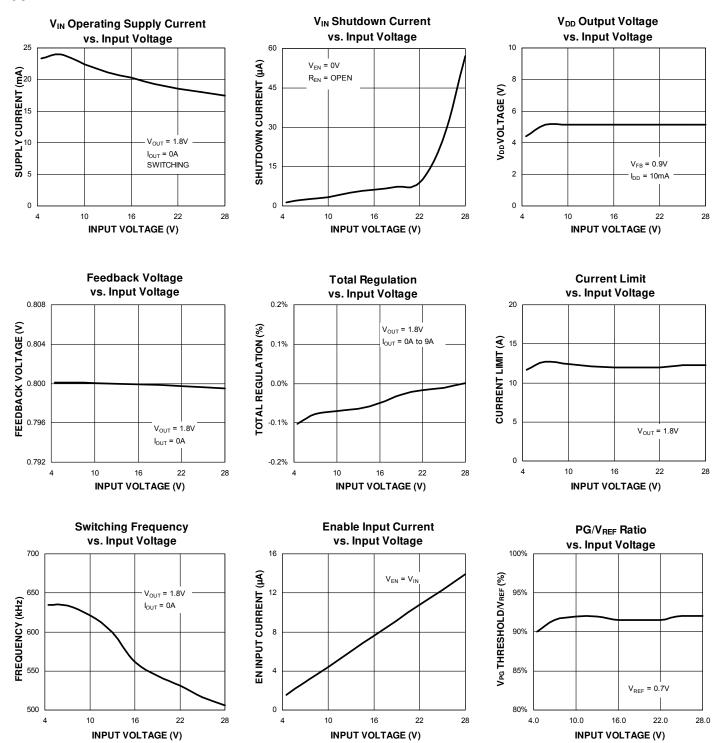

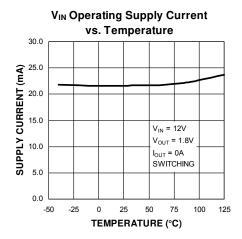

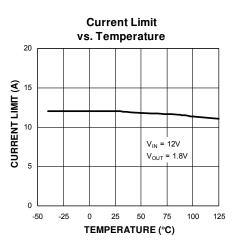

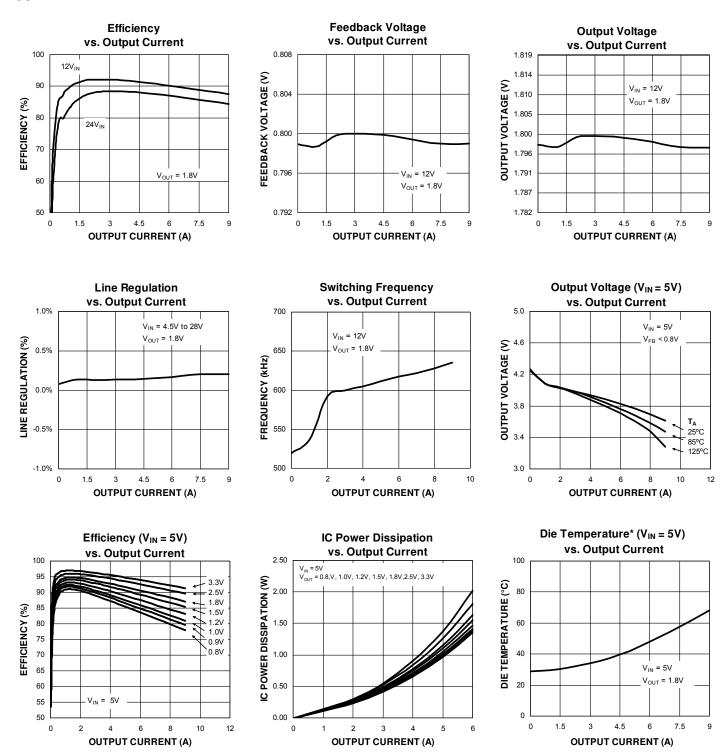

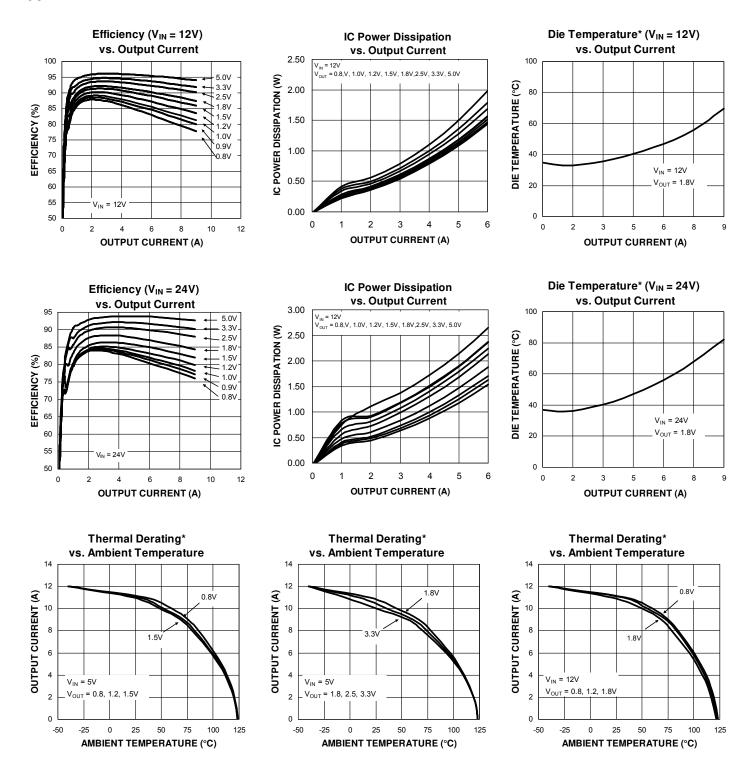

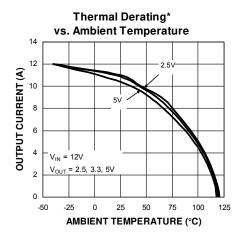

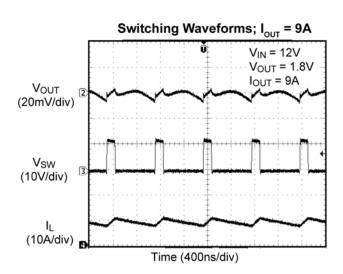

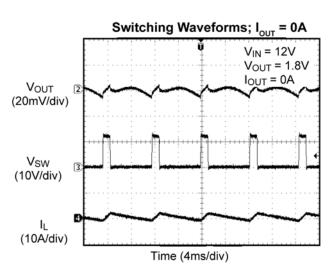

# **Typical Characteristics**

# **Typical Characteristics (Continued)**

# **Typical Characteristics (Continued)**

# **Typical Characteristics (Continued)**

# **Typical Characteristics (Continued)**

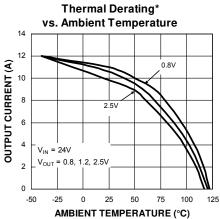

**Die Temperature\***: The temperature measurement was taken at the hottest point on the MIC26901 case mounted on a 5 square inch 4 layer, 0.62", FR-4 PCB with 2oz finish copper weight per layer, see Thermal Measurement section. Actual results will depend upon the size of the PCB, ambient temperature and proximity to other heat emitting components.

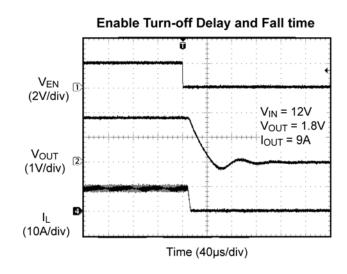

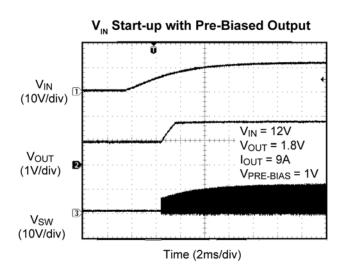

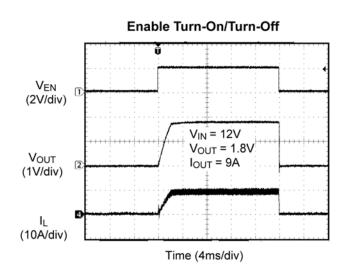

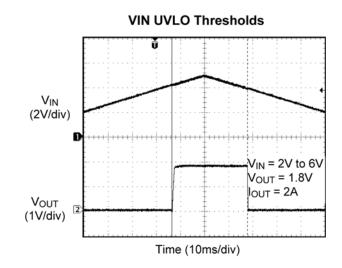

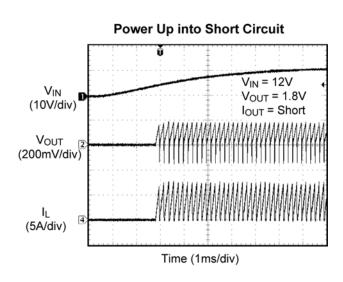

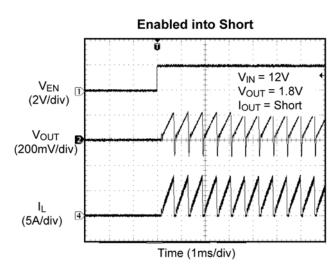

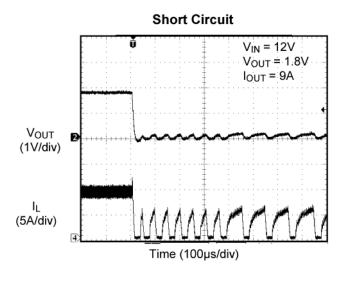

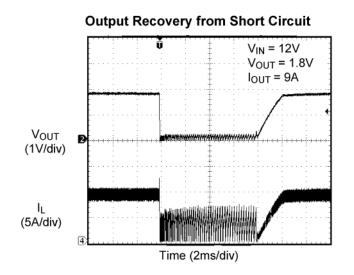

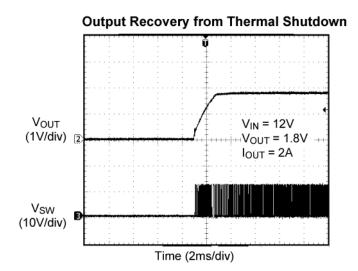

### **Functional Characteristics**

# **Functional Characteristics (Continued)**

# **Functional Characteristics (Continued)**

# Vout (1V/div) Vin = 12V Vout = 1.8V Time (40ms/div)

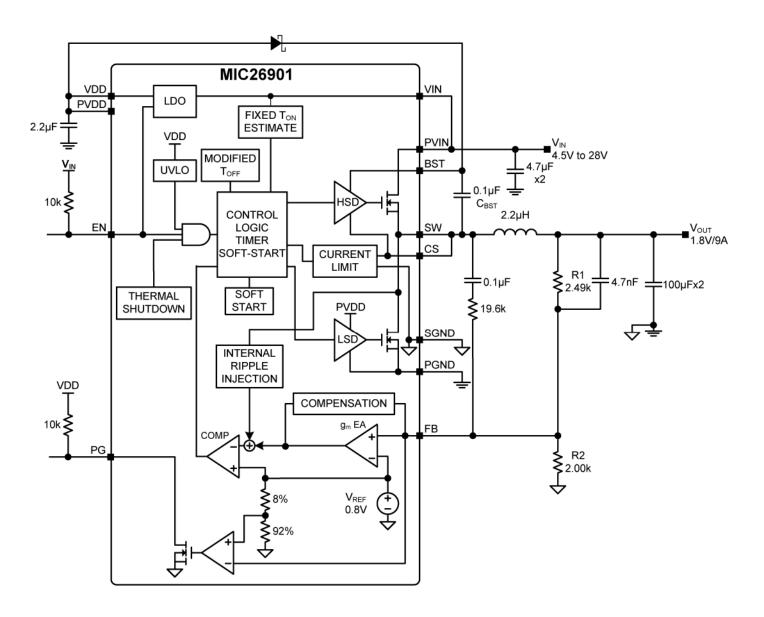

# **Functional Diagram**

Figure 1. MIC26901 Block Diagram

## **Functional Description**

The MIC26901 is an adaptive ON-time synchronous step-down DC/DC regulator with an internal 5V linear regulator and a Power Good (PG) output. It is designed to operate over a wide input voltage range from 4.5V to 28V and provides a regulated output voltage at up to 7A of output current. An adaptive ON-time control scheme is employed in to obtain a constant switching frequency and to simplify the control compensation. Over-current protection is implemented without the use of an external sense resistor. The device includes an internal soft-start function which reduces the power supply input surge current at start-up by controlling the output voltage rise time.

#### **Theory of Operation**

The MIC26901 operates in a continuous mode as shown in Figure 1.

#### **Continuous Mode**

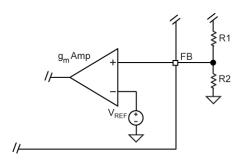

In continuous mode, the output voltage is sensed by the MIC26901 feedback pin FB via the voltage divider R1 and R2, and compared to a 0.8V reference voltage  $V_{\text{REF}}$  at the error comparator through a low gain transconductance  $(g_{\text{m}})$  amplifier. If the feedback voltage decreases and the output of the  $g_{\text{m}}$  amplifier is below 0.8V, then the error comparator will trigger the control logic and generate an ON-time period. The ON-time period length is predetermined by the "FIXED  $t_{\text{ON}}$  ESTIMATION" circuitry:

$$t_{ON(estimated)} = \frac{V_{OUT}}{V_{IN} \times 600 kHz}$$

Eq. 1

where  $V_{\text{OUT}}$  is the output voltage and  $V_{\text{IN}}$  is the power stage input voltage.

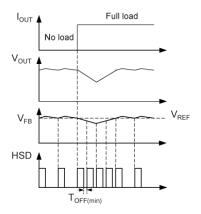

At the end of the ON-time period, the internal high-side driver turns off the high-side MOSFET and the low-side driver turns on the low-side MOSFET. The OFF-time period length depends upon the feedback voltage in most cases. When the feedback voltage decreases and the output of the  $g_m$  amplifier is below 0.8V, the ON-time period is triggered and the OFF-time period ends. If the OFF-time period determined by the feedback voltage is less than the minimum OFF-time  $t_{\rm OFF(min)}$ , which is about 300ns, the MIC26901 control logic will apply the  $t_{\rm OFF(min)}$  instead.  $t_{\rm OFF(min)}$  is required to maintain enough energy in the boost capacitor ( $C_{\rm BST}$ ) to drive the high-side MOSFET.

The maximum duty cycle is obtained from the 300ns  $t_{\mathsf{OFF}(\mathsf{min})}\!\!:$

$$D_{\text{max}} = \frac{t_{\text{S}} - t_{\text{OFF(min)}}}{t_{\text{S}}} = 1 - \frac{300 \text{ns}}{t_{\text{S}}}$$

Eq. 2

where  $t_S = 1/600 \text{kHz} = 1.66 \mu \text{s}$ .

It is not recommended to use MIC26901 with a OFF-time close to  $t_{\text{OFF}(\text{min})}$  during steady-state operation. Also, as  $V_{\text{OUT}}$  increases, the internal ripple injection will increase and reduce the line regulation performance. Therefore, the maximum output voltage of the MIC26901 should be limited to 5.5V and the maximum external ripple injection should be limited to 200mV. Please refer to "Setting Output Voltage" subsection in *Application Information* for more details.

The actual ON-time and resulting switching frequency will vary with the part-to-part variation in the rise and fall times of the internal MOSFETs, the output load current, and variations in the  $V_{\text{DD}}$  voltage. Also, the minimum  $t_{\text{ON}}$  results in a lower switching frequency in high  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  applications, such as 24V to 1.0V. The minimum  $t_{\text{ON}}$  measured on the MIC26901 evaluation board is about 100ns. During load transients, the switching frequency is changed due to the varying OFF-time.

To illustrate the control loop operation, we will analyze both the steady-state and load transient scenarios.

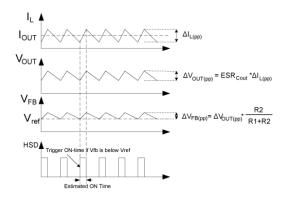

Figure 2 shows the MIC26901 control loop timing during steady-state operation. During steady-state, the  $g_m$  amplifier senses the feedback voltage ripple, which is proportional to the output voltage ripple and the inductor current ripple, to trigger the ON-time period. The ON-time is predetermined by the  $t_{\rm ON}$  estimator. The termination of the OFF-time is controlled by the feedback voltage. At the valley of the feedback voltage ripple, which occurs when  $V_{\rm FB}$  falls below  $V_{\rm REF}$ , the OFF period ends and the next ON-time period is triggered through the control logic circuitry.

Figure 2. MIC26901 Control Loop Timing

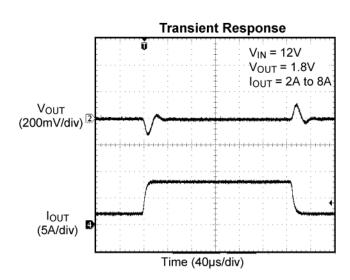

Figure 3 shows the operation of the MIC26901 during a load transient. The output voltage drops due to the sudden load increase, which causes the  $V_{\text{FB}}$  to be less than  $V_{\text{REF}}.$  This will cause the error comparator to trigger an ON-time period. At the end of the ON-time period, a minimum OFF-time  $t_{\text{OFF}(\text{min})}$  is generated to charge  $C_{\text{BST}}$  since the feedback voltage is still below  $V_{\text{REF}}.$  Then, the next ON-time period is triggered due to the low feedback voltage. Therefore, the switching frequency changes during the load transient, but returns to the nominal fixed frequency once the output has stabilized at the new load current level. With the varying duty cycle and switching frequency, the output recovery time is fast and the output voltage deviation is small in MIC26901 converter.

Figure 3. MIC26901 Load Transient Response

Unlike true current-mode control, the MIC26901 uses the output voltage ripple to trigger an ON-time period. The output voltage ripple is proportional to the inductor current ripple if the ESR of the output capacitor is large enough. The MIC26901 control loop has the advantage of eliminating the need for slope compensation.

In order to meet the stability requirements, the MIC26901 feedback voltage ripple should be in phase with the inductor current ripple and large enough to be sensed by the  $g_m$  amplifier and the error comparator. The recommended feedback voltage ripple is  $20\text{mV}\sim100\text{mV}$ . If a low-ESR output capacitor is selected, then the feedback voltage ripple may be too small to be sensed by the  $g_m$  amplifier and the error comparator. Also, the output voltage ripple and the feedback voltage ripple are not necessarily in phase with the inductor current ripple if the ESR of the output capacitor is very low. In these cases, ripple injection is required to ensure proper operation. Please refer to "Ripple Injection" subsection in *Application Information* for more details about the ripple injection technique.

#### **V<sub>DD</sub>** Regulator

The MIC26901 provides a 5V regulated output for input voltage  $V_{\text{IN}}$  ranging from 5.5V to 28V. When  $V_{\text{IN}}$  < 5.5V,  $V_{\text{DD}}$  should be tied to PVIN pins to bypass the internal linear regulator.

#### **Soft-Start**

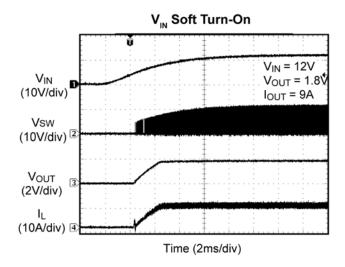

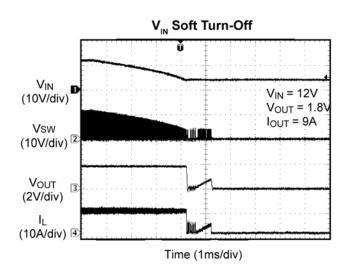

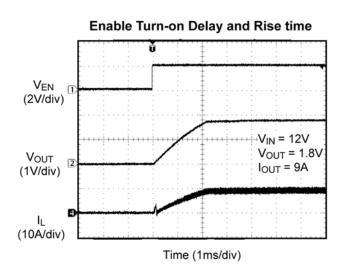

Soft-start reduces the power supply input surge current at startup by controlling the output voltage rise time. The input surge appears while the output capacitor is charged up. A slower output rise time will draw a lower input surge current.

The MIC26901 implements an internal digital soft-start by making the 0.8V reference voltage  $V_{REF}$  ramp from 0 to 100% in about 6ms with 9.7mV steps. Therefore, the output voltage is controlled to increase slowly by a staircase  $V_{FB}$  ramp. Once the soft-start cycle ends, the related circuitry is disabled to reduce current consumption.  $V_{DD}$  must be powered up at the same time or after  $V_{IN}$  to make the soft-start function correctly.

#### **Current Limit**

The MIC26901 uses the  $R_{DS(ON)}$  of the internal low-side power MOSFET to sense over-current conditions. This method will avoid adding cost, board space and power losses taken by a discrete current sense resistor. The low-side MOSFET is used because it displays much lower parasitic oscillations during switching than the high-side MOSFET.

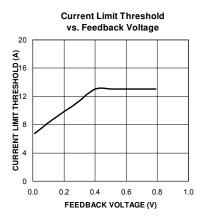

In each switching cycle of the MIC26901 converter, the inductor current is sensed by monitoring the low-side MOSFET in the OFF period. If the peak inductor current is greater than 15A, then the MIC26901 turns off the high-side MOSFET and a soft-start sequence is triggered. This mode of operation is called "hiccup mode" and its purpose is to protect the downstream load in case of a hard short. The load current-limit threshold has a foldback characteristic related to the feedback voltage as shown in Figure 4.

Figure 4. MIC26901 Current-Limit Foldback Characteristic

#### Power Good (PG)

The Power Good (PG) pin is an open drain output which indicates logic high when the output is nominally 92% of its steady state voltage. A pull-up resistor of more than  $10k\Omega$  should be connected from PG to VDD.

#### **MOSFET Gate Drive**

The Block Diagram (Figure 1) shows a bootstrap circuit, consisting of D1 (a Schottky diode is recommended) and C<sub>BST</sub>. This circuit supplies energy to the high-side drive circuit. Capacitor  $C_{\text{BST}}$  is charged, while the low-side MOSFET is on, and the voltage on the SW pin is approximately 0V. When the high-side MOSFET driver is turned on, energy from C<sub>BST</sub> is used to turn the MOSFET on. As the high-side MOSFET turns on, the voltage on the SW pin increases to approximately V<sub>IN</sub>. Diode D1 is reverse biased and C<sub>BST</sub> floats high while continuing to keep the high-side MOSFET on. The bias current of the high-side driver is less than 10mA so a 0.1µF to 1µF is sufficient to hold the gate voltage with minimal droop for the power stroke (high-side switching) cycle, i.e.  $\Delta BST =$  $10mA \times 1.67\mu s/0.1\mu F = 167mV$ . When the low-side MOSFET is turned back on, CBST is recharged through D1. A small resistor R<sub>G</sub>, which is in series with C<sub>BST</sub>, can be used to slow down the turn-on time of the high-side N-channel MOSFET.

The drive voltage is derived from the  $V_{DD}$  supply voltage. The nominal low-side gate drive voltage is  $V_{DD}$  and the nominal high-side gate drive voltage is approximately  $V_{DD}-V_{DIODE}$ , where  $V_{DIODE}$  is the voltage drop across D1. An approximate 30ns delay between the high-side and low-side driver transitions is used to prevent current from simultaneously flowing unimpeded through both MOSFETs.

## **Application Information**

#### **Inductor Selection**

Values for inductance, peak, and RMS currents are required to select the output inductor. The input and output voltages and the inductance value determine the peak-to-peak inductor ripple current. Generally, higher inductance values are used with higher input voltages. Larger peak-to-peak ripple currents will increase the power dissipation in the inductor and MOSFETs. Larger output ripple currents will also require more output capacitance to smooth out the larger ripple current. Smaller peak-to-peak ripple currents require a larger inductance value and therefore a larger and more expensive inductor. A good compromise between size, loss and cost is to set the inductor ripple current to be equal to 20% of the maximum output current. The inductance value is calculated by Equation 3:

$$L = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times f_{sw} \times 20\% \times I_{OUT(max)}}$$

Eq. 3

where:

$f_{SW}$  = switching frequency, 600kHz 20% = ratio of AC ripple current to DC output current  $V_{IN(max)}$  = maximum power stage input voltage The peak-to-peak inductor current ripple is:

$$\Delta I_{L(pp)} = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times f_{sw} \times L}$$

Eq. 4

The peak inductor current is equal to the average output current plus one half of the peak-to-peak inductor current ripple.

$$I_{L(pk)} = I_{OUT(max)} + 0.5 \times \Delta I_{L(pp)}$$

Eq. 5

The RMS inductor current is used to calculate the I<sup>2</sup>R losses in the inductor.

$$I_{L(RMS)} = \sqrt{I_{OUT(max)}^2 + \frac{\Delta I_{L(PP)}^2}{12}}$$

Eq.6

Maximizing efficiency requires the proper selection of core material and minimizing the winding resistance. The high frequency operation of the MIC26901 requires the use of ferrite materials for all but the most cost sensitive applications. Lower cost iron powder cores may be used but the increase in core loss will reduce the efficiency of the power supply. This is especially noticeable at low output power. The winding resistance decreases efficiency at the higher output current levels. The winding resistance must be minimized although this usually comes at the expense of a larger inductor. The power dissipated in the inductor is equal to the sum of the core and copper losses. At higher output loads, the core losses are usually insignificant and can be ignored. At lower output currents, the core losses can be a significant contributor. Core loss information is usually available from the magnetics vendor. Copper loss in the inductor is calculated by Equation 7:

$$P_{INDUCTOR(Cu)} = I_{L(RMS)}^{2} \times R_{WINDING}$$

Eq. 7

The resistance of the copper wire,  $R_{WINDING}$ , increases with the temperature. The value of the winding resistance used should be at the operating temperature.

$$P_{WINDING(Ht)} = R_{WINDING(20^{\circ}C)} \times (1 + 0.0042 \times (T_H - T_{20^{\circ}C}))$$

Eq. 8

where

T<sub>H</sub> = temperature of wire under full load

$T_{20^{\circ}C}$  = ambient temperature

$R_{WINDING(20^{\circ}C)}$  = room temperature winding resistance (usually specified by the manufacturer)

#### **Output Capacitor Selection**

The type of the output capacitor is usually determined by its equivalent series resistance (ESR). Voltage and RMS current capability are two other important factors for selecting the output capacitor. Recommended capacitor types are ceramic, low-ESR aluminum electrolytic, OS-CON and POSCAP. The output capacitor's ESR is usually the main cause of the output ripple. The output capacitor ESR also affects the control loop from a stability point of view.

The maximum value of ESR is calculated:

$$\mathsf{ESR}_{\mathsf{C}_{\mathsf{OUT}}} \leq \frac{\Delta \mathsf{V}_{\mathsf{OUT}(\mathsf{pp})}}{\Delta \mathsf{I}_{\mathsf{L}(\mathsf{PP})}} \qquad \qquad \mathsf{Eq. 9}$$

where:

$\Delta V_{OUT(pp)}$  = peak-to-peak output voltage ripple

$\Delta I_{L(PP)}$  = peak-to-peak inductor current ripple

The total output ripple is a combination of the ESR and output capacitance. The total ripple is calculated in Equation 10:

$$\Delta V_{OUT(pp)} = \sqrt{\left(\frac{\Delta I_{L(PP)}}{C_{OUT} \times f_{SW} \times 8}\right)^2 + \left(\Delta I_{L(PP)} \times ESR_{C_{OUT}}\right)^2}$$

Eq. 10

where:

D = duty cycle

C<sub>OUT</sub> = output capacitance value

f<sub>SW</sub> = switching frequency

As described in the "Theory of Operation" subsection in the *Functional Description* section, the MIC26901 requires at least 20mV peak-to-peak ripple at the FB pin to make the  $g_m$  amplifier and the error comparator behave properly. Also, the output voltage ripple should be in phase with the inductor current. Therefore, the output voltage ripple caused by the output capacitors value should be much smaller than the ripple caused by the output capacitor ESR. If low-ESR capacitors, such as ceramic capacitors, are selected as the output capacitors, a ripple injection method should be applied to provide the enough feedback voltage ripple. Please refer to the "Ripple Injection" subsection for more details.

The voltage rating of the capacitor should be twice the output voltage for a tantalum and 20% greater for aluminum electrolytic or OS-CON. The output capacitor RMS current is calculated in Equation 11:

$$I_{C_{OUT}(RMS)} = \frac{\Delta I_{L(PP)}}{\sqrt{12}}$$

Eq. 11

The power dissipated in the output capacitor is:

$$P_{DISS(C_{OUT})} = I_{C_{OUT}(RMS)}^{2} \times ESR_{C_{OUT}}$$

Eq. 12

#### **Input Capacitor Selection**

The input capacitor for the power stage input  $V_{\text{IN}}$  should be selected for ripple current rating and voltage rating. Tantalum input capacitors may fail when subjected to high inrush currents, caused by turning the input supply on. A tantalum input capacitor's voltage rating should be at least two times the maximum input voltage to maximize reliability. Aluminum electrolytic, OS-CON, and multilayer polymer film capacitors can handle the higher inrush currents without voltage de-rating. The input voltage ripple will primarily depend on the input capacitor's ESR. The peak input current is equal to the peak inductor current, so:

$$\Delta V_{IN} = I_{L(pk)} \times ESR_{CIN}$$

Eq. 13

The input capacitor must be rated for the input current ripple. The RMS value of input capacitor current is determined at the maximum output current. Assuming the peak-to-peak inductor current ripple is low:

$$I_{\text{CIN(RMS)}} \approx I_{\text{OUT(max)}} \times \sqrt{D \times (1-D)}$$

Eq. 14

The power dissipated in the input capacitor is:

$$P_{DISS(CIN)} = I_{CIN(RMS)}^2 \times ESR_{CIN}$$

Eq. 15

#### Ripple Injection

The  $V_{FB}$  ripple required for proper operation of the MIC26901  $g_m$  amplifier and error comparator is 20mV to 100mV. However, the output voltage ripple is generally designed as 1% to 2% of the output voltage. For a low output voltage, such as a 1V, the output voltage ripple is only 10mV to 20mV, and the feedback voltage ripple is less than 20mV. If the feedback voltage ripple is so small that the  $g_m$  amplifier and error comparator can't sense it, then the MIC26901 will lose control and the output voltage is not regulated. In order to have some amount of  $V_{FB}$  ripple, a ripple injection method is applied for low output voltage ripple applications.

The applications are divided into three situations according to the amount of the feedback voltage ripple:

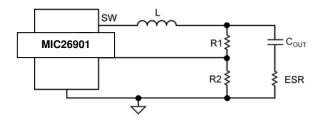

Enough ripple at the feedback voltage due to the large ESR of the output capacitors.

As shown in Figure 5a, the converter is stable without any ripple injection. The feedback voltage ripple is:

$$\Delta V_{FB(pp)} = \frac{R2}{R1 + R2} \times ESR_{C_{OUT}} \times \Delta I_{L(pp)}$$

Eq. 16

where  $\Delta I_{L(pp)}$  is the peak-to-peak value of the inductor current ripple.

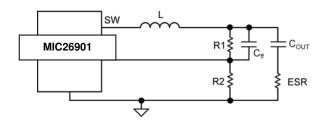

Inadequate ripple at the feedback voltage due to the small ESR of the output capacitors.

The output voltage ripple is fed into the FB pin through a feedforward capacitor  $C_{\rm ff}$  in this situation, as shown in Figure 5b. The typical  $C_{\rm ff}$  value is between 1nF and 100nF. With the feedforward capacitor, the feedback voltage ripple is very close to the output voltage ripple:

$$\Delta V_{FB(pp)} \approx ESR \times \Delta I_{L(pp)}$$

Eq. 17

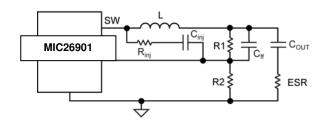

Virtually no ripple at the FB pin voltage due to the very-low ESR of the output capacitors.

Figure 5a. Enough Ripple at FB

Figure 5b. Inadequate Ripple at FB

Figure 5c. Invisible Ripple at FB

In this situation, the output voltage ripple is less than 20mV. Therefore, additional ripple is injected into the FB pin from the switching node SW via a resistor  $R_{\text{inj}}$  and a capacitor  $C_{\text{inj}}$ , as shown in Figure 5c. The injected ripple is:

$$\Delta V_{FB(pp)} = V_{IN} \times K_{div} \times D \times (1-D) \times \frac{1}{f_{SW} \times \tau}$$

Eq. 18

$$K_{div} = \frac{R1//R2}{R_{ini} + R1//R2}$$

Eq. 19

where:

V<sub>IN</sub> = Power stage input voltage

D = duty cycle

f<sub>SW</sub> = switching frequency

$$\tau = (R1//R2//R_{ini}) \times C_{ff}$$

In Equations 21 and 22, it is assumed that the time constant associated with  $C_{\rm ff}$  must be much greater than the switching period:

$$\frac{1}{f_{SW} \times \tau} = \frac{T}{\tau} \ll 1$$

Eq. 20

If the voltage divider resistors R1 and R2 are in the  $k\Omega$  range, a  $C_{ff}$  of 1nF to 100nF can easily satisfy the large time constant requirements. Also, a 100nF injection capacitor  $C_{inj}$  is used in order to be considered as short for a wide range of the frequencies.

The process of sizing the ripple injection resistor and capacitors is:

**Step 1.** Select  $C_{\rm ff}$  to feed all output ripples into the feedback pin and make sure the large time constant assumption is satisfied. Typical choice of  $C_{\rm ff}$  is 1nF to 100nF if R1 and R2 are in  $k\Omega$  range.

**Step 2.** Select R<sub>inj</sub> according to the expected feedback voltage ripple using Equation 22:

$$K_{div} = \frac{\Delta V_{FB(pp)}}{V_{IN}} \times \frac{f_{SW} \times \tau}{D \times (1-D)}$$

Eq. 21

Then the value of R<sub>ini</sub> is obtained as:

$$R_{inj} = (R1//R2) \times (\frac{1}{K_{div}} - 1)$$

Eq. 22

**Step 3.** Select C<sub>inj</sub> as 100nF, which could be considered as short for a wide range of the frequencies.

#### **Setting Output Voltage**

The MIC26603 requires two resistors to set the output voltage as shown in Figure 7.

The output voltage is determined by Equation 23:

$$V_{OUT} = V_{FB} \times (1 + \frac{R1}{R2})$$

Eq. 23

where  $V_{FB} = 0.8V$ .

A typical value of R1 can be between  $3k\Omega$  and  $10k\Omega$ . If R1 is too large, it may allow noise to be introduced into the voltage feedback loop. If R1 is too small, it will decrease the efficiency of the power supply, especially at light loads. Once R1 is selected, R2 can be calculated using:

$$R2 = \frac{V_{FB} \times R1}{V_{OUT} - V_{FB}}$$

Eq. 24

Figure 6. Voltage-Divider Configuration

In addition to the external ripple injection added at the FB pin, internal ripple injection is added at the inverting input of the comparator inside the MIC26901, as shown in Figure 8. The inverting input voltage  $V_{\text{INJ}}$  is clamped to 1.2V. As  $V_{\text{OUT}}$  is increased, the swing of  $V_{\text{INJ}}$  will be clamped. The clamped  $V_{\text{INJ}}$  reduces the line regulation because it is reflected as a DC error on the FB terminal. Therefore, the maximum output voltage of the MIC26901 should be limited to 5.5V to avoid this problem.

Figure 7. Internal Ripple Injection

#### **Thermal Measurements**

Measuring the IC's case temperature is recommended to insure it is within its operating limits. Although this might seem like a very elementary task, it is easy to get erroneous results. The most common mistake is to use the standard thermal couple that comes with a thermal meter. This thermal couple wire gauge is large, typically 22 gauge, and behaves like a heatsink, resulting in a lower case measurement.

Two methods of temperature measurement are using a smaller thermal couple wire or an infrared thermometer. If a thermal couple wire is used, it must be constructed of 36 gauge wire or higher then (smaller wire size) to minimize the wire heat-sinking effect. In addition, the thermal couple tip must be covered in either thermal grease or thermal glue to make sure that the thermal couple junction is making good contact with the case of the IC. Omega brand thermal couple (5SC-TT-K-36-36) is adequate for most applications.

Wherever possible, an infrared thermometer is recommended. The measurement spot size of most infrared thermometers is too large for an accurate reading on a small form factor ICs. However, an IR thermometer from Optris has a 1mm spot size, which makes it a good choice for measuring the hottest point on the case. An optional stand makes it easy to hold the beam on the IC for long periods of time.

## **PCB Layout Guidelines**

# Warning!!! To minimize EMI and output noise, follow these layout recommendations.

PCB Layout is critical to achieve reliable, stable and efficient performance. A ground plane is required to control EMI and minimize the inductance in power, signal and return paths.

The following guidelines should be followed to insure proper operation of the MIC26901 regulator.

#### IC

- A 2.2µF ceramic capacitor, which is connected to the PVDD pin, must be located right at the IC. The PVDD pin is very noise sensitive and placement of the capacitor is very critical. Use wide traces to connect to the PVDD and PGND pins.

- A 1.0uF ceramic capacitor must be placed right between VDD and the signal ground SGND. The SGND must be connected directly to the ground planes. Do not route the SGND pin to the PGND Pad on the top layer.

- Place the IC close to the point-of-load (POL).

- Use fat traces to route the input and output power lines.

- Signal and power grounds should be kept separate and connected at only one location.

#### **Input Capacitor**

- Place the input capacitor next.

- Place the input capacitors on the same side of the board and as close to the IC as possible.

- Keep both the PVIN pin and PGND connections short

- Place several vias to the ground plane close to the input capacitor ground terminal.

- Use either X7R or X5R dielectric input capacitors.

Do not use Y5V or Z5U type capacitors.

- Do not replace the ceramic input capacitor with any other type of capacitor. Any type of capacitor can be placed in parallel with the input capacitor.

- If a Tantalum input capacitor is placed in parallel with the input capacitor, it must be recommended for switching regulator applications and the operating voltage must be derated by 50%.

- In "Hot-Plug" applications, a Tantalum or Electrolytic bypass capacitor must be used to limit the overvoltage spike seen on the input supply with power is suddenly applied.

#### Inductor

- Keep the inductor connection to the switch node (SW) short.

- Do not route any digital lines underneath or close to the inductor.

- Keep the switch node (SW) away from the feedback (FB) pin.

- The CS pin should be connected directly to the SW pin to accurate sense the voltage across the lowside MOSFET.

- To minimize noise, place a ground plane underneath the inductor.

- The inductor can be placed on the opposite side of the PCB with respect to the IC. It does not matter whether the IC or inductor is on the top or bottom as long as there is enough air flow to keep the power components within their temperature limits. The input and output capacitors must be placed on the same side of the board as the IC.

#### **Output Capacitor**

- Use a wide trace to connect the output capacitor ground terminal to the input capacitor ground terminal.

- Phase margin will change as the output capacitor value and ESR changes. Contact the factory if the output capacitor is different from what is shown in the BOM.

- The feedback trace should be separate from the power trace and connected as close as possible to the output capacitor. Sensing a long high current load trace can degrade the DC load regulation.

#### **Optional RC Snubber**

Place the RC snubber on either side of the board and as close to the SW pin as possible.

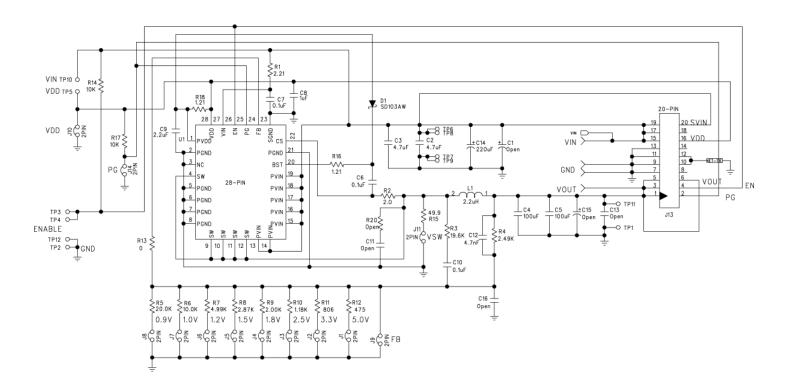

## **Evaluation Board Schematic**

Figure 8. Schematic of MIC26901 Evaluation Board (J11, R13, R15 are for testing purposes)

# **Bill of Materials**

| Item         | Part Number        | Manufacturer                   | Description                                   | Qty. |

|--------------|--------------------|--------------------------------|-----------------------------------------------|------|

| C1           | Open               |                                |                                               |      |

|              | 12105C475KAZ2A     | AVX <sup>(1)</sup>             |                                               |      |

| C2, C3       | GRM32ER71H475KA88L | Murata <sup>(2)</sup>          | 4.7μF Ceramic Capacitor, X7R, Size 1210, 50V  | 2    |

|              | C3225X7R1H475K     | TDK <sup>(3)</sup>             |                                               |      |

| C13, C15     | Open               |                                |                                               |      |

|              | 12106D107MAT2A     | AVX <sup>(1)</sup>             |                                               |      |

| C4, C5       | GRM32ER60J107ME20L | Murata <sup>(2)</sup>          | 100µF Ceramic Capacitor, X5R, Size 1210, 6.3V | 3    |

|              | C3225X5R0J107M     | TDK <sup>(3)</sup>             |                                               |      |

|              | 06035C104KAT2A     | AVX <sup>(1)</sup>             |                                               |      |

| C6, C7, C10  | GRM188R71H104KA93D | Murata <sup>(2)</sup>          | 0.1µF Ceramic Capacitor, X7R, Size 0603, 50V  | 3    |

|              | C1608X7R1H104K     | TDK <sup>(3)</sup>             |                                               |      |

|              | 0603ZC105KAT2A     | AVX <sup>(1)</sup>             |                                               |      |

| C8           | GRM188R71A105KA61D | Murata <sup>(2)</sup>          | 1.0µF Ceramic Capacitor, X7R, Size 0603, 10V  | 1    |

|              | C1608X7R1A105K     | TDK <sup>(3)</sup>             |                                               |      |

|              | 0603ZD225KAT2A     | AVX <sup>(1)</sup>             |                                               | 1    |

| C9           | GRM188R61A225KE34D | Murata <sup>(2)</sup>          | 2.2µF Ceramic Capacitor, X5R, Size 0603, 10V  |      |

|              | C1608X5R1A225K     | TDK <sup>(3)</sup>             |                                               |      |

|              | 06035C472KAZ2A     | AVX <sup>(1)</sup>             |                                               |      |

| C12          | GRM188R71H472K     | Murata <sup>(2)</sup>          | 4.7nF Ceramic Capacitor, X7R, Size 0603, 50V  | 1    |

|              | C1608X7R1H472K     | TDK <sup>(3)</sup>             |                                               |      |

| C14          | B41851F7227M       | EPCOS <sup>(4)</sup>           | 220µF Aluminum Capacitor, 35V                 | 1    |

| C11, C16     | Open               |                                |                                               |      |

|              | SD103AWS           | MCC <sup>(5)</sup>             |                                               |      |

| D1           | SD103AWS-7         | Diodes Inc <sup>(6)</sup>      | 40V, 350mA.Schottky Diode. SOD323             | 1    |

|              | SD103AWS           | Vishay <sup>(7)</sup>          |                                               |      |

| L1           | HCF1305-1R0-R      | Cooper Bussmann <sup>(8)</sup> | 1.0µH Inductor, 21A Saturation Current        | 1    |

| R1           | CRCW06032R21FKEA   | Vishay Dale <sup>(7)</sup>     | 2.21Ω Resistor, Size 0603, 1%                 | 1    |

| R2           | CRCW06032R00FKEA   | Vishay Dale <sup>(7)</sup>     | 2.00Ω Resistor, Size 0603, 1%                 | 1    |

| R3           | CRCW060319K6FKEA   | Vishay Dale <sup>(7)</sup>     | 19.6kΩ Resistor, Size 0603, 1%                | 1    |

| R4           | CRCW06032K49FKEA   | Vishay Dale <sup>(7)</sup>     | 2.49kΩ Resistor, Size 0603, 1%                | 1    |

| R5           | CRCW060320K0FKEA   | Vishay Dale <sup>(7)</sup>     | 20.0kΩ Resistor, Size 0603, 1%                | 1    |

| R6, R14, R17 | CRCW060310K0FKEA   | Vishay Dale <sup>(7)</sup>     | 10.0kΩ Resistor, Size 0603, 1%                | 3    |

| R7           | CRCW06034K99FKEA   | Vishay Dale <sup>(7)</sup>     | 4.99kΩ Resistor, Size 0603, 1%                | 1    |

| R8           | CRCW06032K87FKEA   | Vishay Dale <sup>(7)</sup>     | 2.87kΩ Resistor, Size 0603, 1%                | 1    |

| R9           | CRCW06032K006FKEA  | Vishay Dale <sup>(7)</sup>     | 2.00kΩ Resistor, Size 0603, 1%                | 1    |

| R10          | CRCW06031K18FKEA   | Vishay Dale <sup>(7)</sup>     | 1.18kΩ Resistor, Size 0603, 1%                | 1    |

| R11          | CRCW0603806RFKEA   | Vishay Dale <sup>(7)</sup>     | 806Ω Resistor, Size 0603, 1%                  | 1    |

| R12          | CRCW0603475RFKEA   | Vishay Dale <sup>(7)</sup>     | 475Ω Resistor, Size 0603, 1%                  | 1    |

# **Bill of Materials (Continued)**

| Item     | Part Number      | Manufacturer                | Description                                                   | Qty. |

|----------|------------------|-----------------------------|---------------------------------------------------------------|------|

| R13      | CRCW06030000FKEA | Vishay Dale <sup>(7)</sup>  | 0Ω Resistor, Size 0603, 5%                                    | 1    |

| R15      | CRCW060349R9FKEA | Vishay Dale <sup>(7)</sup>  | 49.9Ω Resistor, Size 0603, 1%                                 | 1    |

| R16, R18 | CRCW06031R21FKEA | Vishay Dale <sup>(7)</sup>  | 1.21Ω Resistor, Size 0603, 1%                                 | 2    |

| R20      | Open             |                             |                                                               |      |

| U1       | MIC26901YJL      | Micrel. Inc. <sup>(9)</sup> | 28V, 9A Hyper Speed Control™ Synchronous DC/DC Buck Regulator | 1    |

#### Notes:

AVX: <u>www.avx.com</u>.

Murata: <u>www.murata.com</u>.

TDK: www.tdk.com.

EPCOS: www.epcos.com.

SANYO: www.sanyo.com.

Diode Inc.: www.diodes.com.

Vishay: www.vishay.com.

8. Cooper Bussmann: www.cooperbussmann.com.

9. Micrel, Inc.: www.micrel.com.

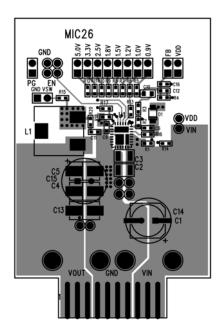

# **PCB Layout Recommendations**

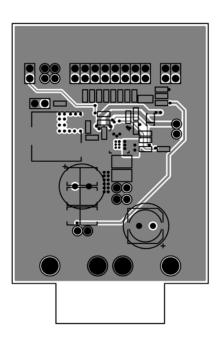

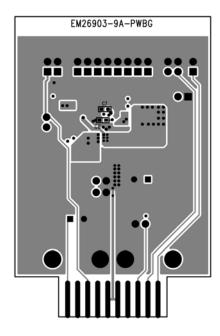

Figure 9. MIC26901 Evaluation Board Top Layer

Figure 10. MIC26901 Evaluation Board Mid-Layer 1 (Ground Plane)

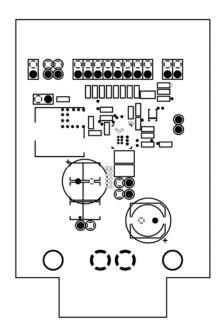

# **PCB Layout Recommendations (Continued)**

Figure 11. MIC26901 Evaluation Board Mid-Layer 2

Figure 12. MIC26901 Evaluation Board Bottom Layer

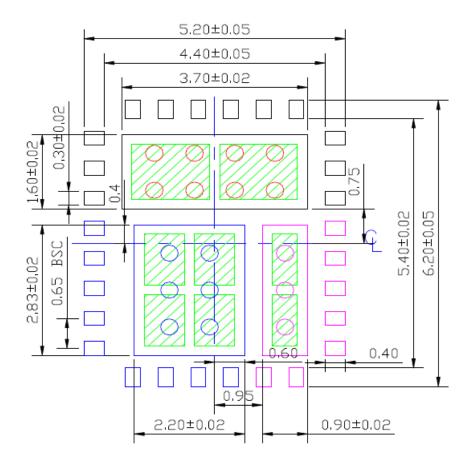

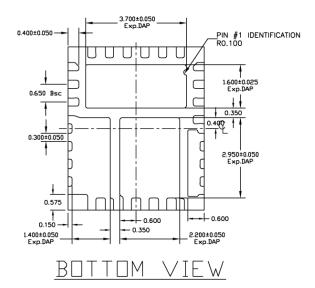

## **Recommended Land and Solder Stencil Pattern**

Red circle indicates Thermal Via. Size should be .300-.350 mm in diameter, 0.80 mm pitch, and it should be connected to GND plane for maximum thermal performance.

Green rectangle (with shaded area) indicates Solder Stencil Opening on exposed pad area. Sizes should be a) 1.55x1.20 mm, 1.75 mm pitch, b) 0.80x1.11 mm, 1.31 mm pitch, c) 0.50x1.11 mm, 1.31 mm pitch.

MIC26901 Micrel, Inc.

## **Package Information**

- ALL DIMENSIONS ARE IN MILLIMETERS.

- MAX. PACKAGE WARPAGE IS 0.05 mm.

MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS.

- PIN #1 ID ON TOP WILL BE LASER/INK MARKED.

DIMENSION APPLIES TO METALIZED TERMINAL AND IS MEASURED

- BETWEEN 0.20 AND 0.25 mm FROM TERMINAL TIP APPLIED ONLY FOR TERMINALS.

- APPLIED FOR EXPOSED PAD AND TERMINALS.

SIDE VIEW

28-Pin 5mm × 6mm MLF® (YJL)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2011 Micrel, Incorporated.