# 8 Line ESD/EMI Protection for Color LCD Interfaces UM8401 DFN16 4.0×1.6

### **General Description**

The UM8401 is a low pass filter array with integrated TVS diodes. It is designed to suppress unwanted EMI/RFI signals and provide electrostatic discharge (ESD) protection in portable electronic equipment. This state-of-the-art device utilizes silicon-avalanche technology for superior clamping performance and DC electrical characteristics. It has been optimized for protection of color LCD panels in cellular phones and other portable electronics.

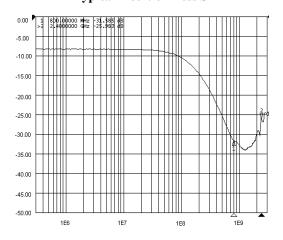

The device consists of eight identical circuits comprised of TVS diodes for ESD protection, and a RC network for EMI filtering. A series resistor value of  $100\Omega$  and a capacitance value of 10pF are used to achieve 25dB minimum attenuation from 800 MHz to 2.5GHz. The TVS diodes provide effective suppression of ESD voltages in excess of  $\pm 15kV$  (air discharge) and  $\pm 8kV$  (contact discharge) per IEC 61000-4-2, level 4.

The UM8401 is in a 16-pin, RoHS compliant DFN16 package. It measures 4.0mm×1.6mm. The leads are spaced at a pitch of 0.5mm and are finished with lead-free Ni Pd. The small package makes it ideal for use in portable electronics such as cell phones, digital still cameras, and PDAs.

#### **Applications**

- EMI Filtering and ESD Protection for Data Lines

- Wireless Phones

- Handheld Products

- Notebook Computers

- LCD Displays

#### **Features**

- EMI/RFI Filter with Integrated TVS for ESD Protection

- ESD Protection to IEC 61000-4-2 (ESD) Level

4, ±15kV (Air), ±8kV (Contact)

- 25dB Minimum Attenuation: 800MHz to 2.5GHz

- Working Voltage: 5V

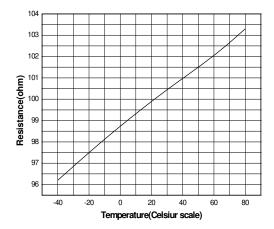

- Resistor:  $100\Omega \pm 15\%$

- Typical Capacitance:  $15pF(V_R=2.5V)$

- Solid-State Technology

- DFN16 Package: 4.0mm×1.6 mm

- Moisture Sensitivity Level 1

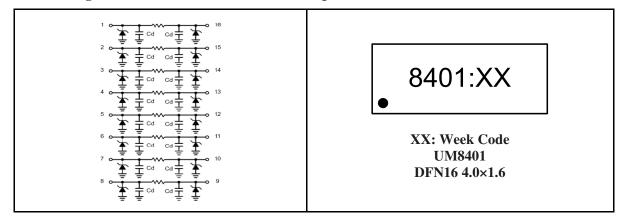

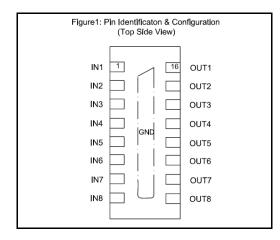

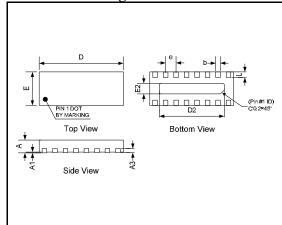

#### **Pin Configurations**

#### **Top View**

# **Ordering Information**

| Part<br>Number | Working<br>Voltage | Packaging Type | Channel | Marking<br>Code | Shipping Qty                  |

|----------------|--------------------|----------------|---------|-----------------|-------------------------------|

| UM8401         | 5.0V               | DFN16 4.0×1.6  | 8       | 8401            | 3000pcs/7 Inch<br>Tape & Reel |

# **Absolute Maximum Ratings**

| Parameter                              | Symbol     | Value      | Unit |

|----------------------------------------|------------|------------|------|

| Junction Temperature                   | $T_{J}$    | 125        | °C   |

| Steady State Power per Resistor @ 25°C | $P_R$      | 328        | mW   |

| Operating Temperature Range            | $T_{OP}$   | -40 to 85  | °C   |

| Storage Temperature Range              | $T_{STG}$  | -55 to 150 | °C   |

| Maximum Lead Temperature for Soldering | $T_{ m L}$ | 260        | °C   |

## **Electrical Characteristics**

| Parameter                    | Symbol    | <b>Test Conditions</b>                               | Min | Тур | Max | Unit |

|------------------------------|-----------|------------------------------------------------------|-----|-----|-----|------|

| Reverse Stand-Off<br>Voltage | $V_{RWM}$ |                                                      |     |     | 5.0 | V    |

| Reverse Breakdown<br>Voltage | $V_{BR}$  | I <sub>T</sub> =1mA                                  | 6.0 | 7.0 | 8.0 | V    |

| Reverse Leakage<br>Current   | $I_R$     | $V_{RWM}=3.3V$                                       |     |     | 100 | nA   |

| Total Series Resistance      | $R_A$     | I <sub>R</sub> =20mA,<br>Each Line                   | 85  | 100 | 115 | Ω    |

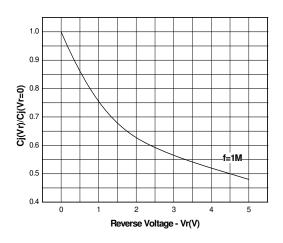

| Total Capacitance            | $C_d$     | Input to GND, Each Line $V_R$ =0V, f=1MHz            | 20  | 23  | 26  | pF   |

| Total Capacitance            | $C_d$     | Input to GND, Each Line $V_R$ =2.5V, f=1MHz          | 13  | 15  | 18  | pF   |

| Cut-Off Frequency (Note 1)   | $f_{3dB}$ | Above this frequency, appreciable attenuation occurs |     | 150 |     | MHz  |

Note 1:  $50\Omega$  source and  $50\Omega$  load termination.

# **Typical Operating Characteristics**

## **Typical Insertion Loss S21**

**Typical Resistance vs. Temperature**

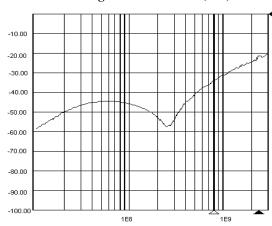

**Analog Crosstalk Curve (S41)**

Capacitance vs. Reverse Voltage

#### **Applications Information**

#### **Device Connection**

The UM8401 is comprised of eight identical circuits each consisting of a low pass filter for EMI/RFI suppression and dual TVS diodes for ESD protection. The device is in a 16-pin DFN package. Electrical connection is made to the 16 pins located at the bottom of the device. A center tab serves as the ground connection. The device has a flow through design for easy layout. All path lengths should be kept as short as possible to minimize the effects of parasitic inductance in the board traces. Recommendations for the ground connection are given below.

#### **Ground Connection Recommendation**

Parasitic inductance present in the board layout will affect the filtering performance of the device. As frequency increases, the effect of the inductance becomes more dominant. This effect is given by Equation 1.

| Pin                      | Identification           |  |  |

|--------------------------|--------------------------|--|--|

| 1 - 8                    | Input Lines              |  |  |

| 9 - 16                   | Output Lines             |  |  |

| Center Tab               | Ground                   |  |  |

| Equation 1: The Imperior | edance of an Inductor at |  |  |

XLF(L, f) =  $2 \times \pi \times f \times L$ Where: L= Inductance (H) f = Frequency (Hz)

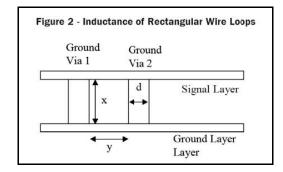

Via connections to the ground plane form rectangular wire loops or ground loop inductance as shown in Figure 2. Ground loop inductance can be reduced by using multiple vias to make the connection to the ground plane. Bringing the ground plane closer to the signal layer (preferably the next layer) also reduces ground loop inductance. Multiple vias in the device ground pad will result in a lower inductive ground loop over two exterior vias. Vias with a diameter d are separated by a distance y run between layers separated by a distance x. The inductance of the loop path is given by Equation 2. Thus, decreasing distance x and y will reduce the loop inductance and result in better high frequency filter characteristics.

Equation 2: Inductance of Rectangular Wire Loop

$$LRECT(d,x,y) = 10.16*10^{-9}*\left[x*ln\left[\frac{2^{*}y}{d}\right]+y*ln\left[\frac{2^{*}x}{d}\right]\right]$$

Where:

$$d = Diameter \ of \ the \ wire \ (in)$$

$$x = Length \ of \ wire \ loop \ (in)$$

$$y = Breath \ of \ wire \ loop \ (in)$$

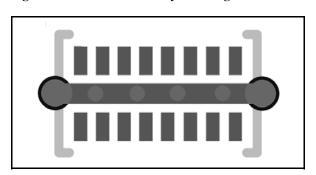

Figure 3 shows the recommended device layout. The ground pad vias have a diameter of 0.008 inches (0.20 mm) while the two external vias have a diameter of 0.010 inches (0.250mm). The internal vias are spaced approximately evenly from the center of the pad. The designer may choose to use more vias with a smaller diameter (such as 0.005 inches or 0.125mm) since changing the diameter of the via will result in little change in inductance (i.e. the log function in Equation 2 in highly insensitive to parameter d).

Figure 3 – Recommended Layout Using Ground Vias

# **Package Information**

## UM8401 DFN16 4.0×1.6

**Outline Drawing**

| DIMENSIONS |             |      |          |          |       |       |  |

|------------|-------------|------|----------|----------|-------|-------|--|

| Symbol     | MILLIMETERS |      |          | INCHES   |       |       |  |

|            | Min         | Тур  | Max      | Min      | Тур   | Max   |  |

| A          | 0.50        | -    | 0.80     | 0.020    | -     | 0.031 |  |

| A1         | 0.00        | ı    | 0.05     | 0.000    | -     | 0.002 |  |

| A3         | 0.203REF    |      | 0.008REF |          |       |       |  |

| b          | 0.15        | -    | 0.30     | 0.006    | -     | 0.012 |  |

| D          | 3.924       | 4.00 | 4.076    | 0.154    | 0.157 | 0.160 |  |

| D2         | 2.95        | -    | 3.30     | 0.116    | -     | 0.130 |  |

| Е          | 1.524       | 1.60 | 1.676    | 0.060    | 0.063 | 0.066 |  |

| E2         | 0.30        | -    | 0.60     | 0.012    | -     | 0.024 |  |

| e          | 0.50TYP     |      |          | 0.020TYP |       |       |  |

| L          | 0.15        | -    | 0.38     | 0.006    | -     | 0.015 |  |

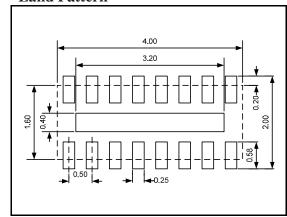

## **Land Pattern**

#### NOTES:

- 1. Compound dimension: 4.00×1.60;

- 2. Unit: mm;

- 3. General tolerance  $\pm 0.05$ mm unless otherwise specified;

- 4. The layout is just for reference.

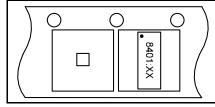

**Tape and Reel Orientation**

#### **GREEN COMPLIANCE**

Union Semiconductor is committed to environmental excellence in all aspects of its operations including meeting or exceeding regulatory requirements with respect to the use of hazardous substances. Numerous successful programs have been implemented to reduce the use of hazardous substances and/or emissions.

All Union components are compliant with the RoHS directive, which helps to support customers in their compliance with environmental directives. For more green compliance information, please visit:

http://www.union-ic.com/index.aspx?cat\_code=RoHSDeclaration

#### **IMPORTANT NOTICE**

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Union assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any update. Union reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.

Union Semiconductor, Inc

Add: Unit 606, No.570 Shengxia Road, Shanghai 201210

Tel: 021-51093966 Fax: 021-51026018

Website: www.union-ic.com