## **General Description**

The MAX1878 dual power supply contains a step-down and step-up DC-DC converter in a small 12-pin TQFN package for use in PDAs. The step-down DC-DC converter delivers over 500mA to an output as low as 1.25V for logic power. The step-up DC-DC converter delivers over 15mA and an output as high as 28V for a liquid crystal display (LCD). With an input voltage from 2.0V to 5.5V the MAX1878 is intended for use in systems powered by a 2-cell alkaline or 1-cell lithium-ion (Li+) battery.

19-2248; Rev 2; 5/11

EVALUATION KIT AVAILABLE

Fast switching frequency allows the use of small inductors and capacitors, and the low  $19\mu$ A typical quiescent current allows high efficiency when the system is in standby mode. Each output can be independently enabled.

The MAX1878 is available in a small 0.75mm high 4mm x 4mm 12-pin TQFN package and requires no external FETs. The MAX1878 evaluation kit is available to speed designs.

# **Applications**

Personal Digital Assistants (PDA) Organizers/Translators MP3 Players GPS Receivers

# \_Features

- Evaluation Kit Available to Speed Designs

- Two Output Voltages Main Output: 1.25V to VIN LCD Output: Up to 28V

- ♦ 2.0V to 5.5V Input Range

- ♦ Low 19µA Quiescent Supply Current

- ♦ 1µA Shutdown Supply Current

- High Switching Frequency for Small External Components

- Small 0.75mm High 4mm x 4mm 12-Pin TQFN Package

# MAX1878

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE | TOP<br>MARK |  |

|-------------|----------------|-----------------|-------------|--|

| MAX1878ETC+ | -40°C to +85°C | 12-TQFN-EP*     | AAGC        |  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

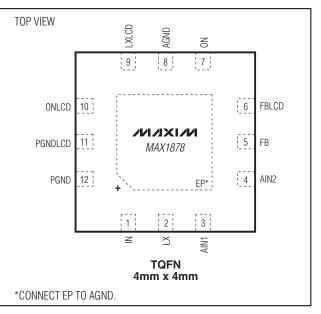

## **Pin Configuration**

###

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

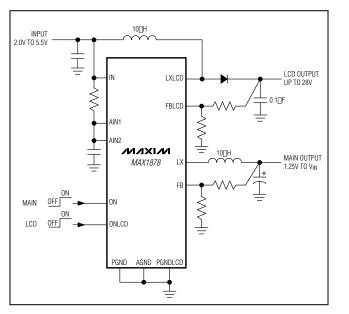

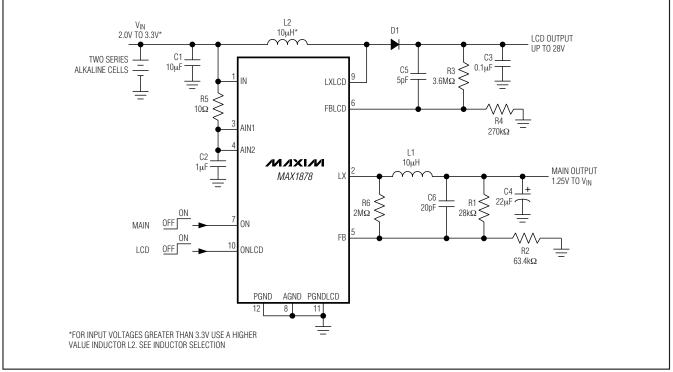

## **Typical Operating Circuit**

Maxim Integrated Products 1

# **MAX1878**

## **ABSOLUTE MAXIMUM RATINGS**

| FB, FBLCD, AIN1, AIN2, ON, ONLCD to AIN2 to AIN1. |                                  |

|---------------------------------------------------|----------------------------------|

| AIN1, AIN2 to IN                                  |                                  |

| IN to PGND                                        |                                  |

| LX to PGND                                        | 0.3V to (V <sub>IN</sub> + 0.3V) |

| LXLCD to PGNDLCD                                  | 0.3V to +30V                     |

| PGND, PGNDLCD to AGND                             | 0.3V to +0.3V                    |

| LX Current                                        |                                  |

| LXLCD Current                                     | 500mA                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

TQFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

# **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = V<sub>AIN</sub> = 2.5V, circuit of Figure 1, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                       | SYMBOL                             | CONDITIONS                                                        |                                               | MIN   | ТҮР   | MAX   | UNITS |

|---------------------------------|------------------------------------|-------------------------------------------------------------------|-----------------------------------------------|-------|-------|-------|-------|

| GENERAL                         |                                    |                                                                   |                                               | •     |       |       | •     |

| Input Voltage Range             | V <sub>IN</sub> , V <sub>AIN</sub> |                                                                   |                                               | 2.0   |       | 5.5   | V     |

|                                 |                                    | V <sub>IN</sub> rising                                            |                                               |       | 1.92  | 2.0   | V     |

| Undervoltage Lockout Threshold  | Vuvlo                              | V <sub>IN</sub> falling                                           |                                               | 1.7   | 1.82  |       | v     |

| Undervoltage Lockout Hysteresis |                                    |                                                                   |                                               |       | 100   |       | mV    |

| Quiescent Current               | IAIN1 +                            | VFB = VFBLCD = 1.30V, VONLCD = 0V,<br>step-down converter only    |                                               |       | 19    | 30    | μA    |

|                                 | I <sub>AIN2</sub>                  | V <sub>FB</sub> = V <sub>FBLCD</sub> = 1.30V                      |                                               |       | 24    | 38    |       |

| Shutdown Quiescent Current      |                                    | V <sub>ON</sub> = V <sub>ONLCD</sub> = 0V                         |                                               |       | 0     | 1     | μA    |

| MAIN OUTPUT (Step-Down Conv     | erter)                             |                                                                   |                                               |       |       |       |       |

| Output Voltage Adjustment Range | VMAIN                              |                                                                   |                                               | 1.25  |       | VIN   | V     |

|                                 | V <sub>FB</sub>                    | $V_{IN} = V_{AIN} = 2V$                                           | $T_A = +25^{\circ}C \text{ to } +85^{\circ}C$ | 1.225 | 1.250 | 1.275 | V     |

| FB Regulation Voltage           |                                    |                                                                   | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C$   | 1.220 |       | 1.280 | v     |

| FB Input Bias Current           | I <sub>FB</sub>                    | $V_{IN} = V_{AIN} = 2V$                                           | •                                             |       | 10    | 50    | nA    |

| Main Output Current             | have                               |                                                                   | $V_{IN} = V_{AIN} = 2.5V$                     | 250   | 500   |       | mA    |

| (Note 2)                        | Imain                              | $V_{MAIN} = 1.8V$                                                 | $V_{IN} = V_{AIN} = 2.0V$                     | 200   | 350   |       |       |

| Line Regulation                 |                                    | $I_{LOAD} = 150$ mA, $V_{IN} = V_{AIN} = 2$ V to 3V,<br>FB = GND  |                                               |       | 1     |       | %     |

| Load Regulation                 |                                    | $V_{IN} = V_{AIN} = 2.5V$ , $I_{LOAD} = 10$ mA to 150mA           |                                               |       | 1     |       | %     |

| Dropput Veltege                 |                                    | $V_{IN} = V_{AIN} = 2V$ , $I_{LOAD} = 150$ mA,<br>$V_{FB} = 0.8V$ |                                               |       |       | 150   |       |

| Dropout Voltage                 |                                    | $V_{IN} = V_{AIN} = 3V, I_{LC}$<br>$V_{FB} = 0.8V$                | <sub>DAD</sub> = 150mA,                       |       |       | 100   | - mV  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{AIN} = 2.5V)$ , circuit of Figure 1, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                       | SYMBOL                | CON                                                                       | IDITIONS                                      | MIN                  | ТҮР   | MAX   | UNITS    |

|---------------------------------|-----------------------|---------------------------------------------------------------------------|-----------------------------------------------|----------------------|-------|-------|----------|

| LX Max Duty Cycle               |                       | $V_{FB} = 0.8V$                                                           |                                               | 100                  |       |       | %        |

| LX Leakage Current              |                       | $V_{ON} = 0V, V_{IN} = 5.5V$                                              |                                               |                      | 0.1   | 5     | μA       |

|                                 |                       | $V_{IN} = V_{AIN} = 2V$ , $I_{LX} = 300$ mA                               |                                               |                      | 0.55  | 0.95  | 0        |

| LX P-Channel On-Resistance      |                       | $V_{IN} = V_{AIN} = 3V, I_{LX}$                                           | = 300mA                                       |                      | 0.42  | 0.65  | Ω        |

|                                 |                       | $V_{IN} = V_{AIN} = 2V, I_{LX}$                                           | = 300mA                                       |                      | 0.62  | 0.93  | 0        |

| LX N-Channel On-Resistance      |                       | $V_{IN} = V_{AIN} = 3V, I_{LX}$                                           | = 300mA                                       |                      | 0.46  | 0.65  | Ω        |

| LX Current Limit                |                       |                                                                           |                                               | 330                  | 550   | 800   | mA       |

| Idle Mode Threshold             |                       |                                                                           |                                               | 70                   | 135   | 220   | mA       |

| LX Minimum On-Time              | t <sub>LXON</sub>     |                                                                           |                                               | 240                  | 440   | 740   | ns       |

| LX Minimum Off-Time             | t <sub>LXOFF</sub>    |                                                                           |                                               | 200                  | 390   | 670   | ns       |

| ON Input Low Voltage            |                       | $2V < V_{IN} < 5.5V$                                                      |                                               |                      |       | 0.4   | V        |

| ON Input High Voltage           |                       | $2V < V_{IN} < 5.5V$                                                      |                                               | 1.3                  |       |       | V        |

| ON Input Leakage Current        |                       |                                                                           |                                               | -1                   |       | 1     | μA       |

| LCD OUTPUT (Step-Up Converted   | r)                    |                                                                           |                                               |                      |       |       | <u>.</u> |

| LCD Output Voltage Adjust Range | VLCD                  |                                                                           |                                               | V <sub>IN</sub> + 1V |       | 28    | V        |

| FBLCD Regulation Voltage        |                       | $V_{IN} = V_{AIN} = 2V$                                                   | $T_A = +25^{\circ}C \text{ to } +85^{\circ}C$ | 1.225                | 1.250 | 1.275 |          |

|                                 | VFBLCD                |                                                                           | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C$   | 1.220                |       | 1.280 | V        |

|                                 |                       | $V_{AIN} = V_{IN} = 2V$ , $I_{LXLCD} = 150$ mA                            |                                               |                      | 2.8   | 5.0   |          |

| LXLCD On-Resistance             |                       | $V_{AIN} = V_{IN} = 3V$ , $I_{LXL}$                                       | _CD = 150mA                                   |                      | 1.7   | 3.0   | Ω        |

| LXLCD Current Limit             |                       |                                                                           |                                               | 140                  | 280   | 440   | mA       |

| LXLCD Leakage Current           |                       | $V_{LXLCD} = 28V$                                                         |                                               |                      | 0     | 1     | μA       |

| LCD Output Current              |                       | $V_{AIN} = V_{IN} = 2.5V, V_{LCD} = 18V$                                  |                                               | 1.5                  | 7.6   |       |          |

| (Note 3)                        | ILCD                  | $V_{AIN} = V_{IN} = 2V, V_{LC}$                                           | D = 18V                                       | 1.4                  | 6.6   |       | mA       |

| FBLCD Input Bias Current        | IFBLCD                | $V_{AIN} = V_{IN} = 2V$                                                   |                                               |                      | 10    | 50    | nA       |

| LCD Line Regulation             |                       | $V_{AIN} = V_{IN} = 2V$ to 3V, $I_{LOAD} = 5mA$ ,<br>$V_{LXLCD} = 18V$    |                                               |                      | 1     |       | %        |

| LCD Load Regulation             |                       | $V_{AIN} = V_{IN} = 2.5V$ , $I_{LOAD} = 1mA$ to 5mA,<br>$V_{LXLCD} = 18V$ |                                               |                      | 1.3   |       | %        |

| LXLCD Maximum On-Time           | <b>t</b> LXLCDON      |                                                                           |                                               | 5.1                  | 9.8   | 17    | μs       |

| VI OD Mining ung Off Time -     |                       |                                                                           |                                               | 0.5                  | 1.0   | 1.7   |          |

| LXLCD Minimum Off-Time          | <sup>t</sup> LXLCDOFF | V <sub>FBLCD</sub> < 0.9V (soft-start)                                    |                                               | 1.3                  | 2.6   | 4.4   | μs       |

| ONLCD Input Low Voltage         |                       | $2V < V_{AIN} = V_{IN} < 5.5V$                                            |                                               |                      |       | 0.4   | V        |

| ONLCD Input High Voltage        |                       | $2V < V_{AIN} = V_{IN} < 5.5V$                                            |                                               | 1.3                  |       |       | V        |

| ONLCD Input Leakage Current     | 1                     |                                                                           |                                               | -1                   |       | 1     | μA       |

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{AIN} = 2.5V, \text{ circuit of Figure 1, } T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) (Note 4)$

| PARAMETER                  | SYMBOL             | CONDITIONS                   | MIN   | МАХ   | UNITS |

|----------------------------|--------------------|------------------------------|-------|-------|-------|

| GENERAL                    |                    |                              | ·     |       |       |

| Quiescent Current from AIN | I <sub>AIN</sub>   | $V_{FB} = V_{FBLCD} = 1.30V$ |       | 38    | μΑ    |

| MAIN OUTPUT (Step-Down Co  | onverter)          |                              |       |       |       |

| FB Regulation Voltage      | V <sub>FB</sub>    | $V_{AIN} = V_{IN} = 2V$      | 1.212 | 1.288 | V     |

| LX Current Limit           |                    |                              | 310   | 820   | mA    |

| LX Minimum On-Time         | tlxon              |                              | 240   | 740   | ns    |

| LX Minimum Off-Time        | t <sub>LXOFF</sub> |                              | 200   | 670   | ns    |

| LCD OUTPUT (Step-Up Conve  | rter)              |                              | ·     |       |       |

| LXLCD Current Limit        |                    |                              | 130   | 450   | mA    |

| LXLCD Maximum On-Time      | <b>t</b> LXLCDON   |                              | 5.1   | 17    | μs    |

|                            |                    |                              | 0.5   | 1.7   |       |

| LXLCD Minimum Off-Time     |                    | V <sub>FBLCD</sub> < 0.9V    | 1.3   | 4.5   | μs    |

| FBLCD Regulation Voltage   | VFBLCD             | $V_{AIN} = V_{IN} = 2V$      | 1.212 | 1.288 | V     |

Note 2: Main output current is guaranteed by LX current limit, LX on resistance, and LX minimum off-time.

Note 3: LCD output current is guaranteed by LXLCD current limit, LXLCD on-resistance, and LXLCD minimum off-time, starting into a resistive load.

Note 4: Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design and not production tested.

$(V_{IN} = V_{AIN} = 2.5V, \text{ circuit of Figure 1, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

**Typical Operating Characteristics**

**STEP-DOWN CONVERTER EFFICIENCY STEP-DOWN CONVERTER EFFICIENCY STEP-UP CONVERTER EFFICIENCY** vs. LOAD CURRENT (VMAIN = 1.8V) vs. LOAD CURRENT (VLCD = 18V) vs. LOAD CURRENT (VMAIN = 1.5V) 100 100 100 2.5V 90 VIN = 5.0V (22µH 251 90 90 80 80 80 (%) EFFICIENCY (%) EFFICIENCY (%) 5.0\ EFFICIENCY 70  $V_{IN} = 3.6V$  $V_{IN} = 5.0V$ 70 70 3.6 = 3.6V 60 60 60  $V_{IN} = 2.5V$ 50 (10ut 50 50 ONLCD = ONLCD = 40 PGNDLCD PGNDLCD ON = PGNI40 40 30 0.1 10 100 1000 0.1 10 100 1000 0.01 0.1 10 100 1 1 1 LOAD CURRENT (mA) LOAD CURRENT (mA) LOAD CURRENT (mA) **STEP-DOWN CONVERTER OUTPUT VOLTAGE STEP-DOWN CONVERTER OUTPUT VOLTAGE STEP-UP CONVERTER OUTPUT VOLTAGE** vs. LOAD CURRENT (VMAIN = 1.8V) vs. LOAD CURRENT (VMAIN = 1.5V) vs. LOAD CURRENT (VLCD = 18V) 1.84 1.535 18.9 ONLCD = PGNDLCD Vin = 5.0V  $V_{IN} = 5.0V$ 18.8 1 5 3 0 1.83 V<sub>IN</sub> = 5.0V (22µH) 18.7 1.525 18.6 1.82 () 1.520 NIW 1.515 18.5 (NINM) 18.3 V<sub>MAIN</sub> (V) 1.81  $V_{IN} = 3.6V (15 \mu H)$ 1.80 1.510 18.2 = 3.6V VIN 1.79  $V_{IN} = 3.6V$ 18.1 1.505 **T**||| 18.0 = 2.5V 1.78 VIN 1.500 Vin ШÜ 17.9 2.5V (10µH) VIN = ONI CD = PGNDI CD ONI CD = PGNDI CDTÜÜ ÌLÌШÍ 17.8 1.77 1,495 10 1000 100 1000 0.01 0.1 100 0.1 10 0.1 10 100 1 1 LOAD CURRENT (mA) LOAD CURRENT (mA) LOAD CURRENT (mA) **NO LOAD SUPPLY CURRENT vs. STEP-DOWN CONVERTER SWITCHING STEP-UP CONVERTER CURRENT LIMIT** FREQUENCY vs. SUPPLY VOLTAGE INPUT VOLTAGE (V<sub>MAIN</sub> = 1.8V, V<sub>LCD</sub> = 18V) vs. INPUT VOLTAGE 140 1.2 500 STEP-UP AND STEP-DOWN 120 450 1.0 SWITCHING FREQUENCY (MHz)  $L2 = 22 \mu H$ SUPPLY CURRENT (MA) 100 CURRENT LIMIT (mA) 320 300 0.8 STEP-UP 80  $V_{MAIN} = 1.5V$ 0.6 60  $V_{MAIN} = 1.8V$ 0.4 40  $L2 = 15 \mu H$  $12 = 10 \mu H$ 0.2 250 20 I<sub>MAIN</sub> = 150mA ONLCD = PGNDLCD STEP-DOWN 0 0 200 3 5 6 2 3 5 0 1 2 4 4 6 2 3 4 5 6 SUPPLY VOLTAGE (V) INPUT VOLTAGE (V) SUPPLY VOLTAGE (V)

**MAX1878**

5

**MAX1878**

# \_Typical Operating Characteristics (continued)

$(V_{IN} = V_{AIN} = 2.5V, \text{ circuit of Figure 1, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

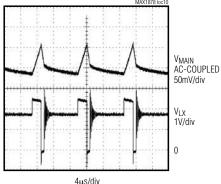

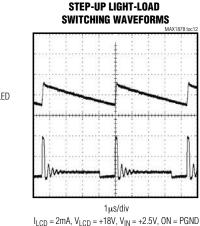

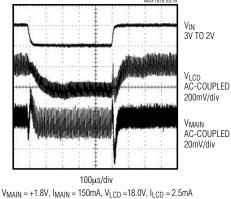

#### STEP-DOWN LIGHT-LOAD Switching Waveforms

$I_{MAIN} = 20$  mA,  $V_{MAIN} = +1.8$  V,  $V_{IN} = +2.5$  V, ONLCD = PGNDLCD

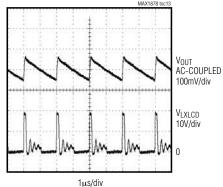

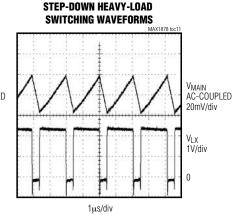

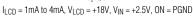

#### STEP-UP HEAVY-LOAD SWITCHING WAVEFORMS

$I_{LCD} = 4.5$ mA,  $V_{LCD} = +18V$ ,  $V_{IN} = +2.5V$ , ON = PGND

$I_{MAIN} = 250$ mA,  $V_{MAIN} = +1.8$ V,  $V_{IN} = +2.5$ V, ONLCD = PGNDLCD

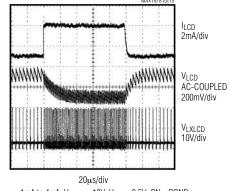

**STEP-DOWN LOAD**

TRANSIENT RESPONSE

VMAIN AC-COUPLED 100mV/div VLX 2V/div 10μs/div

$I_{MAIN} = 10mA \text{ to } 250mA, V_{MAIN} = +1.8V, \\ V_{IN} = +2.5V, \text{ ONLCD} = PGNDLCD$

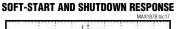

V<sub>OUT</sub> AC-COUPLED

100mV/div

VLXLCD

10V/div

Λ

**Pin Description**

| PIN | NAME FUNCTION |                                                                                                                                                                                                     |  |  |  |  |

|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | IN            | Step-Down Converter Power Input. Connect IN to the step-down converter power source. Bypass IN to PGND with a $10\mu$ F or greater low-ESR capacitor.                                               |  |  |  |  |

| 2   | LX            | Step-Down Converter Switching Node. Connect LX to the step-down converter output LC filter. LX swings between IN and PGND.                                                                          |  |  |  |  |

| 3   | AIN1          | Analog Input Power 1. AIN1 supplies power to the MAX1878 internal circuitry. Connect AIN1 to the 2.0V to 5.5V input power source. Bypass AIN1 to AGND with a $1\mu$ F or greater low-ESR capacitor. |  |  |  |  |

| 4   | AIN2          | Analog Input Power 2. Connect AIN1 and AIN2 together as close to the MAX1878 as possible.                                                                                                           |  |  |  |  |

| 5   | FB            | Step-Down Converter Feedback Input. Connect a resistive voltage-divider from the step-down converter output voltage to FB. The regulation threshold is 1.25V at FB.                                 |  |  |  |  |

| 6   | FBLCD         | LCD Step-Up Converter Feedback Input. Connect a resistive voltage-divider from the step-up converter output voltage to FBLCD. The regulation threshold is 1.25V at FBLCD.                           |  |  |  |  |

| 7   | ON            | Step-Down Converter On/Off Input. Drive ON high to turn on the step-down converter. Drive ON low to turn off the converter. For automatic startup, connect ON to AIN1.                              |  |  |  |  |

| 8   | AGND          | Analog (Low-Noise) Ground. The exposed pad and the corner tabs on the TQFN package are internally connected to analog ground. See the <i>PC Board Layout and Grounding</i> section.                 |  |  |  |  |

| 9   | LXLCD         | LCD Step-Up Converter Switching Node. Connect LXLCD to the step-up converter inductor and rectifier.                                                                                                |  |  |  |  |

| 10  | ONLCD         | LCD Step-Up Converter On/Off Input. Drive ONLCD high to turn on the step-up converter. Drive ONLCD low to turn off the converter. For automatic startup, connect ONLCD to AIN1.                     |  |  |  |  |

| 11  | PGNDLCD       | LCD Step-Up Converter Power Ground. PGNDLCD is the source of the step-up converter's internal N-channel MOSFET switch. Connect PGNDLCD to PGND as close to the MAX1878 as possible.                 |  |  |  |  |

| 12  | PGND          | Power Ground. PGND is the source of the step-down converter's internal N-channel MOSFET synchronous rectifier. Connect PGND to PGNDLCD as close to the MAX1878 as possible.                         |  |  |  |  |

| _   | EP            | Exposed Pad. Internally connected to AGND. Connect to a large analog ground (AGND) plane to maximize thermal performance. Not intended to use as an electrical connection point.                    |  |  |  |  |

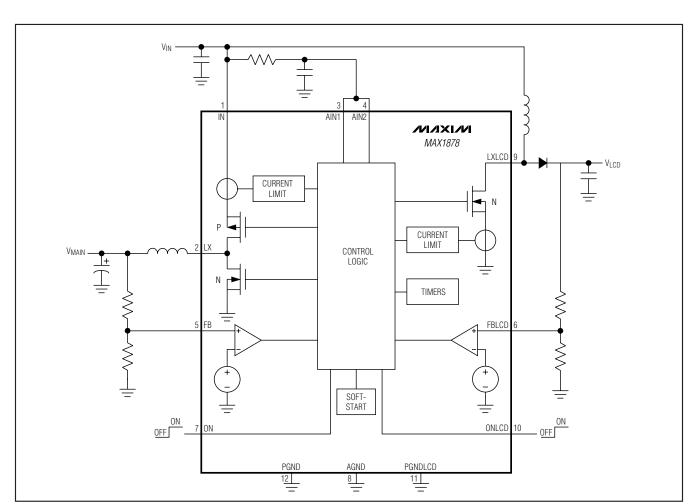

## **Detailed Description**

The MAX1878 step-down and step-up DC-DC converter operates from a 2.0V to 5.5V supply. Consuming only 19µA of quiescent supply current, the main stepdown converter delivers over 500mA to an output as low as 1.25V and the LCD step-up converter delivers over 15mA and an output as high as 28V. The MAX1878 uses a unique proprietary current-limited control scheme that provides excellent performance and high efficiency.

#### **Step-Down Converter Control Scheme**

The MAX1878 step-down converter uses a proprietary, current-limited control scheme to ensure high efficiency, fast transient response, and physically small external components. This control scheme is simple: when the output voltage is out of regulation, the error comparator begins a switching cycle by turning on the high-side switch. This switch remains on until the minimum ontime of 440ns expires and the output voltage regulates or the current-limit threshold is exceeded. Once off, the high-side switch remains off until the minimum off-time of 390ns expires and the output voltage falls out of regulation. During this period, the low-side synchronous rectifier turns on and remains on until either the high-side switch turns on again or the inductor current approaches zero. The internal synchronous rectifier eliminates the need for an external Schottky diode.

This control scheme allows the MAX1878 step-down converter to provide excellent performance throughout the entire load-current range. When delivering light loads, the high-side switch turns off after the minimum on-time and after the inductor current reaches the 135mA ideal mode threshold to reduce peak inductor

current, resulting in increased efficiency and reduced output voltage ripple. When delivering medium and higher output currents, the MAX1878 extends either the on-time or the off-time, as necessary to maintain regulation, resulting in nearly constant frequency operation with high efficiency and low output voltage ripple.

#### Step-Up Converter Control Scheme

The MAX1878 step-up converter features a minimum off-time, current-limited control scheme. The duty cycle is governed by a pair of one-shots that set a minimum off-time and a maximum on-time. The switching frequency can be up to 500kHz and depends upon the load and input voltage. The peak current limit of the internal N-channel MOSFET is 280mA.

#### **On/Off Control**

Pulling ON low places the MAX1878 step-down converter in shutdown mode and reduces step-down converter supply current to less than  $1\mu$ A. In shutdown, the internal switching MOSFETs and synchronous rectifier turn off and LX goes high impedance.

Pulling ONLCD low places the MAX1878 step-up converter in shutdown mode and reduces step-up converter supply current to less than  $1\mu$ A. In shutdown, LXLCD

enters a high-impedance state and the output remains connected to the input through the inductor and rectifier holding the output voltage to a diode drop below  $V_{IN}$ . The LCD output capacitance and load determine the rate at which  $V_{LCD}$  decays. Connect ON and ONLCD to IN for normal operation.

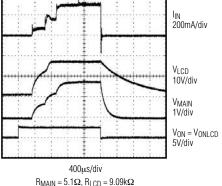

#### Soft-Start

The MAX1878 internal soft-start circuitry limits current drawn at startup, reducing transients on the input source. Soft-start is particularly useful for higher impedance input sources, such as lithium ion and alkaline cells. Step-down converter soft-start is implemented with current limit. At startup the step-down converter current limit is set to 25% of its full current limit. The current limit is increased by 25% every 256 switching cycles until full current limit is reached. Step-up converter soft-start is implemented with LXLCD minimum off-time. At startup the LXLCD minimum off-time is 2.6µs allowing the LCD output voltage to build up gradually. When the output reaches approximately 80% of its final output voltage the LXLCD minimum offtime is decreased to its final value of 1µs. See Soft-Start and Shutdown Response in the Typical Operating Characteristics section.

Figure 1. MAX1878 Standard Application Circuit

## \_Design Procedure

#### Setting the Output Voltage

Set the MAX1878 step-down converter output voltage by connecting a resistive voltage-divider from V<sub>MAIN</sub> to FB (Figure 1). Select an R2 from  $30k\Omega$  to  $300k\Omega$ . Calculate R1 with the following equation:

$$R1 = \frac{R2 \times R6(V_{MAIN} - V_{FB})}{V_{FB}(R6 + R2) - V_{MAIN} \times R2}$$

where  $V_{FB}$  = 1.25V, R6 = 2M $\Omega$  and  $V_{MAIN}$  may range from 1.25V to  $V_{IN}.$

Set the MAX1878 step-up converter output voltage by connecting a resistive voltage-divider from  $V_{\text{LCD}}$  to

FBLCD (Figure 1). Select an R4 from  $30k\Omega$  to  $300k\Omega$ . Calculate R3 with the following equation:

$$R3 = R4 \left( \frac{V_{LCD}}{V_{FBLCD}} - 1 \right)$$

where VFBLCD = 1.25V and VLCD may range from (VIN + 1V) to 28V.

The FB and FBLCD input bias currents are a maximum of 50nA. These small bias currents allow for large-value feedback resistors that improve light-load efficiency. For less than 1% output voltage error due to bias current, feedback resistors should be chosen such that the current through R2 is 100 times greater than IFB and the current through R4 is 100 times greater than IFBLCD.

Figure 2. Simplified Functional Diagram

# **MAX1878**

#### **Inductor Selection**

The MAX1878 is optimized to use a 10µH inductor over the entire operating range. Smaller inductance values typically offer smaller physical size for a given series resistance or saturation current. Circuits using larger inductance values may startup at lower input voltages and exhibit less ripple, but also provide reduced output power. This occurs when the inductance is sufficiently large to prevent the maximum current limit from being reached before the maximum on-time expires. The inductor's saturation current rating should be greater than the peak switching current. However, it is generally acceptable to bias the inductor into saturation by as much as 20%, although this will slightly reduce efficiency. Choose a low DC-resistance inductor to improve efficiency. For the above reasons choose the step-up converter inductor in the range of 10µH to 33µH depending on the input voltage (4µH per volt of VIN).

#### **Step-Up Converter Diode Selection**

The high maximum switching frequency of 500kHz requires a high-speed rectifier such as the 1N4148. To maintain high efficiency, the average current rating of the diode should be greater than the peak switching current. Choose a reverse breakdown voltage greater than the output voltage. A Schottky diode is not recommended as the lower forward voltage does little to improve efficiency whereas the higher reverse leakage current decreases efficiency.

#### Input Bypass Capacitors

Bypass V<sub>IN</sub> with a 10µF low-ESR surface-mount ceramic capacitor to PGND and PGNDLCD as close to the IC as possible. This input bypass capacitor reduces peak currents and noise at the input voltage source. Connect AIN1 and AIN2 together and bypass with a low-ESR 1µF surface-mount ceramic capacitor to AGND. A low resistance (10 $\Omega$ ) from IN to AIN1 and AIN2 creates a lowpass RC filter and provides low-noise analog input power to the MAX1878.

#### **Output Filter Capacitors**

The MAX1878 is a voltage mode converter and requires ripple at FB and FBLCD for stable regulation. For most applications, bypass  $V_{LCD}$  with a 0.1µF small ceramic surface-mount capacitor to PGNDLCD. For small

ceramic capacitors, the output ripple voltage is dominated by the capacitance value. If tantalum or electrolytic capacitors are used, the higher ESR increases the output ripple voltage. Decreasing the ESR reduces the output ripple voltage and the peak-to-peak transient voltage. Surface-mount capacitors are generally preferred because they lack the inductance and resistance of their through-hole equivalents. Bypass V<sub>MAIN</sub> with a 10µF to 47µF tantalum capacitor to PGND. Choose a capacitor with 200m $\Omega$  to 300m $\Omega$  ESR to provide stable switching while minimizing output ripple. A 22µF filter capacitor works well for most applications.

#### **Ripple Regulation**

For proper switching control the ripple at FB and FBLCD must be greater than 25mV. Use R6 and C6 as shown in Figure 1 to inject ripple into FB. To insure sufficient ripple on FBLCD, connect C5 as shown in Figure 1.

#### **PC Board Layout and Grounding**

High switching frequencies make PC board layout a very important part of design. Good design minimizes excessive EMI on the feedback paths and voltage gradients in the ground plane, both of which can result in instability or regulation errors. Connect the inductors, input filter capacitors, and output filter capacitors as close to the device as possible, and keep their traces short, direct, and wide. The external voltage-feedback networks should be very close to the feedback pins, within 0.2 inches (5mm). Keep noisy traces, such as LX and LXLCD, away from the voltage feedback networks; also keep them separate, using grounded copper.

The exposed backside pad and corner tabs of the TQFN package are internally connected to analog ground. For heat dissipation, connect the exposed backside pad to a large analog ground plane, preferably on a surface of the board that receives good airflow. Connect all power grounds and all analog grounds to separate ground planes in a star ground configuration. Connect the analog ground plane and the power ground plane together at a single point. The MAX1878 evaluation kit data sheet includes a proper PC board layout and routing scheme.

## **Chip Information**

EXPOSED PAD CONNECTED TO AGND PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND        |

|---------|---------|----------------|-------------|

| TYPE    | CODE    | NO.            | PATTERN NO. |

| 12 TQFN | T1244+4 | <u>21-0139</u> |             |

**MAX1878**

| REVISION | REVISION | DESCRIPTION                                                                                    | PAGES   |

|----------|----------|------------------------------------------------------------------------------------------------|---------|

| NUMBER   | DATE     |                                                                                                | CHANGED |

| 2        | 5/11     | Replaced QFN package with TQFN package and added exposed pad to <i>Pin Description</i> section | 1, 7    |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

**Revision History**