One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### Evaluating the ADAU7112 2-Channel PDM to I<sup>2</sup>S/TDM Converter

EVALUATION KIT CONTENTS EVAL-ADAU7112Z evaluation board

ADDITIONAL DOCUMENTS NEEDED

ADAU7112 data sheet

#### **GENERAL DESCRIPTION**

This user guide describes the design and setup of the EVAL-ADAU7112Z evaluation board, which can be configured to operate in several different hardware modes. An I<sup>2</sup>S/time division multiplexing (TDM) serial interface is accessible via header pins spaced at 0.1 inches. Pulse density modulation (PDM) data and the clock interface are available on these headers.

The evaluation board can be powered in several ways:

- External 5 V dc power supply and ground using the J14 header

- External 5 V power supply (not included) using the J8 power connector

- Directly powered using external power supplies that bypass the on-board regulators

On-board regulators derive supplies of 3.3 V, 1.8 V, and 1.2 V. Current measurements of the ADAU7112 can be performed with the supplied header pins.

The evaluation board allows demonstration and performance testing of the features of the ADAU7112.

For full details, see the ADAU7112 data sheet, which must be consulted in conjunction with this user guide when using the evaluation board.

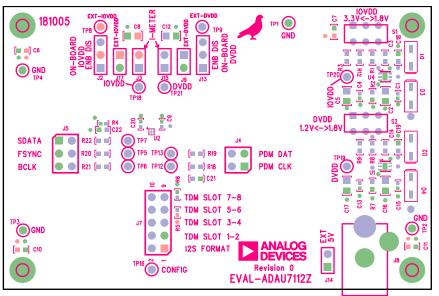

#### **EVALUATION BOARD PHOTOGRAPH**

Figure 1. EVAL-ADAU7112Z

## **TABLE OF CONTENTS**

| Evaluation Kit Contents     | 1 |

|-----------------------------|---|

| Additional Documents Needed | 1 |

| General Description         | 1 |

| Evaluation Board Photograph | 1 |

| Revision History            | 2 |

| Evaluation Board Hardware   | 3 |

| Hardware Mode               | 3 |

| Powering the Board                      | 3 |

|-----------------------------------------|---|

| Connecting the PDM Signals              | 4 |

| Connecting the I <sup>2</sup> S Signals | 4 |

| Evaluation Board Schematics and Artwork | 5 |

| Ordering Information                    | 9 |

| Bill of Materials                       | 9 |

#### **REVISION HISTORY**

6/2019—Revision 0: Initial Version

### EVALUATION BOARD HARDWARE HARDWARE MODE

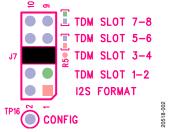

The hardware mode of the ADAU7112 allows the user to choose between a limited number of operation modes without the need for a control interface. Applying a jumper on the J7 header floats the CONFIG Pin (Pin B2) and enables the ADAU7112 to drive the TDM Slot 3-4 with the two PDM audio signal sources, as shown in Figure 2. The CONFIG pin configuration options are listed in Table 1.

| Serial Port<br>Operational Mode | CONFIG Pin Configuration                 |  |  |

|---------------------------------|------------------------------------------|--|--|

| I <sup>2</sup> S Format         | Tie to IOVDD                             |  |  |

| TDM Slot 1-2 <sup>1</sup>       | Tie to GND                               |  |  |

| TDM Slot 3-4 <sup>1</sup>       | Open                                     |  |  |

| TDM Slot 5-6 <sup>1</sup>       | Tie to IOVDD with 47 k $\Omega$ resistor |  |  |

| TDM Slot 7-8 <sup>1</sup>       | Tie to GND with 47 k $\Omega$ resistor   |  |  |

<sup>1</sup> 32-bit slots.

The CONFIG pin is brought to header J7 on the EVAL-ADAU7112Z to allow the selection of all hardware modes. The

Jumper on this header can connect the CONFIG pin to high (IOVDD), low (GND), floating, or through pull-up/pull-down resistors to put the ADAU7112 in the desired mode.

Figure 2. Hardware Mode, TDM Slot 3-4 Setting

#### **POWERING THE BOARD**

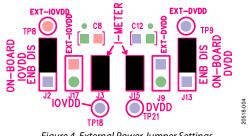

The EVAL-ADAU7112 evaluation board requires a power supply input of 5 V dc to 10 V dc and ground to the on-board voltage regulators. Plug the power supply into J8 or J14 on the evaluation board.

The on-board regulators provide the IOVDD and DVDD voltage rails. The IOVDD is switchable between 3.3 V and 1.8 V. The DVDD supply is switchable between 1.8 V and 1.2 V.

J2 and J13 allow the user to disable the internal regulators to allow external power injection for the IOVDD and DVDD.

Figure 3. DVDD and IOVDD Jumper Positions for On-Board Power

The J3 and J15 jumpers allow access to the IOVDD and DVDD current path for measuring current to the ADAU7112. The jumpers function for both the internal on-board voltage regulators and when an external power supply is used.

Figure 4 shows the jumper settings to disable the on-board voltage regulators allowing the user to connect an external power supply using the J17 and J9 jumpers. Pin 1 of each connector is the positive side of the power. Pin 2 of each header is ground.

Figure 4. External Power Jumper Settings

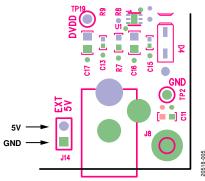

The 5 V dc to 10 V dc input can come from two sources: via the J8 connector or via the J14 jumper with an external laboratory power supply. This 5 V dc to 10 V dc power supplies the internal regulators to operate the evaluation board using the on-board power. This supply is not required when powering the board from external IOVDD and DVDD supplies.

Figure 5. External Power Connections

Figure 6 shows the configuration for using an external 5 V dc supply using the J8 jumper.

Figure 6. External 5 V DC Power with J8 Jumper

#### **CONNECTING THE PDM SIGNALS**

Figure 7 shows the connections for the PDM signal sources and the PDM clock output located on the J4 jumper. The odd pin numbers are ground, and the even pin numbers are signals. The TP12 and TP13 test points allow the user to view the signals on an oscilloscope.

The 0  $\Omega$  resistors, R18 and R19, allow the addition of damping resistors.

#### **CONNECTING THE I<sup>2</sup>S SIGNALS**

Figure 8 shows the I<sup>2</sup>S/TDM interface connections located on the J5 jumper. The odd pin numbers are ground, and the even pin numbers are signals. The TP5 to TP7 test points allow the user to view the signals on an oscilloscope.

The 0  $\Omega$  resistors, R20 to R22, allow the addition of damping resistors.

|       | J5                | [ <b>= =</b> ]C22 | 2             |

|-------|-------------------|-------------------|---------------|

| SDATA |                   | R22 🔳 🔳           | <b>()</b> TP7 |

| FSYNC | $\bullet \bullet$ | R20 🔳 🔳           | O TP5 _       |

| BCLK  |                   | R21 🔳 🔳           | <b>O</b> TP6  |

Figure 8. Connecting to the I<sup>2</sup>S/TDM Interface

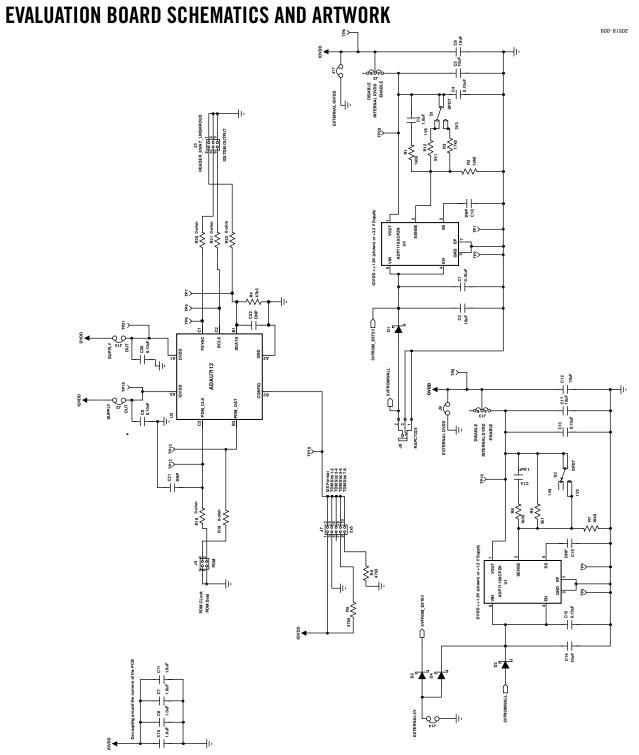

Figure 9. EVAL-ADAU7112 Schematic

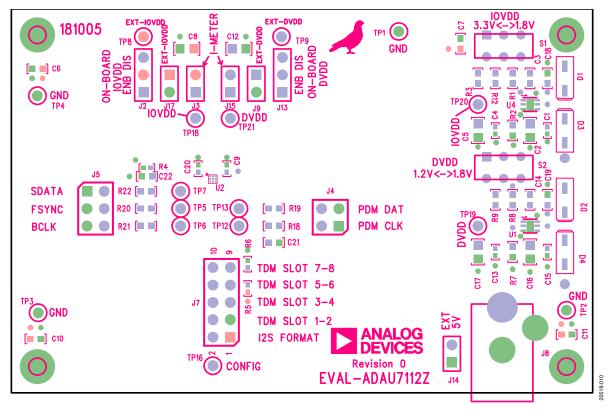

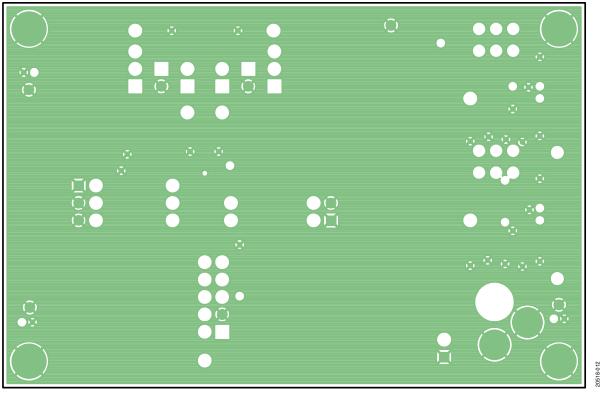

Figure 10. Top Assembly

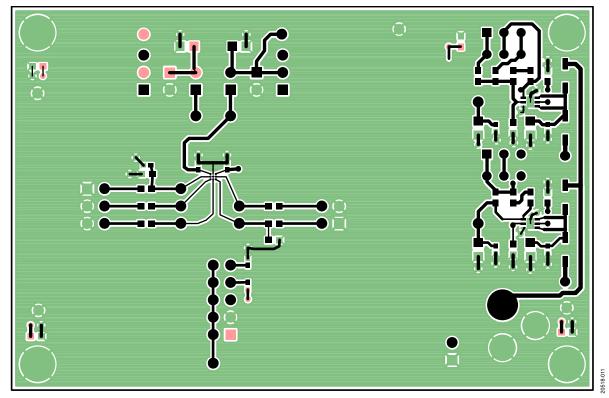

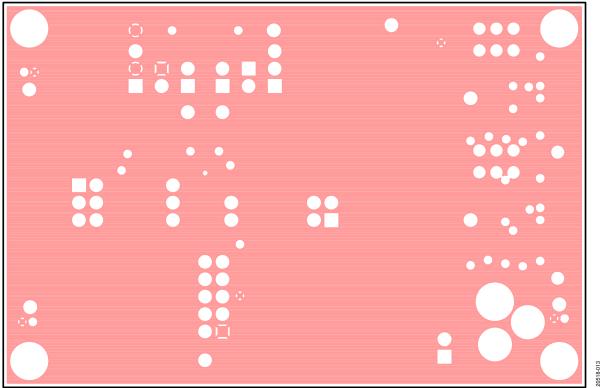

Figure 11. Top Layer, Copper

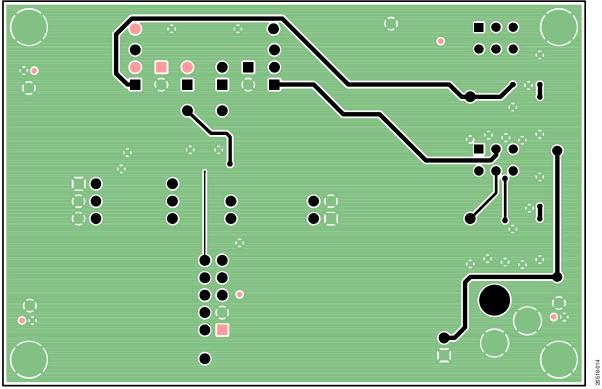

Figure 12. Layer 2, Ground

Figure 14. Bottom Layer, Copper

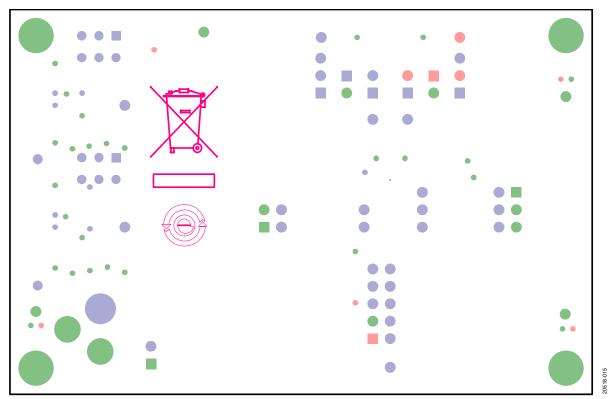

Figure 15. Bottom Assembly

### **ORDERING INFORMATION** BILL OF MATERIALS

Table 2.

|     | Reference                                        |                                                                               |                      |                            |

|-----|--------------------------------------------------|-------------------------------------------------------------------------------|----------------------|----------------------------|

| Qty | Designator                                       | Description                                                                   | Manufacturer         | Part Number                |

| 6   | C1, C4, C9,<br>C13, C15, C20                     | Multilayer ceramic capacitor (MLCC), 16 V, X7R, 0402                          | Murata ENA           | GRM155R71C104JA88D         |

| 6   | C2, C5, C8,<br>C12, C16, C17                     | MLCC, 10 V, X7R, 0805                                                         | TDK Corp             | C2012X7R1A106K125AC        |

| 6   | C3, C6, C7,<br>C10, C11, C14                     | MLCC, 16 V, X7R, 0603                                                         | Knowles Novacap      | 0603BB105K160YT            |

| 2   | C18 C19                                          | MLCC, 16 V, X7R, 0603                                                         | Knowles Novacap      | 0603BB105K160YT            |

| 1   | C22                                              | MLCC, 100 V, NP0, 0603                                                        | Murata ENA           | GRM1885C2A330JA01D         |

| 4   | D1 to D4                                         | Diode, Schottky, 30 V, 0.5 A SOD123                                           | On Semiconductor     | MBR0530T1G                 |

| 2   | J2, J13                                          | Header, SIP, 3-position                                                       | Sullins              | PBC03SAAN or cut PBC36SAAN |

| 5   | J3, J9, J14,<br>J15, J17                         | Jumper                                                                        | Sullins              | PBC02SAAN or cut PBC36SAAN |

| 1   | J4                                               | Header, unshrouded 4-way                                                      | 3M                   | PBC02DAAN or cut PBC36DAAN |

| 1   | J5                                               | Header, unshrouded, 6-way                                                     | 3M                   | PBC03DAAN or cut PBC36DAAN |

| 1   | J7                                               | Header, unshrouded 10-way                                                     | 3M                   | PBC05DAAN or cut PBC36DAAN |

| 1   | J8                                               | Power jack, mini, 0.08 inch, right angle through-hole                         | Switchcraft, Inc.    | RAPC722X                   |

| 2   | R1, R8                                           | Resistor, thick film, chip, 1%, 125 mW, 0603                                  | Panasonic EC         | ERJ-3EKF1001V              |

| 2   | R2, R7                                           | Resistor, thick film, chip, 1%, 100 mW, 0603                                  | Panasonic            | ERJ-3EKF1002V              |

| 1   | R3                                               | Resistor, thick film, chip, 1%, 100 mW, 0603                                  | Panasonic ECG        | ERJ-3EKF1782V              |

| 1   | R4                                               | Do not populate                                                               | Stackpole            | RMCF0402FT4K75             |

| 2   | R5, R6                                           | Resistor, thick film, chip, 1%, 63 mW, 0402                                   | Stackpole            | RMCF0402FT4K75             |

| 2   | R9, R12                                          | Resistor, thick film, chip, 1%, 100 mW, 0603                                  | Panasonic EC         | ERJ-3EKF5101V              |

| 9   | R14 to R22                                       | Resistor, thick film, chip, 1%, 100 mW, 0603                                  | Panasonic            | ERJ-3GEY0R00V              |

| 2   | S1, S2                                           | Switch, single-pole, double throw (SPDT), slide, PC mount                     | E-Switch             | EG1271                     |

| 17  | TP1 to TP9, TP12,<br>TP13, TP16,<br>TP18 to TP21 | Test point, mini, white, 1 inch                                               | Keystone Electronics | 5002                       |

| 2   | U1, U4                                           | Complementary metal-oxide semiconductor (CMOS) linear dropout (LDO) regulator | Analog Devices, Inc. | ADP7118ACPZN-R7            |

| 1   | U2                                               | 2-channel pulse density modulation to I <sup>2</sup> S converter              | Analog Devices       | ADAU7112                   |

### NOTES

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2019 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG20518-0-6/19(0)

www.analog.com

Rev. 0 | Page 10 of 10