# 14.2-GBPS Dual Channel, Dual Mode Linear Equalizer

Check for Samples: SN65LVCP1412

## **FEATURES**

- Dual Channel, Uni-Directional, Multi-Rate, Dual-Mode Linear Equalizer with Operation up to 14.2Gbps Serial Data Rate for Backplane and Cable Interconnects

- Linear Equalization Increases Link Margin for Systems Implementing Decision Feedback Equalizers (DFE)

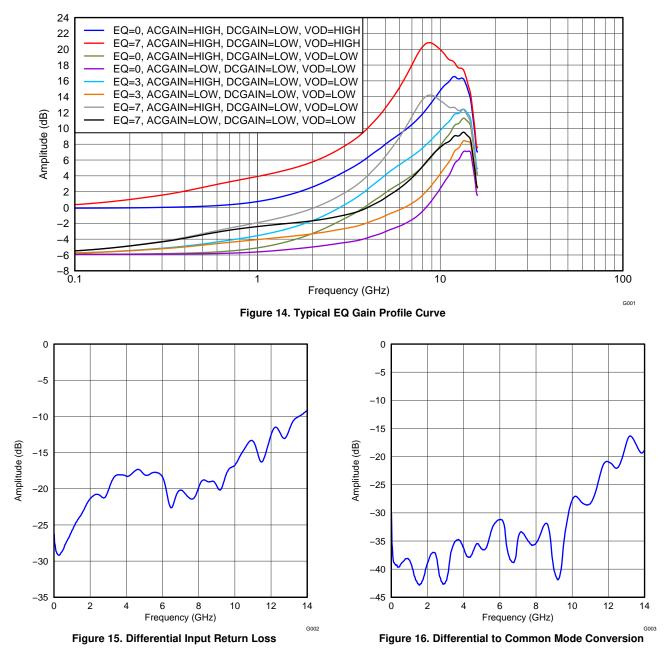

- 18dB Analog Equalization at 7.1GHz with 1dB Step Control for Backplane Mode or Cable Mode

- Output Linear Dynamic Range: 1200mV

- Bandwidth: >20GHz Typical

- Better than 15dB Return Loss at 7.1GHz

- Supports Out-of-Band (OOB) Signaling

- Low Power: Typically 75mW per Channel at 2.5V VCC

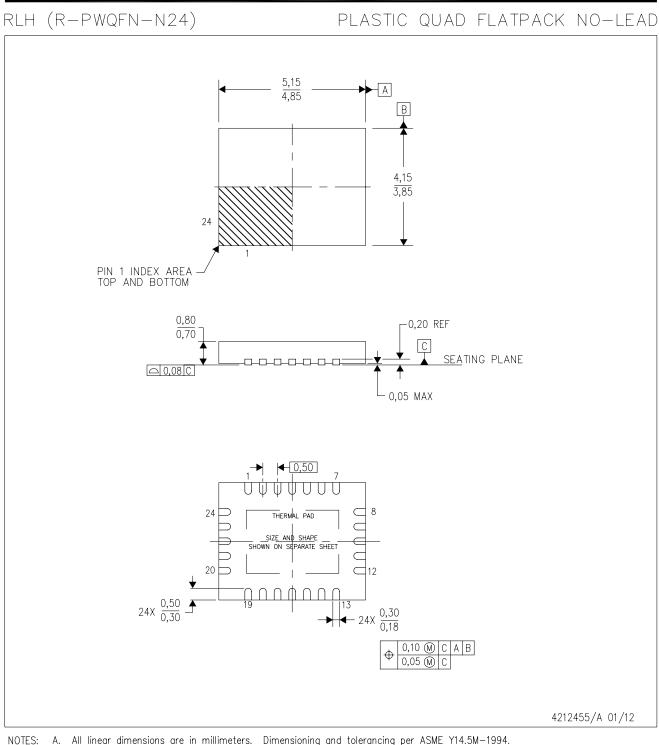

- 24-Terminal QFN (Quad Flatpack, No-Lead) 4mm x 5mm x 0.75mm; 0.5mm Terminal Pitch

- Excellent Impedance Matching to 100Ω

Differential PCB Transmission Lines

- GPIO or I<sup>2</sup>C Control

- 2.5V and 3.3V±5% Single Power Supply

- 2kV ESD (HBM)

- Flow-Through Pin-Out Provides Ease of Routing

- Small Package Size Saves Board Space

## **APPLICATIONS**

- High Speed Links in Telecommunication and Data communication

- Backplane and Cable Interconnects for 10GbE, 16GFC,10G SONET, SAS, SATA, CPRI, OBSAI, Infiniband, 10GBase-KR, and XFI/SFI

## DESCRIPTION

The SN65LVCP1412 is an asynchronous, protocol-agnostic, low latency, two-channel linear equalizer optimized for use up to 14.2Gbps and compensates for losses in backplane or active cable applications. The architecture of SN65LVCP1412 is designed to work with an ASIC or a FPGA with digital equalization employing Decision Feedback Equalizers (DFE). SN65LVCP1412 linear equalizer preserves the shape of the transmitted signal ensuring optimum DFE performance. SN65LVCP1412 provides a low power solution while at the same time extending the effectiveness of DFE.

SN65LVCP1412 is configurable via I<sup>2</sup>C or GPIO interface. Using the I<sup>2</sup>C interface of the SN65LVCP1412 enables the user to control independently the Equalization, Path Gain, and Output Dynamic Range for each individual channel. In GPIO mode, Equalization, Path Gain, and Output Dynamic Range can be set for all channels using the GPIO Input pins.

SN65LVCP1412 outputs can be disabled independently via I<sup>2</sup>C.

The SN65LVCP1412 operates from a single 2.5V or 3.3V power supply.

The package for the SN65LVCP1412 is a 24 pin 4mm x 5mm x 0.75mm QFN (Quad Flatpack, No-lead) lead-free package with 0.5mm pitch, and characterized for operation from –40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLLSED2 -SEPTEMBER 2012

TEXAS INSTRUMENTS

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

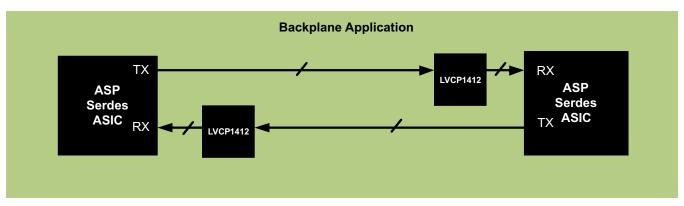

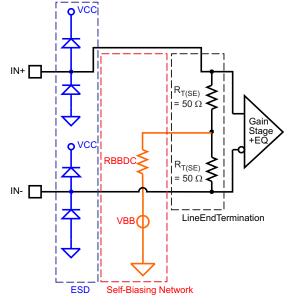

Figure 1. Typical Backplane Application – Trace Mode

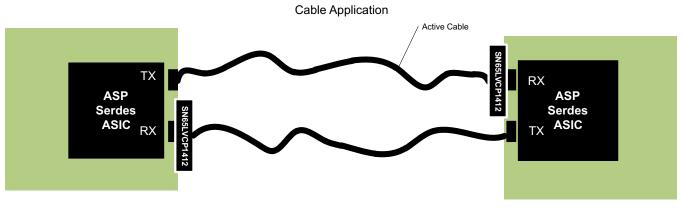

Figure 2. Typical Cable Application – Cable Mode

### BLOCK DIAGRAM (GPIO or I<sup>2</sup>C Mode)

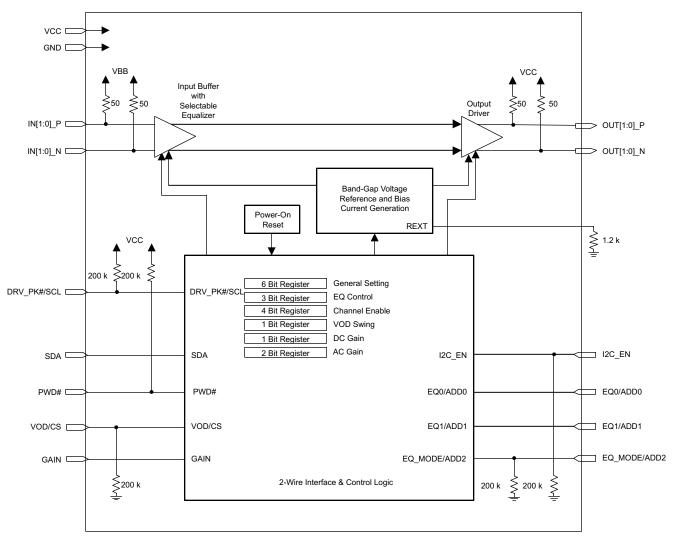

A simplified block diagram of the SN65LVCP1412 is shown in Figure 3 for GPIO or I<sup>2</sup>C input control mode. This compact, low power, 14.2Gbps dual-channel dual-mode linear analog equalizer consists of two high-speed data paths and an input GPIO pin logic-control block and a two-wire interface with a control-logic block.

Figure 3. Simplified Block Diagram of the SN65LVCP1412

SLLSED2 -SEPTEMBER 2012

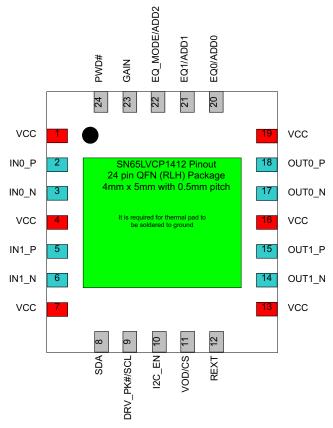

## PACKAGE

The package pin locations and assignments are shown in Figure 4. The SN65LVCP1412 is packaged in a 4mm x 5mm x 0.75mm, 24 pin, 0.5mm pitch lead-free QFN.

Figure 4. Package Drawing (Top View)

#### **PIN DESCRIPTIONS**

| PINS<br>NAME NO. |                             | DIRECTION TYPE                                            | DESCRIPTION                                                                                                                         |                                                                                                  |  |  |  |  |

|------------------|-----------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

|                  |                             | SUPPLY                                                    | DESCRIPTION                                                                                                                         |                                                                                                  |  |  |  |  |

| DIFFERENTIAL     | NIFFERENTIAL HIGH-SPEED I/O |                                                           |                                                                                                                                     |                                                                                                  |  |  |  |  |

| IN0_P<br>IN0_N   | 2<br>3                      | Input, (with 50 Ω<br>termination to input<br>common mode) | Differential input, lane 0                                                                                                          |                                                                                                  |  |  |  |  |

| IN1_P<br>IN1_N   | 5<br>6                      | Input, (with 50 Ω<br>termination to input<br>common mode) | Differential input, lane 1                                                                                                          | )ifferential input, lane 1                                                                       |  |  |  |  |

| OUT0_P<br>OUT0_N | 18<br>17                    | Output                                                    | Differential output, lane 0                                                                                                         |                                                                                                  |  |  |  |  |

| OUT1_P<br>OUT1_N | 15<br>14                    | Output                                                    | Differential output, lane 1                                                                                                         |                                                                                                  |  |  |  |  |

| CONTROL SIGN     | IALS                        | -                                                         | •                                                                                                                                   |                                                                                                  |  |  |  |  |

| SDA              | 8                           | Input Output, Open<br>drain                               | GPIO mode<br>No action needed                                                                                                       | $I^2$ C mode<br>$I^2$ C data. Connect a 10kΩ pull-up resistor externally                         |  |  |  |  |

| DRV_PK#/SCL      | 9                           | Input. (with 200kΩ<br>pull-up)                            | GPIO mode<br>HIGH: disable Driver peaking<br>LOW: enables Driver 6dB AC<br>peaking                                                  | <b>I<sup>2</sup>C mode</b><br>I <sup>2</sup> C clock. Connect a 10kΩ pull-up resistor externally |  |  |  |  |

| I2C_EN           | 10                          | Input, (wtih 200kΩ<br>pull-down)<br>2.5V/3.3V CMOS        | Configures the device operation for I <sup>2</sup> C or GPIO mode:<br>HIGH: enables I <sup>2</sup> C mode<br>LOW: enables GPIO mode |                                                                                                  |  |  |  |  |

## SN65LVCP1412 SLLSED2 -SEPTEMBER 2012

## **PIN DESCRIPTIONS (continued)**

| PIN               | S                         | DIRECTION TYPE                                      | DECODIDATION                                                        |              |                    |                                                                                                |                                                                                                                                        |  |

|-------------------|---------------------------|-----------------------------------------------------|---------------------------------------------------------------------|--------------|--------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME NO.          |                           | SUPPLY                                              | DESCRIPTION                                                         |              |                    |                                                                                                |                                                                                                                                        |  |

| VOD/CS            | 11                        | Input, (with 200kΩ<br>pull-down)<br>2.5V/3.3V CMOS  | GPIO mode<br>HIGH: set high VOD range<br>LOW: set low VOD range     |              |                    | I <sup>2</sup> C mode<br>HIGH: acts as Chip Select<br>LOW: disables I <sup>2</sup> C interface |                                                                                                                                        |  |

| REXT              | 12                        | Input, Analog                                       | External Bias F<br>1,200 Ω to GN                                    |              |                    | +                                                                                              |                                                                                                                                        |  |

| EQ0/ADD0          | 20                        | Input, 2.5V/3.3V<br>CMOS - 3-state                  | <b>GPIO mode</b><br>Working with EQ1 to determine input<br>EQ gain. |              |                    | I <sup>2</sup> C slave a                                                                       | ng with pins ADD1 and ADD2 comprise the three bits of address.<br>D1:ADD0:XXX                                                          |  |

| EQ1/ADD1          | 21                        | Input, 2.5V/3.3V<br>CMOS - 3-state                  | <b>GPIO mode</b><br>Working with E<br>EQ gain steps                 |              |                    | I <sup>2</sup> C slave a                                                                       |                                                                                                                                        |  |

|                   |                           |                                                     | EQ1                                                                 | EQ0          | EQ<br>GAIN         | ADD2:ADI                                                                                       | D1:ADD0:XXX                                                                                                                            |  |

|                   |                           |                                                     | GND                                                                 | GND          | 000                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | GND                                                                 | HiZ          | 000                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | GND                                                                 | VCC          | 001                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | HiZ                                                                 | GND          | 010                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | HiZ                                                                 | HiZ          | 011                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | HiZ                                                                 | VCC          | 100                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | VCC                                                                 | GND          | 101                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | VCC                                                                 | HiZ          | 110                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | VCC                                                                 | VCC          | 111                |                                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | EQ1 and EQ0                                                         | work with    | AC_GAIN ar         | nd DC_GAIN                                                                                     | to determine final EQ gain as this:                                                                                                    |  |

|                   |                           |                                                     | EQ1/<br>EQ0                                                         | GAIN         | DC<br>GAIN<br>(dB) | EQ GAIN<br>(dB)                                                                                |                                                                                                                                        |  |

|                   |                           |                                                     | 000 ~ 111                                                           | LOW          | -6                 | 1~9                                                                                            |                                                                                                                                        |  |

|                   |                           |                                                     | 000 ~ 111                                                           | HiZ          | -6                 | 7 ~ 17                                                                                         |                                                                                                                                        |  |

|                   |                           |                                                     | 000 ~ 111                                                           | HIGH         | 0                  | 1 ~ 9                                                                                          |                                                                                                                                        |  |

| EQ_MODE/<br>ADD2  | 22                        | Input, (with 200kΩ<br>pull-down),<br>2.5V/3.3V CMOS | GPIO mode<br>HIGH: Trace m<br>LOW: Cable m                          |              |                    | I <sup>2</sup> C slave a                                                                       | ng with pins ADD1 and ADD0 comprise the three bits of address.<br>D1:ADD0:XXX                                                          |  |

| GAIN              | 23                        | Input, 2.5V/3.3V<br>CMOS - 3-state                  | GPIO mode<br>Work with EQ1<br>Gain. See table                       |              | et total EQ        | I <sup>2</sup> C mode<br>No action needed                                                      |                                                                                                                                        |  |

| PWD#              | 24                        | Input, (with 200kΩ<br>pull-up),<br>2.5V/3.3V CMOS   | HIGH: Normal<br>LOW: Powers                                         | •            | device, input      | s off and out                                                                                  | puts disabled, resets I <sup>2</sup> C                                                                                                 |  |

| POWER SUPP        | LY                        |                                                     |                                                                     |              |                    |                                                                                                |                                                                                                                                        |  |

| VCC               | 1, 4, 7,<br>13, 16,<br>19 | Power                                               | Power supply 2                                                      | 2.5V±5%, 3   | 3.3V±5%            |                                                                                                |                                                                                                                                        |  |

| GND Center<br>Pad |                           | Ground                                              | the GND plane                                                       | . At least 9 | 9 PCB vias a       | ire recomme                                                                                    | bottom of the package. This pad must be connected to<br>nded to minimize inductance and provide a solid<br>age) for the via placement. |  |

SLLSED2 -SEPTEMBER 2012

**EXAS**

www.ti.com

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                               |                                                                          | VALUES                                  | UNIT |

|-----------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------|------|

| V <sub>CC</sub>                               | Supply voltage range <sup>(2)</sup>                                      | -0.3 to 4                               | V    |

| V <sub>IN,DIFF</sub>                          | Differential Voltage between INx_P and INx_N                             | ±2.5                                    | V    |

| V <sub>IN+, IN</sub>                          | Voltage at Inx_P and fINx_N                                              | -0.5 V to VCC+0.5                       | V    |

| V <sub>IO</sub>                               | Voltage on Control IO pins                                               | -0.5 V to VCC+0.5                       | V    |

| I <sub>IN+</sub> I <sub>IN-</sub>             | Continuous Current at high speed differential data inputs (differential) | -25 to 25                               | mA   |

| I <sub>OUT+</sub> I <sub>OUT-</sub>           | Continuous Current at high speed differential data outputs               | -25 to 25                               | mA   |

|                                               | Human Body Model <sup>(3)</sup> (All Pins)                               | 2.0                                     | kV   |

| ESD                                           | Charged-Device Model <sup>(4)</sup> (All Pins)                           | 500                                     | V    |

| Moisture Sen                                  | sitivity level                                                           | 2                                       |      |

| Shelf Life Conditions In Moisture Barrier Bag |                                                                          | 24 Months at <40°C and <90%<br>Humidity |      |

| Reflow Temp                                   | erature package soldering, 4 sec                                         | 260                                     | °C   |

|                                               |                                                                          |                                         |      |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

(3) Tested in accordance with JEDEC Standard 22, Test Method A114-A.

(4) Tested in accordance with JEDEC Standard 22, Test Method C101.

### THERMAL INFORMATION

|                    | THERMAL METRIC <sup>(1)</sup>                               | SN65LVCP1412  |                |

|--------------------|-------------------------------------------------------------|---------------|----------------|

|                    |                                                             | RLH (24 PINS) | UNITS          |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 34.7          |                |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 33.8          |                |

| $\theta_{JB}$      | Junction-to-board thermal resistance <sup>(4)</sup>         | 12.5          | 0 <b>0</b> 1 M |

| $\Psi_{JT}$        | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.50          | °C/W           |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter <sup>(6)</sup> | 12.5          |                |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 2.00          |                |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## **RECOMMENDED OPERATING CONDITIONS**

|                  |                           | MIN                  | NOM | MAX                  | UNIT |

|------------------|---------------------------|----------------------|-----|----------------------|------|

| dR               | Operating Data Rate       |                      |     | 14.2                 | Gbps |

| V <sub>CC</sub>  | Supply voltage            | 2.375                | 2.5 | 2.625                | V    |

| V <sub>CC</sub>  | Supply voltage            | 3.135                | 3.3 | 3.465                | V    |

| тс               | Junction temperature      | -10                  |     | 125                  | °C   |

| ТВ               | Maximum board temperature |                      |     | 85                   | °C   |

| CMOS DC S        | SPECIFICATIONS            | ·                    |     |                      |      |

| V <sub>IH</sub>  | High-level input voltage  | 0.8×V <sub>CC</sub>  |     |                      | V    |

| V <sub>MID</sub> | Mid-level input voltage   | V <sub>CC</sub> ×0.4 |     | V <sub>CC</sub> ×0.6 | V    |

| V <sub>IL</sub>  | Low-level input voltage   | -0.5                 |     | $0.2 \times V_{CC}$  | V    |

| PSNR BG          | Bandgap Circuit PSNR      | 20                   |     |                      | dB   |

## ELECTRICAL CHARACTERISTICS (VCC 2.5V ±5%)

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

| PARAMETER         |                                               | TEST CONDITIONS                                                      | MIN TYP <sup>(1)</sup> | MAX | UNIT |

|-------------------|-----------------------------------------------|----------------------------------------------------------------------|------------------------|-----|------|

| POWER             | CONSUMPTION                                   |                                                                      |                        |     |      |

| $PD_L$            | Device power dissipation                      | VOD = LOW at 2.5V VCC with all 4 channels active.                    | 150                    | 250 | mW   |

| PD <sub>H</sub>   | Device power dissipation                      | VOD = HIGH, at 2.5V VCC with all 4 channels active.                  | 225                    | 400 | mW   |

| PD <sub>OFF</sub> | Device power with all 4 channels switched off | Refer to I <sup>2</sup> C section for device configuration. 2.5V VCC | 5                      |     | mW   |

(1) All typical values are at 25°C and with 2.5V supply unless otherwise noted.

## ELECTRICAL CHARACTERISTICS (VCC 3.3V ±5%)

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

| PARAMETER         |                                               | TEST CONDITIONS                                            |  | <b>TYP</b> <sup>(1)</sup> | MAX | UNIT |

|-------------------|-----------------------------------------------|------------------------------------------------------------|--|---------------------------|-----|------|

| POWER             | CONSUMPTION                                   |                                                            |  |                           |     |      |

| $PD_L$            | Device power dissipation                      | VOD = LOW at 3.3V VCC with all 4 channels active.          |  | 225                       | 375 | mW   |

| $PD_{H}$          | Device power dissipation                      | VOD = HIGH, at 3.3V VCC with all 4 channels active.        |  | 330                       | 525 | mW   |

| PD <sub>OFF</sub> | Device power with all 4 channels switched off | Refer to $I^2C$ section for device configuration. 3.3V VCC |  | 5                         |     | mW   |

(1) All typical values are at 25°C and with 2.5V supply unless otherwise noted.

## ELECTRICAL CHARACTERISTICS (VCC 2.5V ±5%, 3.3V ±5%)

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

| PARAMETER       |                                                 | TEST CONDITIONS           | MIN | <b>TYP</b> <sup>(1)</sup> | MAX | UNIT             |  |  |  |

|-----------------|-------------------------------------------------|---------------------------|-----|---------------------------|-----|------------------|--|--|--|

| CMOS DO         | CMOS DC SPECIFICATIONS                          |                           |     |                           |     |                  |  |  |  |

| I <sub>IH</sub> | High level input current                        | $VIN = 0.9 \times V_{CC}$ | -40 | 17                        | 40  | μA               |  |  |  |

| I <sub>IL</sub> | Low level input current                         | $VIN = 0.1 \times V_{CC}$ | -40 | 17                        | 40  | μA               |  |  |  |

| CML INP         | CML INPUTS (IN[3:0]_P, IN[3:0]_N)               |                           |     |                           |     |                  |  |  |  |

| r <sub>IN</sub> | Differential input resistance                   | INx_P to INx_N            |     | 100                       |     | Ω                |  |  |  |

| V <sub>IN</sub> | Input linear dynamic range                      | Gain = 0.5                |     | 1200                      |     | mV <sub>pp</sub> |  |  |  |

| VICM            | Input common mode voltage                       | Internally biased         |     | V <sub>CC</sub> -0.8      |     | V                |  |  |  |

| SCD11           | Input differential to common mode<br>conversion | 100MHz to 7.1GHz          |     | -20                       |     | dB               |  |  |  |

| SDD11           | Differential input return loss                  | 100MHz to 7.1GHz          |     | -15                       |     | dB               |  |  |  |

(1) All typical values are at 25°C and with 2.5V and 3.3V supply unless otherwise noted.

SLLSED2 -SEPTEMBER 2012

## ELECTRICAL CHARACTERISTICS (VCC 2.5V ±5%, 3.3V ±5%) (continued)

over operating free-air temperature range. All parameters are referenced to package pins. (unless otherwise noted)

|                      | PARAMETER                                                                     | TEST CONDITIONS                                                                                                                                                                | MIN | <b>TYP</b> <sup>(1)</sup> | MAX | UNIT                        |

|----------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|-----|-----------------------------|

|                      | PUTS (OUT[3:0]_P, OUT[3:0]_N)                                                 |                                                                                                                                                                                |     |                           |     |                             |

| M                    | Output linear dunamia range                                                   | $R_L = 100 \Omega$ , $V_{OD} = HIGH$                                                                                                                                           |     | 1200                      |     | mV <sub>pp</sub>            |

| V <sub>OD</sub>      | Output linear dynamic range                                                   | $R_L = 100 \Omega, V_{OD} = LOW$                                                                                                                                               |     | 600                       |     | mV <sub>pp</sub>            |

| V <sub>OS</sub>      | Output offset voltage                                                         | $R_L = 100 \Omega, 0 V$ applied at inputs                                                                                                                                      |     | 10                        |     | mV <sub>pp</sub>            |

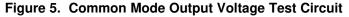

| V <sub>OCM</sub>     | Output common mode voltage                                                    | See Figure 5                                                                                                                                                                   |     | V <sub>CC</sub> -0.4      |     | V                           |

| V <sub>CM,RIP</sub>  | Common mode output ripple                                                     | K28.5 pattern at 14.2Gbps on all 4 channels,<br>no interconnect loss, VOD = HIGH                                                                                               |     | 10                        | 20  | mV <sub>RMS</sub>           |

| V <sub>OD,RIP</sub>  | Differential path output ripple                                               | K28.5 pattern at 14.2Gbps on all channels,<br>no interconnect loss, VIN = 1200mVpp.                                                                                            |     |                           | 20  | $\mathrm{mV}_{\mathrm{pp}}$ |

| V <sub>OC(SS)</sub>  | Change in steady-state common-<br>mode output voltage between logic<br>states |                                                                                                                                                                                |     | ±10                       |     | mV                          |

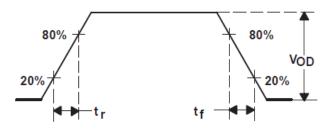

| t <sub>R</sub>       | Rise time <sup>(2)</sup>                                                      | Input signal with 30ps rise time. 20% to 80%. See Figure 7                                                                                                                     |     | 31                        |     | ps                          |

| t <sub>F</sub>       | Fall time <sup>(2)</sup>                                                      | Input signal with 30ps fall time. 20% to 80%. See Figure 7                                                                                                                     |     | 32                        |     | ps                          |

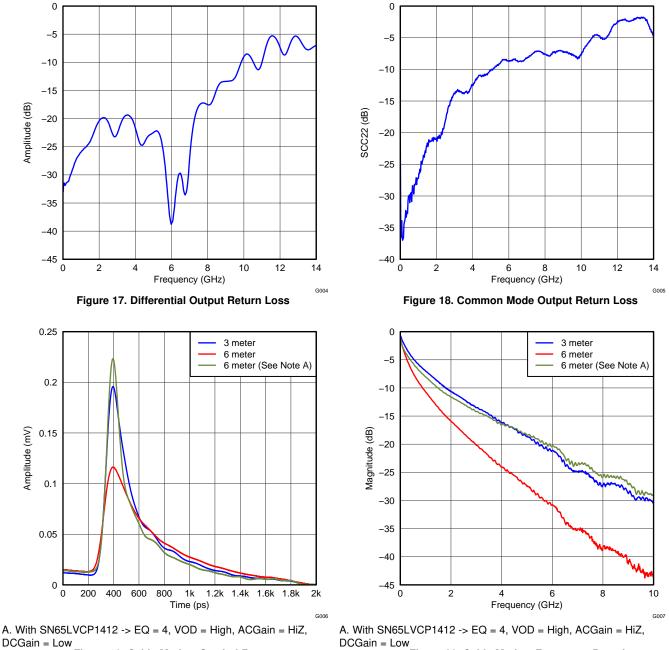

| SDD22                | Differential output return loss                                               | 100MHz to 7.1GHz                                                                                                                                                               |     | -15                       |     | dB                          |

| SCC22                | Common-mode output return loss                                                | 100MHz to 7.1GHz                                                                                                                                                               |     | -8                        |     | dB                          |

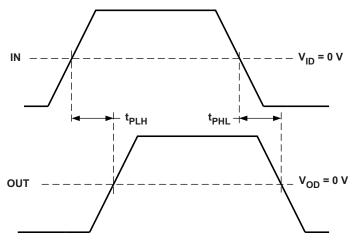

| t <sub>PLH</sub>     | Low-to-high propagation delay                                                 |                                                                                                                                                                                |     | 65                        |     | ps                          |

| t <sub>PHL</sub>     | High-to-low propagation delay                                                 | See Figure 6                                                                                                                                                                   |     | 65                        |     | ps                          |

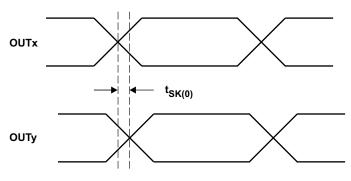

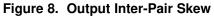

| t <sub>SK(O)</sub>   | Inter-Pair (lane to lane) output skew <sup>(3)</sup>                          | All outputs terminated with 100 $\Omega$ , See Figure 8                                                                                                                        |     | 3                         |     | ps                          |

| t <sub>SK(PP)</sub>  | Part-to-part skew <sup>(4)</sup>                                              | All outputs terminated with 100 $\Omega$                                                                                                                                       |     | -                         | 50  | ps                          |

| r <sub>ot</sub>      | Single ended output resistance                                                | Single ended on-chip termination to VCC. Outputs will be AC coupled.                                                                                                           |     | 50                        |     | Ω                           |

| r <sub>OM</sub>      | Output termination mismatch at 1MHz                                           | $\Delta rom = 2 \times \frac{rp - rn}{rp + rn} \times 100$                                                                                                                     |     | 5                         |     | %                           |

| Ch <sub>iso</sub>    | Channel-to-channel isolation                                                  | Frequency at 7.1GHz                                                                                                                                                            | 35  | 45                        |     | dB                          |

|                      |                                                                               | 10MHz to 7.1GHz. No other noise source present. VOD = LOW                                                                                                                      |     | 400                       |     | μVRMS                       |

| OUT <sub>NOISE</sub> | Output referred noise <sup>(5)</sup>                                          | 10MHz to 7.1GHz. No other noise source present. VOD = HIGH                                                                                                                     |     | 500                       |     | μVRMS                       |

| EQUALIZA             | TION                                                                          |                                                                                                                                                                                |     |                           |     |                             |

| EQ <sub>Gain</sub>   | At 7.1GHz input signal                                                        | Equalization Gain, EQ = MAX                                                                                                                                                    | 15  | 18                        |     | dB                          |

| Vpre                 | Output pre-cursor pre-emphasis                                                | Input signal with 3.75 pre-cursor and measure it on the output<br>signal,<br>Refer Figure 9. Vpre = 20log(V3/V2)                                                               |     | 3.75                      |     | dB                          |

| Vpst                 | Output post-cursor pre-emphasis                                               | Input signal with 12dB post-cursor and measure it on the output signal,<br>Refer Figure 9. Vpst = 20log(V1/V2)                                                                 |     | 12                        |     | dB                          |

| DJ1                  | Residual deterministic jitter at 10.3125<br>Gbps                              | Transmit Side application<br>Tx launch Amplitude = 0.6Vpp, EQ=0, ACGain and DCgain =<br>Low and VOD = High, Trace Mode Test Channel -> 0". See<br>Figure 11                    |     | 0.016                     |     | Ulp-p                       |

| DJ2                  | Residual deterministic jitter at 10.3125<br>Gbps                              | Receive Side Application<br>Tx launch Amplitude = 0.6Vpp, EQ=7, ACGain and VOD = High<br>and DCGain = High, Trace Mode Test Channel -> 12" (9dB loss<br>at 5GHz) See Figure 10 |     | 0.11                      |     | Ulp-p                       |

| DJ3                  | Residual Deterministic Jitter at 14.2<br>Gbps                                 | Transmit Side Application<br>Tx launch Amplitude = 0.6Vpp, EQ=0, ACGain and DCgain =<br>Low and VOD = High, Trace Mode Test Channel -> 0". See<br>Figure 11                    |     | 0.041                     |     | Ulp-p                       |

| DJ4                  | Residual Deterministic Jitter at 14.2<br>Gbps                                 | Receive Side Application<br>Tx launch Amplitude = 0.6Vpp, EQ=7, ACGain and VOD = High<br>and DCGain = High, Trace Mode Test Channel -> 8" (9dB loss<br>at 7GHz) See Figure 10  |     | 0.13                      |     | Ulp-p                       |

Rise and Fall measurements include board and channel effects of the test environment, refer to Figure 10 and Figure 11  $t_{SK(O)}$  is the magnitude of the time difference between the channels.  $t_{SK(PP)}$  is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices (2) (3) (4) operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

All noise sources added. (5)

#### PARAMETER MEASUREMENT INFORMATION

Figure 6. Propagation Delay Input to Output

Figure 7. Output Rise and Fall Time

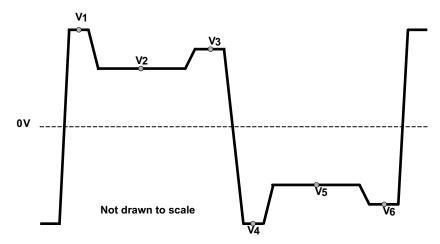

Figure 10. Receive Side Performance Test Circuit

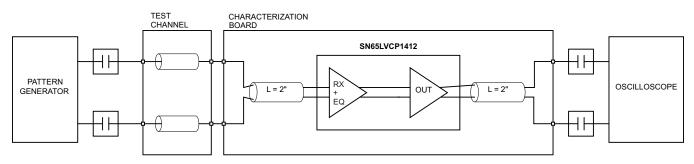

Figure 11. Transmit Side Performance Test Circuit

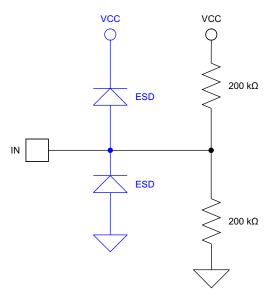

## EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

#### Figure 12. Equivalent Input Circuit Design

Figure 13. 3-Level Input Biasing Network

www.ti.com

STRUMENTS

XAS

#### **TYPICAL CHARACTERISTICS**

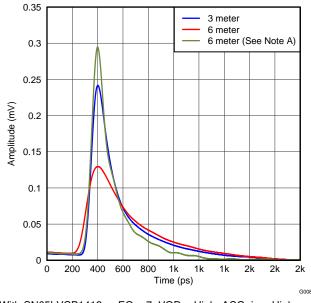

Typical operating condition is at  $V_{CC} = 2.5V$  and  $T_A = 25^{\circ}C$ , no interconnect line at the output, and with default device settings (unless otherwise noted).

#### **TYPICAL CHARACTERISTICS (continued)**

Typical operating condition is at  $V_{CC} = 2.5V$  and  $T_A = 25^{\circ}C$ , no interconnect line at the output, and with default device settings (unless otherwise noted).

SN65LVCP1412 SLLSED2 -SEPTEMBER 2012 Texas Instruments

www.ti.com

Typical operating condition is at  $V_{CC}$  = 2.5V and  $T_A$  = 25°C, no interconnect line at the output, and with default device settings (unless otherwise noted).

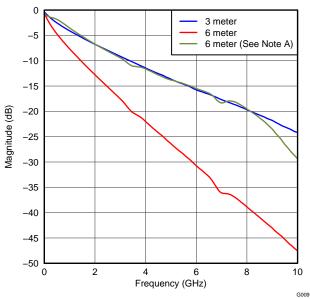

A. With SN65LVCP1412 -> EQ = 7, VOD = High, ACGain = High, DCGain = Low Figure 22. Trace Mode - Frequency Domain

| MODE | DCGAIN | ACGAIN<1:0> | EQ<2:0>    | DC GAIN (dB) | EQ GAIN<br>(dB) | APPLICATION                             |

|------|--------|-------------|------------|--------------|-----------------|-----------------------------------------|

| 0    | 0      | 00          | 000 to 111 | -6           | 1 to 9          | Short Input Trace; Large Input Swing    |

| 0    | 0      | 11          | 000 to 111 | -6           | 7 to 17         | Long Input Trace; Large Input<br>Swing  |

| 0    | 1      | 01          | 000 to 111 | 0            | 1 to 9          | Short Input Trace; Small Input Swing    |

| 0    | 1      | 11          | 000 to 111 | 0            | 2 to 10         | Short Input Trace; Small Input<br>Swing |

| 1    | 0      | 00          | 000 to 111 | -6           | 1 to 9          | Short Input Cable; Large Input Swing    |

| 1    | 0      | 11          | 000 to 111 | -6           | 7 to 17         | Long Input Cable; Large Input<br>Swing  |

| 1    | 1      | 01          | 000 to 111 | 0            | 1 to 9          | Short Input Cable; Small Input<br>Swing |

| 1    | 1      | 11          | 000 to 111 | 0            | 2 to 10         | Short Input Cable; Small Input Swing    |

#### **Table 1. Control Settings Descriptions**

#### **Table 2. Control Settings Descriptions**

| GAIN  | DC GAIN | ACGAIN<1:0> |

|-------|---------|-------------|

| Low   | 0       | 00          |

| HighZ | 0       | 11          |

| High  | 1       | 01          |

### TWO-WIRE SERIAL INTERFACE AND CONTROL LOGIC

The SN65LVCP1412 uses a 2-wire serial interface for digital control. The two circuit inputs, SDA and SCL, are driven, respectively, by the serial data and serial clock from a microcontroller, for example. The SDA and SCK pins require external  $10k\Omega$  pull-ups to VCC.

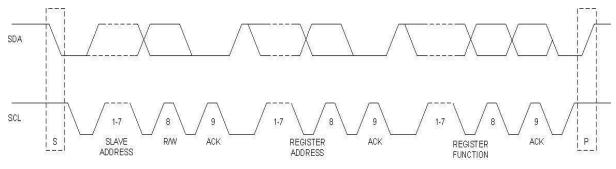

The 2-wire interface allows write access to the internal memory map to modify control registers and read access to read out control and status signals. The SN65LVCP1412 is a slave device only which means that it cannot initiate a transmission itself; it always relies on the availability of the SCK signal for the duration of the transmission. The master device provides the clock signal as well as the START and STOP commands. The protocol for a data transmission is as follows:

- 1. START command

- 2. 7 bit slave address (0000ADD[2:0]) followed by an eighth bit which is the data direction bit (R/W). A zero indicates a WRITE and a 1 indicates a READ. The ADD[2:0] address bits change with the status of the ADD2, ADD1, and ADD0 device pins, respectively. If the pins are left floating or pulled down, the 7 bit slave address is 0000000.

- 3. 8 bit register address

- 4. 8 bit register data word

- 5. STOP command

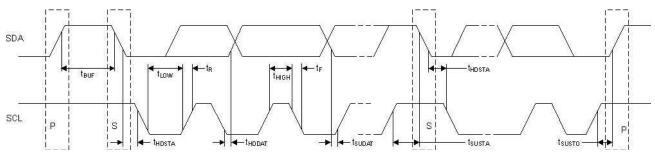

Regarding timing, the SN65LVCP1412 is I<sup>2</sup>C compatible. The typical timing is shown in Figure 9 and a complete data transfer is shown in Figure 10. Parameters for Figure 9 are defined in Table 3.

Bus Idle: Both SDA and SCL lines remain HIGH

**Start Data Transfer:** A change in the state of the SDA line, from HIGH to LOW, while the SCL line is HIGH, defines a START condition (S). Each data transfer is initiated with a START condition.

**Stop Data Transfer:** A change in the state of the SDA line from LOW to HIGH while the SCL line is HIGH defines a STOP condition (P). Each data transfer is terminated with a STOP condition; however, if the master still wishes to communicate on the bus, it can generate a repeated START condition and address another slave without first generating a STOP condition.

Data Transfer: The number of data bytes transferred between a START and a STOP condition is not limited and is determined by the master device. The receiver acknowledges the transfer of data.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge bit. The transmitter releases the SDA line and a device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge the slave address, the data line must be taken into account. When a slave-receiver doesn't acknowledge the slave address, the data line must be left HIGH by the slave. The master can then generate a STOP condition to abort the transfer. If the slave-receiver does acknowledge the slave address but some time later in the transfer cannot receive any more data bytes, the master must abort the transfer. This is indicated by the slave generating the not acknowledge on the first byte to follow. The slave leaves the data line HIGH and the master generates the STOP condition.

Figure 23. Two-wire Serial Interface Timing Diagram

SLLSED2 -SEPTEMBER 2012

www.ti.com

Texas Instruments

| SYMBOL             | PARAMETER                                                                                       | MIN | МАХ | UNIT |

|--------------------|-------------------------------------------------------------------------------------------------|-----|-----|------|

| f <sub>SCL</sub>   | SCL clock frequency                                                                             |     | 400 | kHz  |

| t <sub>BUF</sub>   | Bus free time between START and STOP conditions                                                 | 1.3 |     | μs   |

| t <sub>HDSTA</sub> | Hold time after repeated START condition. After this period, the first clock pulse is generated | 0.6 |     | μs   |

| t <sub>LOW</sub>   | Low period of the SCL clock                                                                     | 1.3 |     | μs   |

| t <sub>HIGH</sub>  | High period of the SCL clock                                                                    | 0.6 |     | μs   |

| t <sub>SUSTA</sub> | Setup time for a repeated START condition                                                       | 0.6 |     | μs   |

| t <sub>HDDAT</sub> | Data HOLD time                                                                                  | 0   |     | μs   |

| t <sub>SUDAT</sub> | Data setup time                                                                                 | 100 |     | ns   |

| t <sub>R</sub>     | Rise time of both SDA and SCL signals                                                           |     | 300 | ns   |

| t <sub>F</sub>     | Fall time of both SDA and SCL signals                                                           |     | 300 | ns   |

| t <sub>susto</sub> | Setup time for STOP condition                                                                   | 0.6 |     | μs   |

Figure 24. Two-wire Serial Interface Data Transfer

### **REGISTER MAPPING**

The register mapping for read/write register addresses 0 (0x00) through 22 (0x18) are shown in Table 4. Table 5 describes the circuit functionality based on the register settings.

#### Table 4. SN65LVCP1412 Register Mapping Information

|               |                   |                  |       | • • •    | •           |           |          |

|---------------|-------------------|------------------|-------|----------|-------------|-----------|----------|

| Register 0x00 | (General Device S | ettings) R/W     |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

| RSVD          | PWRDOWN           | SYNC_01          | RSVD  | SYNC_ALL | EQ_MODE     |           | RSVD     |

| Register 0x01 | (Channel Enable)  | R/W              |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

|               |                   |                  |       |          | LN_EN_CH1   | LN_EN_CH0 |          |

| Register 0x05 | (Channel 0 Contro | ol Settings) R/W |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

| RSVD          | EQ2               | EQ1              | EQ0   | VOD_CTRL | DC_GAIN     | AC_GAIN1  | AC_GAIN0 |

| Register 0x06 | (Channel 0 Enable | e Settings) R/W  |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

|               |                   |                  |       |          | DRV_PEAK    | EQ_EN     | DRV_EN   |

| Register 0x08 | (Channel 1 Contro | ol Settings) R/W |       |          |             |           |          |

| bit 7         | bit 6             | 6 bit 5 bit 4    |       | bit 3    | bit 2 bit 1 |           | bit 0    |

| RSVD          | EQ2               | EQ1              | EQ0   | VOD_CTRL | DC_GAIN     | AC_GAIN1  | AC_GAIN0 |

| Register 0x09 | (Channel 1 Enable | e Settings) R/W  |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

|               |                   |                  |       |          | DRV_PEAK    | EQ_EN     | DRV_EN   |

| Register 0x0F | Read Only         |                  |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

| RSVD          | RSVD              | RSVD             | RSVD  | RSVD     | RSVD        | RSVD      | RSVD     |

| Register 0x11 | R/W               |                  |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

|               | RSVD              |                  |       |          |             |           |          |

| Register 0x12 | R/W               |                  |       |          |             |           |          |

| bit 7         | bit 6             | bit 5            | bit 4 | bit 3    | bit 2       | bit 1     | bit 0    |

| RSVD          |                   |                  |       |          |             |           |          |

## Table 5. SN65LVCP1412 Register Description

| REGISTER | BIT                  | SYMBOL   | FUNCTION                                                                                                                                          | DEFAULT  |  |

|----------|----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|          | 7                    | RSVD     | Fot TI use only                                                                                                                                   |          |  |

|          | 6                    | PWRDOWN  | Power down the device:<br>0 = Normal operation<br>1 = Powerdown                                                                                   |          |  |

|          | 5                    | SYNC_01  | All settings from channel 1 will be used for channel 0 and 1:<br>0 = channel 0 tracking channel 1 settings<br>1 = no tracking tracking            |          |  |

|          | 4 RSVD<br>3 SYNC_ALL | RSVD     | For TI use only                                                                                                                                   |          |  |

| 0x00     |                      | SYNC_ALL | All settings from channel 1 will be used on all channels:<br>0 = all channels tracking channel 1<br>1 = no channel tracking<br>Overwrites SYNC_01 | 00000000 |  |

|          | 2                    | EQ_MD    | Set EQ Mode:<br>0 = Cable Mode<br>1 = Trace Mode                                                                                                  |          |  |

|          | 1                    |          |                                                                                                                                                   |          |  |

|          | 0                    | RSVD     | For TI use only                                                                                                                                   |          |  |

SLLSED2 -SEPTEMBER 2012

www.ti.com

NSTRUMENTS

Texas

| REGISTER     | BIT            | SYMBOL        | FUNCTION                                                                                        | DEFAULT  |

|--------------|----------------|---------------|-------------------------------------------------------------------------------------------------|----------|

|              | 7              |               |                                                                                                 |          |

|              | 6              |               |                                                                                                 |          |

|              | 5              |               |                                                                                                 |          |

|              | 4              |               |                                                                                                 |          |

|              | 3              |               |                                                                                                 |          |

| 0x01         | 2              | LN_EN_CH1     | Channel 1 Enable:<br>0 = Enable<br>1 = Disable                                                  | 0000000  |

|              | 1              | LN_EN_CH0     | Channel 0 Enable:<br>0 = Enable<br>1 = Disable                                                  |          |

|              | 0              |               |                                                                                                 |          |

|              | 7              | RSVD          |                                                                                                 |          |

|              | 6              | EQ2           | Equalizer Adjustment Setting                                                                    |          |

|              | 5              | EQ1           | 000 = Minimum equalization setting                                                              |          |

|              | 4              | EQ0           | 111 = Maximum equalization setting                                                              |          |

| 0x05         | 3              | VOD_CTRL      | Channel [x] VOD control:<br>0 = low VOD range<br>1 = high VOD range                             | 00000000 |

| 0x08         | 2 DC_GAIN_CTRL |               | Channel [x] EQ DC Gain:<br>0 = set EQ DC Gain to 0.5x<br>1 = set EQ DC Gain to 1x               |          |

|              | 1              | AC_GAIN_CTRL1 | AC Gain Control:                                                                                |          |

|              | 0              | AC_GAIN_CTRL0 | 00 = Low<br>01 = HiZ<br>11 = High                                                               |          |

|              | 7              |               |                                                                                                 |          |

|              | 6              |               |                                                                                                 |          |

|              | 5              |               |                                                                                                 |          |

|              | 4              |               |                                                                                                 |          |

|              | 3              |               |                                                                                                 |          |

| 0x06<br>0x09 | 2              | DRV_PEAK      | Channel [x] Driver Peaking:<br>0 = disables driver Peaking<br>1 = enables driver 6db AC Peaking | 00000000 |

|              | 1 EQ_EN        |               | Channel [x] EQ stage enable:<br>0 = Enable<br>1 = Disable                                       |          |

|              | 0              | DRV_EN        | Channel [x] Driver stage enable:<br>0 = Enable<br>1 = Disable                                   |          |

|              | 7              | RSVD          | For TI use only                                                                                 |          |

|              | 6              | RSVD          | For TI use only                                                                                 |          |

|              | 5              | RSVD          | For TI use only                                                                                 |          |

| 005          | 4              | RSVD          | For TI use only                                                                                 | 00110000 |

| 0x0F         | 3              | RSVD          | For TI use only                                                                                 | 00110000 |

|              | 2              | RSVD          | For TI use only                                                                                 |          |

|              | 1              | RSVD          | For TI use only                                                                                 |          |

|              | 0              | RSVD          | For TI use only                                                                                 |          |

## Table 5. SN65LVCP1412 Register Description (continued)

SLLSED2 -SEPTEMBER 2012

www.ti.com

## Table 5. SN65LVCP1412 Register Description (continued)

| REGISTER | BIT | SYMBOL | FUNCTION        | DEFAULT  |

|----------|-----|--------|-----------------|----------|

|          | 7   |        |                 |          |

|          | 6   | RSVD   | For TI use only |          |

|          | 5   |        |                 |          |

| 0x11     | 4   |        |                 | 00000000 |

| UXII     | 3   |        |                 | 0000000  |

|          | 2   |        |                 |          |

|          | 1   |        |                 |          |

|          | 0   |        |                 |          |

|          | 7   | RSVD   | For TI use only |          |

|          | 6   |        |                 |          |

|          | 5   |        |                 |          |

| 0x12     | 4   |        |                 | 00000000 |

| 0.012    | 3   |        |                 | 0000000  |

|          | 2   |        |                 |          |

|          | 1   |        |                 |          |

|          | 0   |        |                 |          |

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| SN65LVCP1412RLHR | ACTIVE        | WQFN         | RLH                | 24   | 3000           | RoHS & Green    | (6)<br>NIPDAU                 | Level-2-260C-1 YEAR  | -40 to 85    | LVCP<br>1412            | Samples |

| SN65LVCP1412RLHT | ACTIVE        | WQFN         | RLH                | 24   | 250            | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR  | -40 to 85    | LVCP<br>1412            | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

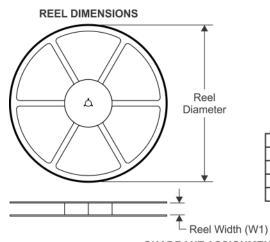

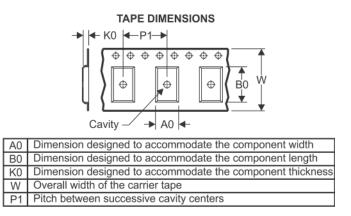

### TAPE AND REEL INFORMATION

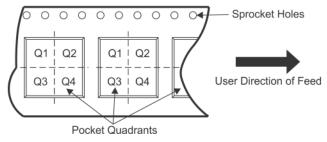

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| SN65LVCP1412RLHR            | WQFN            | RLH                | 24 | 3000 | 330.0                    | 12.4                     | 4.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

| SN65LVCP1412RLHT            | WQFN            | RLH                | 24 | 250  | 330.0                    | 12.4                     | 4.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

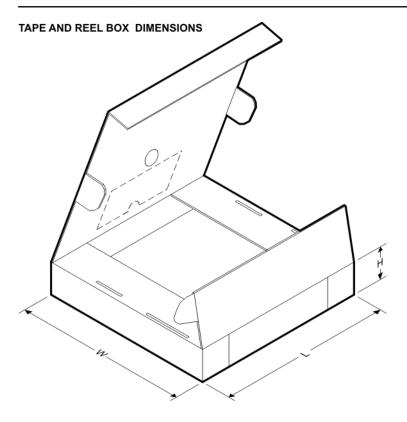

# PACKAGE MATERIALS INFORMATION

15-Feb-2019

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65LVCP1412RLHR | WQFN         | RLH             | 24   | 3000 | 367.0       | 367.0      | 38.0        |

| SN65LVCP1412RLHT | WQFN         | RLH             | 24   | 250  | 367.0       | 367.0      | 38.0        |

# **MECHANICAL DATA**

A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) Package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

F. Falls within JEDEC MO-220.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated