SBAS022D - NOVEMBER 1992 - REVISED NOVEMBER 2006

# Low-Power, 16-Bit, Sampling CMOS ANALOG-to-DIGITAL CONVERTER

## **FEATURES**

- 35mW max POWER DISSIPATION

- 50µW POWER-DOWN MODE

- 25µs max ACQUISITION AND CONVERSION

- ±1.5LSB max INL

- DNL: 16 Bits, No Missing Codes

- 86dB min SINAD WITH 1kHz INPUT

- ullet ±10V, 0V TO +5V, AND 0V TO +4V INPUT RANGES

- SINGLE +5V SUPPLY OPERATION

- PARALLEL AND SERIAL DATA OUTPUT

- PIN-COMPATIBLE WITH THE 12-BIT ADS7806

- USES INTERNAL OR EXTERNAL REFERENCE

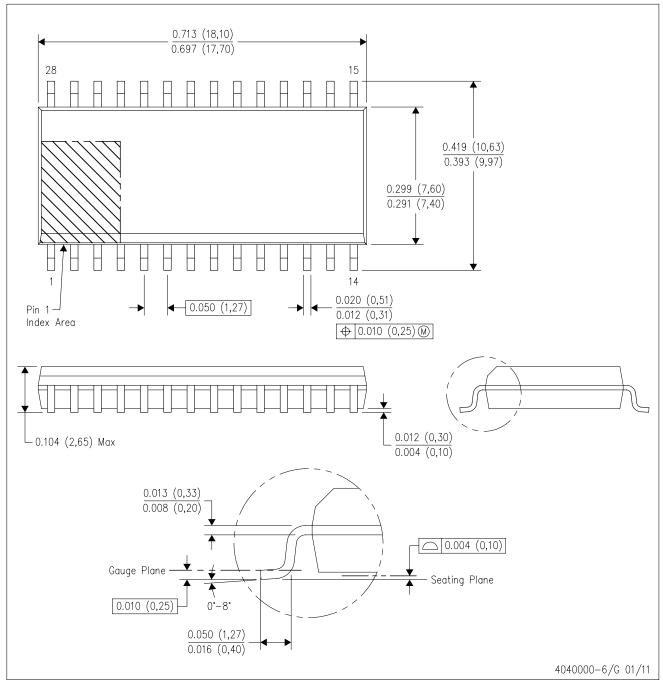

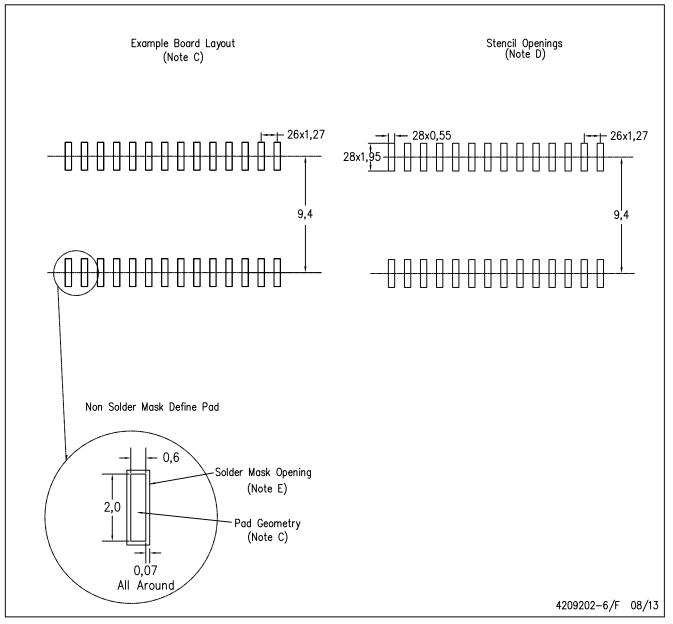

- 0.3" DIP-28 AND SO-28

## DESCRIPTION

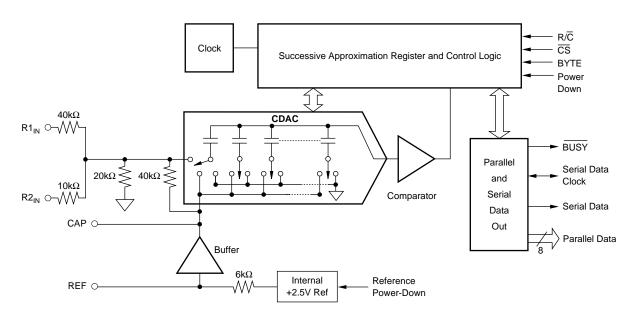

The ADS7807 is a low-power, 16-bit, sampling Analog-to-Digital (A/D) converter using state-of-the-art CMOS structures. It contains a complete 16-bit, capacitor-based, Successive Approximation Register (SAR) A/D converter with sample-and-hold, clock, reference, and microprocessor interface with parallel and serial output drivers.

The ADS7807 can acquire and convert 16 bits to within  $\pm 1.5 LSB$  in 25 $\mu s$  max while consuming only 35mW max. Laser trimmed scaling resistors provide standard industrial input ranges of  $\pm 10V$  and 0V to +5V. In addition, a 0V to +4V range allows development of complete single-supply systems.

The ADS7807 is available in a 0.3" DIP-28 and SO-28, both fully specified for operation over the industrial -40°C to +85°C temperature range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Analog Inputs: R1 <sub>IN</sub> ±1                     | 2V  |

|--------------------------------------------------------|-----|

| R2 <sub>IN</sub> ±5.                                   | .5V |

| CAP V <sub>ANA</sub> + 0.3V to AGND2 – 0.              | .3V |

| REFIndefinite Short to AGNI                            | D2, |

| Momentary Short to V                                   | ANA |

| Ground Voltage Differences: DGND, AGND1, and AGND2 ±0. |     |

| V <sub>ANA</sub>                                       | 7V  |

| V <sub>DIG</sub> to V <sub>ANA</sub> +0.               | .3V |

| V <sub>DIG</sub>                                       | 7V  |

| Digital Inputs –0.3V to V <sub>DIG</sub> + 0.          |     |

| Maximum Junction Temperature+165                       | °C  |

| Internal Power Dissipation 825n                        | nW  |

| Lead Temperature (soldering, 10s)+300                  | )°C |

|                                                        |     |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

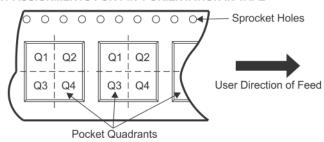

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT   | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>ERROR (LSB) | SPECIFIED<br>NO MISSING<br>CODE LEVEL<br>(LSB) | MINIMUM<br>SIGNAL-TO-<br>(NOISE +<br>DISTORTION)<br>RATIO (DB) | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|-----------|-------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| ADS7807P  | ±3                                              | 15                                             | 83                                                             | DIP-28       | NT                    | -40°C to +85°C                    | ADS7807P           | ADS7807P           | Tubes, 13                    |

| ADS7807PB | ±1.5                                            | 16                                             | 86                                                             | "            | "                     | "                                 | ADS7807PB          | ADS7807PB          | Tubes, 13                    |

| ADS7807U  | ±3                                              | 15                                             | 83                                                             | SO-28        | DW                    | -40°C to +85°C                    | ADS7807U           | ADS7807U           | Tubes, 28                    |

| "         | "                                               | "                                              | "                                                              | "            | "                     | "                                 | "                  | ADS7807U/1K        | Tape and Reel, 1000          |

| ADS7807UB | ±1.5                                            | 16                                             | 86                                                             | "            | "                     | "                                 | ADS7807UB          | ADS7807UB          | Tubes, 28                    |

| "         | "                                               |                                                | "                                                              | "            | "                     | "                                 | "                  | ADS7807UB/1K       | Tape and Reel, 1000          |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at

## **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}\text{C}$  to +85°C,  $f_S = 40\text{kHz}$ ,  $V_{DIG} = V_{ANA} = +5V$ , and using internal reference and fixed resistors (see Figure 7b), unless otherwise specified.

|                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                      |     | ADS7807P,                                 | U                                         | AD                    | S7807PB,                  | UB                                      |                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------|-------------------------------------------|-----------------------|---------------------------|-----------------------------------------|------------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                 | CONDITIONS                                                                                                                                           | MIN | TYP                                       | MAX                                       | MIN                   | TYP                       | MAX                                     | UNITS                                                                  |

| RESOLUTION                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                      |     |                                           | 16                                        |                       |                           | *                                       | Bits                                                                   |

| ANALOG INPUT Voltage Ranges Impedance Capacitance                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |     | 45                                        | 1 '                                       | +5, 0 to +4  [able I) | *                         |                                         | V<br>pF                                                                |

| THROUGHPUT SPEED Conversion Time Complete Cycle Throughput Rate                                                                                                                                                                                                                                                                           | Acquire and Convert                                                                                                                                  | 40  |                                           | 20<br>25                                  | *                     |                           | *                                       | μs<br>μs<br>kHz                                                        |

| DC ACCURACY Integral Linearity Error Differential Linearity Error No Missing Codes Transition Noise(2) Gain Error Full-Scale Error Drift Full-Scale Error Drift Full-Scale Error Drift Bipolar Zero Error(3) Bipolar Zero Error Drift Unipolar Zero Error(3) Unipolar Zero Error Drift Recovery Time to Rated Accuracy from Power-Down(5) | Ext. 2.5000V Ref<br>Ext. 2.5000V Ref<br>±10V Range<br>±10V Range<br>0V to 5V, 0V to 4V Ranges<br>0V to 5V, 0V to 4V Ranges<br>2.2μF Capacitor to CAP | 15  | 0.8<br>±0.2<br>±7<br>±0.5<br>±0.5<br>±0.5 | ±3<br>+3, -2<br>±0.5<br>±0.5<br>±10<br>±3 | 16                    | *<br>±0.1<br>±5<br>*<br>* | ±1.5<br>+1.5, -1<br>±0.25<br>±0.25<br>* | LSB(1) LSB Bits LSB % ppm/°C % ppm/°C mV ppm/°C mV ppm/°C mV ppm/°C ms |

| Power-Supply Sensitivity<br>$(V_{DIG} = V_{ANA} = V_S)$                                                                                                                                                                                                                                                                                   | +4.75V < V <sub>S</sub> < +5.25V                                                                                                                     |     |                                           | ±8                                        |                       |                           | *                                       | LSB                                                                    |

## **ELECTRICAL CHARACTERISTICS (Cont.)**

At  $T_A = -40^{\circ}$ C to +85°C,  $f_S = 40$ kHz,  $V_{DIG} = V_{ANA} = +5$ V, and using internal reference and fixed resistors (see Figure 7b), unless otherwise specified.

|                                                                                                                                                                               |                                                                                                                                                                                                                                                         | ,                 | ADS7807P,                                   | U                                           | Al             | DS7807PB,                   | UB          |                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------|---------------------------------------------|----------------|-----------------------------|-------------|-----------------------------------|

| PARAMETER                                                                                                                                                                     | CONDITIONS                                                                                                                                                                                                                                              | MIN               | TYP                                         | MAX                                         | MIN            | TYP                         | MAX         | UNITS                             |

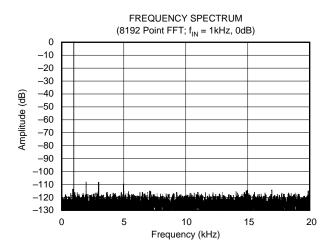

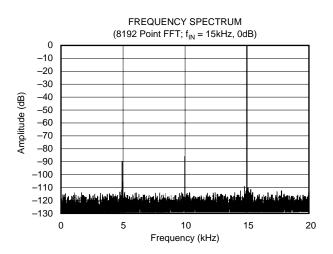

| AC ACCURACY Spurious-Free Dynamic Range Total Harmonic Distortion Signal-to-(Noise + Distortion)  Signal-to-Noise Usable Bandwidth <sup>(7)</sup> Full-Power Bandwidth (-3dB) | $\begin{split} f_{\text{IN}} &= 1 \text{kHz}, \pm 10 \text{V} \\ f_{\text{IN}} &= 1 \text{kHz}, \pm 10 \text{V} \\ f_{\text{IN}} &= 1 \text{kHz}, \pm 10 \text{V} \\ -60 \text{dB Input} \\ f_{\text{IN}} &= 1 \text{kHz}, \pm 10 \text{V} \end{split}$ | 90<br>83<br>83    | 100<br>-100<br>88<br>30<br>88<br>130<br>600 | -90                                         | 96<br>86<br>86 | *<br>*<br>*<br>32<br>*<br>* | -96         | dB <sup>(6)</sup> dB dB dB dB kHz |

| SAMPLING DYNAMICS Aperture Delay Aperture Jitter Transient Response Over-Voltage Recovery <sup>(8)</sup>                                                                      | FS Step                                                                                                                                                                                                                                                 |                   | 40<br>20<br>750                             | 5                                           |                | * *                         | *           | ns<br>ps<br>µs<br>ns              |

| REFERENCE Internal Reference Voltage Internal Reference Source Current (Must use external buffer.) Internal Reference Drift External Reference Voltage Range                  | No Load                                                                                                                                                                                                                                                 | 2.48              | 2.5<br>1<br>8<br>2.5                        | 2.52                                        | *              | * * * *                     | *           | V<br>μA<br>ppm/°C<br>V            |

| for Specified Linearity External Reference Current Drain                                                                                                                      | External 2.5000V Ref                                                                                                                                                                                                                                    |                   |                                             | 100                                         |                |                             | *           | μΑ                                |

| DIGITAL INPUTS Logic Levels  V <sub>IL</sub> V <sub>IH</sub> (9)  I <sub>IL</sub> I <sub>IH</sub>                                                                             | $V_{IL} = 0V$ $V_{IH} = 5V$                                                                                                                                                                                                                             | -0.3<br>+2.0      |                                             | +0.8<br>V <sub>D</sub> + 0.3V<br>±10<br>±10 | *              |                             | *<br>*<br>* | V<br>V<br>μΑ<br>μΑ                |

| DIGITAL OUTPUTS Data Format Data Coding VoL VoH Leakage Current                                                                                                               | I <sub>SINK</sub> = 1.6mA<br>I <sub>SOURCE</sub> = 500μA<br>High-Z State,<br>V <sub>OUT</sub> = 0V to V <sub>DIG</sub>                                                                                                                                  | +4                |                                             | Parallel 16 b<br>y Two's Con<br>+0.4<br>±5  |                |                             | *           | V<br>V<br>μΑ                      |

| Output Capacitance  DIGITAL TIMING  Bus Access Time  Bus Relinquish Time                                                                                                      | High-Z State $R_L = 3.3k\Omega, C_L = 50pF$ $R_L = 3.3k\Omega, C_L = 10pF$                                                                                                                                                                              |                   |                                             | 15<br>83<br>83                              |                |                             | * *         | pF<br>ns<br>ns                    |

| POWER SUPPLIES Specified Performance  V <sub>DIG</sub> V <sub>ANA</sub> I <sub>DIG</sub> I <sub>ANA</sub> Power Dissipation                                                   | Must be $\leq$ V <sub>ANA</sub> $V_{ANA} = V_{DIG} = 5V, f_S = 40kHz$ REFD HIGH PWRD and REFD HIGH                                                                                                                                                      | +4.75<br>+4.75    | +5<br>+5<br>0.6<br>5.0<br>28<br>23<br>50    | +5.25<br>+5.25                              | *              | * * * * * * * * *           | * *         | V<br>V<br>mA<br>mA<br>mW<br>mW    |

| TEMPERATURE RANGE Specified Performance Derated Performance Storage Thermal Resistance $(\theta_{JA})$ DIP SO                                                                 |                                                                                                                                                                                                                                                         | -40<br>-55<br>-65 | 75<br>75                                    | +85<br>+125<br>+150                         | *<br>*<br>*    | *                           | *<br>*<br>* | °C<br>°C<br>°C<br>°CW             |

<sup>\*</sup> Same specifications as ADS7807P, U.

NOTES: (1) LSB means Least Significant Bit. One LSB for the  $\pm 10V$  input range is  $305\mu V$ .

- (2) Typical rms noise at worst-case transition.

- (3) As measured with fixed resistors, see Figure 7b. Adjustable to zero with external potentiometer.

- (4) Full-scale error is the worst case of -Full-Scale or +Full-Scale untrimmed deviation from ideal first and last code transitions, divided by the transition voltage (not divided by the full-scale range) and includes the effect of offset error.

- (5) This is the time delay after the ADS7807 is brought out of Power-Down mode until all internal settling occurs and the analog input is acquired to rated accuracy. A Convert command after this delay will yield accurate results.

- (6) All specifications in dB are referred to a full-scale input.

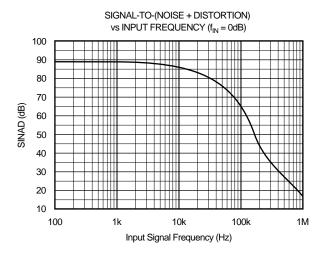

- (7) Usable bandwidth defined as full-scale input frequency at which Signal-to-(Noise + Distortion) degrades to 60dB.

- (8) Recovers to specified performance after 2 FS input overvoltage.

- (9) The minimum  $V_{\text{IH}}$  level for the DATACLK signal is 3V.

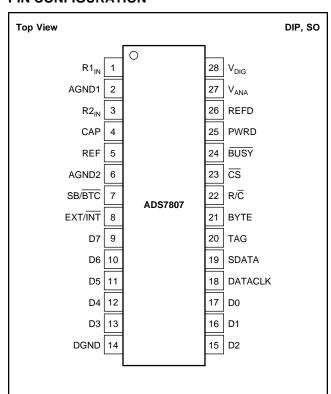

### **PIN DESCRIPTIONS**

|      |                  | DIGITAL |                                                                                                                                                                                                                    |

|------|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN# | NAME             | I/O     | DESCRIPTION                                                                                                                                                                                                        |

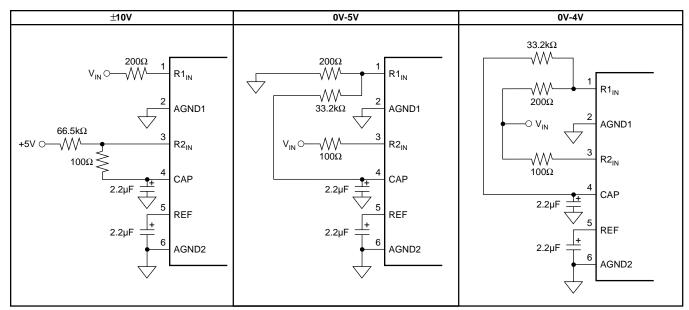

| 1    | R1 <sub>IN</sub> |         | Analog Input. See Figure 7.                                                                                                                                                                                        |

| 2    | AGND1            |         | Analog Sense Ground.                                                                                                                                                                                               |

| 3    | R2 <sub>IN</sub> |         | Analog Input. See Figure 7.                                                                                                                                                                                        |

| 4    | CAP              |         | Reference Buffer Output. 2.2μF tantalum capacitor to ground.                                                                                                                                                       |

| 5    | REF              |         | Reference Input/Output. 2.2µF tantalum capacitor to ground.                                                                                                                                                        |

| 6    | AGND2            |         | Analog Ground                                                                                                                                                                                                      |

| 7    | SB/BTC           | 1       | Selects Straight Binary or Binary Two's Complement for Output Data Format.                                                                                                                                         |

| 8    | EXT/INT          | 1       | External/Internal data clock select.                                                                                                                                                                               |

| 9    | D7               | 0       | Data Bit 7 if BYTE is HIGH. Data bit 15 (MSB) if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW. Leave                                                                                                        |

|      |                  |         | unconnected when using serial output.                                                                                                                                                                              |

| 10   | D6               | 0       | Data Bit 6 if BYTE is HIGH. Data bit 14 if BYTE is LOW. Hi-Z when $\overline{\text{CS}}$ is HIGH and/or R/ $\overline{\text{C}}$ is LOW.                                                                           |

| 11   | D5               | 0       | Data Bit 5 if BYTE is HIGH. Data bit 13 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                    |

| 12   | D4               | 0       | Data Bit 4 if BYTE is HIGH. Data bit 12 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                    |

| 13   | D3               | 0       | Data Bit 3 if BYTE is HIGH. Data bit 11 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                    |

| 14   | DGND             |         | Digital Ground                                                                                                                                                                                                     |

| 15   | D2               | 0       | Data Bit 2 if BYTE is HIGH. Data bit 10 if BYTE is LOW. Hi-Z when <del>CS</del> is HIGH and/or R/ <del>C</del> is LOW.                                                                                             |

| 16   | D1               | 0       | Data Bit 1 if BYTE is HIGH. Data bit 9 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                     |

| 17   | D0               | 0       | Data Bit 0 (LSB) if BYTE is HIGH. Data bit 8 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                               |

| 18   | DATACLK          | I/O     | Data Clock Output when EXT/INT is LOW. Data clock input when EXT/INT is HIGH.                                                                                                                                      |

| 19   | SDATA            | 0       | Serial Output Synchronized to DATACLK                                                                                                                                                                              |

| 20   | TAG              | 1       | Serial Input When Using an External Data Clock                                                                                                                                                                     |

| 21   | BYTE             | 1       | Selects 8 most significant bits (LOW) or 8 least significant bits (HIGH) on parallel output pins.                                                                                                                  |

| 22   | R/C              | 1       | With $\overline{\text{CS}}$ LOW and $\overline{\text{BUSY}}$ HIGH, a Falling Edge on $\overline{\text{R/C}}$ Initiates a New Conversion. With $\overline{\text{CS}}$ LOW, a rising edge on $\overline{\text{R/C}}$ |

|      |                  |         | enables the parallel output.                                                                                                                                                                                       |

| 23   | <del>cs</del>    | 1       | Internally OR'd with R/C. If R/C is LOW, a falling edge on CS initiates a new conversion. If EXT/INT is LOW, this same                                                                                             |

|      |                  |         | falling edge will start the transmission of serial data results from the previous conversion.                                                                                                                      |

| 24   | BUSY             | 0       | At the start of a conversion, BUSY goes LOW and stays LOW until the conversion is completed and the digital outputs                                                                                                |

|      |                  |         | have been updated.                                                                                                                                                                                                 |

| 25   | PWRD             | 1       | PWRD HIGH shuts down all analog circuitry except the reference. Digital circuitry remains active.                                                                                                                  |

| 26   | REFD             |         | REFD HIGH shuts down the internal reference. External reference will be required for conversions.                                                                                                                  |

| 27   | $V_{ANA}$        |         | Analog Supply. Nominally +5V. Decouple with 0.1μF ceramic and 10μF tantalum capacitors.                                                                                                                            |

| 28   | $V_{DIG}$        |         | Digital Supply. Nominally +5V. Connect directly to pin 27. Must be ≤ V <sub>ANA</sub> .                                                                                                                            |

### **PIN CONFIGURATION**

| ANALOG<br>INPUT<br>RANGE | CONNECT R1 <sub>IN</sub> VIA 200 $\Omega$ TO | CONNECT $\mathbf{R2_{IN}}$ VIA 100 $\Omega$ TO | IMPEDANCE |

|--------------------------|----------------------------------------------|------------------------------------------------|-----------|

| ±10V                     | V <sub>IN</sub>                              | CAP                                            | 45.7kΩ    |

| 0V to 5V                 | AGND                                         | V <sub>IN</sub>                                | 20.0kΩ    |

| 0V to 4V                 | V <sub>IN</sub>                              | V <sub>IN</sub>                                | 21.4kΩ    |

TABLE I. Input Range Connections. See Figure 7.

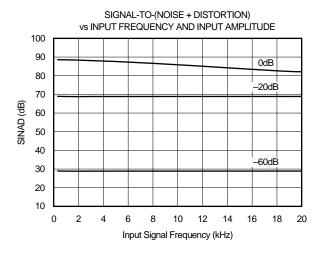

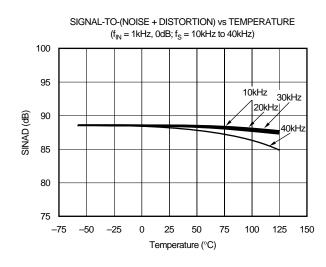

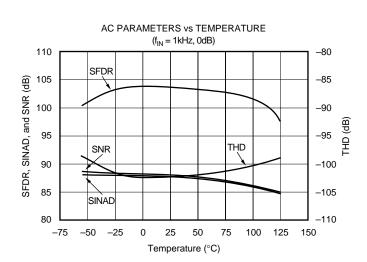

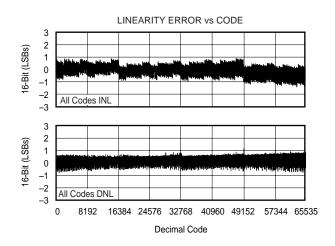

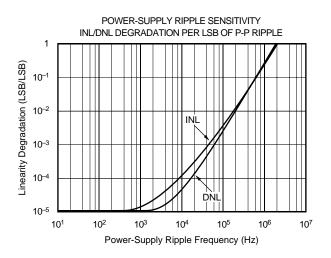

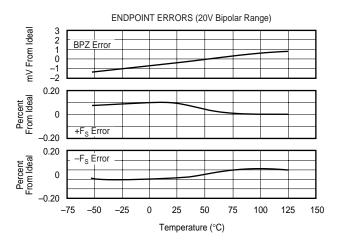

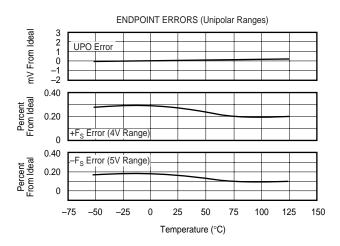

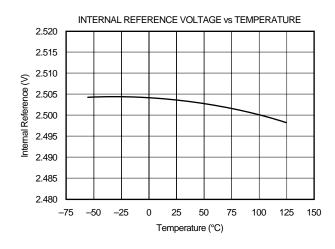

## TYPICAL CHARACTERISTICS

At T<sub>A</sub> = +25°C, f<sub>S</sub> = 40kHz, V<sub>DIG</sub> = V<sub>ANA</sub> = +5V, and using internal reference and fixed resistors (see Figure 7b), unless otherwise specified.

## **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25^{\circ}C$ ,  $f_S = 40$ kHz,  $V_{DIG} = V_{ANA} = +5V$ , and using internal reference and fixed resistors (see Figure 7b), unless otherwise specified.

## **BASIC OPERATION**

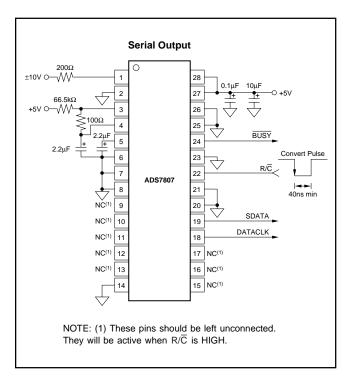

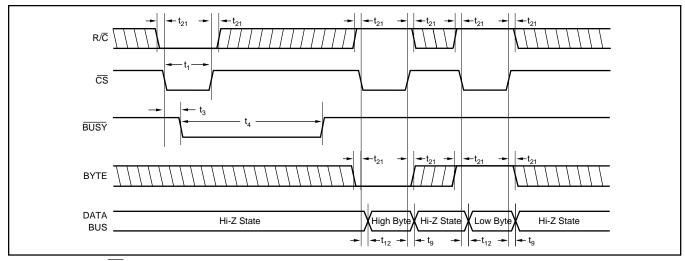

#### PARALLEL OUTPUT

Figure 1a shows a basic circuit to operate the ADS7807 with a  $\pm 10\text{V}$  input range and parallel output. Taking R/ $\overline{\text{C}}$  (pin 22) LOW for a minimum of 40ns (12 $\mu$ s max) will initiate a conversion.  $\overline{\text{BUSY}}$  (pin 24) will go LOW and stay LOW until the conversion is completed and the output register is updated. If BYTE (pin 21) is LOW, the eight Most Significant Bits (MSBs) will be valid when  $\overline{\text{BUSY}}$  rises; if BYTE is HIGH, the eight Least Significant Bits (LSBs) will be valid when  $\overline{\text{BUSY}}$  rises. Data will be output in Binary Two's Complement (BTC) format.  $\overline{\text{BUSY}}$  going HIGH can be used to latch the data. After the first byte has been read, BYTE can be toggled allowing the remaining byte to be read. All convert commands will be ignored while  $\overline{\text{BUSY}}$  is LOW.

The ADS7807 will begin tracking the input signal at the end of the conversion. Allowing 25µs between convert commands assures accurate acquisition of a new signal.

The offset and gain are adjusted internally to allow external trimming with a single supply. The external resistors compensate for this adjustment and can be left out if the offset and gain will be corrected in software (refer to the **Calibration** section).

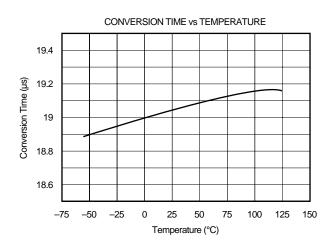

#### **SERIAL OUTPUT**

Figure 1b shows a basic circuit to operate the ADS7807 with a  $\pm 10$ V input range and serial output. Taking R/ $\overline{C}$  (pin 22) LOW for 40ns (12 $\mu$ s max) will initiate a conversion and

Parallel Output

200Ω

200Ω

4

210V 0

3

3

45V 0

2.2μF

45V 0

2.2μF

5

40ns min

Pin 21 B15 B14 B13 B12 B11

LOW (MSB)

Pin 21 B7 B6 B5 B4 B3

Pin 21 B7 B6 B5 B4 B3

NOTE: (1) SDATA (pin 19) is always active.

FIGURE 1a. Basic ±10V Operation, both Parallel and Serial Output.

output valid data from the previous conversion on SDATA (pin 19) synchronized to 16 clock pulses output on DATACLK (pin 18).  $\overline{\text{BUSY}}$  (pin 24) will go LOW and stay LOW until the conversion is completed and the serial data has been transmitted. Data will be output in BTC format, MSB first, and will be valid on both the rising and falling edges of the data clock.  $\overline{\text{BUSY}}$  going HIGH can be used to latch the data. All convert commands will be ignored while  $\overline{\text{BUSY}}$  is LOW.

The ADS7807 will begin tracking the input signal at the end of the conversion. Allowing 25µs between convert commands assures accurate acquisition of a new signal.

The offset and gain are adjusted internally to allow external trimming with a single supply. The external resistors compensate for this adjustment and can be left out if the offset and gain will be corrected in software (refer to the **Calibration** section).

## STARTING A CONVERSION

The combination of  $\overline{\text{CS}}$  (pin 23) and R/ $\overline{\text{C}}$  (pin 22) LOW for a minimum of 40ns puts the sample-and-hold of the ADS7807 in the hold state and starts conversion 'n'.  $\overline{\text{BUSY}}$  (pin 24) will go LOW and stay LOW until conversion 'n' is completed and the internal output register has been updated. All new convert commands during  $\overline{\text{BUSY}}$  LOW will be ignored.  $\overline{\text{CS}}$  and/ or R/ $\overline{\text{C}}$  must go HIGH before  $\overline{\text{BUSY}}$  goes HIGH, or a new conversion will be initiated without sufficient time to acquire a new signal.

FIGURE 1b. Basic ±10V Operation with Serial Output.

The ADS7807 will begin tracking the input signal at the end of the conversion. Allowing 25 $\mu$ s between convert commands assures accurate acquisition of a new signal. Refer to Tables II and III for a summary of  $\overline{CS}$ , R/ $\overline{C}$ , and  $\overline{BUSY}$  states, and Figures 2 through 6 for timing diagrams.

| cs       | R/C      | BUSY | OPERATION                                                                                                                                                                                       |

|----------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Х        | Х    | None. Databus is in Hi-Z state.                                                                                                                                                                 |

| <b>+</b> | 0        | 1    | Initiates conversion 'n'. Databus remains in Hi-Z state.                                                                                                                                        |

| 0        | <b>\</b> | 1    | Initiates conversion 'n'. Databus enters Hi-Z state.                                                                                                                                            |

| 0        | 1        | 1    | Conversion 'n' completed. Valid data from conversion 'n' on the databus.                                                                                                                        |

| <b>+</b> | 1        | 1    | Enables databus with valid data from conversion 'n'.                                                                                                                                            |

| <b>+</b> | 1        | 0    | Enables databus with valid data from conversion ' $n - 1^{1(1)}$ . Conversion n in progress.                                                                                                    |

| 0        | 1        | 0    | Enables databus with valid data from conversion 'n $-1$ '(1). Conversion 'n' in progress.                                                                                                       |

| 0        | 0        | 1    | New conversion initiated without acquisition of a new signal. Data will be invalid. $\overline{\text{CS}}$ and/or $\overline{\text{R/C}}$ must be HIGH when $\overline{\text{BUSY}}$ goes HIGH. |

| Х        | Х        | 0    | New convert commands ignored. Conversion 'n' in progress.                                                                                                                                       |

NOTE: (1) See Figures 2 and 3 for constraints on data valid from conversion 'n - 1'.

TABLE II. Control Functions When Using Parallel Output (DATACLK tied LOW, EXT/INT tied HIGH).

$\overline{\text{CS}}$  and  $\text{R/}\overline{\text{C}}$  are internally OR'ed and level triggered. There is not a requirement which input goes LOW first when initiating a conversion. If, however, it is critical that  $\overline{\text{CS}}$  or  $\text{R/}\overline{\text{C}}$  initiates conversion 'n', be sure the less critical input is LOW at least 10ns prior to the initiating input. If  $\text{EXT/}\overline{\text{INT}}$  (pin 8) is LOW when initiating conversion 'n', serial data from conversion 'n – 1' will be output on SDATA (pin 19) following the start of conversion 'n'. See *Internal Data Clock* in the **Reading Data** section.

To reduce the number of control pins,  $\overline{CS}$  can be tied LOW using  $R/\overline{C}$  to control the read and convert modes. This will have no effect when using the internal data clock in the serial output mode. The parallel output and the serial output (only when using an external data clock), however, will be affected whenever  $R/\overline{C}$  goes HIGH. Refer to the **Reading Data** section.

## READING DATA

The ADS7807 outputs serial or parallel data in Straight Binary (SB) or Binary Two's Complement data output format. If SB/BTC (pin 7) is HIGH, the output will be in SB format, and if LOW, the output will be in BTC format. Refer to Table IV for ideal output codes.

The parallel output can be read without affecting the internal output registers; however, reading the data through the serial port will shift the internal output registers one bit per data

| cs           | R/C          | BUSY                                                                                     | EXT/INT | DATACLK | OPERATION                                                                                                                                                                                        |  |  |  |  |  |

|--------------|--------------|------------------------------------------------------------------------------------------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| $\downarrow$ | 0            | 1                                                                                        | 0       | Output  | Initiates conversion 'n'. Valid data from conversion 'n – 1' clocked out on SDATA.                                                                                                               |  |  |  |  |  |

| 0            | $\downarrow$ | 1                                                                                        | 0       | Output  | Initiates conversion 'n'. Valid data from conversion 'n – 1' clocked out on SDATA.                                                                                                               |  |  |  |  |  |

| $\downarrow$ | 0            | 1                                                                                        | 1       | Input   | Initiates conversion 'n'. Internal clock still runs conversion process.                                                                                                                          |  |  |  |  |  |

| 0            | $\downarrow$ | 1                                                                                        | 1       | Input   | Initiates conversion 'n'. Internal clock still runs conversion process.                                                                                                                          |  |  |  |  |  |

| <b>\</b>     | 1            | 1                                                                                        | 1       | Input   | Conversion 'n' completed. Valid data from conversion 'n' clocked out on SDATA synchronized to external data clock.                                                                               |  |  |  |  |  |

| <b>\</b>     | 1            | 0                                                                                        | 1       | Input   | Valid data from conversion 'n – 1' output on SDATA synchronized to external data clock. Conversion 'n' in progress.                                                                              |  |  |  |  |  |

| 0            | 1            | 0                                                                                        | 1       | Input   | Valid data from conversion 'n – 1' output on SDATA synchronized to external data clock. Conversion 'n' in progress.                                                                              |  |  |  |  |  |

| 0            | 0            | 1                                                                                        | Х       | Х       | New conversion initiated without acquisition of a new signal. Data will be invalid. $\overline{\text{CS}}$ and/or R/ $\overline{\text{C}}$ must be HIGH when $\overline{\text{BUSY}}$ goes HIGH. |  |  |  |  |  |

| Х            | Х            | 0                                                                                        | Х       | Х       | New convert commands ignored. Conversion 'n' in progress.                                                                                                                                        |  |  |  |  |  |

| NOTE: (1     | ) See Figur  | NOTE: (1) See Figures 4, 5, and 6 for constraints on data valid from conversion 'n – 1'. |         |         |                                                                                                                                                                                                  |  |  |  |  |  |

TABLE III. Control Functions When Using Serial Output.

| DESCRIPTION                                     | CRIPTION ANALOG INPUT DIGITAL OUTPUT |                  |                  |                                         |      |                                  |      |

|-------------------------------------------------|--------------------------------------|------------------|------------------|-----------------------------------------|------|----------------------------------|------|

| Full-Scale Range<br>Least Significant Bit (LSB) | ±10<br>305μV                         | 0V to 5V<br>76μV | 0V to 4V<br>61μV | BINARY TWO'S COMPLEMENT<br>(SB/BTC LOW) |      | STRAIGHT BINARY<br>(SB/BTC HIGH) |      |

| . ,                                             |                                      | ·                |                  |                                         | HEX  |                                  | HEX  |

|                                                 |                                      |                  |                  | BINARY CODE                             | CODE | BINARY CODE                      | CODE |

| +Full-Scale (FS - 1LSB)                         | 9.999695V                            | 4.999924V        | 3.999939V        | 0111 1111 1111 1111                     | 7FFF | 1111 1111 1111 1111              | FFFF |

| Midscale                                        | 0V                                   | 2.5V             | 2V               | 0000 0000 0000 0000                     | 0000 | 1000 0000 0000 0000              | 8000 |

| One LSB Below Midscale                          | –305μV                               | 2.499924V        | 1.999939V        | 1111 1111 1111 1111                     | FFFF | 0111 1111 1111 1111              | 7FFF |

| -Full-Scale                                     | -10V                                 | 0V               | 0V               | 1000 0000 0000 0000                     | 8000 | 0000 0000 0000 0000              | 0000 |

TABLE IV. Output Codes and Ideal Input Voltages.

clock pulse. As a result, data can be read on the parallel port prior to reading the same data on the serial port, but data cannot be read through the serial port prior to reading the same data on the parallel port.

#### PARALLEL OUTPUT

To use the parallel output, tie EXT/ $\overline{\text{INT}}$  (pin 8) HIGH and DATACLK (pin 18) LOW. SDATA (pin 19) should be left unconnected. The parallel output will be active when R/ $\overline{\text{C}}$  (pin 22) is HIGH and  $\overline{\text{CS}}$  (pin 23) is LOW. Any other combination of  $\overline{\text{CS}}$  and R/ $\overline{\text{C}}$  will tri-state the parallel output. Valid conversion data can be read in two 8-bit bytes on D7-D0 (pins 9-13 and 15-17). When BYTE (pin 21) is LOW, the 8 most significant bits will be valid with the MSB on D7. When BYTE is HIGH, the 8 least significant bits will be valid with the LSB on D0. BYTE can be toggled to read both bytes within one conversion cycle.

Upon initial power up, the parallel output will contain indeterminate data.

#### PARALLEL OUTPUT (AFTER A CONVERSION)

After conversion 'n' is completed and the output registers have been updated,  $\overline{BUSY}$  (pin 24) will go HIGH. Valid data from conversion 'n' will be available on D7-D0 (pins 9-13 and 15-17).  $\overline{BUSY}$  going high can be used to latch the data. Refer to Table V and Figures 2 and 3 for timing constraints.

#### PARALLEL OUTPUT (DURING A CONVERSION)

After conversion 'n' has been initiated, valid data from conversion 'n – 1' can be read and will be valid up to  $12\mu s$  after the start of conversion 'n'. Do not attempt to read data beyond  $12\mu s$  after the start of conversion 'n' until  $\overline{BUSY}$  (pin 24) goes HIGH; this may result in reading invalid data. Refer to Table V and Figures 2 and 3 for timing constraints.

FIGURE 2. Conversion Timing with Parallel Output (CS and DATACLK tied LOW, EXT/INT tied HIGH).

FIGURE 3. Using  $\overline{\text{CS}}$  to Control Conversion and Read Timing with Parallel Outputs.

| SYMBOL                          | DESCRIPTION                    | MIN  | TYP  | MAX  | UNITS |

|---------------------------------|--------------------------------|------|------|------|-------|

| t <sub>1</sub>                  | Convert Pulse Width            | 0.04 |      | 12   | μs    |

| t <sub>2</sub> (1)              | Data Valid Delay after R/C LOW |      | 18   | 20   | μs    |

| t <sub>3</sub> <sup>(1)</sup>   | BUSY Delay from                |      |      |      |       |

|                                 | Start of Conversion            |      | 12   | 85   | ns    |

| t <sub>4</sub> (1)              | BUSY LOW                       |      | 18   | 20   | μs    |

| t <sub>5</sub>                  | BUSY Delay after               |      | 90   |      | ns    |

|                                 | End of Conversion              |      |      |      |       |

| t <sub>6</sub>                  | Aperture Delay                 |      | 40   |      | ns    |

| t <sub>7</sub> <sup>(1)</sup>   | Conversion Time                |      | 18   | 20   | μs    |

| t <sub>8</sub> <sup>(1)</sup>   | Acquisition Time               | 5    | 7    |      | μs    |

| t <sub>9</sub>                  | Bus Relinquish Time            | 10   |      | 83   | ns    |

| t <sub>10</sub>                 | BUSY Delay after Data Valid    | 20   | 60   |      | ns    |

| t <sub>11</sub> <sup>(1)</sup>  | Previous Data Valid            | 12   | 18   |      | μs    |

|                                 | after Start of Conversion      |      |      |      |       |

| t <sub>12</sub> <sup>(1)</sup>  | Bus Access Time and BYTE Delay |      | 10   | 83   | ns    |

| t <sub>13</sub> <sup>(1)</sup>  | Start of Conversion            |      | 2.4  |      | μs    |

|                                 | to DATACLK Delay               |      |      |      |       |

| t <sub>14</sub> <sup>(1)</sup>  | DATACLK Period                 | 0.6  | 0.82 | 0.85 | μs    |

| t <sub>15</sub> <sup>(1)</sup>  | Data Valid to DATACLK          | 150  | 200  |      | ns    |

|                                 | HIGH Delay                     |      |      |      |       |

| t <sub>16</sub> <sup>(1)</sup>  | Data Valid after DATACLK       | 150  | 200  |      | ns    |

|                                 | LOW Delay                      |      |      |      |       |

| t <sub>17</sub>                 | External DATACLK Period        | 100  |      |      | ns    |

| t <sub>18</sub>                 | External DATACLK LOW           | 40   |      |      | ns    |

| t <sub>19</sub>                 | External DATACLK HIGH          | 50   |      |      | ns    |

| t <sub>20</sub>                 | CS and R/C to External         | 25   |      |      | ns    |

|                                 | DATACLK Setup Time             |      |      |      |       |

| t <sub>21</sub>                 | R/C to CS Setup Time           | 10   |      |      | ns    |

| t <sub>22</sub> (1)             | Valid Data after DATACLK HIGH  | 2    | 12   |      | ns    |

| t <sub>7</sub> + t <sub>8</sub> | Throughput Time                |      |      | 25   | μs    |

| DIP (NT) F                      | PACKAGE ONLY TIMING            |      |      |      |       |

| t <sub>2</sub>                  | Data Valid Delay after R/C LOW |      | 19   | 20   | μs    |

| t <sub>3</sub>                  | BUSY Delay from                |      |      | 85   | ns    |

|                                 | Start of Conversion            |      |      |      |       |

| t <sub>4</sub>                  | BUSY LOW                       |      | 19   | 20   | μs    |

| t <sub>7</sub>                  | Conversion Time                |      | 19   | 20   | μs    |

| t <sub>8</sub>                  | Acquisition Time               |      |      | 5    | μs    |

| t <sub>11</sub>                 | Previous Data Valid            | 12   | 19   |      | μs    |

|                                 | after Start of Conversion      |      |      |      |       |

| t <sub>12</sub>                 | Bus Access Time and BYTE Delay |      |      | 83   | ns    |

| t <sub>13</sub>                 | Start of Conversion            |      | 1.4  |      | μs    |

|                                 | to DATACLK Delay               |      |      |      |       |

| t <sub>14</sub>                 | DATACLK Period                 |      | 1.1  |      | μs    |

| t <sub>15</sub>                 | Data Valid to DATACLK          | 20   | 75   |      | ns    |

|                                 | HIGH Delay                     |      |      |      |       |

|                                 |                                |      |      | 1    |       |

NOTE: (1) See the bottom part of this table if using the DIP (NT) package.

600

ns

ns

400

Data Valid after DATACLK

LOW Delay

Valid Data after DATACLK HIGH

TABLE V. Conversion and Data Timing.  $T_A = -40^{\circ}\text{C}$  to +85°C.

#### **SERIAL OUTPUT**

t<sub>16</sub>

t<sub>22</sub>

Data can be clocked out with the internal data clock or an external data clock. When using serial output, be careful with the parallel outputs, D7-D0 (pins 9-13 and 15-17), as these pins will come out of Hi-Z state whenever  $\overline{\text{CS}}$  (pin 23) is LOW and R/ $\overline{\text{C}}$  (pin 22) is HIGH. The serial output can not be tristated and is always active. Refer to the **Applications Information** section for specific serial interfaces.

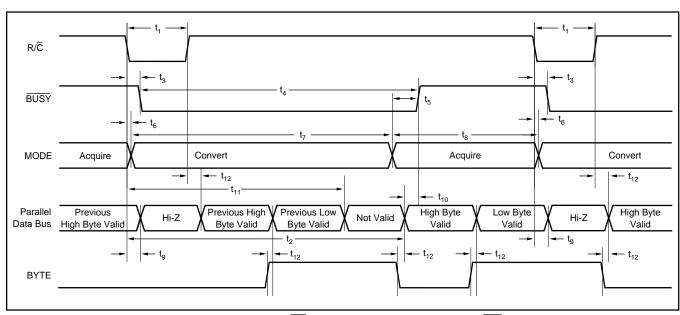

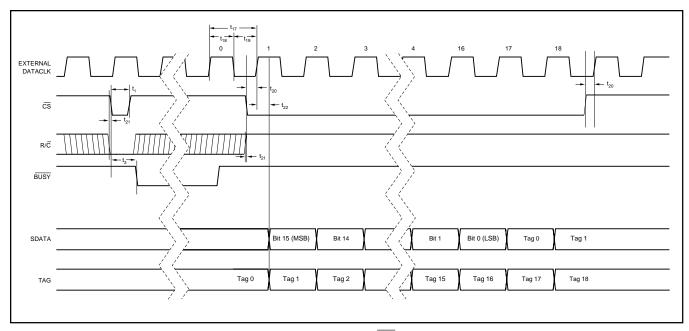

## INTERNAL DATA CLOCK (During a Conversion)

To use the internal data clock, tie  $EXT/\overline{\text{INT}}$  (pin 8) LOW. The combination of R/ $\overline{\text{C}}$  (pin 22) and  $\overline{\text{CS}}$  (pin 23) LOW will initiate conversion 'n' and activate the internal data clock (typically 900kHz clock rate). The ADS7807 will output 16 bits of valid data, MSB first, from conversion 'n-1' on SDATA (pin 19), synchronized to 16 clock pulses output on DATACLK (pin 18). The data will be valid on both the rising and falling edges of the internal data clock. The rising edge of  $\overline{\text{BUSY}}$  (pin 24) can be used to latch the data. After the 16th clock pulse, DATACLK will remain LOW until the next conversion is initiated, while SDATA will go to whatever logic level was input on TAG (pin 20) during the first clock pulse. Refer to Table V and Figure 4.

#### **EXTERNAL DATA CLOCK**

To use an external data clock, tie EXT/INT (pin 8) HIGH. The external data clock is not a conversion clock; it can only be used as a data clock. To enable the output mode of the ADS7807,  $\overline{CS}$  (pin 23) must be LOW and R/ $\overline{C}$  (pin 22) must be HIGH. DATACLK must be HIGH for 20% to 70% of the total data clock period; the clock rate can be between DC and 10MHz. Serial data from conversion 'n' can be output on SDATA (pin 19) after conversion 'n' is completed or during conversion 'n + 1'.

An obvious way to simplify control of the converter is to tie  $\overline{CS}$  LOW and use  $R/\overline{C}$  to initiate conversions.

While this is perfectly acceptable, there is a possible problem when using an external data clock. At an indeterminate point from 12 $\mu$ s after the start of conversion 'n' until  $\overline{BUSY}$  rises, the internal logic will shift the results of conversion 'n' into the output register. If  $\overline{CS}$  is LOW, R/ $\overline{C}$  HIGH, and the external clock is HIGH at this point, data will be lost. So, with  $\overline{CS}$  LOW, either R/ $\overline{C}$  and/or DATACLK must be LOW during this period to avoid losing valid data.

## EXTERNAL DATA CLOCK (After a Conversion)

After conversion 'n' is completed and the output registers have been updated, BUSY (pin 24) will go HIGH. With CS LOW and R/C HIGH, valid data from conversion 'n' will be output on SDATA (pin 19) synchronized to the external data clock input on DATACLK (pin 18). The MSB will be valid on the first falling edge and the second rising edge of the external data clock. The LSB will be valid on the 16th falling edge and 17th rising edge of the data clock. TAG (pin 20) will input a bit of data for every external clock pulse. The first bit input on TAG will be valid on SDATA on the 17th falling edge and the 18th rising edge of DATACLK; the second input bit will be valid on the 18th falling edge and the 19th rising edge, etc. With a continuous data clock, TAG data will be output on SDATA until the internal output registers are updated with the results from the next conversion. Refer to Table V and Figure 5.

FIGURE 4. Serial Data Timing Using Internal Data Clock (TAG tied LOW).

FIGURE 5. Conversion and Read Timing with External Clock (EXT/INT Tied HIGH) Read after Conversion.

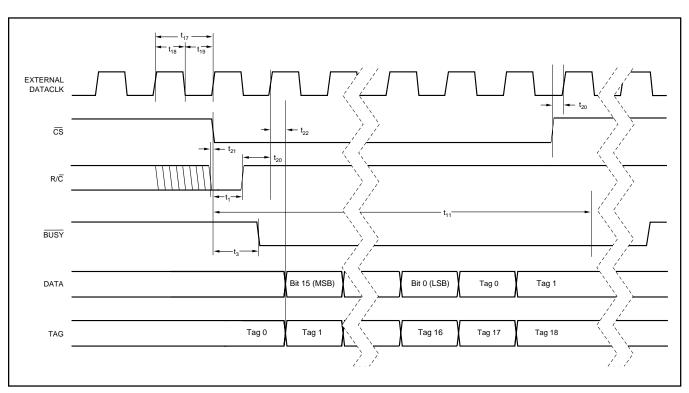

## EXTERNAL DATA CLOCK (During a Conversion)

After conversion 'n' has been initiated, valid data from conversion 'n – 1' can be read and will be valid up to  $12\mu s$  after the start of conversion 'n'. Do not attempt to clock out data from  $12\mu s$  after the start of conversion 'n' until  $\overline{BUSY}$  (pin 24) rises; this will result in data loss. NOTE: For the best possible performance when using an external data clock, data should not be clocked out during a conversion. The switching noise of the asynchronous data clock can cause digital feedthrough degrading the converter's performance. Refer to Table V and Figure 6.

#### TAG FEATURE

TAG (pin 20) inputs serial data synchronized to the external or internal data clock.

When using an external data clock, the serial bit stream input on TAG will follow the LSB output on SDATA until the internal output register is updated with new conversion results. See Table V and Figures 5 and 6.

The logic level input on TAG for the first rising edge of the internal data clock will be valid on SDATA after all 16 bits of valid data have been output.

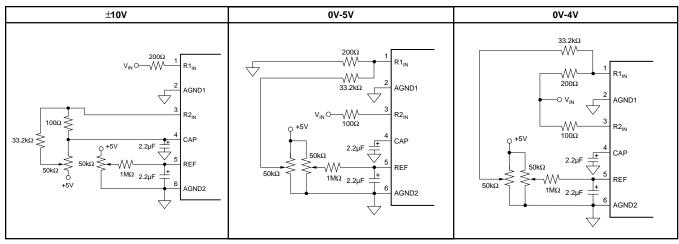

## **INPUT RANGES**

The ADS7807 offers three input ranges: standard  $\pm 10V$  and 0V-5V, and a 0V-4V range for complete, single-supply systems. See Figures 7a and 7b for the necessary circuit connections for implementing each input range and optional offset and gain adjust circuitry. Offset and full-scale error<sup>(1)</sup> specifications are tested with the fixed resistors, see Figure 7b. Adjustments for offset and gain are described in the **Calibration** section of this data sheet.

The offset and gain are adjusted internally to allow external trimming with a single supply. The external resistors compensate for this adjustment and can be left out if the offset and gain will be corrected in software (refer to the **Calibration** section).

The input impedance, summarized in Table II, results from the combination of the internal resistor network (see the front page of this product data sheet) and the external resistors used for each input range (see Figure 8). The input resistor divider network provides inherent over-voltage protection to at least  $\pm 5.5 \text{V}$  for R2\_{IN} and  $\pm 12 \text{V}$  for R1\_{IN}.

Analog inputs above or below the expected range will yield either positive full-scale or negative full-scale digital outputs, respectively. Wrapping or folding over for analog inputs outside the nominal range will not occur.

NOTE: (1) Full-scale error includes offset and gain errors measured at both +FS and -FS.

FIGURE 6. Conversion and Read Timing with External Clock (EXT/INT tied HIGH) Read During a Conversion.

## **CALIBRATION**

#### HARDWARE CALIBRATION

To calibrate the offset and gain of the ADS7807 in hardware, install the resistors shown in Figure 7a. Table VI lists the hardware trim ranges relative to the input for each input range.

| INPUT RANGE | OFFSET ADJUST<br>RANGE (mV) | GAIN ADJUST<br>RANGE (mV) |

|-------------|-----------------------------|---------------------------|

| ±10V        | ±15                         | ±60                       |

| 0 to 5V     | ±4                          | ±30                       |

| 0 to 4V     | ±3                          | ±30                       |

TABLE VI. Offset and Gain Adjust Ranges for Hardware Calibration (see Figure 7a).

#### **SOFTWARE CALIBRATION**

To calibrate the offset and gain in software, no external resistors are required. However, to get the data sheet specifications for offset and gain, the resistors shown in Figure 7b are necessary. See the **No Calibration** section for more details on the external resistors. Refer to Table VIII for the range of offset and gain errors with and without the external resistors.

#### **NO CALIBRATION**

Figure 7b shows circuit connections. Note that the actual voltage dropped across the external resistors is at least two orders of magnitude lower than the voltage dropped across the internal resistor divider network. This should be considered when choosing the accuracy and drift specifications of the external resistors. In most applications, 1% metal-film resistors will be sufficient.

FIGURE 7a. Circuit Diagrams (With Hardware Trim).

FIGURE 7b. Circuit Diagrams (Without Hardware Trim).

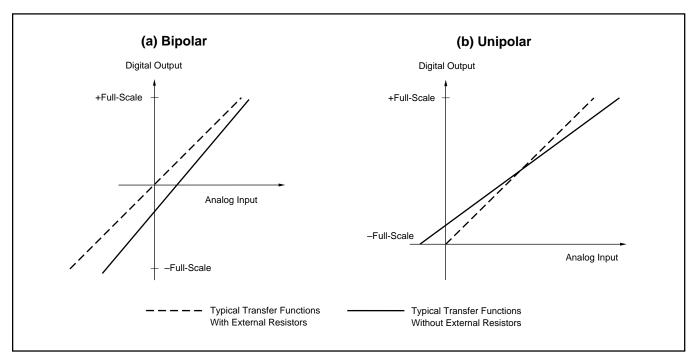

The external resistors (see Figure 7b) may not be necessary in some applications. These resistors provide compensation for an internal adjustment of the offset and gain which allows calibration with a single supply. Not using the external resistors will result in offset and gain errors in addition to those listed in the **Electrical Characteristics** section. Offset refers to the equivalent voltage of the digital output when converting with the input grounded. A positive gain error occurs when the equivalent output voltage of the digital output is larger than the analog input. Refer to Table VII for nominal ranges of gain and offset errors with and without the external resistors. Refer to Figure 8 for typical shifts in the transfer functions which occur when the external resistors are removed.

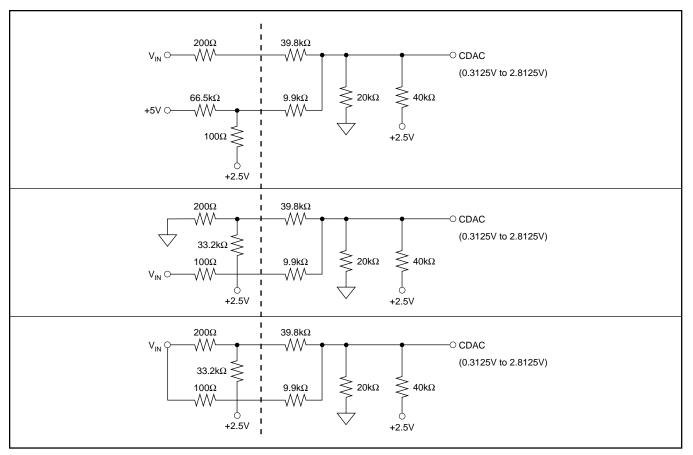

To further analyze the effects of removing any combination of the external resistors, consider Figure 9. The combination of the external and the internal resistors form a voltage divider which reduces the input signal to a 0.3125V to 2.8125V input range at the Capacitor Digital-to-Analog Converter (CDAC). The internal resistors are laser trimmed to high relative accuracy to meet full scale specifications. The actual input impedance of the internal resistor network looking into pin 1 or pin 3 however, is only accurate to  $\pm 20\%$  due to process variations. This should be taken into account when determining the effects of removing the external resistors.

## REFERENCE

The ADS7807 can operate with its internal 2.5V reference or an external reference. By applying an external reference to pin 5, the internal reference can be bypassed; REFD (pin 26) tied HIGH will power-down the internal reference reducing the overall power consumption of the ADS7807 by approximately 5mW.

|              |                | OFFSET ERROR                                                     |      | GAIN ERROR                                           |                                                       |                |  |

|--------------|----------------|------------------------------------------------------------------|------|------------------------------------------------------|-------------------------------------------------------|----------------|--|

| INPUT        | WITH RESISTORS | WITH RESISTORS WITHOUT RESISTORS  RANGE (mV) RANGE (mV) TYP (mV) |      | WITH RESISTORS                                       | WITHOUT RESISTORS                                     |                |  |

| RANGE (V)    | RANGE (mV)     |                                                                  |      | RANGE (% FS)                                         | RANGE (% FS)                                          | TYP            |  |

| ±10          | -10 ≤ BPZ ≤ 10 | 0 ≤ BPZ ≤ 35                                                     | 15   | $-0.4 \le G \le 0.4$<br>$0.15 \le G^{(1)} \le 0.15$  | $-0.3 \le G \le 0.5$<br>$-0.1 \le G^{(1)} \le 0.2$    | +0.05<br>+0.05 |  |

| 0 to 5       | -3 ≤ UPO ≤ 3   | -12 ≤ UPO ≤ -3                                                   | -7.5 | $-0.4 \le G \le 0.4$<br>$0.15 \le G^{(1)} \le 0.15$  | $-1.0 \le G \le 0.1$<br>$-0.55 \le G^{(1)} \le -0.05$ | -0.2<br>-0.2   |  |

| 0 to 4       | -3 ≤ UPO ≤ 3   | -10.5 ≤ UPO ≤ -1.5                                               | -6   | $-0.4 \le G \le 0.4$<br>$-0.15 \le G^{(1)} \le 0.15$ | $-1.0 \le G \le 0.1$<br>$-0.55 \le G^{(1)} \le -0.05$ | -0.2<br>-0.2   |  |

| NOTE: (1) Hi | gh Grade.      |                                                                  |      | •                                                    | 1                                                     |                |  |

TABLE VII. Range of Offset and Gain Errors With and Without External Resistors.

FIGURE 8. Typical Transfer Functions With and Without External Resistors.

FIGURE 9. Circuit Diagrams Showing External and Internal Resistors.

The internal reference has approximately an 8ppm/ $^{\circ}$ C drift (typical) and accounts for approximately 20% of the full-scale error (FSE =  $\pm 0.5\%$  for low grade,  $\pm 0.25\%$  for high grade).

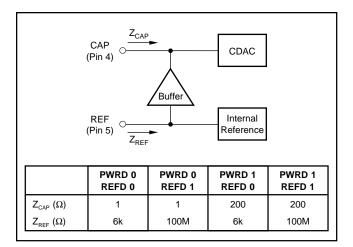

The ADS7807 also has an internal buffer for the reference voltage. Figure 10 shows characteristic impedances at the input and output of the buffer with all combinations of power-down and reference down.

FIGURE 10. Characteristic Impedances of Internal Buffer.

#### **REF**

REF (pin 5) is an input for an external reference or the output for the internal 2.5V reference. A 2.2µF tantalum capacitor should be connected as close as possible to the REF pin from ground. This capacitor and the output resistance of REF create a low-pass filter to bandlimit noise on the reference. Using a smaller value capacitor will introduce more noise to the reference, degrading the SNR and SINAD. The REF pin should not be used to drive external AC or DC loads, as shown in Figure 10.

The range for the external reference is 2.3V to 2.7V and determines the actual LSB size. Increasing the reference voltage will increase the full-scale range and the LSB size of the converter which can improve the SNR.

#### CAP

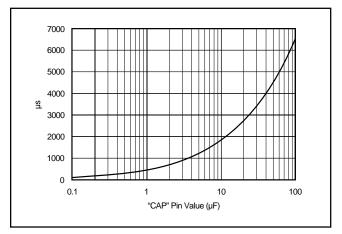

CAP (pin 4) is the output of the internal reference buffer. A  $2.2\mu F$  tantalum capacitor should be placed as close as possible to the CAP pin from ground to provide optimum switching currents for the CDAC throughout the conversion cycle. This capacitor also provides compensation for the output of the buffer. Using a capacitor any smaller than  $1\mu F$  can cause the output buffer to oscillate and may not have sufficient charge for the CDAC. Capacitor values larger than  $2.2\mu F$  will have little affect on improving performance. See Figures 10 and 11.

The output of the buffer is capable of driving up to 1mA of current to a DC load. Using an external buffer will allow the internal reference to be used for larger DC loads and AC loads. Do not attempt to directly drive an AC load with the output voltage on CAP. This will cause performance degradation of the converter.

FIGURE 11. Power-Down to Power-Up Time vs Capacitor Value on CAP.

## REFERENCE AND POWER-DOWN

The ADS7807 has analog power-down and reference power down capabilities via PWRD (pin 25) and REFD (pin 26), respectively. PWRD and REFD HIGH will power-down all analog circuitry maintaining data from the previous conversion in the internal registers, provided that the data has not already been shifted out through the serial port. Typical power consumption in this mode is  $50\mu$ W. Power recovery is typically 1ms, using a  $2.2\mu$ F capacitor connected to CAP. Figure 11 shows power-down to power-up recovery time relative to the capacitor value on CAP. With +5V applied to  $V_{DIG}$ , the digital circuitry of the ADS7807 remains active at all times, regardless of PWRD and REFD states.

#### **PWRD**

PWRD HIGH will power-down all of the analog circuitry except for the reference. Data from the previous conversion will be maintained in the internal registers and can still be read. With PWRD HIGH, a convert command yields meaningless data.

#### REFD

REFD HIGH will power-down the internal 2.5V reference. All other analog circuitry, including the reference buffer, will be active. REFD should be HIGH when using an external reference to minimize power consumption and the loading effects on the external reference. See Figure 10 for the characteristic impedance of the reference buffer's input for both REFD HIGH and LOW. The internal reference consumes approximately 5mW.

### LAYOUT

#### **POWER**

For optimum performance, tie the analog and digital power pins to the same +5V power supply and tie the analog and digital grounds together. As noted in the electrical characteristics, the ADS7807 uses 90% of its power for the analog circuitry. The ADS7807 should be considered as an analog component.

The +5V power for the A/D converter should be separate from the +5V used for the system's digital logic. Connecting  $V_{DIG}$  (pin 28) directly to a digital supply can reduce converter performance due to switching noise from the digital logic. For best performance, the +5V supply can be produced from whatever analog supply is used for the rest of the analog signal conditioning. If +12V or +15V supplies are present, a simple +5V regulator can be used. Although it is not suggested, if the digital supply must be used to power the converter, be sure to properly filter the supply. Either using a filtered digital supply or a regulated analog supply, both  $V_{DIG}$  and  $V_{ANA}$  should be tied to the same +5V source.

#### **GROUNDING**

Three ground pins are present on the ADS7807.  $D_{GND}$  is the digital supply ground.  $A_{GND2}$  is the analog supply ground.  $A_{GND1}$  is the ground to which all analog signals internal to the A/D converter are referenced.  $A_{GND1}$  is more susceptible to current induced voltage drops and must have the path of least resistance back to the power supply.

All the ground pins of the A/D converter should be tied to an analog ground plane, separated from the system's digital logic ground, to achieve optimum performance. Both analog and digital ground planes should be tied to the "system" ground as near to the power supplies as possible. This helps to prevent dynamic digital ground currents from modulating the analog ground through a common impedance to power ground.

#### SIGNAL CONDITIONING

The FET switches used for the sample hold on many CMOS A/D converters release a significant amount of charge injection which can cause the driving op amp to oscillate. The amount of charge injection due to the sampling FET switch on the ADS7807 is approximately 5% to 10% of the amount on similar A/D converters with the charge redistribution Digital-to-Analog Converter (DAC) CDAC architecture. There is also a resistive front end which attenuates any charge which is released. The end result is a minimal requirement for the drive capability on the signal conditioning preceding the A/D converter. Any op amp sufficient for the signal in an application will be sufficient to drive the ADS7807.

The resistive front end of the ADS7807 also provides a specified ±25V over-voltage protection. In most cases, this eliminates the need for external over-voltage protection circuitry.

#### INTERMEDIATE LATCHES

The ADS7807 does have tri-state outputs for the parallel port, but intermediate latches should be used if the bus will be active during conversions. If the bus is not active during conversion, the tri-state outputs can be used to isolate the A/D converter from other peripherals on the same bus.

Intermediate latches are beneficial on any monolithic A/D converter. The ADS7807 has an internal LSB size of  $38\mu V.$  Transients from fast switching signals on the parallel port, even when the A/D converter is tri-stated, can be coupled through the substrate to the analog circuitry causing degradation of converter performance.

## APPLICATIONS INFORMATION

#### TRANSITION NOISE

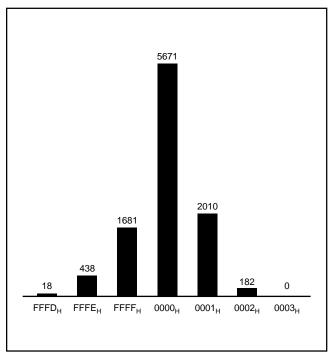

Apply a DC input to the ADS7807 and initiate 1000 conversions. The digital output of the converter will vary in output codes due to the internal noise of the ADS7807. This is true for all 16-bit SAR converters. The transition noise specification found in the **Electrical Characteristics** section is a statistical figure which represents the one sigma limit or rms value of these output codes.

Using a histogram to plot the output codes, the distribution should appear bell-shaped with the peak of the bell curve representing the nominal output code for the input voltage value. The  $\pm 1\sigma$ ,  $\pm 2\sigma$ , and  $\pm 3\sigma$  distributions will represent 68.3%, 95.5%, and 99.7% of all codes. Multiplying TN by 6 will yield the  $\pm 3\sigma$  distribution or 99.7% of all codes. Statistically, up to 3 codes could fall outside the 5 code distribution when executing 1000 conversions. The ADS7807 has a TN of 0.8LSBs which yields 5 output codes for a  $\pm 3\sigma$  distribution. Figures 12 and 13 show 1000 and 10000 conversion histogram results.

#### **AVERAGING**

The noise of the converter can be compensated by averaging the digital codes. By averaging conversion results, transition noise will be reduced by a factor of  $1/\sqrt{\text{Hz}}$  where n is the number of averages. For example, averaging four conversion results will reduce the TN by 1/2 to 0.4LSBs. Averaging should only be used for input signals with frequencies near DC.

For AC signals, a digital filter can be used to low-pass filter and decimate the output codes. This works in a similar manner to averaging: for every decimation by 2, the signalto-noise ratio will improve 3dB.

FIGURE 12. Histogram of 1000 Conversions with Input Grounded.

FIGURE 13. Histogram of 10000 Conversions with Input Grounded.

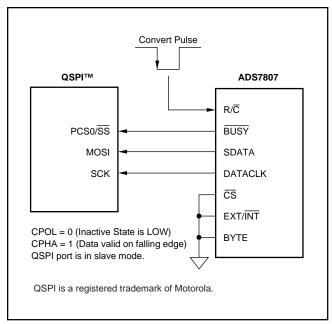

#### **QSPI™ INTERFACING**

Figure 14 shows a simple interface between the ADS7807 and any QSPI equipped microcontroller. This interface assumes that the convert pulse does not originate from the microcontroller and that the ADS7807 is the only serial peripheral.

FIGURE 14. QSPI Interface to the ADS7807.

Before enabling the QSPI interface, the microcontroller must be configured to monitor the slave select line. When a transition from LOW to HIGH occurs on Slave Select  $(\overline{SS})$  from  $\overline{BUSY}$  (indicating the end of the current conversion), the port can be enabled. If this is not done, the microcontroller and the A/D converter may be "out-of-sync".

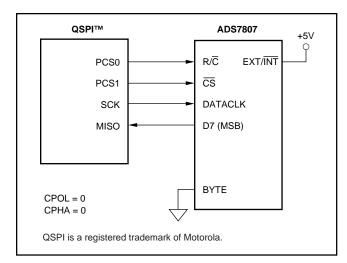

Figure 15 shows another interface between the ADS7807 and a QSPI equipped microcontroller which allows the microcontroller to give the convert pulses while also allowing multiple peripherals to be connected to the serial bus. This interface and the following discussion assume a master clock for the QSPI interface of 16.78MHz. Notice that the serial data input of the microcontroller is tied to the MSB (D7) of the ADS7807 instead of the serial output (SDATA). Using D7 instead of the serial port offers tri-state capability which allows other peripherals to be connected to the MISO pin. When communication is desired with those peripherals, PCS0 and PCS1 should be left HIGH; that will keep D7 tri-stated.

In this configuration, the QSPI interface is actually set to do two different serial transfers. The first, an 8-bit transfer, causes PCS0 (R/ $\overline{\text{C}}$ ) and PCS1 ( $\overline{\text{CS}}$ ) to go LOW, starting a conversion. The second, a 16-bit transfer, causes only PCS1 ( $\overline{\text{CS}}$ ) to go LOW. This is when the valid data will be transferred.

QSPI is a registered trademark of Motorola.

FIGURE 15. QSPI Interface to the ADS7807. Processor Initiates Conversions.

For both transfers, the DT register (delay after transfer) is used to cause a  $19\mu s$  delay. The interface is also set up to wrap to the beginning of the queue. In this manner, the QSPI is a state machine which generates the appropriate timing for the ADS7807. This timing is thus locked to the crystal-based timing of the microcontroller and not interrupt driven. So, this interface is appropriate for both AC and DC measurements.

For the fastest conversion rate, the baud rate should be set to 2 (4.19MHz SCK), DT set to 10, the first serial transfer set to 8 bits, the second set to 16 bits, and DSCK disabled (in the command control byte). This will allow for a 23kHz maximum conversion rate. For slower rates, DT should be increased. Do not slow SCK as this may increase the chance of affecting the conversion results or accidently initiating a second conversion during the first 8-bit transfer.

In addition, CPOL and CPHA should be set to zero (SCK normally LOW and data captured on the rising edge). The command control byte for the 8-bit transfer should be set to  $20_{\rm H}$  and for the 16-bit transfer to  $61_{\rm H}$ .

#### **SPI™ INTERFACE**

The SPI interface is generally only capable of 8-bit data transfers. For some microcontrollers with SPI interfaces, it might be possible to receive data in a similar manner as shown for the QSPI interface in Figure 14. The microcontroller will need to fetch the 8 most significant bits before the contents are overwritten by the least significant bits.

A modified version of the QSPI interface shown in Figure 15 might be possible. For most microcontrollers with SPI interface, the automatic generation of the start-of-conversion pulse will be impossible and will have to be done with software. This will limit the interface to 'DC' applications due to the insufficient jitter performance of the convert pulse itself.

SPI is a registered trademark of Motorola.

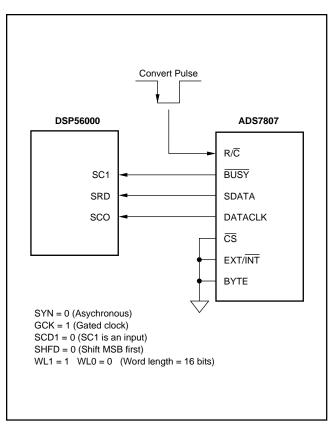

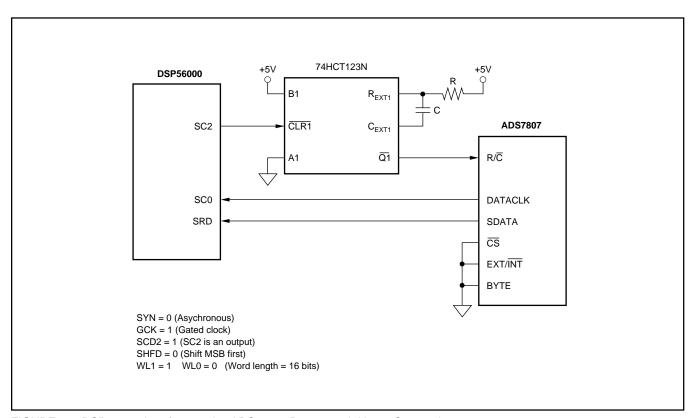

#### **DSP56000 INTERFACING**

The DSP56000 serial interface has SPI compatibility mode with some enhancements. Figure 16 shows an interface between the ADS7807 and the DSP56000 which is very similar to the QSPI interface seen in Figure 14. As mentioned in the **QSPI** section, the DSP56000 must be programmed to enable the interface when a LOW to HIGH transition on SC1 is observed (BUSY going HIGH at the end of conversion).