# 1024 (H) x 1024 (V) Interline CCD Image Sensor

#### Description

The KAI–1003 Image Sensor is a high-performance megapixel monochrome image sensor designed for a wide range of medical imaging and machine vision applications.

The 12.8  $\mu$ m square pixels with microlenses provide high sensitivity and the large capacity results in large dynamic range. The two output, split horizontal register and several binning modes allow a 15 to 60 frame per second (fps) video rate for the progressively scanned images.

The vertical overflow drain structure provides anti-blooming protection, and enables electronic shuttering for precise exposure control. Other features include low dark current, negligible lag and low smear.

| Parameter                                                                 | Typical Value                                                            |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Architecture                                                              | Interline CDD; Progressive Scan                                          |

| Total Number of Pixels                                                    | 1056 (H) × 1032 (V)                                                      |

| Number of Effective Pixels                                                | 1028 (H) × 1028 (V)                                                      |

| Number of Active Pixels                                                   | 1024 (H) × 1024 (V)                                                      |

| Pixel Size                                                                | 12.8 μm(H) × 12.8 μm (V)                                                 |

| Active Image Size                                                         | 13.1 mm (H) × 13.1 mm (V),<br>18.5 mm (Diagonal),<br>4/3″ Optical Format |

| Aspect Ratio                                                              | 1:1                                                                      |

| Number of Outputs                                                         | 1 or 2                                                                   |

| Charge Capacity                                                           | 170,000 e⁻                                                               |

| Output Sensitivity                                                        | 7.5 μV/e <sup>-</sup>                                                    |

| Quantum Efficiency (500 nm)                                               | 45%                                                                      |

| Read Noise (f = 20 MHz)                                                   | 40 e <sup>-</sup> rms                                                    |

| Dark Current                                                              | < 0.5 nA/cm <sup>2</sup>                                                 |

| Dynamic Range                                                             | 72 dB                                                                    |

| Blooming Suppression                                                      | > 100 X                                                                  |

| Smear                                                                     | -80 dB                                                                   |

| Maximum Pixel Clock Speed                                                 | 20 MHz                                                                   |

| Maximum Frame Rate<br>Single Output<br>Dual Output<br>Dual Output 2×2 Bin | 15 fps<br>30 fps<br>60 fps                                               |

| Package                                                                   | 28-Pin CERDIP                                                            |

| Cover Glass                                                               | AR Coated, 2 Sides                                                       |

NOTE: All Parameters are specified at T = 40°C unless otherwise noted.

# **ON Semiconductor®**

www.onsemi.com

#### Figure 1. KAI–1003 Interline CCD Image Sensor

#### Features

- Megapixel Progressive Scan Interline CCD

- 1024 (H) × 1024 (V) Imaging Pixels

- 12.8 µm Square Pixels

- 13.1 mm Square Imaging Area

- Microlenses for Increased Sensitivity

- Large Capacity (170 ke<sup>-</sup>)

- Split Horizontal Register for 1 or 2 Outputs

- Binning to  $1 \times 2$  or  $2 \times 2$

#### Applications

- Machine Vision

- Medical

- Scientific

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

# **ORDERING INFORMATION**

#### Table 2. ORDERING INFORMATION – KAI–1003 IMAGE SENSOR

| Part Number        | Description                                                                                                                           | Marking Code  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| KAI-1003-AAA-CR-AE | Monochrome, No Microlens, CERDIP Package (Sidebrazed),<br>Taped Clear Cover Glass with AR Coating (Both Sides), Engineering Sample    | KAI–1003      |  |

| KAI-1003-AAA-CR-B2 | Monochrome, No Microlens, CERDIP Package (Sidebrazed),<br>Taped Clear Cover Glass with AR Coating (Both Sides), Grade 2               | Serial Number |  |

| KAI-1003-ABA-CD-AE | Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Clear Cover Glass with AR Coating (Both Sides), Engineering Sample |               |  |

| KAI-1003-ABA-CD-B2 | Monochrome, Telecentric Microlens, CERDIP Package (Sidebrazed),<br>Clear Cover Glass with AR Coating (Both Sides), Grade 2            | Serial Number |  |

## Table 3. ORDERING INFORMATION – EVALUATION SUPPORT

| Part Number          | Description                     |

|----------------------|---------------------------------|

| KAI-1003-12-20-A-EVK | Evaluation Board (Complete Kit) |

See the ON Semiconductor *Device Nomenclature* document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at <u>www.onsemi.com</u>.

# **DEVICE DESCRIPTION**

#### Architecture

The KAI–1003 is a high-performance, interline charge-coupled device (CCD) designed for a wide range of medical imaging and machine vision applications. The device is built using an advanced two-phase, double-polysilicon, NMOS CCD technology. The p+npn-photodiodes eliminate image lag while providing anti-blooming protection and electronic shutter capability. The 12.8  $\mu$ m square pixels with microlenses provide high sensitivity and large dynamic range. The two output, split horizontal register and several binning modes enable a 15 to 60 frame per second (fps) video rate with this megapixel progressive scan imager.

#### **Image Acquisition**

An electronic representation of an image is formed when incident photons falling on the sensor plane create electron-hole pairs within the individual silicon photodiodes. These photoelectrons are collected locally by the formation of potential wells at each photodiode. Below photodiode saturation, the number of photoelectrons collected at each pixel is linearly dependent on light level and integration time and non-linearly dependent on wavelength. When the photodiode's charge capacity is reached, excess electrons are discharged into the substrate to prevent blooming. The integration time can be decreased below the frame time by using an electronic shutter, which is a voltage pulse applied to the substrate to empty the photodiodes.

#### **Charge Transport**

The integrated charge from each photodiode is transported to the output by a three-step process. The charge is first transferred from the photodiodes to the vertical shift registers by applying a large positive voltage to one of the vertical CCD phases. This transfer occurs simultaneously for all photodiodes. The charge is then transported from the vertical CCD registers to the horizontal CCD line by line in parallel. Finally, the horizontal CCD register transports each line of charge pixel by pixel serially to one or both of the output structures.

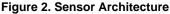

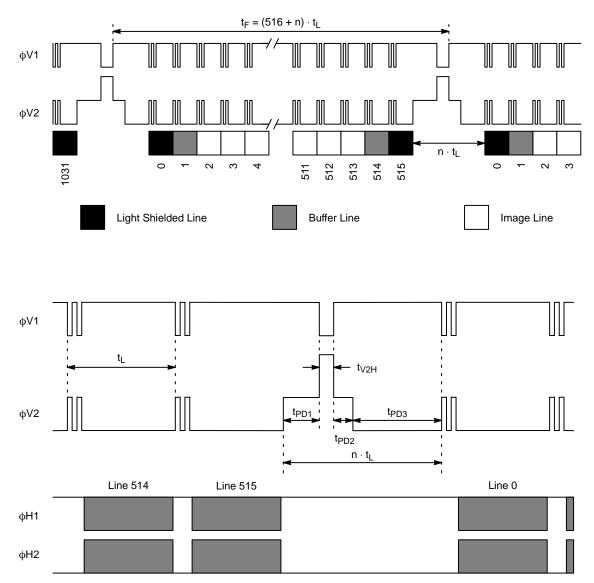

The single horizontal CCD register is split into two halves to allow a variety of line readout modes, as shown in Figure 2 and Figure 3. The A output half of the register is a true two-phase design, which results in unidirectional transport using phases H1A and H2A. The B output half of the register is a pseudo two-phase design, which allows bi-directional transport using phases H1B, H2B, H1C and H2C. Dual output is achieved with all of the first phases identical and all the second phases identical. If the clocks of H1A and H2A phases are shifted by one half cycle, the output remains dual with the outputs alternating, so that only one analog-to-digital converter is necessary. Finally, single output of the entire image from the A output is obtained by

complementing the C phases, which reverses transport in the B half of the horizontal CCD.

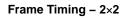

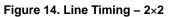

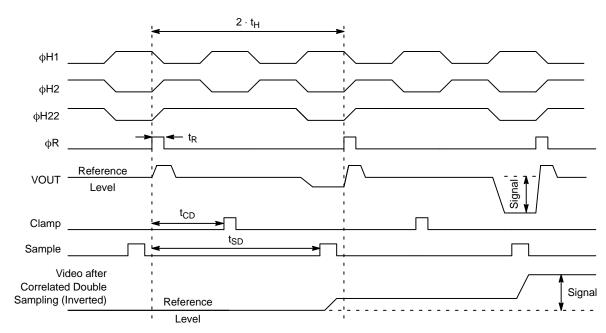

Binning can be used in a  $1\times 2$  and a  $2\times 2$  mode. Two successive vertical transfers vertically bin the charge directly onto the horizontal CCD, as shown in Figure 13 and Figure 14. Horizontal binning is accomplished by two successive horizontal transfers onto the H22 gate, which then transfers the charge to the output structure, as shown in Figure 15.

Combinations of output modes, binning and horizontal clock frequency allow the range of frame rates listed in.

|                                  | Binning (H × V)<br>Output | 1×1<br>Dual  | 1×2<br>Dual  | 2×1<br>Dual | 2×2         | 1×1<br>Single |          |

|----------------------------------|---------------------------|--------------|--------------|-------------|-------------|---------------|----------|

| Parameter                        |                           |              |              |             | Dual        |               | Unit     |

| HORIZONTAL CLOCH                 | K                         |              |              |             |             |               |          |

| Frequency                        |                           | 20           | 20           | 20          | 40          | 20            | MHz      |

| Period                           | Actual<br>Effective       | 50<br>50     | 50<br>50     | 50<br>100   | 25<br>50    | 50<br>50      | ns       |

| Pixel Counts                     | Actual<br>Effective       | 532<br>532   | 532<br>532   | 532<br>266  | 532<br>266  | 1060<br>1060  |          |

| VERTICAL TO HORIZ                | ONTAL TRANSFER (H         | IORIZONTAL F | RETRACE TIME | E)          |             |               |          |

| Equivalent H-Clock<br>Counts (m) |                           | 80           | 80           | 80          | 160         | 80            |          |

| Duration                         |                           | 4.0          | 4.0          | 4.0         | 4.0         | 4.0           | μS       |

| HORIZONTAL LINE T                | IME                       |              |              |             |             |               | •        |

| Total H-Clock<br>Counts          |                           | 612          | 612          | 612         | 692         | 1140          |          |

| Line time                        |                           | 30.6         | 30.6         | 30.6        | 17.3        | 57.0          | μS       |

| VERTICAL CLOCK                   |                           |              |              |             |             |               | •        |

| Line Counts                      | Actual<br>Effective       | 1032<br>1032 | 1032<br>516  | 1032<br>516 | 1032<br>516 | 1032<br>1032  |          |

| PHOTODIODE READ                  | (VERTICAL RETRACE         | TIME)        |              |             |             |               |          |

| Equivalent Line<br>Counts (n)    |                           | 4            | 4            | 4           | 7           | 2             |          |

| Duration                         |                           | 122.4        | 122.4        | 122.4       | 121.1       | 114.0         | μS       |

| FRAME RATE                       |                           |              | ·            | ·           |             |               |          |

| Total Effective Line<br>Counts   |                           | 1036         | 520          | 520         | 523         | 1034          |          |

| Frame Time                       |                           | 31.7         | 15.9         | 15.9        | 9.0         | 58.9          | ms       |

| Frame Rate                       |                           | 31.5         | 62.8         | 62.8        | 110.5       | 17.0          | frames/s |

# Table 4. KAI–1003 CALCULATED CLOCK PARAMETERS

1. Time values have been rounded.

2. The number of counts (n and m) shown here are nominal integers, but in general they do not need be integers. They can be adjusted for frame time, so long as the horizontal and vertical retrace times exceed the minimums specified in AC Timing Requirements.

3. Operation at 40 MHz will have increased readout noise.

## **Output Structure**

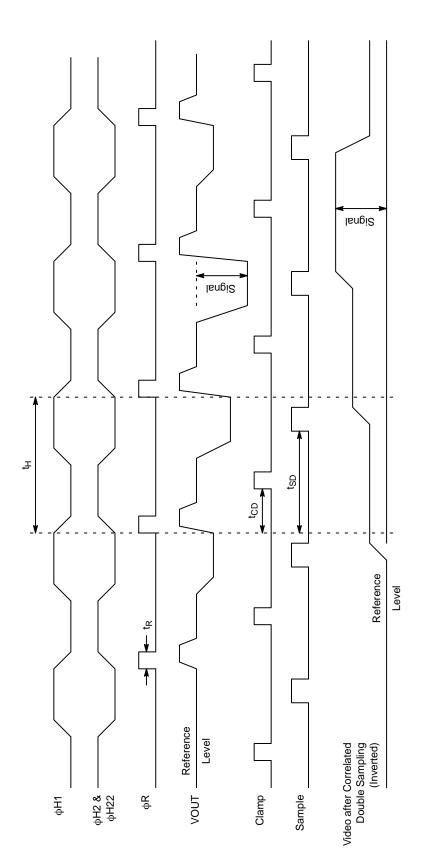

Charge presented to the floating diffusion (FD) is converted into a voltage and current amplified in order to drive off-chip loads. The resulting voltage change seen at the output is linearly related to the amount of charge placed on the FD. Once the signal has been sampled by the system electronics, the reset gate ( $\phi R$ ) is clocked to remove the signal and the FD is reset to the potential applied by the reset drain (RD). More signal at the floating diffusion reduces the voltage seen at the output pin. In order to activate the output structure, an off-chip load must be added to the output pin of the device.

#### **Non-Imaging Pixels**

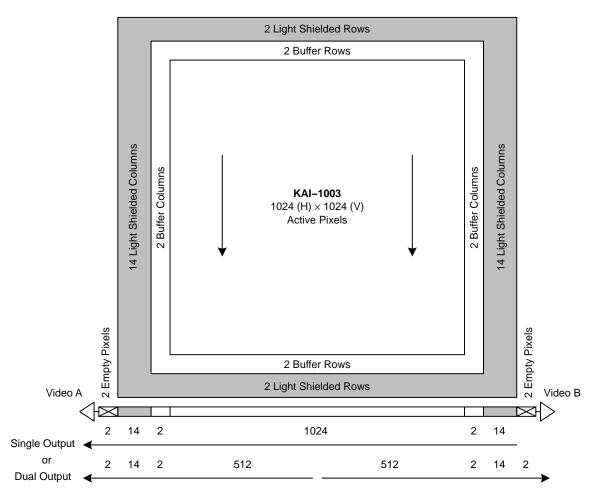

In addition to the 1024 (H) by 1024 (V) imaging pixels, there are active buffer, light shielded and empty pixels, as

shown in Figure 2. A two-pixel border of active buffer pixels surrounds the imaging area. These buffer pixels respond to illumination but are not tested for defects and non-uniformities. Two light shielded rows lead and follow each frame, and 14 light shielded columns lead and follow each line. The light shielded columns are tested for column defects and can be used for dark reference. Only the center 10 columns by 1028 rows of light shielded region on each side can be used for dark reference due to light leakage into the border of two pixels at the edges. Finally, two empty pixels occur at the beginning of each line, which are empty shift register cycles not associated with any vertical CCD columns. Empty pixels may also occur at the end of the line, depending on the timing.

Figure 3. Horizontal CCD Registers

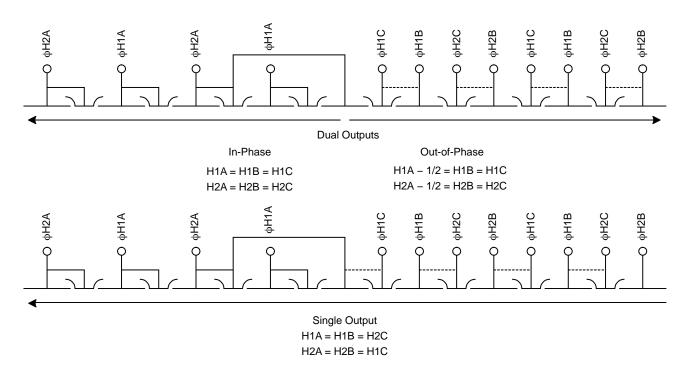

#### **Pin Description and Device Orientation**

## Table 5. PIN DESCRIPTION

| Pin No. | Label |

|---------|-------|

| 1       | φV1   |

| 2       | GND   |

| 3       | SUB   |

| 4       | VDD   |

| 5       | VOUTA |

| 6       | VLG   |

| 7       | RDA   |

| 8       | φRA   |

| 9       | OGA   |

| 10      | SUB   |

| 11      | φH1A  |

| 12      | φΗ2Α  |

| 13      | φH22A |

| 14      | GND   |

| Pin No. | Label         |

|---------|---------------|

| 15      | φH22B         |

| 16      | ф <b>H</b> 2B |

| 17      | φH2C          |

| 18      | φH1C          |

| 19      | φH1B          |

| 20      | OGB           |

| 21      | φRB           |

| 22      | RDB           |

| 23      | VSS           |

| 24      | VOUTB         |

| 25      | VMIN          |

| 26      | SUB           |

| 27      | GND           |

| 28      | φV2           |

# PERFORMANCE SPECIFICATIONS

#### **Table 6. PERFORMANCE SPECIFICATIONS**

(All values measured at  $40^{\circ}$ C and 30 fps (integration time = 33 ms, f<sub>H</sub> = 20 MHz) for nominal operating parameters unless otherwise noted. These parameters exclude defective pixels.)

| Description                                             | Symbol            | Min. | Nom.  | Max. | Unit               |

|---------------------------------------------------------|-------------------|------|-------|------|--------------------|

| Saturation Charge Capacity with Blooming Control        | Q <sub>SAT</sub>  | 170  | -     | -    | ke-                |

| Output Gain                                             |                   | 6.5  | 7.5   | 8.5  | μV/e⁻              |

| Output Voltage at the Saturation Level                  | V <sub>SAT</sub>  | -    | 1.3   | -    | V                  |

| Quantum Efficiency at 500 nm                            |                   | -    | 32    | -    | %                  |

| Quantum Efficiency at 540 nm                            |                   | -    | 30    | -    | %                  |

| Quantum Efficiency at 600 nm                            |                   | -    | 24    | -    | %                  |

| CCD Readout Noise with CDS                              |                   | -    | 40    | 50   | e⁻ rms             |

| Dark Current                                            | I <sub>DARK</sub> | -    | 0.25  | 0.45 | nA/cm <sup>2</sup> |

| Anti-Blooming Factor (Notes 1, 2)                       | X <sub>AB</sub>   | 100  | -     | -    |                    |

| Vertical Smear (Notes 2, 6)                             |                   | -    | 0.005 | 0.01 | %                  |

| Non-Uniformity of Sensitivity (Notes 3, 4)              |                   | -    | 0.3   | 0.5  | % rms              |

| Non-Uniformity of Dark Current (Note 4)                 |                   | -    | 14    | -    | e <sup>-</sup> rms |

| Output Signal Non-Linearity (Note 5)                    |                   | -    | 1     | 2    | %                  |

| Gain Difference between the Two Video Outputs (Note 5)  |                   | -    | -     | 10   | %                  |

| Non-Uniformity of Gain between the Two Outputs (Note 5) |                   | -    | 0.5   | 1.5  | %                  |

1. The illumination required to bloom the image sensor reported as a multiple of the saturation intensity. Blooming is defined as doubling the vertical height of a spot that is 10% of the vertical CCD height at the saturation intensity.

2. Measured with continuous green light centered at 550 nm, F/4 optics and a spot size that is 10% of the vertical CCD height.

3. Measured at 90% of 150 ke<sup>-</sup> output.

4. Measured in the center  $50 \times 50$  pixels.

5. Between 10% and 90% of 150 ke<sup>-</sup> output.

6. Measured without electronic shutter operation.

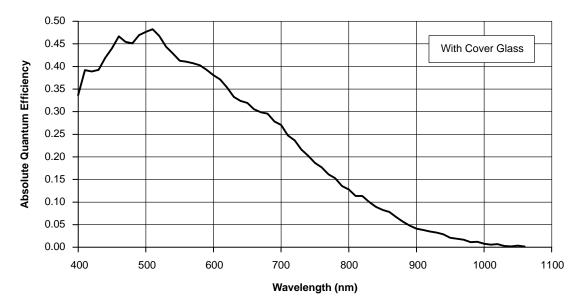

## **Typical Quantum Efficiency**

Figure 5. Quantum Efficiency Spectrum

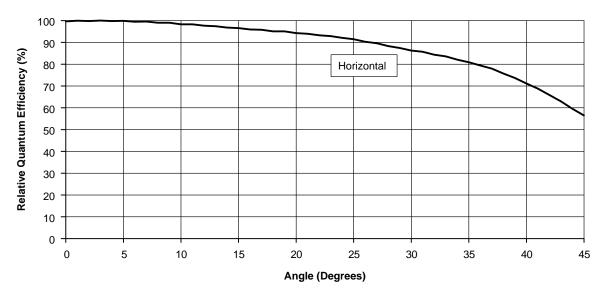

# Angular Dependance of Quantum Efficiency

For the curve marked "Horizontal", the incident light angle is varied in a plane parallel to the HCCD.

Figure 6. Angular Dependance of Quantum Efficiency

# DEFECT SPECIFICATIONS

## **Defect Test Conditions**

| Temperature:      | 40°C                                                         |

|-------------------|--------------------------------------------------------------|

| Integration Time: | 33 ms (20 MHz HCCD Frequency, No Binning, 30 fps Frame Rate) |

| Light Source:     | Continuous Green Light Centered at 550 nm                    |

| Operation:        | Nominal Voltages and Timing                                  |

#### Table 7. DEFECT DEFINITIONS

| Name                  | Maximum<br>Number | Definition                                                                                                                                                                                                                                        |

|-----------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Major Defective Pixel | 20                | A pixel whose signal deviates by more than 25 mV from the mean value of all active pixels under dark field condition or by more than 8% from the mean value of all active pixels under uniform illumination at 105 ke <sup>-</sup> output signal. |

| Minor Defective Pixel | 100               | A pixel whose signal deviates by more than 8 mV from the mean value of all active pixels under dark field condition.                                                                                                                              |

| Cluster Defect        | 4                 | A group of 2 to 6 contiguous major defective pixels, but no more than 2 adjacent defects horizontally.                                                                                                                                            |

| Column Defect         | 0                 | A group of more than 6 contiguous major defective pixels along a single column.                                                                                                                                                                   |

# **Defect Proximity**

Minimum Distance between Defective Clusters: Minimum Distance between Defective Columns:

2 Pixels in All Directions without Major Pixel Defects 3 Columns without Column Defects or Cluster Defects

# **OPERATION**

#### **Table 8. ABSOLUTE MAXIMUM RATINGS**

| Item                   | Description                                               | Min. | Max | Unit |

|------------------------|-----------------------------------------------------------|------|-----|------|

| Temperature            | Operation to Specification                                | 0    | 40  | °C   |

|                        | Operation without Damage                                  | -10  | 70  | °C   |

|                        | Storage                                                   | -55  | 80  | °C   |

| Relative Humidity      | Operation without Damage (Note 1)                         | 0    | 95  | %    |

| Voltage (Between Pins) | SUB – GND (Notes 2, 5)                                    | -0.6 | 50  | V    |

|                        | V <sub>RD</sub> , V <sub>SS</sub> , V <sub>DD</sub> – GND | -0.6 | 25  | V    |

|                        | V <sub>MIN</sub> – GND                                    | –15  | 0.6 | V    |

|                        | All Clocks – GND                                          | -    | 17  | V    |

|                        | $\phi$ V1 – $\phi$ V2 (Note 3)                            | -    | 17  | V    |

|                        | φH1 – φH2                                                 | -    | 17  | V    |

|                        | φH1, φH2 – φV2                                            | -    | 17  | V    |

|                        | φH2 – OG                                                  | -    | 17  | V    |

|                        | V <sub>LG</sub> , OG – GND                                | -    | 17  | V    |

|                        | $\phi R, \phi H1, \phi H2 - V_{MIN}$                      | -    | 17  | V    |

| Capacitance            | Output Load Capacitance (C <sub>LOAD</sub> ) (Note 4)     | -    | 10  | pF   |

| Current                | Output Bias Current (I <sub>DD</sub> ) (Note 4)           | -    | 10  | mA   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Without condensation.

2. Under normal operating conditions, the substrate voltage should be maintained above 8.0 V. The substrate voltage should not remain above 25 V for longer than 100 μs.

3. Maximum of 20 V for  $\phi$ V1H –  $\phi$ V2L, with 20  $\mu$ s maximum duration.

4. Each output.

5. Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions.

#### **Table 9. DC OPERATING CONDITIONS**

| Description                      | Symbol           | Min. | Nom. | Max. | Unit |

|----------------------------------|------------------|------|------|------|------|

| Output Gate                      | OG               | 1.8  | 2.0  | 2.2  | V    |

| Reset Drain                      | V <sub>RD</sub>  | 10.0 | 10.5 | 11.0 | V    |

| Output Amplifier Return (Note 1) | V <sub>SS</sub>  | -    | 0.0  | -    | V    |

| Output Amplifier Load Gate       | V <sub>LG</sub>  | 1.4  | 1.5  | 1.6  | V    |

| Output Amplifier Supply          | V <sub>DD</sub>  | 14.5 | 15.0 | 15.5 | V    |

| Disable ESD Protection (Note 2)  | V <sub>MIN</sub> | -    | -8.5 | -    | V    |

| Substrate (Notes 3, 4, 5)        | V <sub>SUB</sub> | 8.0  | TBS  | 18.0 | V    |

| Ground, P-Well (Note 4)          | GND              | -    | 0.0  | -    | V    |

1. Current sink.

2. Connect a 0.001  $\mu$ F capacitor between V<sub>MIN</sub> and GND. V<sub>MIN</sub> must be more negative than the low voltage of any of the  $\phi$ H clocks and should be established before the  $\phi$ H voltage is applied.

3. DC value when electronic shutter is not in use. See AC Clock Level Conditions for electronic shutter pulse voltage. The operating value of the substrate voltage, V<sub>SUB</sub>, will be supplied with each shipment.

Ground and substrate biases should be established before other gate and diode potentials are applied.

5. Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions.

## Table 10. AC CLOCK LEVEL CONDITIONS

| Description                           | Level        | Symbol               | mbol Min. |      | Max. | Unit |

|---------------------------------------|--------------|----------------------|-----------|------|------|------|

| Vertical CCD Clocks                   | High         | φV2H                 | 9.5       | 10.5 | 11.5 | V    |

| (Note 1)                              | Mid          | φV1M, φV2M           | -0.8      | -0.5 | 0.0  | V    |

|                                       | Low          | φV1L, φV2L           | -9.0      | -8.5 | -8.0 | V    |

| Horizontal CCD Clocks<br>(Note 1)     | High         | φΗ1Η, φΗ2Η           | 4.5       | 5.0  | 5.5  | V    |

|                                       | Low          | φH1L, φH2L           | -6.5      | -6.0 | -5.5 | V    |

| Reset Clock                           | Amplitude    | φR <sub>SWING</sub>  | -         | 5.0  | -    | V    |

|                                       | Low (Note 2) | V <sub>¢Rlow</sub>   | 0         | TBS  | 5.0  | V    |

| Electronic Shutter Pulse (Notes 3, 4) | Shutter      | V <sub>SHUTTER</sub> | 37        | 40   | 45   | V    |

1. For best results, the CCD clock swings must be greater than or equal to the nominal values.

2. Reset clock low level voltage will be supplied with each shipment.

3. Electronic shutter pulse voltage referenced to GND. See DC Operating Conditions for DC level when electronic shutter is not in use.

4. Refer to Application Note Using Interline CCD Image Sensors in High Intensity Visible Lighting Conditions.

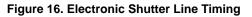

#### **Electronic Shutter Operation**

Electronic shuttering is accomplished by pulsing the substrate voltage to empty the photodiodes. See Figure 16

for timing. The pulse must not occur while useful information is being read from a line.

## Table 11. CALCULATED CLOCK CAPACITANCE

| Description                           | Phase    | Symbol                  | Typical | Unit |

|---------------------------------------|----------|-------------------------|---------|------|

| Vertical CCD Clocks                   | 1 to GND | C φV1                   | 55/37   | nF   |

| (Note 1)                              | 2 to GND | C φV2                   | 50/32   | nF   |

|                                       | 1 to 2   | C φV1 – φV2             | 4       | nF   |

| Horizontal CCD Clocks<br>(Notes 1, 2) | 1A       | C φH1A                  | 58/21   | pF   |

|                                       | 1B       | C φH1B                  | 41/13   | pF   |

|                                       | 1C       | C φH1C                  | 15/10   | pF   |

|                                       | 2A       | C φH2A                  | 48/22   | pF   |

|                                       | 2B       | С фН2В                  | 30/11   | pF   |

|                                       | 2C       | C <sub>\$\phi</sub> H2C | 18/13   | pF   |

| HCCD Summing Clock                    |          | С фН22А/В               | 3       | pF   |

| Reset Clock – GND                     |          | C $\phi$ RA/B           | 5       | pF   |

1. Accumulation/depletion capacitances.

2. Capacitance of this gate to GND and all other gates.

#### **Table 12. AC TIMING REQUIREMENTS**

| Description                             | Symbol                                | Min.    | Nom.    | Max. | Unit |

|-----------------------------------------|---------------------------------------|---------|---------|------|------|

| Vertical High Level Duration            | t <sub>V2H</sub>                      | 15      | -       | 20   | μs   |

| Vertical Transfer Time (Note 1)         | t <sub>V</sub>                        | 1.0     | 2.0/1.0 | -    | μS   |

| Vertical Pedestal Delay 1 & 3           | t <sub>VPD1</sub> , t <sub>VPD3</sub> | 40      | -       | -    | μs   |

| Vertical Pedestal Delay 2               | t <sub>VPD2</sub>                     | 15      | -       | -    | μs   |

| Horizontal Delay (Note 1)               | t <sub>HD</sub>                       | 1.5/0.5 | -       | -    | μs   |

| Reset Duration (Note 2)                 | t <sub>R</sub>                        | -       | 10      | -    | ns   |

| Horizontal CCD Clock Frequency (Note 3) | fH                                    | -       | 20      | -    | MHz  |

| Pixel Time                              | t <sub>H</sub>                        | -       | 50      | -    | ns   |

| Line Time (Note 4)                      | tL                                    | -       | -       | -    |      |

| Frame Time (Note 4)                     | t <sub>F</sub>                        | -       | -       | -    |      |

| Clamp Delay (Note 5)                    | t <sub>CD</sub>                       | -       | -       | -    | ns   |

| Sample Delay (Note 5)                   | t <sub>SD</sub>                       | -       | -       | -    | ns   |

| Electronic Shutter Pulse Duration       | t <sub>ES</sub>                       | 5       | 7.5     | 10   | μs   |

| Electronic Shutter Horizontal Delay     | t <sub>ESHD</sub>                     | 1.0     | -       | -    | μs   |

Non-binning/binning times.

The rising edge of φR should be coincident with the rising edge of φH22, within ±5 ns.

Horizontal CCD clock frequency can be increased to 40 MHz, with increased readout noise.

See Table 4 for nominal line and frame time in each mode.

5. The clamp delay and sample delay should be adjusted for optimum results.

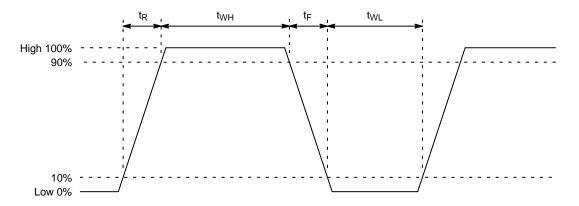

## Table 13. CCD CLOCK WAVEFORM CONDITIONS

| Description           | Phase               | Symbol | t <sub>WH</sub> | t <sub>WL</sub> | t <sub>R</sub> | t <sub>F</sub> | Unit |

|-----------------------|---------------------|--------|-----------------|-----------------|----------------|----------------|------|

| NON-BINNING           |                     |        |                 |                 |                |                |      |

| Vertical CCD Clocks   | 1                   | φV1M/L | -               | 1.5             | 0.5            | 0.5            | μS   |

|                       | 2                   | φV2M/L | 1.5             | -               | 0.5            | 0.5            | μS   |

|                       | 2, High             | φV2H   | 15              |                 | 1.0            | 1.0            | μs   |

| Horizontal CCD Clocks | 1                   | φH1    | 20.5            | 21.5            | 4.0            | 4.0            | ns   |

|                       | 2                   | φH2    | 20.5            | 21.5            | 4.0            | 4.0            | ns   |

|                       | 2, Binning (Note 1) | φH22   | 20.5            | 21.5            | 4.0            | 4.0            | ns   |

| Reset clock           |                     | φR     | 5               | 39              | 3              | 3              | ns   |

#### 2×2 BINNING

| Vertical CCD Clocks   | 1 (Note 2) | φV1M/L | 0.5  | 0.5  | 0.5 | 0.5 | μs |

|-----------------------|------------|--------|------|------|-----|-----|----|

|                       | 2 (Note 2) | φV2M/L | 0.5  | 0.5  | 0.5 | 0.5 | μs |

|                       | 2, High    | φV2H   | 15   | -    | 1.0 | 1.0 | μs |

| Horizontal CCD Clocks | 1          | φH1    | 20.5 | 21.5 | 4.0 | 4.0 | ns |

|                       | 2          | φH2    | 20.5 | 21.5 | 4.0 | 4.0 | ns |

|                       | 2, Binning | φH22   | 46.0 | 46.0 | 4.0 | 4.0 | ns |

| Reset clock           |            | φR     | 5    | 89   | 3   | 3   | ns |

Typical values measured with clocks connected to image sensor device. The actual values should be optimized for particular board layout.

φH22 may be connected to φH2 in 1×1 mode.

t<sub>WH</sub> and t<sub>WL</sub> for φV1M/L and φV2M/L are the time periods during the double pulses.

# TIMING

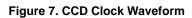

Frame Timing – 1×1

Figure 8. Frame Timing – 1×1

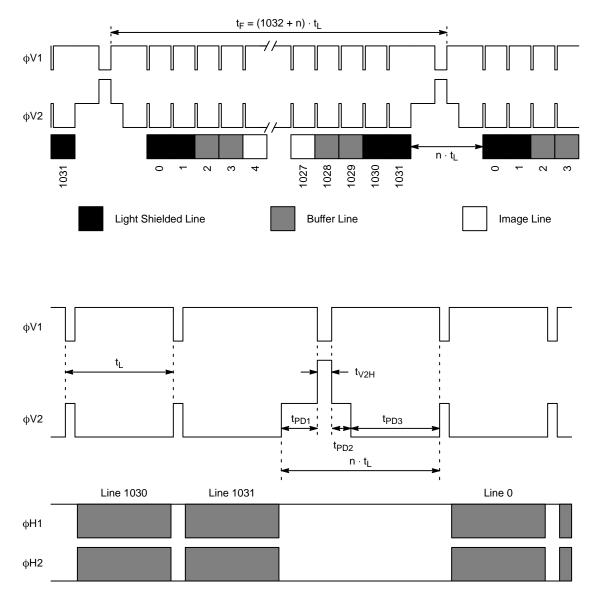

Figure 9. Line Timing – 1×1 – Single Output

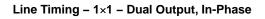

Figure 10. Line Timing – 1×1 – Dual Output, In-Phase

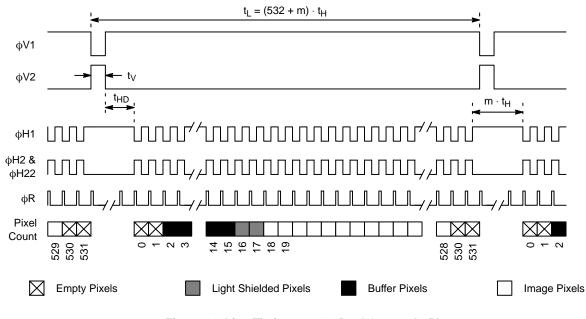

Figure 11. Line Timing – 1×1 – Dual Output, Out-of-Phase

Figure 12. Pixel Timing – 1×1

Figure 13. Frame Timing – 2×2

# Line Timing – 2×2

Pixel Timing – 2×2

# **Electronic Shutter Line Timing**

# Figure 17. Integration Time Definition

# REFERENCES

For information on ESD and cover glass care and cleanliness, please download the *Image Sensor Handling and Best Practices* Application Note (AN52561/D) from www.onsemi.com.

For information on environmental exposure, please download the *Using Interline CCD Image Sensors in High Intensity Lighting Conditions* Application Note (AND9183/D) from <u>www.onsemi.com</u>.

For information on soldering recommendations, please download the Soldering and Mounting Techniques Reference Manual (SOLDERRM/D) from www.onsemi.com. For quality and reliability information, please download the *Quality & Reliability* Handbook (HBD851/D) from <u>www.onsemi.com</u>.

For information on device numbering and ordering codes, please download the *Device Nomenclature* technical note (TND310/D) from <u>www.onsemi.com</u>.

For information on Standard terms and Conditions of Sale, please download <u>Terms and Conditions</u> from <u>www.onsemi.com</u>.

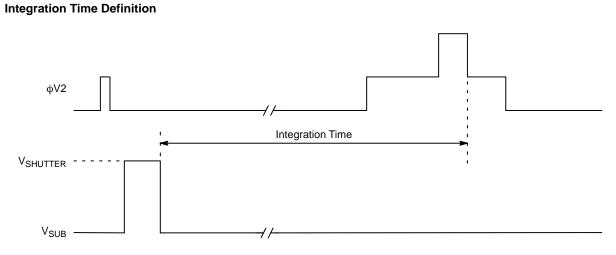

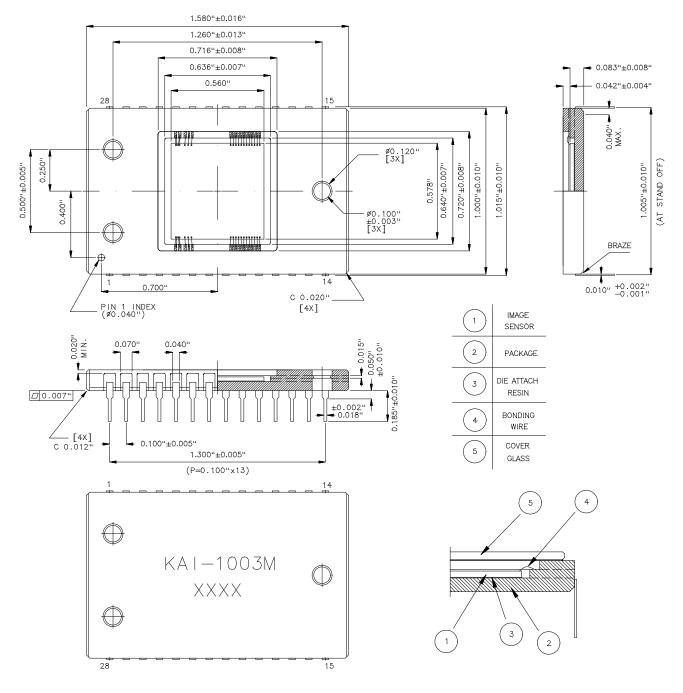

# **MECHANICAL DRAWINGS**

# **Completed Assembly**

Figure 18. Completed Assembly

#### **Cover Glass Specification**

#### Table 14. COVER GLASS SPECIFICATION

| Item      | Specification                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Substrate | Schott D263T eco or equivalent                                                                                                              |

| Thickness | $0.030'' \pm 0.002''$                                                                                                                       |

| Coating   | Double-sided anti-reflecting coating on a $0.660'' \times 0.660''$ square for a transmission minimum of 98% in the 400 to 700 nm wavelength |

| Scratch   | No scratch greater than 10 microns                                                                                                          |

#### Cover Glass Care and Cleanliness:

- 1. The cover glass is highly susceptible to particles and other contamination. Perform all assembly operations in a clean environment.

- 2. Touching the cover glass must be avoided

- 3. Improper cleaning of the cover glass may damage these devices. Improper cleaning of the cover glass may damage these devices. Refer to Application Note *Image senosr Handling and Best Practices*.

ON Semiconductor and the intervent and the inter

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative