# Precision, Ultra-Fast, Low Supply Current, Bidirectional Overvoltage Protector

### **General Description**

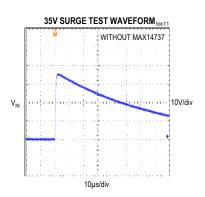

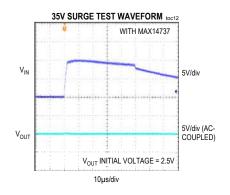

The MAX14736/MAX14737 overvoltage-protection (OVP) devices guard battery-powered modules in portable devices against overvoltage faults. The low  $15 \text{m}\Omega$  (typ) on-resistance, as well as the low 13 µA (typ) quiescent supply current of the devices, minimize power consumption, making them an ideal choice for low-power systems. Additionally, the devices feature a precision overvoltage-lockout (OVLO) threshold, ultra-fast response time, and surge suppression to  $\pm 35 \text{V}$ , which serve to provide excellent protection against even high slew-rate, high-voltage transients.

The integrated power transistor in the devices is a p-channel device, but the intrinsic body diode from OUT to IN is removed through appropriate design techniques. Consequently, when the switch is in the off state, reverse-current blocking that is inherent to the devices. The MAX14736/MAX14737 feature a push-pull POK output, which is driven low if either an overvoltage, undervoltage, or thermal fault is detected; or if the device is placed into shutdown mode.

The MAX14736 has an active-low enable pin  $(\overline{EN})$ , while the enable pin (EN) on the MAX14737 is active high.

When the enable pin is driven to the active state, the device is enabled. When driven to the inactive state, the device is placed in a low-power shutdown mode and the switch is kept in the off state.

The MAX14736/MAX14737 are offered in a small, 9-bump (1.34mm x 1.36mm) wafer-level package (WLP) and operate over the -40°C to +85°C extended temperature range.

#### **Benefits and Features**

- Protects Battery-Connected Modules with Minimal Power Consumption

- Wide Operating Input Voltage: +2.1V to +5.5V

- 4.5A Continuous Current Capability

- Integrated 15mΩ (typ) pFET

- Ultra-Low Supply Current: 13µA (typ)

- Allows Precise Design in OVLO Implementation

- · Preset Accurate Internal OVP Thresholds

- MAX14736: 4.7V ±2.0%

- MAX14737: 5.2V ±2.0%

- Increases System Reliability Through Premium Security

- Surge Immunity to ±35V

- · Soft-Start to Minimize Inrush Current

- · Output Hot Plug-In Protection

- Thermal Shutdown

- Ultra-Fast OVP Response Time: 200ns (typ)

- Minimizes Board Space by Compact WLP

- 9-Bump 1.34mm x 1.36mm WLP

#### **Applications**

- Smartphones

- Tablet PCs

- e-Readers

Ordering Information appears at end of data sheet.

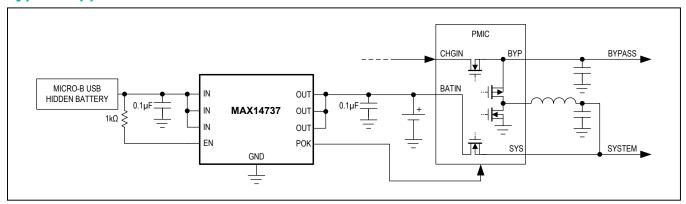

# **Typical Application Circuit**

# Precision, Ultra-Fast, Low Supply Current, Bidirectional Overvoltage Protector

## **Absolute Maximum Ratings**

| (All voltages referenced to GND.) | )                           |

|-----------------------------------|-----------------------------|

| IN (Note 1), OUT, EN, EN          | 0.3V to +6V                 |

| POK                               | 0.3V to max (IN,OUT) + 0.3V |

| Maximum Current into IN (DC) (N   | Note 2)4.5A                 |

| Peak Current into IN (10ms)       | 8A                          |

| 952mW          |

|----------------|

| 40°C to +85°C  |

| +150°C         |

| 65°C to +150°C |

| +260°C         |

|                |

## **Package Thermal Characteristics (Note 3)**

WI P

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) .....83.98°C/W

- Note 1: Survives burst pulse up to  $\pm 40V$  with  $2\Omega$  minimum source resistance.

- Note 2: Limited by thermal design.

- Note 3: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{IN} = +2.1V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 4)

| PARAMETER                          | SYMBOL      | CONDI                                | TIONS                                   | MIN   | TYP   | MAX   | UNITS |

|------------------------------------|-------------|--------------------------------------|-----------------------------------------|-------|-------|-------|-------|

| IN, OUT                            |             |                                      |                                         |       |       |       |       |

| Input Voltage Range                | VIN         |                                      |                                         | 2.1   |       | 5.5   | V     |

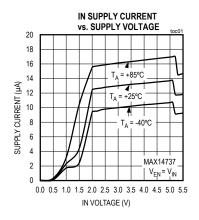

| Supply Current                     | ΙΝ          | VIN = 4.3V, no load                  |                                         |       | 13    | 30    | μA    |

| IN Shutdown Current                | IN_Q        | Device disabled,<br>VIN = 4.3V, VOUT | Device disabled, VIN = 4.3V, VOUT = 0V  |       | 2     | 6     | μA    |

| OUT Shutdown Current               |             | Device disabled,<br>VOUT = 5V, VIN = | Device disabled,<br>VOUT = 5V, VIN = 0V |       | 2     | 6     | μΑ    |

| OVP                                |             | •                                    |                                         |       |       |       |       |

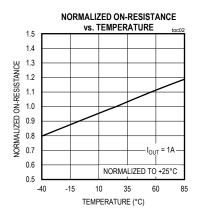

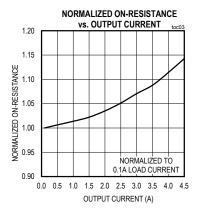

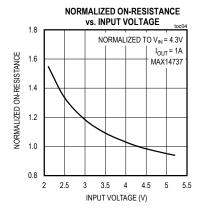

| On-Resistance (IN to OUT)          | RON         | VIN = 4.3V, IOUT =                   | VIN = 4.3V, IOUT = 100mA,               |       | 15    | 22    | mΩ    |

| Over alterna Tria I avel Threehold | \/ <b>-</b> |                                      | MAX14736                                | 4.600 | 4.700 | 4.800 | V     |

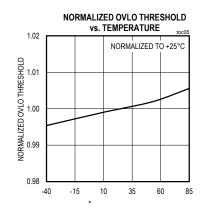

| Overvoltage Trip-Level Threshold   | VOVLO       | VIN rising                           | MAX14737                                | 5.095 | 5.200 | 5.305 | V     |

| Overvoltage Trip-Level Hysteresis  | VOVLO       |                                      |                                         |       | 100   |       | mV    |

| Undervoltage Trip-Level Threshold  | VUVLO       |                                      |                                         |       | 2.015 |       | V     |

| Undervoltage Trip-Level Hysteresis | VUVLO       |                                      |                                         |       | 80    |       | mV    |

| OUT Load Capacitance               | COUT        |                                      |                                         |       | 100   |       | μF    |

| DIGITAL OUTPUT (POK)               |             |                                      |                                         |       |       |       |       |

| Output Voltage Low                 | VOL         | ISINK = 100µA                        |                                         |       |       | 0.4   | V     |

| Output Voltage High                | ۷ОН         | ISOURCE = 100µA                      |                                         | 1.4   |       |       | V     |

www.maximintegrated.com Maxim Integrated | 2

# **Electrical Characteristics (continued)**

$(V_{IN}$  = +2.1V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{IN}$  = 4.3V,  $T_A$  = +25°C, unless otherwise noted.) (Note 4)

| PARAMETER                        | SYMBOL            | CONDITIONS                                                                            | MIN  | TYP | MAX  | UNITS |

|----------------------------------|-------------------|---------------------------------------------------------------------------------------|------|-----|------|-------|

| ENABLE INPUT (EN, EN) (FIGURE 1) |                   |                                                                                       |      |     |      |       |

| EN, EN Input High Current        | <sup>I</sup> EN_H | $V$ IN = 5.5V, $V$ EN = 3.0V, $V$ EN = 3.0V (internal 650k $\Omega$ connected to GND) |      | 4.6 |      | μΑ    |

| EN, EN Input Low Current         | <sup>I</sup> EN L | VEN = 0V, VEN = 0V                                                                    | -0.1 |     | +0.1 | μA    |

| EN, EN Input Voltage High        | VIH               |                                                                                       | 1.6  |     |      | V     |

| EN, EN Input Voltage Low         | ٧IL               |                                                                                       |      |     | 0.4  | ٧     |

| TIMING CHARACTERISTICS (NOT      | E 5)              |                                                                                       |      |     |      |       |

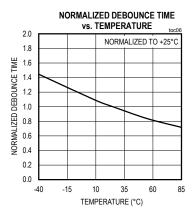

| Debounce Time                    | <sup>t</sup> DEB  | From $VEN = 3.0V$ , $VEN = 0V$ to when POK goes high                                  |      | 15  |      | ms    |

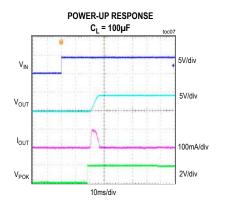

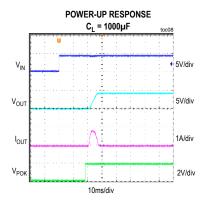

| Soft-Start Time                  | tSS               |                                                                                       |      | 30  |      | ms    |

| Switch Turn-On Time              | tON               | VIN = 5V, RL = 100Ω,<br>CL = 100μF, VOUT = 10% to 90% of<br>VIN                       |      | 4   |      | ms    |

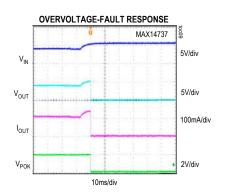

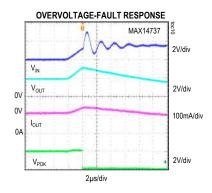

| Switch Turn-Off Response Time    | tOFF_RES          | VIN = VOVLO(MIN); VIN rising at 2V/μs until VOUT stops rising, RL =                   |      | 200 |      | ns    |

| THERMAL PROTECTION               |                   |                                                                                       |      |     |      |       |

| Thermal Shutdown                 | TSHDN             |                                                                                       |      | 150 |      | °C    |

| Thermal Hysteresis               | THYS              |                                                                                       |      | 20  |      | °C    |

| ESD PROTECTION                   |                   |                                                                                       |      |     |      |       |

| Human Rody Model                 |                   | All pins                                                                              |      | ±2  |      | kV    |

| Human Body Model                 |                   | IN pin, with 0.1µF bypass capacitor                                                   |      | ±15 |      | kV    |

Note 4: All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over temperature are guaranteed by design. Note 5: All timing characteristics are measured using 20% to 80% levels, unless otherwise noted.

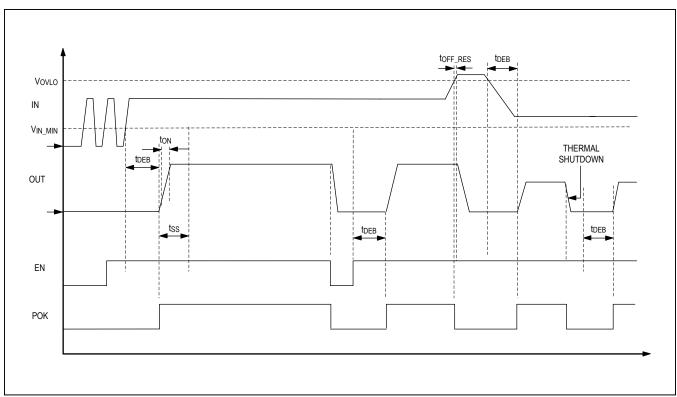

Figure 1. Timing Diagram

# **Typical Operating Characteristics**

$(V_{IN} = 4.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

# **Typical Operating Characteristics (continued)**

$(V_{IN} = 4.3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

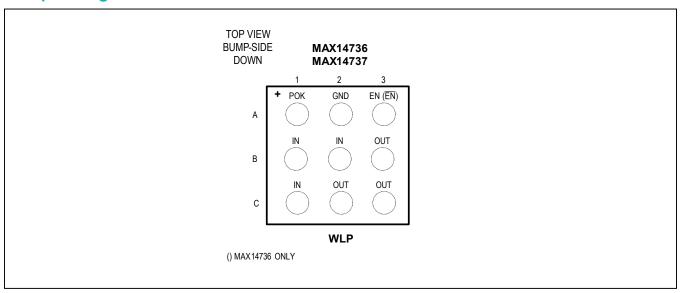

# **Bump Configuration**

# **Bump Description**

| BUMP NAI       |                          | NAME | FUNCTION                                                                                                                                                                                                                   |  |  |

|----------------|--------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                |                          | NAME |                                                                                                                                                                                                                            |  |  |

| A1             | A1                       | POK  | Push-Pull Power-Okay Output. When the POK output is low, an OVLO, UVLO, or thermal fault has been detected, or the device has been placed into shutdown mode.                                                              |  |  |

| A2             | A2                       | GND  | Ground                                                                                                                                                                                                                     |  |  |

| A3 — <u>EN</u> |                          | ĒN   | Active-Low Enable Input. Drive $\overline{EN}$ high to place the device in shutdown mode (power switch is open). Drive $\overline{EN}$ low to place the device in normal operating mode.                                   |  |  |

| _              | А3                       | EN   | Active-High Enable Input. Drive EN low to place the device in shutdown mode (power switch is open). Drive EN high to place the device in normal operating mode.                                                            |  |  |

| B1, B2, C1     | B1, B2, C1 B1, B2, C1 IN |      | Overvoltage-Protection Input. Bypass IN with a 0.1µF ceramic capacitor for ±15kV Human Body Model (HBM) ESD protection. No capacitor is required for ±2kV HBM ESD protection. Externally connect all the IN pins together. |  |  |

| B3, C2, C3     | B3, C2, C3               | OUT  | Overvoltage-Protection Output. Bypass OUT with at least a 1µF ceramic capacitor. Externally connect all the OUT pins together.                                                                                             |  |  |

www.maximintegrated.com Maxim Integrated | 7

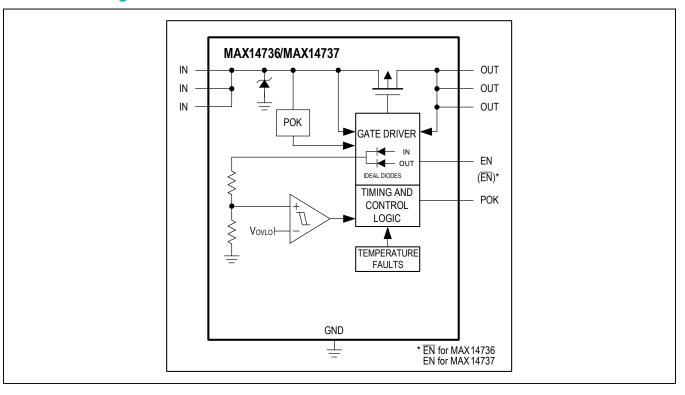

## **Functional Diagram**

## **Detailed Description**

The MAX14736/MAX14737 overvoltage-protection (OVP) devices guard battery-powered modules in portable devices against overvoltage faults. The low,  $15 m\Omega$  (typ) on-resistance, as well as the low  $13 \mu A$  (typ) quiescent supply current of the devices minimize power consumption, making them an excellent choice for low-power systems. Additionally, the devices feature a precision overvoltage-lockout (OVLO) threshold, ultra-fast response time, and surge suppression to  $\pm 35 \text{V}$ , which serve to provide excellent protection against even high-slew rate, high-voltage transients.

The integrated power transistor in the devices is a p-channel device, but the intrinsic body diode from OUT to IN is removed through appropriate design techniques. Consequently, when the switch is in the off state, reverse-current blocking is inherent to the devices. The devices feature a push-pull POK output that is driven low if either an overvoltage, undervoltage, or thermal fault is detected; or if the device is placed into shutdown mode.

The MAX14736 has an active-low enable pin  $(\overline{EN})$ , while the enable pin (EN) on MAX14737 is active-high. When driven to the active state, the device is enabled. When driven to the inactive state, the device is placed in a low-power shutdown mode and the switch is kept in the off state.

#### **Device Operation**

The devices contain timing logic that controls the turn-on of the internal FET. When the device is enabled and  $V_{UVLO} < V_{INT}^* < V_{OVLO}$ , the internal gate-driver circuitry is powered. After 15ms of debounce time, which prevents false turn-on of the FET during startup, the soft-start function limits inrush current through the FET for 30ms (typ). At any time, if  $V_{INT}^*$  rises above  $V_{OLVO}$ , or falls below  $V_{UVLO}$ , the FET is turned off and OUT is consequently disconnected from IN.

$*V_{INT} = max(V_{IN}, V_{OUT})$

#### **Overvoltage Lockout**

The MAX14736 offers a 4.7V (typ) precision overvoltage threshold, while the overvoltage threshold for MAX14737 is 5.2V (typ). When IN or OUT rise above the overvoltage-lockout threshold ( $V_{\rm OVLO}$ ), OUT is disconnected from IN. When  $V_{\rm INT}^*$  drops by the OVLO falling hysteresis ( $V_{\rm OVLO}$  Hys), OUT and IN are reconnected.

#### **Shutdown Mode**

The devices feature a low-power shutdown mode, which disconnects OUT from IN and reduces current consumption to  $2\mu A$  (typ). To enter shutdown mode, drive  $\overline{EN}$  high on the MAX14736 or EN low on the MAX14737. The POK output is driven low when the device is in shutdown mode.

For MAX14737, EN has an internal pulldown resistor. The MAX14737 is placed in shutdown mode by leaving EN unconnected.

#### Thermal-Shutdown Protection

The devices contain internal thermal-shutdown circuitry necessary to protect the devices. The internal FET turns off, and POK is driven low, when the junction temperature exceeds +150°C (typ). The devices exit thermal shutdown after the junction temperature cools by 20°C (typ).

### **POK Output**

The push-pull POK output on the devices assert high when they are enabled and when OVLO, UVLO, or thermal fault is not present. <u>Table 1</u> shows the truth table for the POK output.

**Table 1. POK Truth Table**

| VINT*                                  | EN<br>(MAX14736) | EN<br>(MAX14737) | THERMAL SHUTDOWN | РОК               |

|----------------------------------------|------------------|------------------|------------------|-------------------|

|                                        | HIGH             | LOW              | NO FAULT         | LOW               |

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | HIGH             | LOW              | FAULT            | LOW               |

| VUVLO < VINT < VOVLO                   | LOW              | HIGH -           | NO FAULT         | HIGH (AFTER tDEB) |

|                                        |                  |                  | FAULT            | LOW               |

| VINT < VUVLO OR VINT ><br>VOVLO        | HIGH             | LOW              | NO FAULT         | LOW               |

|                                        | пібп             | LOW              | FAULT            | LOW               |

|                                        | LOW              | 111011           | NO FAULT         | LOW               |

|                                        | LOW              | HIGH             | FAULT            | LOW               |

$<sup>*</sup>V_{INT} = max(V_{IN}, V_{OUT})$

## **Applications Information**

#### **IN Bypass Capacitor**

The MAX14736/MAX14737 do not require an input capacitor, though it is generally recommended to bypass IN to GND with a  $0.1\mu F$  ceramic capacitor as close as possible to the device. If the power source has significant inductance due to long lead length or other non-ideal layout conditions, the device clamps the overshoot due to the LC tank circuit.

### **Output Capacitor**

The soft-start functionality included in the MAX14736/MAX14737 limits inrush current for 30ms (typ), allowing the devices to charge capacitances over 1000µF.

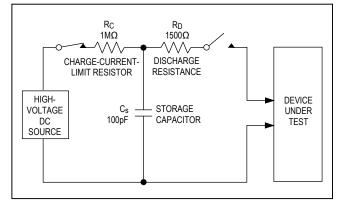

Figure 2. Human Body ESD Test Model

#### **ESD Test Conditions**

ESD performance depends on a number of conditions. The MAX14736/MAX14737 are specified for  $\pm 2kV$  (HBM) typical ESD resistance on all pins and  $\pm 15kV$  (HBM) typical ESD resistance on IN with a  $0.1\mu F$  bypass capacitor.

#### **HBM ESD Protection**

Figure 2 shows the Human Body Model, while Figure 3 shows the current waveform it generates when discharged into low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a 1.5kΩ resistor.

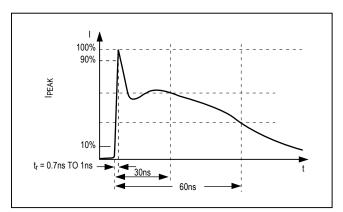

Figure 3. Human Body Current Waveform

# Precision, Ultra-Fast, Low Supply Current, Bidirectional Overvoltage Protector

# **Ordering Information**

| PART          | ENABLE POLARITY | OVLO (V) | TOP MARK | PIN-PACKAGE |

|---------------|-----------------|----------|----------|-------------|

| MAX14736EWL+T | ĒΝ              | 4.7      | AKQ      | 9 WLP       |

| MAX14737EWL+T | EN              | 5.2      | AKR      | 9 WLP       |

Note: All devices are specified over the -40°C to +85°C extended temperature range.

## **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO.               |

|--------------|--------------|----------------|--------------------------------|

| 9 WLP        | W91K1+1      | <u>21-0760</u> | Refer to Application Note 1891 |

www.maximintegrated.com Maxim Integrated | 11

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

# Precision, Ultra-Fast, Low Supply Current, **Bidirectional Overvoltage Protector**

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------|------------------|

| 0                  | 5/15             | Initial release | _                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.