# RENESAS

# DATASHEET

## ISL68147

Digital Dual Output, 7-Phase Configurable, PWM Controller with PMBus for Cavium

The ISL68147 is a digital dual output, flexible multiphase  $(X+Y \le 7)$  PWM controller developed to support the latest Cavium CN99xx server class processors. The ISL68147 supports the PMbus1.3 specification and meets the latest Intel server-class transient performance specifications. Either output can be configured to support any desired phase assignments up to a maximum of seven phases across the two outputs (X+Y). For example, 6+1, 5+2, 4+2, 3+3, 3+2, or even a single output operation as a 7+0 configuration. With full digital control, this new generation of controllers ushers in design flexibility by supporting any microprocessor, FPGA, or Digital ASIC rail requirements that includes adjustable load setting. The ISL68147 uses the Intersil proprietary linear synthetic digital current modulation scheme to achieve the industry's best combination of transient response and ease of tuning while addressing the challenges of modern multiphase designs.

Device configuration and telemetry monitoring is accomplished using the Intersil PowerNavigator™ GUI. The ISL68147 device supports on-chip, nonvolatile memory to store various configuration settings that are user-selectable through pin strap, giving system designers increased power density to configure and deploy multiple configurations. The device supports an automatic phase add/drop feature to allow maximum efficiency across all load ranges. Thresholds for automatic phase add/drop are user-programmable using PowerNavigator.

The ISL68147 supports a comprehensive fault management system to enable the design of highly reliable systems. From a multitiered overcurrent protection scheme to the configurable power-good and output overvoltage/undervoltage fault thresholds and temperature monitoring, almost any need is accommodated.

With minimal external components, easy configuration, robust fault management, and highly accurate regulation capability, implementing a high-performance, multiphase regulator has never been easier.

## **Applications**

- Networking equipment

- Telecom/datacom equipment

- Server/storage equipment

- Point-of-load power supply (Memory, DSP, ASIC, FPGA)

## **Features**

- Advanced linear digital modulation scheme

- Zero latency synthetic current control for excellent HF current balance

- Dual-edge modulation for fastest transient response

- · Auto phase add/drop for excellent load vs efficiency profile

- PMBus 1.3 support

- Telemetry  $V_{IN},\,V_{OUT},\,I_{OUT},$  power IN/OUT, temperature, and various fault status registers

- Up to 2MHz bus interface

- Flexible phase configuration

- 7+0, 6+1, 5+2, 4+3 phase operation

- Operation using fewer than seven phases between two outputs is also supported

- Diode braking for overshoot reduction

- Differential remote voltage sensing supports ±0.5% closed loop system accuracy over load, line, and temperature

- Highly accurate current sensing for excellent load line regulation and accurate OCP

- Supports the ISL99227 60A smart power stages

- Supports DCR sense with integrated temperature compensation

- Supports Phase Doubler (ISL6617A) for up to 14-phase operation

- Comprehensive fault management enables high reliability systems

- Pulse-by-pulse phase current limiting

- Total output current protection

- Output and input OV/UV

- Open voltage sense detect

- Black box recording capability for faults

- · Intuitive configuration using PowerNavigator

- NVM to store up to 8 configurations

- Pb-free (RoHS compliant)

## **Related Literature**

- · For a full list of related documents, visit our website

- ISL68147 product page

FN8880 Rev.2.00 Jul 14, 2017

## **Table of Contents**

| Ordering Information                                                                          |

|-----------------------------------------------------------------------------------------------|

| Pin Configuration                                                                             |

| Functional Pin Descriptions                                                                   |

| Driver, DrMOS, and Smart Power Stage Recommendation                                           |

| Internal Block Diagram                                                                        |

| Typical Application: 6+1 Configuration with ISL99227 SPS                                      |

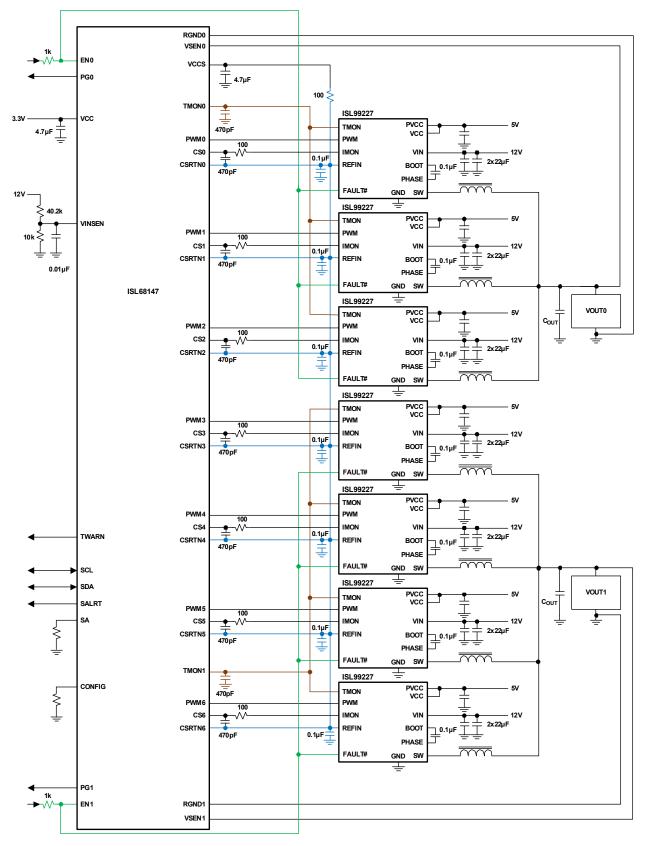

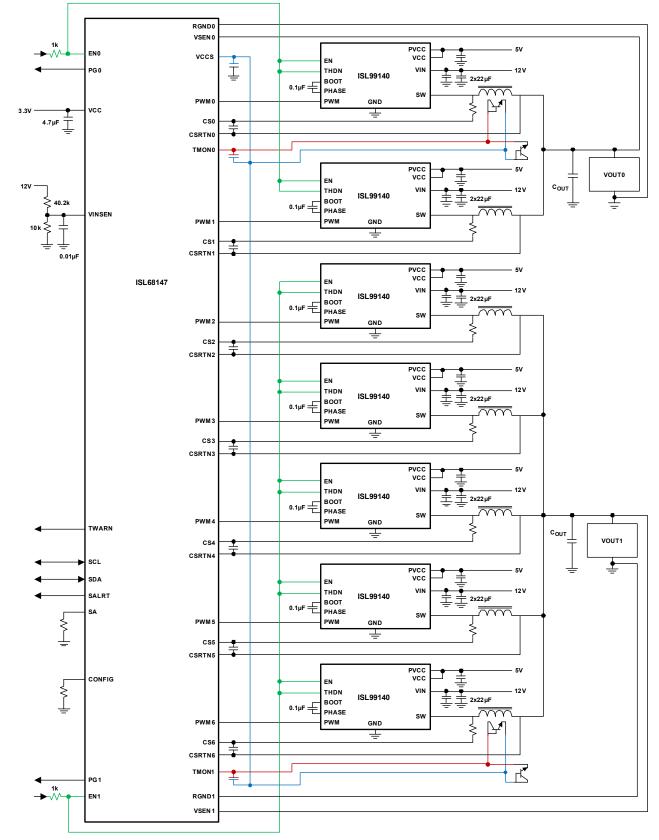

| Typical Application: 4+3 Configuration with ISL99227 SPS                                      |

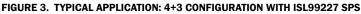

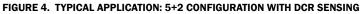

| Typical Application: 5+2 Configuration with DCR Sensing                                       |

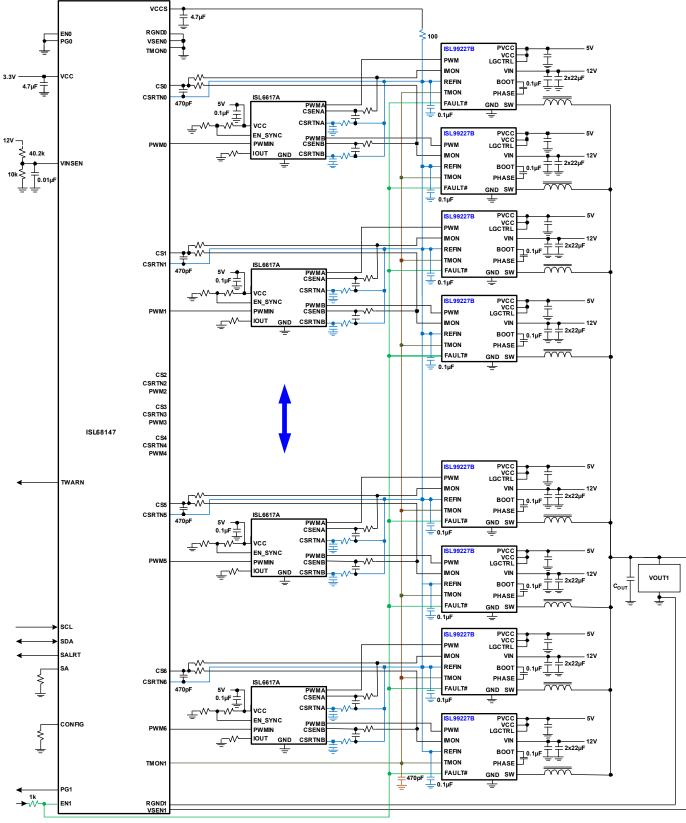

| Typical Application: Phase Doubler 14-Phase VR with ISL6617A+SPS                              |

| Absolute Maximum Ratings                                                                      |

| Thermal Information                                                                           |

| Recommended Operating Conditions                                                              |

| Electrical Specifications                                                                     |

| Typical Performance Curves                                                                    |

| Functional Description                                                                        |

| -                                                                                             |

| Overview         12           PWM Modulation Scheme         12                                |

| PMBus Address Selection                                                                       |

| Phase Configuration                                                                           |

| Automatic Phase Add and Drop                                                                  |

| Output Voltage Configuration.       13         Switching Frequency.       13                  |

| Current Sensing                                                                               |

| Temperature Sensing                                                                           |

| Temperature Compensation                                                                      |

| Lossless Input Current and Power Sensing                                                      |

| Voltage Regulation       16         Current Feedback       16                                 |

| Power-On Reset (POR)                                                                          |

| Soft-Start Delay and Ramp Times                                                               |

| Stored Configuration Selection                                                                |

| Fault Monitoring and Protection                                                               |

| Power-Good Signals                                                                            |

| Output Voltage Protection                                                                     |

| Output Current Protection                                                                     |

| Smart Power Stage OC Fault Detect       18         Thermal Monitoring and Protection       18 |

| Layout and Design Considerations                                                              |

| PMBus Operation                                                                               |

| -                                                                                             |

| PMBus Protocol                                                                                |

| PMBus Command Summary                                                                         |

| PMBus Use Guidelines       23         PMBus Data Formats       23                             |

| PMBus Command Detail                                                                          |

|                                                                                               |

| Revision History                                                                              |

| About Intersil                                                                                |

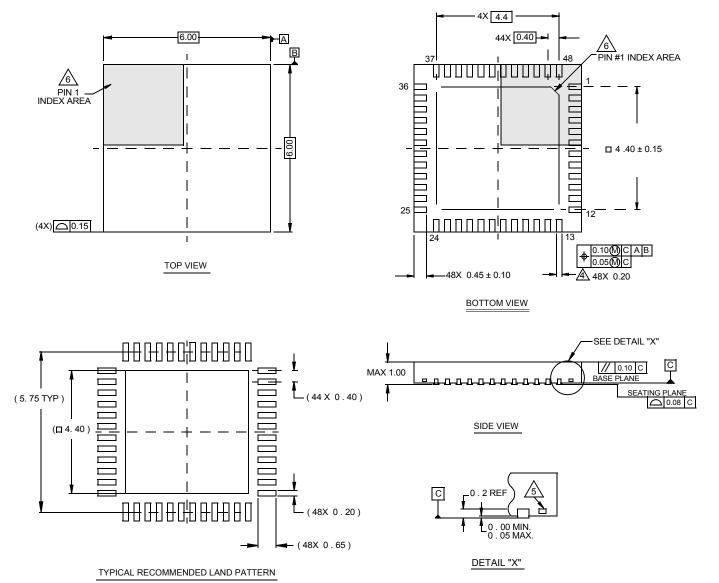

| Package Outline Drawing                                                                       |

## **Ordering Information**

| PART NUMBER              | PART         | TEMP. RANGE | PACKAGE          | PKG.     |

|--------------------------|--------------|-------------|------------------|----------|

| ( <u>Notes 1, 2, 3</u> ) | MARKING      | (°C)        | (RoHS COMPLIANT) | DWG. #   |

| ISL68147IRAZ             | ISL68147 IRZ | -40 to +85  | 48 Ld 6x6 QFN    | L48.6x6B |

NOTES:

1. Add "-T" suffix for 4k unit or "-T7A" suffix for 250 unit tape and reel options. Refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

TABLE 1. KEY DIFFERENCES BETWEEN FAMILY OF PARTS

3. For Moisture Sensitivity Level (MSL), see the product information page for ISL68147. For more information on MSL, see TB363.

| PART NUMBER  | PHASE CONFIGURATION<br>OUTPUT X/OUTPUT Y | SPECIFICATION SUPPORTED  | PACKAGE           |  |

|--------------|------------------------------------------|--------------------------|-------------------|--|

| ISL68147     | X+Y ≤ 7                                  | Cavium Thunder X2, PMBus | QFN 48 Ld, 6x6mm  |  |

| ISL68144     | X+Y ≤ 4                                  | PMBus                    | TQFN 40 Ld, 5x5mm |  |

| ISL68137     | X+Y ≤ 7                                  | PMBus/AVSBus             | QFN 48 Ld, 6x6mm  |  |

| ISL68134     | X+Y ≤ 4                                  | PMBus/AVSBus             | TQFN 40 Ld, 5x5mm |  |

| ISL68127     | X+Y ≤ 7                                  | PMBus                    | QFN 48 Ld, 6x6mm  |  |

| <br>ISL68124 | X+Y ≤ 4                                  | PMBus                    | TQFN 40 Ld, 5x5mm |  |

|              |                                          |                          |                   |  |

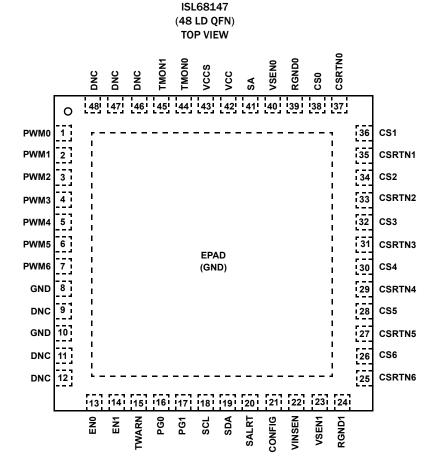

## **Pin Configuration**

## Functional Pin Descriptions Refer to Table 4 on page 19 for design layout considerations.

| PIN NUMBER                            | PIN NAME   | DESCRIPTION                                                                                                                                                                                                            |  |

|---------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7, 6, 5, 4, 3, 2, 1                   | PWM[6:0]   | Pulse width modulation outputs. Connect these pins to the PWM input pins of 3.3V logic-compatible Intersil smart power stages, driver IC(s), or power stages.                                                          |  |

| 8, 10                                 | GND        | Ground pins. Connect directly to system GND plane.                                                                                                                                                                     |  |

| 9, <b>11</b> , <b>12</b> , 46, 47, 48 | DNC        | Do not connect any signals to these pins.                                                                                                                                                                              |  |

| 13                                    | ENO        | Input pin used for enable control of Output 0. Active high. Connect to ground if not used.                                                                                                                             |  |

| 14                                    | EN1        | Input pin used for enable control of Output 1. Active high. Connect to ground if not used.                                                                                                                             |  |

| 15                                    | TWARN      | Thermal warning flag. This open-drain output will be pulled low in the event of a sensed over-temperature at TMON pins without disabling the regulators. Maximum pull-up voltage is VCC.                               |  |

| 16                                    | PG0        | Open-drain, power-good indicators for Output 0. Maximum pull-up voltage is VCC.                                                                                                                                        |  |

| 17                                    | PG1        | Open-drain, power-good indicators for Output 1. Maximum pull-up voltage is VCC.                                                                                                                                        |  |

| 18                                    | SCL        | Serial clock signal pin for SMBus interface. Maximum pull-up voltage is VCC.                                                                                                                                           |  |

| 19                                    | SDA        | Serial data signal pin for SMBus interface. Maximum pull-up voltage is VCC.                                                                                                                                            |  |

| 20                                    | SALRT      | Serial alert signal pin for SMBus interface. Maximum pull-up voltage is VCC.                                                                                                                                           |  |

| 21                                    | CONFIG     | Configuration ID selection pin. See <u>Table 3 on page 16</u> for more details.                                                                                                                                        |  |

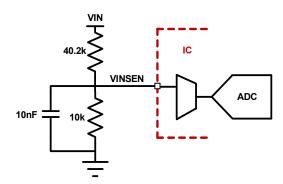

| 22                                    | VINSEN     | Input voltage sense pin. Connect to VIN through a resistor divider (typically 402k/10k) with a 10nF decoupling capacitor.                                                                                              |  |

| 23                                    | VSEN1      | Positive differential voltage sense input for Output 1. Connect to positive remote sensing point. Connect ground if not used.                                                                                          |  |

| 24                                    | RGND1      | Negative differential voltage sense input for Output 1. Connect to negative remote sensing point. Conneground if not used.                                                                                             |  |

| 25, 27, 29, 31,<br>33, 35, 37         | CSRTN[6:0] | The CS and CSRTN pins are current sense inputs to individual phase differential amplifiers. Unused phases should have their respective current sense inputs grounded. The ISL68147 supports smart power stage, DCR,    |  |

| 26, 28, 30, 32,<br>34, 36, 38         | CS[6:0]    | and resistor sensing. Connection details depend on the current sense method chosen.                                                                                                                                    |  |

| 39                                    | RGNDO      | Negative differential voltage sense input for Output 0. Connect to negative remote sensing point. Connect to ground if not used.                                                                                       |  |

| 40                                    | VSENO      | Positive differential voltage sense input for Output 0. Connect to positive remote sensing point. Connect to ground if not used.                                                                                       |  |

| 41                                    | SA         | PMBus address selection pin. See Table 2 on page 12 for more details.                                                                                                                                                  |  |

| 42                                    | VCC        | Chip primary bias input. Connect this pin directly to a +3.3V supply with a high quality MLCC bypass capacitor.                                                                                                        |  |

| 43                                    | VCCS       | Internally generated 1.2V LDO logic supply from VCC. Decouple with 4.7µF or greater MLCC (X5R or better).                                                                                                              |  |

| 44                                    | TMONO      | Input pin for external temperature measurement at Output 0. Supports diode based temperature sensing as well as smart power stage sensing. Refer to <u>"Temperature Compensation" on page 15</u> for more information. |  |

| 45                                    | TMON1      | Input pin for external temperature measurement at Output 1. Supports diode based temperature sensing as well as smart power stage sensing. Refer to <u>"Temperature Compensation" on page 15</u> for more information. |  |

| EPAD                                  | GND        | Package pad serves as GND return for all chip functions. Connect directly to system GND plane with multiple thermal vias.                                                                                              |  |

## **Driver, DrMOS, and Smart Power Stage Recommendations**

| INTERSIL PART<br>NUMBER | QUIESCENT<br>CURRENT<br>(mA) | GATE<br>DRIVE VOLTAGE<br>(V) | NUMBER OF<br>DRIVERS | COMMENTS                                                                                                                          |

|-------------------------|------------------------------|------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| ISL99227                | 4.85                         | 5                            | Single               | 60A, 5x5 smart power stage                                                                                                        |

| ISL99140                | 0.19                         | 5                            | Single               | 40A, 6x6 DrMOS                                                                                                                    |

| ISL6596                 | 0.19                         | 5                            | Single               | Connect ISL6596 VCTRL to 3.3V                                                                                                     |

| ISL6617A                | 5                            | N/A                          | N/A                  | Phase Doubler with 5V PWM output to be compatible with 60A DrMOS or with 60A smart power stage. Supports up to a 14-phase design. |

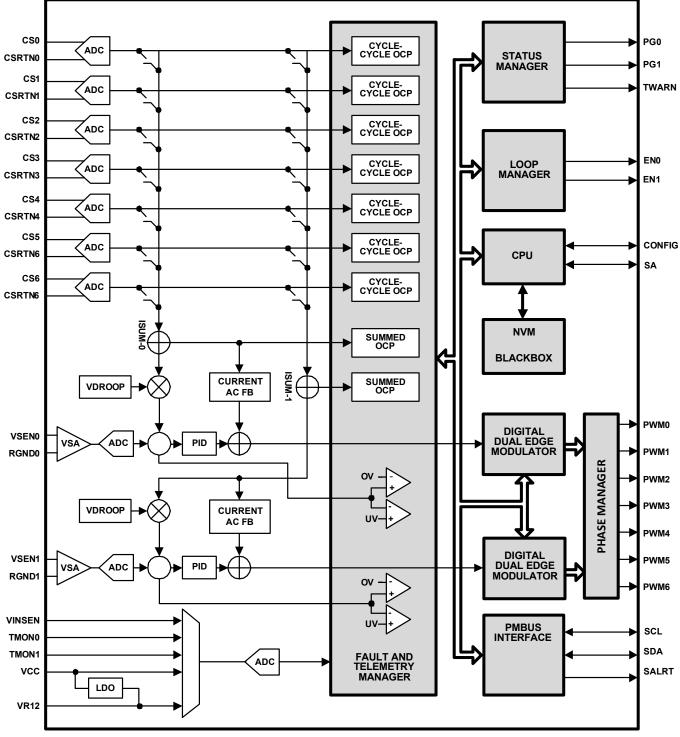

## **Internal Block Diagram**

FIGURE 1. INTERNAL BLOCK DIAGRAM

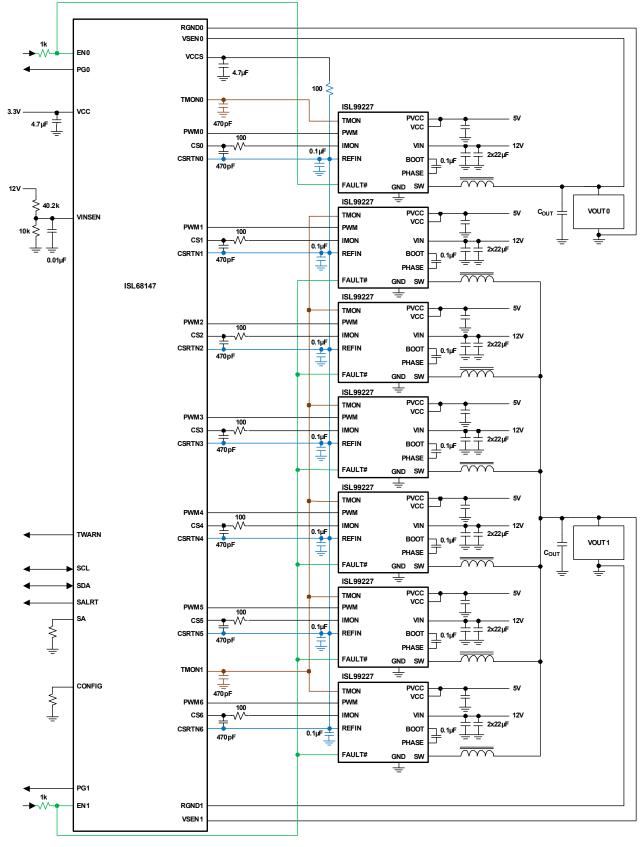

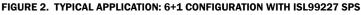

## Typical Application: 6+1 Configuration with ISL99227 SPS

## **Typical Application: 5+2 Configuration with DCR Sensing**

## Typical Application: Phase Doubler 14-Phase VR with ISL6617A+SPS

#### **Absolute Maximum Ratings**

| VCC+4.3V                                               |

|--------------------------------------------------------|

| VCCS                                                   |

| All Other Pins                                         |

| ESD Rating:                                            |

| Human Body Model (Tested per JS-001-2014) 2kV          |

| Charged Device Model (Tested per JS-001-2014) 1kV      |

| Latch-Up (Tested per JESD-78D; Class 2, Level A) 100mA |

#### **Thermal Information**

| Thermal Resistance ( <u>Notes 4, 5</u> ) | θ <b>JA</b> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|--------------------|------------------------|

| 48 Ld 6x6 QFN Package                    | 27                 | 1                      |

| Maximum Junction Temperature             |                    | +150°C                 |

| Maximum Storage Temperature Range        | 65                 | °C to +150 °C          |

| Pb-Free Reflow Profile                   |                    | see <u>TB493</u>       |

#### **Recommended Operating Conditions**

| Supply Voltage, V <sub>CC</sub> | +3.3V ±5%   |

|---------------------------------|-------------|

| Ambient Temperature40           | °C to +85°C |

| Output Voltage                  | 0V to 3.05V |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

4.  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See TB379.

5. For  $\theta_{\text{JC}}$  , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Recommended operating conditions, V<sub>CC</sub> = 3.3V, unless otherwise specified. Boldface limits apply across the operating temperature range -40°C to +85°C.

| PARAMETER                                                     | TEST CONDITIONS                                                | MIN<br>( <u>Note 7</u> ) | TYP                   | MAX<br>( <u>Note 7</u> ) | UNIT |

|---------------------------------------------------------------|----------------------------------------------------------------|--------------------------|-----------------------|--------------------------|------|

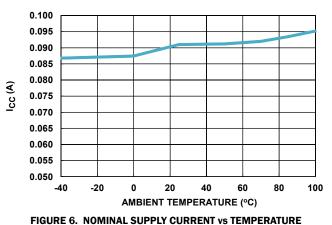

| V <sub>CC</sub> SUPPLY CURRENT                                |                                                                |                          |                       |                          |      |

| Nominal Supply Current                                        | $V_{CC}$ = 3.3VDC; EN1/2 = $V_{IH}$ , f <sub>SW</sub> = 400kHz |                          | 90.5                  |                          | mA   |

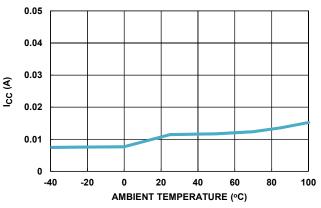

| Shutdown Supply Current                                       | $V_{CC}$ = 3.3VDC; EN1/2 = 0V, no switching                    |                          | 11.4                  |                          | mA   |

| VCCS LDO SUPPLY                                               |                                                                |                          |                       | 11                       |      |

| Output Voltage                                                |                                                                | 1.20                     | 1.25                  | 1.30                     | ٧    |

| Maximum Current Capability                                    | Excluding internal load                                        | 50                       |                       |                          | mA   |

| POWER-ON RESET AND INPUT VOLTAGE LOCKOUT                      | 1                                                              | Ļ                        | 4                     | 1 1                      |      |

| V <sub>CC</sub> Rising POR Threshold                          |                                                                |                          | 2.7                   | 2.9                      | v    |

| V <sub>CC</sub> Falling POR Threshold                         |                                                                | 1.0                      |                       |                          | v    |

| Enable (ENO and EN1) Input High Level                         |                                                                | 2.55                     |                       |                          | v    |

| Enable (ENO and EN1) Input Low Level                          |                                                                |                          |                       | 0.8                      | V    |

| Enable (ENO and EN1) Input LOW to HIGH Ramp Delay (TON_DELAY) |                                                                | 200                      |                       |                          | μs   |

| POR to Initialization Complete Time                           |                                                                |                          | 30                    | 40                       | ms   |

| OUTPUT VOLTAGE CHARACTERISTICS (Note 6)                       | I                                                              | I                        | 1                     | 11                       |      |

| Output Voltage Adjustment Range                               |                                                                | 0.25                     |                       | 3.05                     | v    |

| Output Voltage Set-Point Accuracy                             | Set-point 0.8V to 3.05V                                        | -0.5                     |                       | 0.5                      | %    |

|                                                               | Set-point 0.25V to <0.8V                                       | -5                       |                       | 5                        | mV   |

| VOLTAGE SENSE AMPLIFIER                                       | 1                                                              | Ļ                        | 4                     | 1 1                      |      |

| Open Sense Current                                            | Only during open pin check of initialization                   |                          | 22                    |                          | μΑ   |

| Input Impedance (VSEN - RGND)                                 |                                                                |                          | 200                   |                          | kΩ   |

| Maximum Common-Mode Input                                     |                                                                |                          | V <sub>CC</sub> - 0.2 |                          | v    |

| Maximum Differential Input (VSEN-RGND)                        |                                                                |                          |                       | 3.05                     | v    |

| CURRENT SENSE AND OVERCURRENT PROTECTION                      |                                                                | ·                        |                       |                          |      |

| Maximum Common-Mode Input (SPS mode)                          | CSRTNx - GND                                                   |                          | 1.6                   |                          | V    |

| Maximum Common-Mode Input (DCR mode)                          | CSRTNx - GND                                                   |                          | 3.3                   |                          | v    |

| Current Sense Accuracy                                        | ISEN to ADC accuracy                                           | -2                       |                       | 2                        | %    |

| Average Overcurrent Threshold Resolution                      |                                                                |                          | 0.1                   |                          | Α    |

| Cycle-by-Cycle Current Limiting Threshold Accuracy            |                                                                |                          | 0.1                   |                          | Α    |

FN8880 Rev.2.00 Jul 14, 2017

Electrical Specifications Recommended operating conditions, V<sub>CC</sub> = 3.3V, unless otherwise specified. Boldface limits apply across the operating temperature range -40°C to +85°C. (Continued)

| PARAMETER                                      | TEST CONDITIONS                                   | MIN<br>( <u>Note 7</u> ) | ТҮР                   | MAX<br>( <u>Note 7</u> ) | UNIT  |

|------------------------------------------------|---------------------------------------------------|--------------------------|-----------------------|--------------------------|-------|

| DIGITAL DROOP                                  |                                                   |                          |                       |                          |       |

| Droop Resolution                               |                                                   |                          | 0.01                  |                          | mV/A  |

| OSCILLATORS                                    |                                                   | l                        |                       |                          |       |

| Accuracy of Switching Frequency Setting        | When set to 500kHz                                | 480                      | 500                   | 520                      | kHz   |

|                                                |                                                   | -4                       |                       | +4                       | %     |

| Switching Frequency Range                      |                                                   | 200                      |                       | 1000                     | kHz   |

| SOFT-START RATE AND VOLTAGE TRANSITION RATE    |                                                   | l                        |                       |                          |       |

| Minimum Soft-Start Ramp Rate                   | Programmable minimum rate                         |                          | 20                    |                          | μs    |

| Maximum Soft-Start Ramp Rate                   | Programmable maximum rate                         |                          | 10                    |                          | ms    |

| Soft-Start Ramp Rate Accuracy                  |                                                   | -4                       |                       | 4                        | %     |

| Minimum Transition Rate                        | Programmable minimum rate                         |                          | 0.1                   |                          | mV/µs |

| Maximum Transition Rate                        | Programmable maximum rate                         |                          | 100                   |                          | mV/µs |

| Transition Rate Accuracy                       |                                                   | -4                       |                       | 4                        | %     |

| PWM OUTPUT                                     |                                                   |                          |                       |                          |       |

| PWMx Output High Level                         | I <sub>OUT</sub> = 4mA                            | V <sub>CC</sub> - 0.4    |                       |                          | v     |

| PWMx Output Low Level                          | I <sub>OUT</sub> = 4mA                            |                          |                       | 0.4                      | v     |

| PWMx Output Tri-State I <sub>OL</sub>          | V <sub>OH</sub> = V <sub>CC</sub>                 |                          |                       | 1                        | μA    |

| PWMx Output Tri-State I <sub>OH</sub>          | V <sub>OL</sub> = 0V                              | -1                       |                       |                          | μA    |

| THERMAL MONITORING AND PROTECTION              |                                                   | - I                      |                       |                          |       |

| Temperature Sensor Range                       |                                                   | -50                      |                       | 150                      | °C    |

| Temperature Sensor Accuracy                    | TMON to ADC accuracy                              | -4.5                     |                       | 4.5                      | %     |

| TWARN Output Low Impedance                     |                                                   | 4                        | 9                     | 13                       | Ω     |

| TWARN Hysteresis                               |                                                   |                          | 3                     |                          | °C    |

| POWER-GOOD AND PROTECTION MONITORS             |                                                   | l                        |                       |                          |       |

| PG Output Low Voltage                          | I <sub>OUT</sub> = 8mA load                       |                          |                       | 0.4                      | v     |

| PG Leakage Current                             | With pull-up resistor externally connected to VCC |                          | 0.5                   | 1                        | μA    |

| Overvoltage Protection Threshold Resolution    |                                                   |                          | 1                     |                          | mV    |

| Undervoltage Protection Threshold Resolution   |                                                   |                          | 1                     |                          | mV    |

| Overvoltage Protection Threshold When Disabled |                                                   |                          | V <sub>CC</sub> - 0.2 |                          | v     |

| INPUT VOLTAGE SENSE                            |                                                   | I                        |                       |                          | 1     |

| Input Voltage Accuracy                         | VINSEN to ADC accuracy                            | -2.5                     |                       | 2.5                      | %     |

| Input Voltage Protection Threshold Resolution  |                                                   |                          | 1                     |                          | mV    |

| SMBus/PMBus                                    |                                                   | l                        |                       |                          |       |

| SALERT, SDA Output Low Level                   | I <sub>OUT</sub> = 4mA                            |                          |                       | 0.4                      | v     |

| SCL, SDA Input High Level                      |                                                   | 1.55                     | 1.25                  |                          | v     |

| SCL, SDA Input Low Level                       |                                                   |                          |                       | 0.8                      | v     |

| SCL, SDA Input Hysteresis                      |                                                   |                          | 2                     |                          | mV    |

| SCL Frequency Range                            |                                                   | 0.05                     |                       | 2                        | MHz   |

NOTES:

6. These parts are designed and adjusted for accuracy with all errors in the voltage loop included.

7. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

## **Typical Performance Curves**

## **Functional Description**

#### **Overview**

The ISL68147 is a digital dual output, 7-phase PWM controller that can be programmed for a single output 7+0, dual output 6+1, 5+2, or 4+3 phase operation. Operation using less than seven phases between two outputs is also supported. Existing digital multiphase solutions use analog comparator-based schemes (nonlinear) to bolster the inadequate transient response common to many digital multiphase solutions. The ISL68147 uses a linear voltage regulation scheme to address transient loads. As a result, it is much easier for users to configure and validate their designs when compared with nonlinear schemes. By combining a proprietary low noise and zero latency digital current sense scheme with cutting edge digital design techniques, Intersil is able to meet transient demands without resorting to nonlinear schemes. In addition, the ISL68147 can store up to eight user configurations in NVM and allows the user to select the desired configuration through pin-strap (CONFIG). The result is a system that is easy to configure and deploy.

A number of performance enhancing features are supported in the ISL68147. These include diode braking, automatic phase dropping, DCR/resistor/smart power stage current sense support, load line regulation, and multiple temperature sensing options.

To facilitate configuration development, PowerNavigator provides a step-by-step arrangement for setup and parametric adjustment. After a configuration has been set, the user can employ PowerNavigator to monitor telemetry or use the direct PMBus interface based on the supported command set.

#### **PWM Modulation Scheme**

The ISL68147 uses the Intersil proprietary linear synthetic current modulation scheme to improve transient performance. This is a unique, constant frequency, dual-edge PWM modulation scheme with both PWM leading and trailing edges being independently moved to give the best response to transient loads. Current balance is an inherent part of the regulation scheme. The modulation scheme is capable of overlapping pulses if the load

FIGURE 7. SHUTDOWN SUPPLY CURRENT vs TEMPERATURE

profile demands such operation. In addition, the modulator is capable of adding or removing pulses from a given cycle in response to regulation demands while still managing maximum average frequency to safe levels. For DC load conditions, the operating frequency is constant.

#### **PMBus Address Selection**

When communicating with multiple PMBus devices on a single bus, each device must have its own unique address so the host can distinguish between the devices. The device address can be set using a 1% resistor on the SA pin according to the pin-strap options listed in Table 2.

| R SA<br>(Ω) | PMBus<br>ADDRESS | R SA<br>(Ω) | PMBus<br>ADDRESS |  |

|-------------|------------------|-------------|------------------|--|

| 0           | 60h              | 1500        | 50h              |  |

| 180         | 61h              | 1800        | 51h              |  |

| 330         | 64h              | 2200        | 54h              |  |

| 470         | 65h              | 2700        | 55h              |  |

| 680         | 40h              | 3300        | 58h              |  |

| 820         | 41h              | 3900        | 59h              |  |

| 1000        | 44h              | 4700        | 5Ch              |  |

| 1200        | 45h              | 5600        | 5Dh              |  |

#### TABLE 2. RESISTOR VALUES TO ADDRESS MAPPING

### **Phase Configuration**

The ISL68147 supports up to two regulated outputs through seven configurable phases. Either output is capable of controlling up to seven phases in any arbitrary mix. Phase assignments are accomplished using PowerNavigator.

Although the device supports arbitrary phase assignment, it is good practice to assign phases to Output 1 in descending sequential numerical order starting from Phase 6. For example, a 4-phase rail could consist of Phases 6, 5, 4, and 3. For Output 0, phases would be assigned starting from Phase 0 in ascending sequential numerical order.

#### **Automatic Phase Add and Drop**

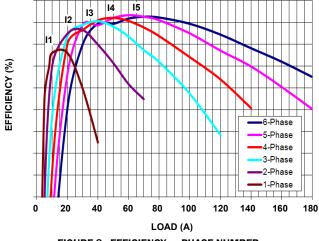

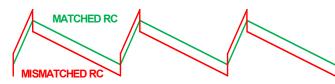

To produce the most optimal efficiency across a wide range of output loading, the modulator supports automatic dropping or adding of phases. Use of automatic phase dropping is optional. If automatic phase dropping is enabled, the number of active phases at any time is determined solely by load current. During operation, phases of Output 1 will drop beginning with the lowest phase number assigned. Phase dropping begins with the highest assigned phase number. Figure 8 illustrates the typical characteristic of efficiency vs load current vs phase count.

Phases are dropped one at a time with a user-programmed drop delay between drop events. As an example, suppose the delay is set to 1ms and 3 phases are active. If the load suddenly drops to a level needing only 1 phase, the ISL68147 will begin by dropping a phase after 1ms. An additional phase will be dropped each 1ms thereafter until only 1 phase remains.

In addition to the described load current add/drop thresholds, the fast phase add function provides a very rapid response to transient load conditions. This feature continuously monitors the system regulation error and, if it exceeds the user set threshold, all dropped phases will be readied for use. In this way, there is no delay if all phases are needed to support a load transient. The fast phase add threshold is set in PowerNavigator. Output current threshold for adding and dropping phases can also be configured.

To ensure dropped phases have sufficient boot capacitor charge to turn on the high-side MOSFET after a long period of disable, a boot refresh circuit turns on the low-side MOSFET of each dropped phase to refresh the boot capacitor. The frequency of the boot refresh is programmable through PowerNavigator.

#### **Output Voltage Configuration**

Output voltage set points and thresholds for each output can be configured in PowerNavigator. Parameters such as output voltage, V<sub>OUT</sub> margin high/low and V<sub>OUT</sub> OV/UV fault thresholds can be configured with GUI. Additionally, output voltage and margin high/low can be adjusted during regulation through the PMBus command VOUT\_COMMAND, VOUT\_MARGIN\_HIGH, and VOUT\_MARGIN\_LOW for further tuning. The following V<sub>OUT</sub> relationships must be maintained for correct operation: VOUT\_OV\_FAULT\_LIMIT > VOUT\_COMMAND (VOUT\_MARGIN\_HIGH and VOUT\_MARGIN\_LOW, if used) > VOUT\_UV\_FAULT\_LIMIT. Additionally, the V<sub>OUT</sub> commands are bounded by VOUT\_MAX and VOUT\_MIN to provide protection against incorrect set points being sent to the device.

#### **Switching Frequency**

The switching frequency is user-configurable over a range of 200kHz to 1MHz.

#### **Current Sensing**

The ISL68147 supports DCR, resistor, and smart power stage current sensing. Connection to the various sense elements is accomplished through the CS and CSRTN pins. Current sensing inputs are high impedance differential inputs to reject noise and ground related inaccuracies.

To accommodate a wide range of effective sense resistance, information about the effective sense resistance and required per phase current capability is used by the GUI to properly configure the current sense circuitry.

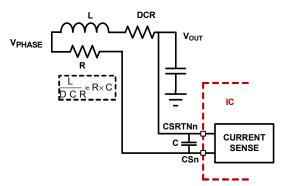

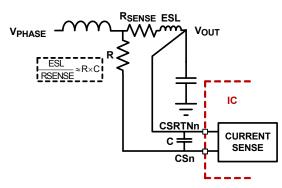

#### **INDUCTOR DCR SENSING**

DCR sensing takes advantage of the fact that an inductor winding has a resistive component (DCR) that will drop a voltage proportional to the inductor current. Figure 9 shows that the DCR is treated as a lumped element with one terminal inaccessible for measurement. Fortunately, a simple R-C network as shown in Figure 10 on page 14 is capable of reproducing the hidden DCR voltage. By simply matching the R-C time constant to the L/DCR time constant, it is possible to precisely recreate the DCR voltage across the capacitor. This means that  $V_{DCR}(t) = V_C(t)$ , thus preserving even the high frequency characteristic of the DCR voltage.

FIGURE 9. DCR SENSING CONFIGURATION

Modern inductors often have such low DCR values that the resulting signal is <10mV. To avoid noise problems, care must be taken in the PCB layout to properly place the R-C components and route the differential lines between controller and inductor. Figure 9 shows one PCB design method that places the R component near the inductor  $V_{PHASE}$  and the C component very close to the IC pins. This minimizes routing of the noisy  $V_{PHASE}$  and maximizes filtering near the IC. The lines between the inductor and IC should be routed as a pair on a single layer directly to the controller. Care must be taken to avoid routing the pair near any switching signals including Phase, PWM etc. This is the method used by Intersil on evaluation board designs.

This method senses the resistance of a metal winding where the DCR value will increase with temperature. This must be compensated or the sensed (and reported) current will increase with temperature. To compensate for the temperature effect, the ISL68147 provides temperature sensing options and an internal methodology to apply the correction.

#### **RESISTIVE SENSING**

For more accurate current sensing, a dedicated current sense resistor,  $R_{SENSE}$ , in series with each output inductor can serve as the current sense element. However, this technique reduces the overall converter efficiency due to the additional power loss on the current sense element,  $R_{SENSE}$ .

FIGURE 10. SENSE RESISTOR IN SERIES WITH INDUCTOR

A current sensing resistor has a distributed parasitic inductance, known as Equivalent Series Inductance (ESL), typically less than 4nH. Consider the ESL as a separate lumped quantity, as shown in Figure 10. The phase current I<sub>L</sub>, flowing through the inductor, will also pass through the ESL. Similar to DCR sensing described previously, a simple R-C network across the current sense resistor extracts the R<sub>SENSE</sub> voltage. Simply match the ESL/R<sub>SENSE</sub> time constant to the R-C time constant.

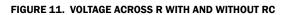

Figure 11 shows the sensed waveforms with and without matching RC when using resistive sense. The PCB layout should be treated similar to that described for DCR sense.

#### L/DCR OR ESL/R<sub>SEN</sub> MATCHING

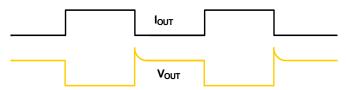

Assuming the compensator design is correct, Figure 12 shows the expected load transient response waveforms if L/DCR or ESL/R<sub>SEN</sub> is matching the R-C time constant. When the load current  $I_{OUT}$  has a square change, the output voltage  $V_{OUT}$  also has a square response, except for the potential overshoot at load release. However, there is always some uncertainty in the true parameter values involved in the time constant matching and therefore fine-tuning is generally required.

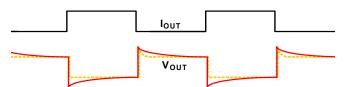

If the R-C time constant is too large or too small,  $V_C(t)$  will not accurately represent real-time  $I_{OUT}(t)$  and will worsen the transient response. Figure 13 shows the load transient response

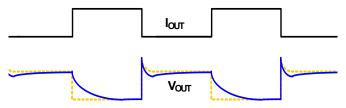

when the R-C timing constant is too small. In this condition,  $V_{OUT}$  will sag excessively upon load insertion and might create a system failure or early overcurrent trip. Figure 14 shows the transient response when the R-C timing constant is too large.  $V_{OUT}$  is sluggish in drooping to its final value. Use these general guides if fine-tuning is needed.

FIGURE 12. DESIRED LOAD TRANSIENT RESPONSE WAVEFORMS

FIGURE 13. LOAD TRANSIENT RESPONSE WHEN R-C TIME CONSTANT IS TOO SMALL

FIGURE 14. LOAD TRANSIENT RESPONSE WHEN R-C TIME CONSTANT IS TOO LARGE

#### SPS CURRENT SENSING

SPS current sense is accomplished by sensing each SPS IMON output individually using VCCS as a common reference. Connect all SPS IREF input pins and all ISL68147 CSRTNn input pins together and tie them to VCCS, then connect the SPS IMONn output pins to the corresponding ISL68147 CSn input pins. The signals should be run as differential pairs from the SPS back to the ISL68147.

#### **Temperature Sensing**

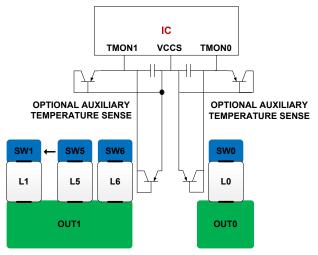

The ISL68147 supports temperature sensing through BJT or smart power stage sense elements. Support for BJT sense elements uses the well known delta Vbe method and allows up to two sensors (MMBT3906 or similar) on each temperature sense input, TMON0 and TMON1. Support for smart power stage uses a linear conversion algorithm and allows one sensor reading per pin. The conversion from voltage to temperature for smart power stage sensing is user-programmable through PowerNavigator.

SPS temperature sensing measures the temperature-dependent voltage output on the SPS TMON pin. All of the SPS devices attached to the Output 0 rail have their TMON pins connected to the ISL68147 TMONO pin. All of the SPS devices attached to the Output 1 rail have their TMON pins connected to the ISL68147

TMON1 pin. The reported temperature is that of the highest temperature SPS of the group.

In addition to the external temperature sense, the IC senses its own die temperature, which can be monitored through PowerNavigator.

Sensed temperature is used in the system for faults, telemetry, and temperature compensation of sensed current.

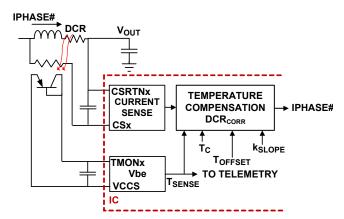

#### **Temperature Compensation**

The ISL68147 supports inductor DCR sensing, which generally requires temperature compensation due to the copper wire used to form inductors. Copper has a positive temperature coefficient of approximately 0.39%/°C. Because the voltage across the inductor is sensed for the output current information, the sensed current has the same positive temperature coefficient as the inductor DCR.

Compensating current sense for temperature variation generally requires that the current sensing element temperature and its temperature coefficient is known. Although the temperature coefficient is generally obtained easily, actual current sense element temperature is essentially impossible to measure directly. Instead, a temperature sensor (a BJT for the ISL68147) placed near the inductors is measured and the current sense element (DCR) temperature is calculated from that measurement. Calculating current sense element temperature is equivalent to applying gain and offset corrections to the temperature sensor measurement. The ISL68147 supports both corrections.

Figure 15 depicts the block diagram of temperature compensation. A BJT placed near the inductors used for DCR sensing is monitored by the IC using the well known delta Vbe method of temperature sensing.  $T_{SENSE}$  is the direct measured temperature of the BJT. Because the BJT is not directly sensing DCR, corrections must be made such that  $T_{DCR}$  reflects the true DCR temperature. Corrections are applied according to the relationship shown in Equation 1, where  $k_{SLOPE}$  represents a gain scaling and  $T_{OFFSET}$  represents an offset correction. The designer can use PowerNavigator to provide the parameters:

$$T_{DCR} = k_{SLOPE} \bullet T_{SENSE} + T_{OFFSET}$$

(EQ. 1)

After T<sub>DCR</sub> has been determined, the compensated DCR value can be determined according to Equation 2, where DCR<sub>25</sub> is the DCR at +25°C and T<sub>C</sub> is the temperature coefficient of copper (3900 ppm/°C). T<sub>DCR</sub> = T<sub>ACTUAL</sub> here:

$$DCR_{CORR} = DCR_{25} \bullet (1 + T_{C} \bullet (T_{ACTUAL} - 25))$$

(EQ. 2)

Thus, the temperature-compensated DCR is now used to determine the actual value of current in the DCR sense element.

FIGURE 15. BLOCK DIAGRAM OF TEMPERATURE COMPENSATION

In the physical PCB design, the temperature sense diode (BJT) is placed close to the inductor of the phase that is never dropped during automatic phase drop operation. Additionally, a filter capacitor no larger than 500pF should be added near the IC between each TMONx pin and VCCS. This is shown in <u>Figure 16</u>.

FIGURE 16. RECOMMENDED PLACEMENT OF TEMPERATURE SENSORS

#### **Lossless Input Current and Power Sensing**

Input current telemetry is provided by an input current synthesizer. By using the IC's ability to precisely determine its operational conditions, input current can be synthesized to a high degree of accuracy without the need for a lossy sense resistor. Fine-tuning of offset and gain are provided for in the GUI. Note that input current sense fine-tuning must be done after output current sense setup is finalized. With a precise knowledge of input current and voltage, input power can be computed.

Input current and power telemetry is accessed through PMBus and easily monitored in PowerNavigator.  $V_{IN}$  is monitored directly by the VINSEN pin through a 1:5 resistor divider as shown in Figure 17 on page 16.

FIGURE 17. INPUT VOLTAGE SENSE CONFIGURATION

#### **Voltage Regulation**

Output voltage is sensed through the remote sense differential amplifier and digitized. From this point, the regulation loop is entirely digital. Traditional PID controls are used in conjunction with several enhanced methods to compensate the voltage regulation loop and tune the transient response.

### **Current Feedback**

Current feedback in a voltage regulator is often used to ease the stability design of the voltage feedback path. Additionally, many microprocessors require the voltage regulator to have a controlled output resistance (known as load line or droop regulation) and this is accomplished using current feedback.

For applications requiring droop regulation, the designer simply specifies the output resistance desired using PowerNavigator.

Current feedback stability benefits are available for rails that do not specify droop regulation such as system agent. For these applications, the designer can enable AC current feedback in PowerNavigator. With this configuration, the DC output voltage will be steady regardless of load current.

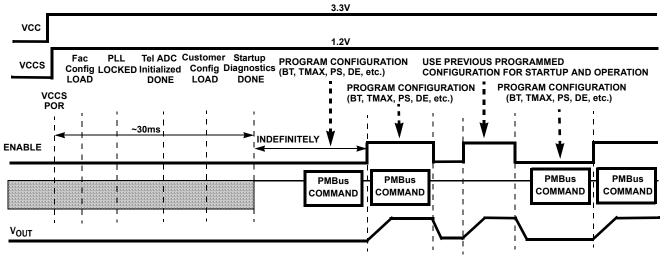

#### **Power-On Reset (POR)**

Initialization of the ISL68147 begins after V<sub>CC</sub> crosses its rising POR threshold. When POR conditions are met, the internal 1.2V LDO is enabled and basic digital subsystem integrity checks begin. During this process, the controller will load the selected user configuration from NVM as indicated by the CONFIG pin resistor value, read VIN UVL0 thresholds from memory, and start the telemetry subsystem. With telemetry enabled, V<sub>IN</sub> can be monitored to determine when it exceeds its user-programmable, rising UVL0 threshold. After V<sub>CC</sub> and V<sub>IN</sub> satisfy their respective voltage conditions, the controller is in its shutdown state. It will transition to its active state and begin soft-start when the state of ENO/EN1 command is at start-up. While in shutdown mode, the PWM outputs are held in a high-impedance state to ensure the drivers remain off.

#### **Soft-Start Delay and Ramp Times**

It might be necessary to set a delay from when an enable signal is received until the output voltage starts to ramp to its target value. In addition, the designer might want to precisely set the time required for an output to ramp to its target value after the delay period has expired. These features can be used as part of an overall inrush current management strategy or to precisely control how fast a load IC is turned on. The ISL68147 gives the system designer several options for precisely and independently controlling both the delay and ramp time periods. The soft-start delay period begins when the EN pin is asserted and ends when the delay time expires.

The soft-start delay and ramp-up/down times can be configured through PowerNavigator. The device needs approximately 200µs after enable to initialize before starting to ramp up. When the soft-start ramp period is set to 0ms, the output ramps up as quickly as the output load capacitance and loop settings allow. It is recommended to set the ramps to a non-zero value to prevent inadvertent fault conditions due to excessive inrush current.

### **Stored Configuration Selection**

As many as eight configurations can be stored and used at any time using the on-board nonvolatile memory. Configurations are assigned an identifier number between 0 and 7 at power-up. The device will load the configuration indicated by the 1% resistor value detected on the CONFIG pin. Resistor values are used to indicate use of one of the eight possible configurations. Table 3 provides the resistor value corresponding to each configuration identifier.

| R CONFIG<br>(Ω) | CONFIG<br>ID |

|-----------------|--------------|

| 6800            | 0            |

| 1800            | 1            |

| 2200            | 2            |

| 2700            | 3            |

| 3300            | 4            |

| 3900            | 5            |

| 4700            | 6            |

| 5600            | 7            |

TABLE 3. RESISTOR VALUES TO CONFIGURATION MAPPING

Only the most recent configuration with a given number can be loaded. The device supports a total of eight stored operations. As an example, a configuration with the identifier 0 could be saved eight times or configurations with all eight identifiers could be stored one time each for a total of eight save operations.

PowerNavigator provides a simple interface to save and load configurations.

## **Fault Monitoring and Protection**

The ISL68147 actively monitors temperature, input voltage, output voltage, and output current to detect and report fault conditions. Fault monitors trigger configurable protective measures to prevent damage to a load. The power-good indicators, PG0/PG1, are provided for linking to external system monitors.

A high level of flexibility is provided in the ISL68147 fault logic. Faults can be enabled or disabled individually. Each fault type can also be configured to either latch off or retry indefinitely.

#### **Power-Good Signals**

The PG0/PG1 pins are open-drain, power-good outputs that indicate completion of the soft-start sequence and output voltage of the associated rail within the expected regulation range.

The PG pins can be associated or disassociated with a number of the available fault types. This allows a system design to be tailored for almost any condition. In addition, these power-good indicators will be pulled low when a fault (OCP or OVP) condition or UV condition is detected on the associated rail.

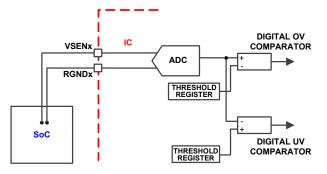

#### **Output Voltage Protection**

Output voltage is measured at the load sensing points differentially for regulation and the same measurement is used for OVP and UVP. The fault thresholds are set using PMBus commands. Figure 18 shows a simplified OVP/UVP block diagram. The output voltage comparisons are done in the digital domain.

FIGURE 18. OVP, UVP COMPARATORS

The device responds to an output overvoltage condition by disabling the output, declaring a fault, setting the SALRT pin, setting the PG pin, and then pulsing the LFET until the output voltage has dropped below the threshold. Similarly, the device responds to an output undervoltage condition by disabling the output, declaring a fault, setting the SALRT pin, and setting the PG pin. The output will not restart until the EN pin is cycled (unless the device is configured to retry).

In addition, the ISL68147 features open pin sensing protection to detect an open of the output voltage sensing circuit. When this condition is detected, controller operation is suspended.

#### **Output Current Protection**

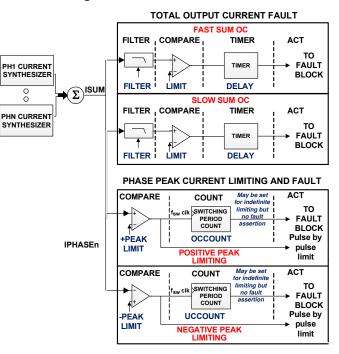

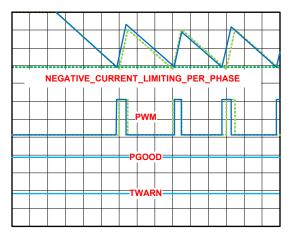

The ISL68147 offers a comprehensive overcurrent protection scheme. Each phase is protected from both excessive peak current and sustained current. In addition, the system is protected from sustained total output overcurrent.

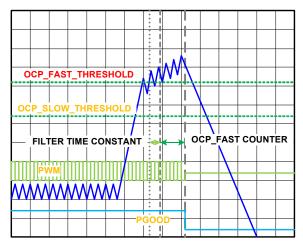

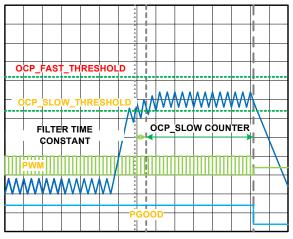

Figure 19 depicts a block diagram of the system total output current protection scheme. In this scheme, the phase currents are summed to form ISUM. ISUM is then fed to dual response paths allowing the user to program separate LPF, threshold, and response time. One path is intended to allow response more quickly than the other path. With this system, the user can allow high peak total current for a short time and a lower level of current for a sustained time. Note that neither of these paths

affect PWM activity on a cycle-by-cycle basis. The characteristics of each path are easily set in PowerNavigator.

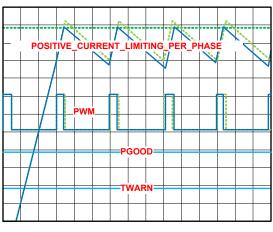

In addition to total output current, the ISL68147 provides an individual phase peak current limit that will act on PWM in a cycle-by-cycle manner. This means that if a phase current is detected to exceed the OC threshold, the phase PWM signal will be inverted to move current away from the threshold. In addition to limiting positive or negative peak current on a cycle-by-cycle basis, individual phase OC can be configured to limit current indefinitely or to declare a fault after a programmable number of consecutive OC cycles. This feature is useful for applications where a fault shutdown of the system would not be acceptable but some ability to limit phase currents is desired. Figures 22 and 23 depict this operation. If configured for an indefinite current limit, the converter will act as a current source and VOLT will not remain at its regulation point. It should be noted that in this case, a  $V_{OUT}$  OV or UV protection action can occur, which could shut the regulator down.

FIGURE 19. OCP FUNCTIONAL DIAGRAM

Example OCP\_Fast and OCP\_Slow waveforms are shown in Figures 20 and 21.

FIGURE 20. OCP\_FAST

FIGURE 21. OCP\_SLOW

FIGURE 22. POSITIVE PEAK PHASE CURRENT LIMITING

FIGURE 23. NEGATIVE PEAK PHASE CURRENT LIMITING

### **Smart Power Stage OC Fault Detect**

Intersil Smart Power Stage (SPS) devices will output a large signal on their IMON lines if the peak current exceeds their preprogrammed threshold. (For more details about this functionality, refer to the relevant SPS datasheet.) The ISL68147 is equipped to detect this fault flag and immediately shut down. This detector is enabled on the GUI Overcurrent Fault setup screen.

This feature functions by detecting signals that exceed the current sense ADC full scale range. If this detector is disabled while using an Intersil SPS, the SPS Fault# signal must be connected to the controller Enable pin of the associated rail. This will ensure that and SPS OC event will be detected and the converter will shut down.

### **Thermal Monitoring and Protection**

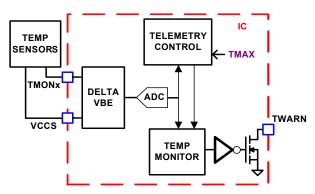

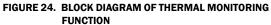

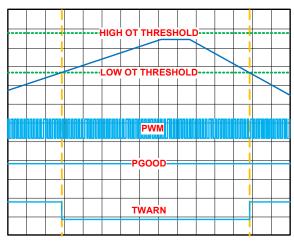

The TWARN pin indicates the temperature status of the voltage regulator. The TWARN pin is an open-drain output and an external pull-up resistor is required. This signal is valid only after the controller is enabled.

The TWARN signal can be used to inform the system that the temperature of the voltage regulator is too high and the load should reduce its power consumption. TWARN only indicates a thermal warning, not a fault.

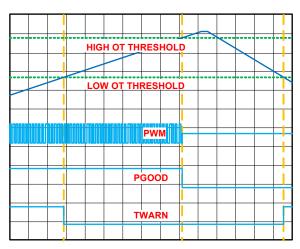

The thermal monitoring function block diagram is shown in Figure 24 on page 19. The ISL68147 has two over-temperature thresholds, which allow both warning and fault indications. Each temperature sensor threshold can be independently programmed in PowerNavigator. Figure 25 on page 19 shows the thermal warning to TWARN and Figure 26 on page 19 shows the over-temperature fault to shut down. PGOOD and TWARN can be configured to indicate these warning and fault thresholds through PowerNavigator.

FIGURE 25. THERMAL WARNING TO TWARN

FIGURE 26. OVER-TEMPERATURE FAULT

## **Layout and Design Considerations**

In addition to <u>TB379</u>, the following PCB layout and design strategies are intended to minimize noise coupling and the impact of board parasitic impedances on converter performance. In addition, these strategies will optimize the heat dissipating capabilities of the printed circuit board. This section highlights some important practices, which should be followed during the layout process.

<u>Table 4</u> provides general guidance on best practices related to pin noise sensitivity. Good engineering judgment is required to implement designs based on criteria specific to the situation.

| PIN<br>NAME         | NOISE<br>SENSITIVE | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |

|---------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VINSEN              | Yes                | Connects to the resistor divider between VIN and GND (see <u>Figure 17 on page 16</u> ). Filter VINSEN with 10nF to GND.                                                                                                                                                                                                       |

| RGND<br>VSEN        | Yes                | Treat each of the remote voltage sense pairs as<br>differential signals in the PCB layout. They should<br>be routed side by side on the same layer. They<br>should not be routed in proximity to noisy signals<br>like PWM or Phase. Tie to ground when not used.                                                              |

| PG                  | No                 | Open-drain. 3.3V maximum pull-up voltage. Tie to ground when not used.                                                                                                                                                                                                                                                         |

| SCL, SDA,<br>SALRT  | Yes                | 50kHz to 2MHz signal during communication,<br>pair up with SALRT and route carefully. 20 mils<br>spacing within SDA, SALRT, and SCL, and more<br>than 30 mils to all other signals. Refer to the<br>SMBus design guidelines and place proper<br>termination resistance for impedance matching.<br>Tie to ground when not used. |

| TMON                | Yes                | When diode sensing is used, VCCS is the return<br>path for the delta Vbe currents. Use a separate<br>VCCS route specifically for diode temp sense. A<br>filter capacitor no greater than 500pF should be<br>placed between each TMON pin and at VCCS pin<br>near the IC. Tie to ground when not used.                          |

| TWARN               | No                 | Open-drain. 3.3V maximum pull-up voltage.                                                                                                                                                                                                                                                                                      |

| VCC                 | Yes                | Place at least 2.2µF MLCC decoupling capacitor directly at the pin.                                                                                                                                                                                                                                                            |

| VCCS                | Yes                | Place 4.7 $\mu$ F MLCC decoupling capacitor directly at the pin.                                                                                                                                                                                                                                                               |

| PWM                 | No                 | Avoid routing near noise sensitive analog lines such as current sense or voltage sense.                                                                                                                                                                                                                                        |

| CS<br>CSRTN         | Yes                | Treat each of the current sense pairs as<br>differential signals in the PCB layout. They should<br>be routed side by side on the same layer. They<br>should not be routed in proximity to noisy signals<br>like PWM or Phase. Proper routing of current<br>sense is perhaps the most critical of all the layout<br>tasks.      |

| GND                 | Yes                | This EPAD is the return of PWM output drivers.<br>Use four or more vias to directly connect the EPAD<br>to the power ground plane.                                                                                                                                                                                             |

| General<br>Comments |                    | The layer next to the top or bottom layer is<br>preferred to be ground layers, while the signal<br>layers can be sandwiched in the ground layers if<br>possible.                                                                                                                                                               |

| TABLE 4. | <b>PIN DESIGN AN</b> | D/OR LAYOUT | CONSIDERATION |

|----------|----------------------|-------------|---------------|

|----------|----------------------|-------------|---------------|

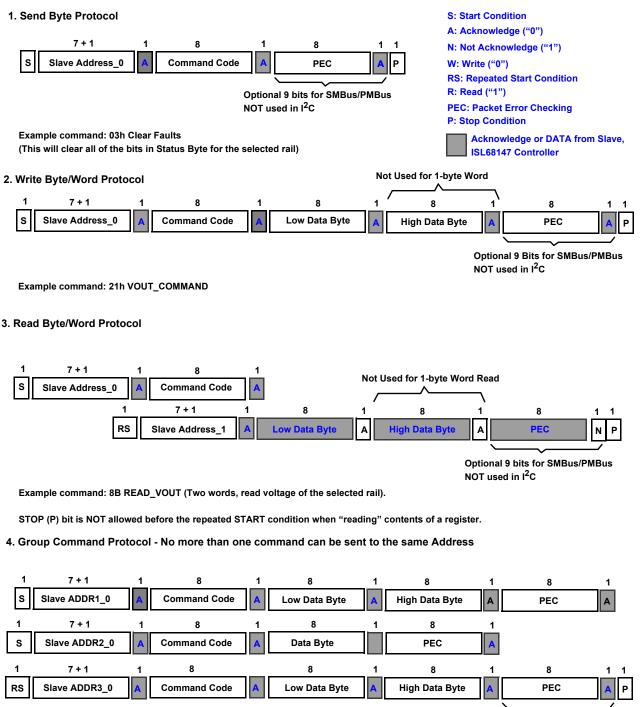

## **PMBus Operation**

The ISL68147 PMBus slave address is pin selectable, using the SA pin and resistor value described in <u>Table 2 on page 12</u>. For proper operation, users should follow the PMBus protocol, as shown in <u>"PMBus Protocol" on page 21</u>. The supported PMBus addresses are in 8-bit format (including write and read bit): 80-8E, A0-AE, B0-BE, and C0-CE. The least significant bit of the 8-bit address is for write (Oh) and read (1h). PMBus commands are in the range from 0x00h to 0xFFh. For the ISL68147, Page 0 corresponds to Output 0 and Page 1 to Output 1. For reference purposes, the 7-bit format addresses are also summarized in <u>Table 5</u>.

TABLE 5. PMBus 8-BIT AND 7-BIT FORMAT ADDRESS (HEX)

| 8-BIT | 7-BIT | 8-BIT | 7-BIT | 8-BIT | 7-BIT | 8-BIT | 7-BIT |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 80/81 | 40    | A0/A1 | 50    | B0/B1 | 58    | C0/C1 | 60    |

| 82/83 | 41    | A2/A3 | 51    | B2/B3 | 59    | C2/C3 | 61    |

| 88/89 | 44    | A8/A9 | 54    | B8/B9 | 5C    | C8/C9 | 64    |

| 8A/8B | 45    | AA/AB | 55    | BA/BB | 5D    | CA/CB | 65    |

The PMBus data formats follow PMBus Specification version 1.3 and SMBus version 2.0.

Basic PMBus telemetry commands are summarized in <u>"PMBus</u> <u>Command Summary" on page 22</u>.

FIGURE 27. SIMPLIFIED PMBus INITIALIZATION TIMING DIAGRAM

## **PMBus Protocol**

Optional 9 bits for SMBus/PMBus NOT used in I<sup>2</sup>C

5. Alert Response Address (ARA, 0001\_1001, 25h) for SMBus and PMBus, not used for I<sup>2</sup>C

Optional 9 bits for SMBus/PMBus NOT used in I<sup>2</sup>C

## **PMBus Command Summary**

| CODE | COMMAND NAME         | DESCRIPTION                                                       | TYPE  | DATA<br>FORMAT | DEFAULT<br>VALUE | DEFAULT SETTING     |

|------|----------------------|-------------------------------------------------------------------|-------|----------------|------------------|---------------------|

| 00h  | PAGE                 | Selects Output 0, 1, or both                                      | R/W   | Bit Field      | 00h              | Page 0              |

| 01h  | OPERATION            | Enable/disable, margin settings                                   | R/W   | Bit Field      | 08h              | Off                 |

| 02h  | ON_OFF_CONFIG        | On/off configuration settings                                     | R/W   | Bit Field      | 16h              | ENABLE pin control  |

| 03h  | CLEAR_FAULTS         | Clears all fault bits in all registers and releases the SALRT pin | Write | N/A            | N/A              |                     |

| 10h  | WRITE_PROTECT        | Write protection to sets of commands                              | R/W   | Bit Field      | 00h              | No write protection |

| 20h  | VOUT_MODE            | Defines format for output voltage related commands                | Read  | Bit Field      | 40h              | Direct format       |

| 21h  | VOUT_COMMAND         | Sets the nominal V <sub>OUT</sub> target                          | R/W   | Direct         | 0384h            | 900mV               |

| 22h  | VOUT_TRIM            | Applies trim voltage to V <sub>OUT</sub> set-point                | R/W   | Direct         | 0000h            | 0mV                 |

| 24h  | VOUT_MAX             | Absolute maximum voltage setting                                  | R/W   | Direct         | 08FCh            | 2300mV              |

| 25h  | VOUT_MARGIN_HIGH     | Sets V <sub>OUT</sub> target during margin high                   | R/W   | Direct         | 0640h            | 1600mV              |

| 26h  | VOUT_MARGIN_LOW      | Sets V <sub>OUT</sub> target during margin low                    | R/W   | Direct         | 00FAh            | 250mV               |

| 27h  | VOUT_TRANSITION_RATE | Slew rate setting for V <sub>OUT</sub> changes                    | R/W   | Direct         | 0064h            | 10mV/µs             |

| 28h  | VOUT_DROOP           | Sets the load line (V/I slope) resistance for the output          | R/W   | Direct         | 0000h            | ΟμV/Α               |

| 2Bh  | VOUT_MIN             | Absolute minimum target voltage setting                           | R/W   | Direct         | 0000h            | 0mV                 |

| 40h  | VOUT_OV_FAULT_LIMIT  | Sets the V <sub>OUT</sub> overvoltage fault threshold             | R/W   | Direct         | 076Ch            | 1900mV              |

| 44h  | VOUT_UV_FAULT_LIMIT  | Sets the V <sub>OUT</sub> undervoltage fault threshold            | R/W   | Direct         | 0000h            | OmV                 |

| 4Fh  | OT_FAULT_LIMIT       | Sets the over-temperature fault threshold                         | R/W   | Direct         | 007Dh            | +125°C              |

| 51h  | OT_WARN_LIMIT        | Sets the over-temperature warn threshold                          | R/W   | Direct         | 07D0h            | +2000°C             |

| 55h  | VIN_OV_FAULT_LIMIT   | Sets the V <sub>IN</sub> overvoltage fault threshold              | R/W   | Direct         | 36B0h            | 14,000mV            |

| 59h  | VIN_UV_FAULT_LIMIT   | Sets the V <sub>IN</sub> undervoltage fault threshold             | R/W   | Direct         | 1F40h            | 8,000mV             |

| 5Bh  | IIN_OC_FAULT_LIMIT   | Sets the I <sub>IN</sub> overcurrent fault threshold              | R/W   | Direct         | 0032h            | 50A                 |

| 60h  | TON_DELAY            | Sets the delay time from enable to V <sub>OUT</sub> rise          | R/W   | Direct         | 0014h            | 200µs               |

| 61h  | TON_RISE             | Turn-on rise time                                                 | R/W   | Direct         | 01F4h            | 500µs               |

| 64h  | TOFF_DELAY           | Turn-off delay time                                               | R/W   | Direct         | 0000h            | Oµs                 |

| 65h  | TOFF_FALL            | Turn-off fall time                                                | R/W   | Direct         | 01F4h            | 500µs               |

| 78h  | STATUS_BYTE          | First byte of STATUS_WORD                                         | Read  | Bit Field      | N/A              | N/A                 |

| 79h  | STATUS_WORD          | Summary of critical faults                                        | Read  | Bit Field      | N/A              | N/A                 |

| 7Ah  | STATUS_VOUT          | Reports V <sub>OUT</sub> faults                                   | Read  | Bit Field      | N/A              | N/A                 |

| 7Bh  | STATUS_IOUT          | Reports I <sub>OUT</sub> faults                                   | Read  | Bit Field      | N/A              | N/A                 |

| 7Ch  | STATUS_INPUT         | Reports input faults                                              | Read  | Bit Field      | N/A              | N/A                 |

| 7Dh  | STATUS_TEMPERATURE   | Reports temperature warnings/faults                               | Read  | Bit Field      | N/A              | N/A                 |

| 7Eh  | STATUS_CML           | Reports communication, memory, logic errors                       | Read  | Bit Field      | N/A              | N/A                 |

| 80h  | STATUS_MFR_SPECIFIC  | Reports specific events                                           | Read  | Bit Field      | N/A              | N/A                 |

| 88h  | READ_VIN             | Reports input voltage measurement                                 | Read  | Direct         | N/A              | N/A                 |

| 89h  | READ_IIN             | Reports input current measurement                                 | Read  | Direct         | N/A              | N/A                 |

| 8Bh  | READ_VOUT            | Reports output voltage measurement                                | Read  | Direct         | N/A              | N/A                 |

| 8Ch  | READ_IOUT            | Reports output current measurement                                | Read  | Direct         | N/A              | N/A                 |