# IAR Debug probes User Guide

I-jet®, I-jet Trace, and I-scope™

for Advanced RISC Machines Ltd's ARM® Cores

#### **COPYRIGHT NOTICE**

© 2012-2017 IAR Systems AB.

No part of this document may be reproduced without the prior written consent of IAR Systems AB. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such a license.

#### **DISCLAIMER**

The information in this document is subject to change without notice and does not represent a commitment on any part of IAR Systems. While the information contained herein is assumed to be accurate, IAR Systems assumes no responsibility for any errors or omissions.

In no event shall IAR Systems, its employees, its contractors, or the authors of this document be liable for special, direct, indirect, or consequential damage, losses, costs, charges, claims, demands, claim for lost profits, fees, or expenses of any nature or kind.

#### **TRADEMARKS**

IAR Systems, IAR Embedded Workbench, IAR Connect, C-SPY, C-RUN, C-STAT, visualSTATE, IAR KickStart Kit, IAR Experiment!, I-jet, I-jet Trace, I-scope, IAR Academy, IAR, and the logotype of IAR Systems are trademarks or registered trademarks owned by IAR Systems AB.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

ARM and Thumb are registered trademarks of Advanced RISC Machines Ltd. EmbeddedICE is a trademark of Advanced RISC Machines Ltd. uC/OS-III and uC/OS-III are trademarks of Micrium, Inc. CMX-RTX is a trademark of CMX Systems, Inc. ThreadX is a trademark of Express Logic. RTXC is a trademark of Quadros Systems. Fusion is a trademark of Unicoi Systems.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems Incorporated.

All other product names are trademarks or registered trademarks of their respective owners.

#### **EDITION NOTICE**

Sixth edition: March 2017 Part number: IARprobes-6 Internal reference: IMAE.

# **Contents**

| ı-jet       |                                                                    | 5    |

|-------------|--------------------------------------------------------------------|------|

| Intro       | duction                                                            | 5    |

|             | The I-jet in-circuit debugging probe                               | 5    |

|             | Requirements                                                       | 7    |

|             | Supported ARM core families                                        | 7    |

|             | Target connections                                                 | 7    |

| Wor         | king with I-jet                                                    | 7    |

|             | Setup and installation                                             | 8    |

|             | Connecting the target system                                       | 8    |

|             | Updating the probe firmware                                        | 9    |

| Tech        | nical specifications                                               | . 13 |

|             | The I-jet package                                                  | . 13 |

|             | Model specifications                                               | . 13 |

|             | JTAG timing specification                                          | . 15 |

|             | Hardware revision history                                          | . 16 |

|             | Target interface                                                   | . 17 |

|             | Indicators                                                         | . 20 |

|             | Adapters                                                           | . 21 |

| I-jet Trace |                                                                    | 35   |

| Intro       | duction                                                            | . 35 |

|             | The I-jet Trace CM and I-jet Trace A/R/M in-circuit debugging prob | oes  |

|             | 35                                                                 |      |

|             | Requirements                                                       | .36  |

|             | Target connections                                                 | . 37 |

| Wor         | king with I-jet Trace                                              | .37  |

|             | Setup and installation                                             | .38  |

|             | Connecting the target system                                       | . 38 |

|             | Using trace                                                        | . 39 |

|             | Updating the probe firmware                                        | . 39 |

|             |                                                                    |      |

| Tech    | nical specifications                                                                                                                           | 40                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|         | The I-jet Trace package                                                                                                                        | 40                   |

|         | Model specifications                                                                                                                           | 40                   |

|         | Hardware revision history                                                                                                                      | 42                   |

|         | Connectors                                                                                                                                     | 43                   |

|         | Indicators                                                                                                                                     | 45                   |

|         | Adapters                                                                                                                                       | 47                   |

|         | Designing target boards for ETM trace                                                                                                          | 51                   |

|         | General PCB layout guidelines                                                                                                                  | 51                   |

| I-scope |                                                                                                                                                | 55                   |

|         |                                                                                                                                                |                      |

| Intro   | oduction                                                                                                                                       | 55                   |

| Intro   | Reasons for using I-scope                                                                                                                      |                      |

| Intro   |                                                                                                                                                | 55                   |

| Intro   | Reasons for using I-scope                                                                                                                      | 55                   |

|         | Reasons for using I-scope  The I-scope probe                                                                                                   | 55<br>55             |

|         | Reasons for using I-scope  The I-scope probe  Current and voltage measurement using I-scope                                                    | 55<br>55<br>55       |

| Wor     | Reasons for using I-scope  The I-scope probe  Current and voltage measurement using I-scope  king with I-scope                                 | 55<br>55<br>55<br>57 |

| Wor     | Reasons for using I-scope  The I-scope probe  Current and voltage measurement using I-scope  king with I-scope  Installation                   |                      |

| Wor     | Reasons for using I-scope The I-scope probe Current and voltage measurement using I-scope king with I-scope Installation unical specifications |                      |

# I-jet

- Introduction

- Working with I-jet

- Technical specifications

#### Introduction

These topics are covered:

- The I-jet in-circuit debugging probe

- Requirements

- Supported ARM core families

- Target connections.

#### THE I-JET IN-CIRCUIT DEBUGGING PROBE

The I-jet in-circuit debugging probe has full support for on-chip trace: ETB, MTB, and TMC (Trace Memory Controller).

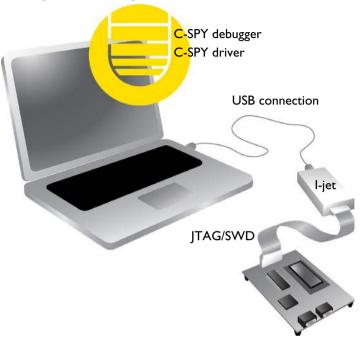

I-jet connects to the target board via a JTAG, SWD, or cJTAG connection, and to the host computer via the USB port.

I-jet communicates using USB 2.0. USB 1.0 is also supported but not advised. The I-jet in-circuit debugging probe is also referred to as a debug probe, debug adapter, or JTAG in-circuit emulator by different tool vendors.

I-jet streams the program counter, variables, and power measurement data to the host computer to provide a view into program execution in real time. Besides the typical JTAG debugging, I-jet is capable of providing power to the target board and measuring

it with sufficient accuracy to provide a power profile during program execution in real time. This feature is referred to as *power debugging*.

For debugging Cortex devices, I-jet also supports the SWO (Serial Wire Output) feature, which can be used for tracing the program execution and tracking variables at predefined points in your code.

The I-jet in-circuit debugging probe has full support for on-chip trace: ETB, MTB, and TMC (Trace Memory Controller).

#### **REQUIREMENTS**

I-jet needs to be controlled by the IAR C-SPY® Debugger which comes with the IAR Embedded Workbench® IDE.

#### **SUPPORTED ARM CORE FAMILIES**

These cores are currently supported:

- ARM7

- ARM9

- ARM11

- Cortex-M

- Cortex-R

- Cortex-A.

#### **TARGET CONNECTIONS**

These interfaces are supported:

- MIPI-20 (part number SHF-110-01-L-D): JTAG, cJTAG, SWD, SWO, ETM

- MIPI-10 (part number SHF-105-01-L-D): JTAG, cJTAG, SWD, SWO

- ARM-20 (part number HTST-110-01-L-DV): JTAG, cJTAG, SWD, SWO

I-jet comes with a MIPI-20 connector on the front panel and with MIPI-20 and MIPI-10 cables, as well as a legacy ARM-20 adapter.

All other available I-jet adapters are also compatible with I-jet Trace.

## Working with I-jet

These tasks are covered:

- Setup and installation

- Connecting the target system.

• Updating the probe firmware

For information about debugging using I-jet, see the *C-SPY® Debugging Guide for ARM*.

#### SETUP AND INSTALLATION

#### **S**oftware

Before you can use I-jet, you need to install IAR Embedded Workbench for ARM.

#### **Probe setup**

I-jet does not require any special driver software installation. Normally, all drivers for I-jet are automatically installed as part of the installation of IAR Embedded Workbench.

If you need to install the USB driver manually, navigate to

For information about using multiple I-jet probes on the same host computer, see the *C-SPY® Debugging Guide for ARM*.

#### **CONNECTING THE TARGET SYSTEM**

#### Power-up your I-jet probe

- I Connect I-jet to the host computer using the USB micro cable.

- 2 Connect I-jet to the target board using the cable that matches the target board connector (MIPI-20 or MIPI-10). If a standard JTAG connector is used, you must first plug the ARM-20 to MIPI-20 adapter into the JTAG connector.

Note: No harm is done if the above order is reversed.

To prevent damage, the target GND and the USB host GND must be at the same level. When *hot-plugging*, make sure that the PC and the target board power supply are connected to the same grounded wall outlet or a common grounded desktop power strip.

#### Power up your evaluation board

If you have an evaluation board that is prepared for it, you can power the board via I-jet through pin 19 on the standard ARM-20 connector, or pin 11/13 on the small MIPI-20 connector. Target power of up to 420 mA can be supplied from I-jet with overload protection. Most of the IAR Systems KickStart Kits contain an evaluation board that can be powered this way. Make sure that the power jumper found on most of these boards matches your setup.

**Note:** The target board will get power via I-Jet once you choose the **Download and Debug** or **Debug without Downloading** command, but not before.

**Note:** The only way to use the power debugging feature is to power up your evaluation board via I-jet.

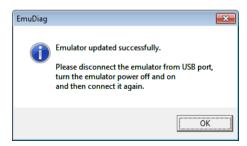

#### **UPDATING THE PROBE FIRMWARE**

I-jet and I-jet Trace are designed so that firmware updates are not necessary unless new features added to IAR Embedded Workbench for ARM require extra hardware support. When a new version of IAR Embedded Workbench for ARM is released and a new feature that requires new firmware is used, C-SPY displays a message in the **Debug Log** window asking you to update the firmware.

**Note:** Support for new MCU devices is managed totally by software updates in IAR Embedded Workbench for ARM and has nothing to do with I-jet or I-jet Trace firmware.

For more information about firmware versions, see the release notes.

#### To update the probe firmware:

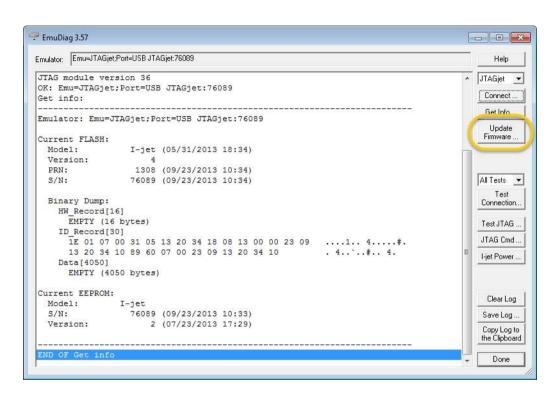

In IAR Embedded Workbench, choose I-jet/JTAGjet>EmuDiag to display the About to Connect to an Emulator dialog box.

Select Connect to an Emulator Automatically and click Next.

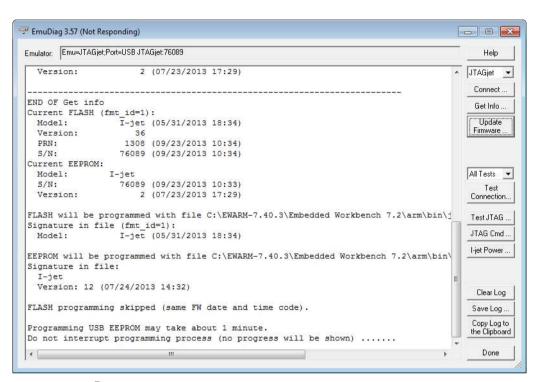

2 In the EmuDiag dialog box that is displayed, click the Update Firmware button.

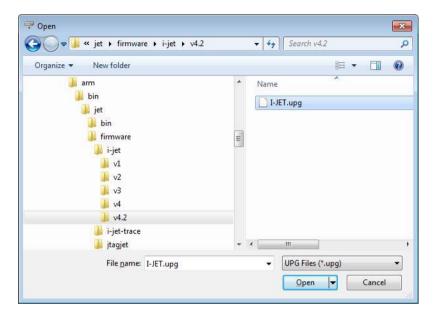

**3** In the dialog box that is displayed, browse to the arm\bin\jet\firmware\i-jet folder of your IAR Embedded Workbench installation. In one of the subfolders, select the firmware file that you want to use and click **Open**.

4 The update log information is printed in the **EmuDiag** dialog box.

**5** When the firmware update is complete, a message is displayed.

## **Technical specifications**

Reference information about:

- The I-jet package, page 13

- Model specifications, page 13

- JTAG timing specification, page 15

- Hardware revision history, page 16

- Target interface, page 17

- The JTAG/SWD MIPI-20 cable, page 17

- The JTAG/SWD MIPI-10 cable, page 19

- Indicators, page 20

- Adapters, page 21.

#### THE I-JET PACKAGE

The I-jet package contains:

- The I-jet in-circuit debugging probe

- MIPI-20 JTAG cable

- MIPI-10 JTAG cable

- USB 2.0 Micro B cable

- MIPI-20 to ARM-20 adapter

- Welcome letter.

#### **MODEL SPECIFICATIONS**

These are the specifications of I-jet:

USB speed 480 Mbps (USB 2.0)

USB connection Micro-B

Target connection MIPI-20, MIPI-10

**Adapters included** MIPI-20 to ARM-20

I-jet debug interface JTAG and SWD

JTAG/SWD maximum clock 32 MHz

SWO protocols supported Manchester and UART

**SWO maximum speed** 60 Mbps

**Power supplied to target** 420 mA max at 4.4 V-5 V

Over-current protection ~520 mA

Target power measurement resolution ~160 uA

Target power measurement speed up to 200 ksps (kilo samples per second)

JTAG voltage range (auto-sensing) 1.65 V to 5.5 V

JTAG VTref measurement resolution ~2 mV

Current draw from VTref <50 uA

JTAG clock rise/fall time (TCK) <= 2 ns\*

Clock fall time <= 2 ns\*

I-jet comes with a 20-pin MIPI connector (0.05 in  $\times$  0.05 in pitch) on the front panel. It includes two cables:

- A 6-inch cable with 20-pin MIPI connectors on both ends for the Cortex-M targets with 20-pin MIPI headers. Pin 7 on each end is keyed with a white plug.

- A 6-inch cable with 20-pin MIPI connectors on one side (to connect to I-jet), and 10-pin MIPI connector on the other side for connection to Cortex-M targets with 10-pin headers. Pin 7 on each end is keyed with a white plug. A red stripe on the cable indicates pin 1 (VTref).

<sup>\* &</sup>lt;= 4 ns when the target board is connected

#### JTAG TIMING SPECIFICATION

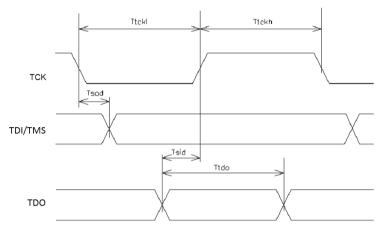

This figure shows the JTAG timing and parameters:

In a JTAG device that fully complies to IEEE1149.1 standard, the TDI/TMS signals should be sampled on the rising edge of TCK, and TDO should be sent on the falling edge of TCK. I-jet takes advantage of these requirements and changes its TDI and TMS signals on the falling edge of TCK and samples the TDO on the rising edge of TCK. However, to accommodate target boards with long JTAG chains and fast JTAG clocks, I-jet allows TDO to be as late as 50 ns after the rising edge of TCK.

**Note:** In the adaptive mode of operation, I-jet samples the TDO on the rising edge of RTCK rather than TCK.

This table shows the timing specifications of the JTAG port measured at the end of its MIPI-20 cable without connection to target (VTref set to 3.3 V). The only load on the measured signals is the oscilloscope 3.9 pF probe.

| Parameter          | Min                                   | Max    | Description                                |

|--------------------|---------------------------------------|--------|--------------------------------------------|

| T <sub>tckl</sub>  | 15.6 ns                               | 250 us | TCK LOW period                             |

| $T_tckh$           | 15.6 ns                               | 250 us | TCK HIGH period                            |

| T <sub>sod</sub> I |                                       | 2.0 ns | TDI and TMS outputs valid from TCK falling |

| $T_{sid}^2$        | 3 ns before TCK to<br>50 ns after TCK |        | TDO setup to TCK rising                    |

| $T_tdo$            | $T_{tckl}$                            |        | TDO valid length                           |

Table 1: Timing for the I-jet JTAG port

$1~T_{sod}$  is the maximum delay from the falling edge of TCK and a valid level on the I-jet output signals TDI and TMS. The target MCU will sample these signals on the following rising edge of TCK and so the minimum setup time for the target, relative to the rising edge of TCK, is  $T_{bsol}$ - $T_{bsod}$ .

$2\,T_{sid}$  is the minimum setup time for the TDO input signal, relative to the rising edge of TCK when I-jet samples this signal. Because the target MCU changes its TDO value on the previous falling edge of TCK, there might not be enough time at very-high JTAG speeds for the TDO to arrive before the positive edge of TCK. To compensate for any TDO delays, I-jet configures itself automatically to delays introduced to the TDO by the target board and will tolerate TDO delays of up to 50 ns after the positive edge of the TCK.

#### HARDWARE REVISION HISTORY

These are the versions of I-jet:

| Version   | Change specification | Date       |

|-----------|----------------------|------------|

| Version A | The first version    | April 2012 |

Table 2: I-jet versions

Version, production date, and serial number can be found on the backside of the probe.

**Note:** In IAR Embedded Workbench, choose **I-jet/JTAGjet>EmuDiag** to open the **EmuDiag** dialog box where you can find both hardware and firmware versions of the plugged-in I-jet.

#### **TARGET INTERFACE**

This section contains descriptions of pinout, signals, and connectors.

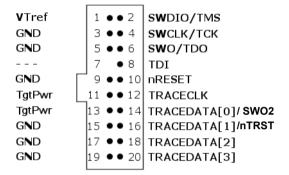

#### The JTAG/SWD - MIPI-20 cable

I-jet comes with a 6-inch cable with 20-pin MIPI connectors on both ends for the Cortex-M devices with 20-pin MIPI headers. Pin 7 on each end is keyed with a white plug:

The mating connector for a target board has the part number SHF-110-01-L-D.

These are the MIPI-20 pin definitions:

| Pin | Signal    | Туре        | Description                                                                                                                                                                                                                                       |

|-----|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I   | VTref     | Input       | The target reference voltage. Used by I-jet to check whether the target has power, to create the logic-level reference for the input comparators, and to control the output logic levels to the target. It is normally fed from JTAG I/O voltage. |

| 2   | SWDIO/TMS | I/O, output | JTAG mode set input of target CPU. This pin should be pulled up on the target. Typically connected to TMS of the target CPU.                                                                                                                      |

| 3   |           |             | This pin is a GND pin connected to GND in I-jet. It should also be connected to GND in the target system.                                                                                                                                         |

| 4   | SWCLK/TCK | Output      | JTAG clock signal to target CPU. It is recommended that this pin is pulled to a defined state of the target board. Typically connected to TCK of the target CPU.                                                                                  |

Table 3: MIPI-20 pin definitions

| Pin            | Signal                 | Туре   | Description                                                                                                                                                                                                                                             |

|----------------|------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5              |                        |        | This pin is a GND pin connected to GND in I-jet. It should also be connected to GND in the target system.                                                                                                                                               |

| 6              | SWO/TDO                | Input  | JTAG data output from target CPU. Typically connected to TDO of the target CPU. When using SWD, this pin is used as Serial Wire Output trace port. (Optional, but not required for SWD communication.)                                                  |

|                |                        |        | This pin (normally pin 7) does not exist.                                                                                                                                                                                                               |

| 8              | TDI                    | Output | JTAG data input of target CPU. It is recommended that this pin is pulled to a defined state on the target board. Typically connected to TDI of the target CPU. For CPUs which do not provide TDI (SWD-only devices), this pin is not used (tri-stated). |

| 9              |                        |        | This pin is a GND pin connected to GND in I-jet. It should also be connected to GND in the target system.                                                                                                                                               |

| 10             | nRESET                 | I/O    | Target CPU reset signal. Typically connected to the RESET pin of the target CPU, which is typically called nRST, nRESET, or RESET.                                                                                                                      |

| 11             | TgtPwr                 | Output | This pin can be used for supplying 5 V power to the target hardware from I-jet.                                                                                                                                                                         |

| 12<br>Not used | TRACECLK               | Input  | Input trace clock.                                                                                                                                                                                                                                      |

| 13             | TgtPwr                 | Output | This pin can be used for supplying 5 V power to the target hardware from I-jet.                                                                                                                                                                         |

| 14<br>Not used | TRACEDATA[0]/<br>SWO2  | Input  | Input Trace data pin 0. This pin can be used as secondary SWO.                                                                                                                                                                                          |

| 15             |                        |        | This pin is a GND pin connected to GND in I-jet. It should also be connected to GND in the target system.                                                                                                                                               |

| 16<br>Not used | TRACEDATA[I]/<br>nTRST | Input  | Input Trace data pin I. This pin can be used as $nTRST$ .                                                                                                                                                                                               |

| 17             |                        |        | This pin is a GND pin connected to GND in I-jet. It should also be connected to GND in the target system.                                                                                                                                               |

Table 3: MIPI-20 pin definitions

| Pin            | Signal       | Туре  | Description                                                                                               |

|----------------|--------------|-------|-----------------------------------------------------------------------------------------------------------|

| 18             | TRACEDATA[2] | Input | Input Trace data pin 2.                                                                                   |

| Not used       |              |       |                                                                                                           |

| 19             |              |       | This pin is a GND pin connected to GND in I-jet. It should also be connected to GND in the target system. |

| 20<br>Not used | TRACEDATA[3] | Input | Input Trace data pin 3.                                                                                   |

Table 3: MIPI-20 pin definitions

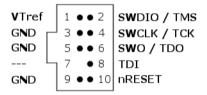

#### The JTAG/SWD - MIPI-10 cable

I-jet also comes with a 6-inch cable with a 20-pin MIPI connector on one side (to connect to I-jet) and a 10-pin MIPI connector on the other side for connection to Cortex devices with 10-pin headers. Pin 7 on each end is keyed with a white plug:

The mating connector for a target board has the part number SHF-105-01-L-D.

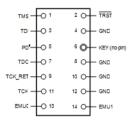

These are the MIPI-10 pin definitions:

| Pin | Signal    | Туре        | Description                                                                                                                                                                                                                                       |

|-----|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ī   | VTref     | Input       | The target reference voltage. Used by I-jet to check whether the target has power, to create the logic-level reference for the input comparators, and to control the output logic levels to the target. It is normally fed from JTAG I/O voltage. |

| 2   | SWDIO/TMS | I/O, output | JTAG mode set input of target CPU. This pin should be pulled up on the target. Typically connected to TMS of the target CPU. When using SWD, this pin is used as Serial Wire Output trace port. (Optional, not required for SWD communication)    |

| 3   | GND       | GND         | Connected to logic GND on I-jet.                                                                                                                                                                                                                  |

| 4   | SWCLK/TCK | Output      | JTAG clock signal to target CPU. It is recommended that this pin is pulled to a defined state of the target board.  Typically connected to TCK of the target CPU.                                                                                 |

Table 4: MIPI-10 pin definitions

| Pin | Signal  | Туре   | Description                                                                                                                                                                                                                                            |

|-----|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | GND     | GND    | Connected to logic GND on I-jet.                                                                                                                                                                                                                       |

| 6   | SWO/TDO | Input  | JTAG data output from target CPU. Typically connected to TDO of the target CPU.                                                                                                                                                                        |

| 7   |         | KEY    | KEY or GND.                                                                                                                                                                                                                                            |

| 8   | TDI/NC  | Output | JTAG data input of target CPU. It is recommended that this pin is pulled to a defined state on the target board. Typically connected to TDI of the target CPU. For CPUs that do not provide TDI (SWD-only devices), this pin is not used (tri-stated). |

| 9   | GND     | GND    | GND and target detect presence.                                                                                                                                                                                                                        |

| 10  | nRESET  | Output | nRESET or TRST.                                                                                                                                                                                                                                        |

Table 4: MIPI-10 pin definitions

#### **INDICATORS**

I-jet has three LED indicators on the top, marked TPWR, DBG, and USB. This section describes the indicators and their statuses.

#### The TPWR indicator (Target power)

| Indicator status | Description                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------|

| Off              | Power to target is not provided by I-jet.                                                       |

| Green            | Power to target is provided by I-jet.                                                           |

| Yellow           | Warning. Power to target is above 420 mA.                                                       |

| Red              | Error. Overcurrent limit (520 mA) detected and power to target was switched off for protection. |

Table 5: TPWR indicator statuses

#### The DBG indicator (JTAG/SWD)

| Indicator status | Description                                |

|------------------|--------------------------------------------|

| Off              | vTRef on JTAG header is too low.           |

| Green            | vTRef is at or above 1.8 V.                |

| Green blinking   | Indicates JTAG/SWD communication activity. |

Table 6: JTAG indicator statuses

#### The USB indicator

| Indicator status | Description                               |

|------------------|-------------------------------------------|

| Off              | No USB power.                             |

| Green steady     | Initial state or no transfer.             |

| Green blinking   | USB transfers to or from I-jet.           |

| Red blinking     | USB enumeration.                          |

| Red steady       | USB did not enumerate or broken hardware. |

Table 7: USB indicator statuses

#### **ADAPTERS**

There are a number of useful adapters available. All of them are automatically recognized by I-jet. The following adapters are described in detail:

- The MIPI20 isolation adapter

- The MIPI-20 to ARM-20 adapter

- The MIPI-20 to TI-14 adapter

- The MIPI-20 to cTI-20 adapter.

Adapters not included in the I-jet package can be purchased from IAR Systems.

These are the mating target headers for the adapters

| TI-14            | cTI-20                          |

|------------------|---------------------------------|

| HTST-107-01-L-DV | TML-110-02-GD-SM-006 (shrouded) |

|                  | FTR-110-51-S-D-06 (unshrouded)  |

Table 8: Mating target headers, part numbers

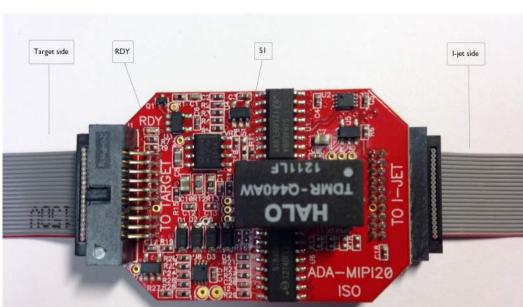

#### The ADA to MIPI20-ISO isolation adapter

The isolation adapter galvanically isolates signals between the I-jet MIPI-20 connector and the target MIPI-20 connector. You can use it to reduce the risk of damage to the I-jet debug probe associated with power ground loops, voltage spikes, electrostatic discharge (ESD), and noisy power and ground lines generated by targets which drive high-current motors and other machinery.

The adapter has two MIPI-20 headers marked **TO I-JET** and **TO TARGET**. Make sure to connect the headers correctly because switching the sides will not work and might damage the adapter. The target side of the isolation adapter can be used with any other passive I-jet adapters ID needed: ADA-MIPI20-ARM20, ADA-MIPI20-TI14, ADA-MIPI20-CTI20, and the MIPI20-MIPI10 cable.

The adapter is automatically recognized by the C-SPY, and the adapter powers up and the green RDY LED is turned on.

#### **Specifications**

- Galvanic isolation up to 3000 V peak\* (< 1 sec transients. See safety note.) with continuous working voltage operation of up to 300 V.

- Compatible with I-jet

- Supports JTAG, SWD, and SWO debug modes

- Compatible with I-jet Trace in JTAG, SWD, and SWO modes only (ETM trace is not supported)

- Powered entirely by I-jet via pins 11 and 13 on the MIPI-20 header

- The RDY LED indicates that the unit is powered and ready to use

- Supports target voltages from 2.5 to 5 V

- JTAG clock speed up to 32 MHz

#### Compatibility notes

- The adapter might not be automatically detected and powered by older versions of IAR Embedded Workbench for ARM. In such cases, select the Target Power option on the Project>Options>Debugger>I-jet/JTAGjet>Setup page.

- The adapter does not supply power to target and therefore does not resume the target power consumption.

- When used with the TI14 and CTI20 adapters, the EMU0 and EMU1 signals are not connected.

- Due to added JTAG signals propagation delays, some target boards might not work at the full 32 MHz JTAG clock speed, so reducing the JTAG speed in C-SPY might be needed.

- The majority of target boards have the SWO signal routed to pin 6 of the target MIPI20 debug connector. In cases when pin 14 is used for SWO, you must move the 0R shunt (marked S1) up from position 3-2 to position 2-1.

- The adapter does not support 1.8 V JTAG signals from target. The target JTAG voltage range is limited to 2.5-5 V.

- The JTAG interface on the target side automatically adapts to the voltage given on the target VTREF pin (2.5 V-5 V). Because of the isolation barrier, the I-jet side uses its own voltage, independent of the target voltage. This is for information only and has no effect on the target JTAG operation.

- ETM trace is not supported by this adapter.

- This adapter cannot be used with I-scope.

#### VTref 2 SWDIO/TMS GND SWCLK/TCK GND SWO/TDO TDI GND nRESET 10 GND 12 RTCK GND 14 SWO2

#### MIPI20 connector pinout on target side

For more information about the signal descriptions, see *The JTAG/SWD - MIPI-20 cable*, page 17.

nTRST

NC

NC

#### Important safety and disclaimer note

20

The continuous normal operation voltage across the isolation barrier should not exceed  $300\ V\ DC.$

The isolation voltage only represents a measure of immunity to transient voltages—the probe should never be used as an element of a safety isolation system. For use with higher continuous voltages, additional isolation/insulation systems must be used in accordance with the safety standard requirements.

Use caution and follow all safety regulations when handling equipment subjected to high voltages.

GND

GND

GND

19

Touching any exposed circuitry on the target, the adapter, cables, or the I-jet probe can cause injuries or death.

IAR Systems or the manufacturer shall not be liable for any damages related to the use of this probe.

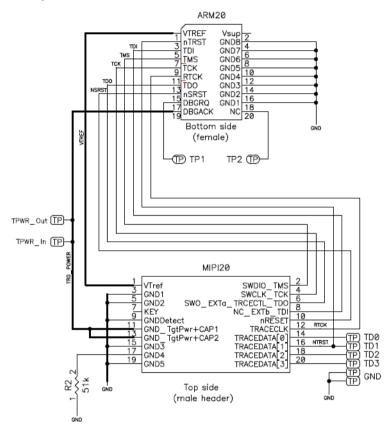

#### The MIPI-20 to ARM-20 adapter

The MIPI-20 to ARM-20 adapter is included with I-jet. It converts the MIPI-20 I-jet cable to the legacy ARM-20 (0.1 in  $\times$  0.1 in pitch) JTAG headers. This is a diagram of the adapter:

These are the pin definitions of the ARM-20 adapter:

| Pin   | I-jet<br>direction | Name             | Description                                                                   |

|-------|--------------------|------------------|-------------------------------------------------------------------------------|

| nTRST | Output             | Test Logic Reset | Test reset. Active LOW signal that resets the TAP controller's state machine. |

Table 9: ARM-20 pin definitions

| Pin   | l-jet<br>direction | Name                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|--------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK   | Output             | Test Clock                  | TCK synchronizes all JTAG transactions. TCK connects to all JTAG devices in the scan chain. TCK flows down the stack of modules and connects to each JTAG device. However, if there is a device in the scan chain that synchronizes TCK to some other clock, then all down-stream devices are connected to the RTCK signal on that processor.                                                                                                                                                                                     |

| TMS   | Output             | Test Mode Select            | TMS controls transitions in the tap controller state machine. TMS connects to all JTAG devices in the scan chain as the signal flows down the module stack.                                                                                                                                                                                                                                                                                                                                                                       |

| TDI   | Output             | Test Data Input             | TDI is the test data input signal that is routed to the TDI input of the first device in the scan chain.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TDO   | Input              | Test Data Output            | TDO is the return path of the test data input signal TDI. In a multi-device JTAG chain, the TDO of the first device connects to the TDI of the next device, etc. The last device's TDO is connected to the TDO on the JTAG header.                                                                                                                                                                                                                                                                                                |

| RTCK  | Input              | TCK Return                  | RTCK is a mechanism for returning the sampled clock to the JTAG equipment, so that the clock is not advanced until the synchronizing device captured the data. In adaptive clocking mode, I-jet is required to detect an edge on RTCK before changing TCK. In a multi-device JTAG chain, the RTCK output from a device connects to the TCK input of the down-stream device.  If there are no synchronizing devices in the scan chain, it is unnecessary to use the RTCK signal and it is connected to ground on the target board. |

| VTref | Input              | Voltage Target<br>Reference | This is the target reference voltage. It indicates that the target has power. VTref is normally fed from Vdd on the target hardware and might have a series resistor (though this is not recommended).  VTref is used by I-jet to detect if target power is active and to set JTAG signal voltage reference for level translators.                                                                                                                                                                                                |

Table 9: ARM-20 pin definitions

| Pin                   | l-jet<br>direction | Name         | Description                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nSRST                 | I/O                | System Reset | Active LOW open-collector signal that is driven by I-jet to reset the device and/or the target board. I-jet senses this line to determine when you have reset the device.                                                                                                                                                                                  |

| Vsupply               | Output             |              | This pin is not connected to I-jet.                                                                                                                                                                                                                                                                                                                        |

| DBGRQ                 | Output             |              | This pin is not connected on I-jet.                                                                                                                                                                                                                                                                                                                        |

| DBGAC<br>K/TRGP<br>WR | Output             | Target Power | This pin is used under SW control to supply 5 V power to the target board. It should be routed through a jumper shunt to the 5 V DC board input to eliminate the power adapter during debugging. The maximum current supplied by I-jet on this pin is about 420 mA. When the current supplied reaches ~500 mA, the power will be shut down for protection. |

Table 9: ARM-20 pin definitions

The R2 pull-down on pin 17 of the I-jet MIPI20 connector is a signal to I-jet that a legacy ARM-20 adapter is being used. Other adapters will have different resistors so that I-jet can identify them if needed. A solid GND on this pin means that no adapter is being used and that the MIPI cable is connected directly between the I-jet and the target board.

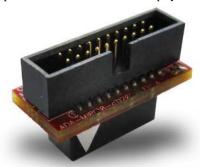

#### The ADA-MIPI20-TI14 adapter

The ADA-MIPI20-TI14 adapter converts the I-jet standard MIPI-20 cable pinout to the Texas Instruments legacy 14-pin JTAG interface used on older OMAP and other TMS320, TMS470, and TMS570 target boards.

The adapter has the MIPI-20 ale header on top for connecting the I-jet MIPI-20 cable and a TI-14-style female header (socket) on the bottom. The TI-14 JTAG header is a 14-pin, double-row, 0.1 in  $\times$  0.1 in (2.56 mm  $\times$  2.56 mm) pitch connector with a key

(plug) in position 6 to prevent misconnections. In case the plug is missing, a white arrow on pin 1 of the TI-14 connector helps you ensure proper orientation.

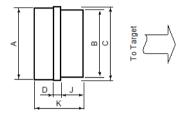

This is a diagram of the adapter:

### ADA-MIPI20-TI14

These are the pin definitions for the TI-14 adapter:

| Pin   | l-jet<br>direction | Name                | Description                                                                                                                                                                                                                            |

|-------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nTRST | Output             | Test Logic<br>Reset | Active LOW signal that causes all test and debug logic in the device to be reset along with the IEEE 1149.1 TAP.                                                                                                                       |

| TCK   | Output             | Test Clock          | This is the test clock used for driving the IEEE 1149.1 TAP state machine and logic.                                                                                                                                                   |

| TMS   | Output             | Test Mode<br>Select | Directs the next state of the IEEE 1149.1 TAP state machine.                                                                                                                                                                           |

| TDI   | Output             | Test Data Input     | IEEE 1149.1 scan data input to the device.                                                                                                                                                                                             |

| TDO   | Input              | Test Data<br>Output | IEEE 1149.1 scan data output from the device.                                                                                                                                                                                          |

| RTCK  | Input              | TCK Return          | Used only in Adaptive Clocking mode. I-jet monitors RTCK to determine when to send the next TCK.                                                                                                                                       |

| PD    | Input              | Power Detect        | Should be ties to the I/O voltage of the target device. Used by I-jet to detect whether target power is active and to set the JTAG signal voltage reference for level translators.                                                     |

| EMU0  | I/O                | Emulation 0         | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[2] pin on the MIPI20 connector. For proper booting, this pin should be pulled up on the target. |

| EMUI  | I/O                | Emulation I         | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[3] pin on the MIPI20 connector. For proper booting, this pin should be pulled up on the target. |

Table 10: Pin definitions for the TI-14 adapter

This is the pinout of the target cTI20 JTAG header. Pin 6 should be missing to indicate the proper orientation.

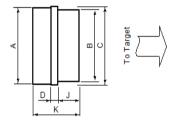

These are the top view dimensions of the ADA-MIPI20-TI14 adapter:

A 18.9 mm (0.74 in)

B 25.4 mm (1.0 in)

C 19.4 mm (0.76 in)

D 1.6 mm (0.062 in)

J 9.6 mm (0.38 in)

K 20.3 mm (0.80 in)

#### TII4 header information (for target board)

The TI14 header is manufactured by Samtec USA. The model number is TSM-17-DV. For more information, see the manufacturer's web page:

http://samtec.com/technical\_specifications/ovreview.aspx?series=TSM

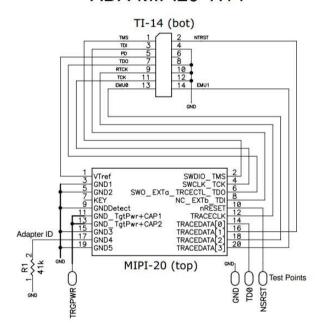

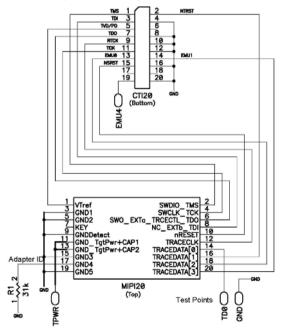

#### The ADA-MIPI20-cTI20 adapter

The ADA-MIPI20-cTI20 adapter adapts the I-jet standard MIPI-20 cable pinout to the Texas Instruments compact 20-pin JTAG interface used on some newer OMAP, DaVinci, and other TMS320, TMS470, and TMS570 target boards.

The adapter has the MIPI-20 male header on top for connecting the I-jet MIPI-20 cable, and a cTI-20 style female header (socket) on the bottom. The cTI-20 JTAG header is a 20-pin, double-row, high-density 0.05 in  $\times$  0.1 in  $(1.27 \text{ mm} \times 2.56 \text{ mm})$  pitch connector with a key (plug) in position 6 to prevent misconnections. In case the plug is missing, a white arrow on pin 1 of the cTI-20 connector helps you ensure proper orientation.

This is a diagram of the adapter:

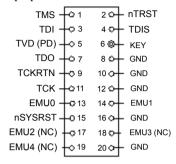

These are the pin definitions for cTI20:

| Pin    | l-jet<br>direction | Name                | Description                                                                                                                                                                                                                            |

|--------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nTRST  | Output             | Test Logic<br>Reset | Active LOW signal that causes all test and debug logic in the device to be reset along with the IEEE 1149.1 TAP.                                                                                                                       |

| TCK    | Output             | Test Clock          | This is the test clock used to drive the IEEE 1149.1 TAP state machine and logic.                                                                                                                                                      |

| TMS    | Output             | Test Mode<br>Select | Directs the next state of the IEEE 1149.1 TAP state machine.                                                                                                                                                                           |

| TDI    | Output             | Test Data<br>Input  | IEEE 1149.1 scan data input to the device.                                                                                                                                                                                             |

| TDO    | Input              | Test Data<br>Output | IEEE 1149.1 scan data output from the device.                                                                                                                                                                                          |

| RTCK   | Input              | TCK<br>Return       | Used only in Adaptive Clocking mode. I-jet monitors RTCK to determine when to send the next TCK.                                                                                                                                       |

| PD     | Input              | Power<br>Detect     | Should be tied to the I/O voltage of the target device. Used by I-jet to detect if target power is active and to set the JTAG signal voltage reference for level translators.                                                          |

| EMU0   | I/O                | Emulation 0         | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[2] pin on the MIPI20 connector. For proper booting, this pin should be pulled-up on the target. |

| EMUI   | I/O                | Emulation I         | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[3] pin on the MIPI20 connector. For proper booting, this pin should be pulled-up on the target. |

| nRESET | I/O                | System<br>Reset     | Active LOW open-collector signal that can be driven by I-jet to reset the device and/or the target board. I-jet senses this line to determine when a board has been reset by the user or by watchdog timer.                            |

Table 11: cTI20 pin definitions

This is the pinout of the target cTI20 JTAG header. Pin 6 should be missing to indicate the proper orientation.

These are the top view dimensions of the ADA-MIPI20-cTI20 adapter:

A 18.9 mm (0.74 in)

B 17.7 mm (0.7 in)

C 19.4 mm (0.76 in)

D 1.8 mm (0.07 in)

J 6.0 mm (0.24 in)

K 12.8 mm (0.50 in)

These are the side view dimensions of the ADA-MIPI20-cTI20 adapter:

G 0.5 mm (0.19 in) H 5.1 mm (0.2 in) 9.1 mm (0.36 in)

#### cTI20 header information (for target board)

Ι

The cTI20 header is manufactured by Samtec USA. The model number is FTR-110-51-S-D-06. For more information, see the manufacturer's web page http://www.samtec.com/technical\_specifications/overview.aspx?series=FTR.

# I-jet Trace

- Introduction

- Working with I-jet Trace

- Technical specifications

#### Introduction

These topics are covered:

- The I-jet Trace CM and I-jet Trace A/R/M in-circuit debugging probes

- Requirements

- Target connections.

## THE I-JET TRACE CM AND I-JET TRACE A/R/M IN-CIRCUIT DEBUGGING PROBES

I-jet Trace CM and I-jet Trace A/R/M are in-circuit debugging probes, designed to take full advantage of the speed and current delivery of the USB3 communication ports. USB 2.0 is also supported, but not recommended due to slower speed and smaller power delivery.

I-jet Trace CM and I-jet Trace A/R/M have all the features of I-jet, but with enhanced performance and ETM (Embedded Trace Macrocell) support, which allows for real-time tracing of the instruction and data over a 1-, 2- or 4-bit trace bus on Cortex-M devices.

I-jet Trace A/R/M provides extensive debug and trace functionality for ARM Cortex devices equipped with the CoreSight<sup>TM</sup> debug interface. I-jet Trace A/R/M is equipped with up to 16-bit wide trace data collection.

Hereafter, whenever I-jet Trace is mentioned in this document, both the I-jet Trace CM and the I-Jet Trace A/R/M probes are referred to, unless otherwise explicitly specified.

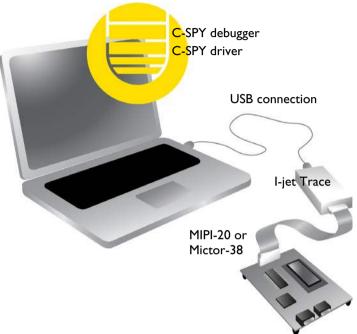

I-jet Trace CM connects to the target board via a MIPI-20 header. I-jet Trace A/R/M by default connects to target via the Mictor-38 headers, but it also supports the MIPI20 headers. The probes connect to the host computer via the USB port.

I-jet Trace streams the program counter, variables, and power measurement data to the host computer to provide a view into program execution in real time. Besides the typical JTAG debugging, I-jet Trace is capable of providing power to the target board and measuring it with sufficient accuracy to provide a power profile during program execution in real time. This feature is referred to as *power debugging*.

For debugging Cortex devices, I-jet Trace also supports the SWO (Serial Wire Output) feature, which can be used for tracing the program execution and tracking variables at predefined points in your code.

The I-jet Trace in-circuit debugging probe is also referred to as a debug probe, debug adapter, or JTAG in-circuit emulator by different tool vendors.

#### **REQUIREMENTS**

I-jet Trace needs to be controlled by the IAR C-SPY® Debugger which comes with the IAR Embedded Workbench® IDE.

## **TARGET CONNECTIONS**

These target interfaces are supported:

- MIPI-20, for up to 4-bit wide trace (part number SHF-110-01-L-D): JTAG, SWD, cJTAG, SWO, ETM

- MIPI-10 for debugging without trace (part number SHF-105-01-L-D): JTAG, SWD, cJTAG, SWO

- ARM-20 for debugging without trace (part number HTST-110-01-L-DV): JTAG, SWD, cJTAG, SWO

- Mictor-38 for up to 16-bit wide trace (I-jet Trace A/R/M only): JTAG, SWD, cJTAG, ETM, and SWO

- MIPI-60 (with trace) and TI-14/cTI-20 (without trace) connections via optional adapters

I-jet Trace CM comes with a MIPI-20 connector on the front panel and with MIPI-20 and MIPI-10 cables, as well as a legacy ARM-20 adapter.

I-jet Trace A/R/M comes with an adapter board with a Mictor-38 connector that plugs directly into the target board. For boards that do not use the high-speed Mictor connector, the pod also supports the standard MIPI-20 headers.

**Note:** Only the MIPI-20 and Mictor-38 cables support the ETM trace functionality. All other connections (MIPI-10 and ARM-20) are only for plain JTAG/SWD/SWO/cJTAG debugging.

All I-jet adapters are compatible with I-jet Trace.

# Working with I-jet Trace

These tasks are covered:

- Setup and installation

- Connecting the target system

- Using trace

- Updating the probe firmware

For information about debugging using I-jet Trace, see the C-SPY® Debugging Guide for ARM.

#### SETUP AND INSTALLATION

#### **Software**

Before you can use I-jet Trace, you need to install IAR Embedded Workbench for ARM. For more information, see the *Quick Reference Installation and Licensing* guide.

#### **Probe setup**

I-jet Trace does not require any special driver software installation. Normally, all drivers for I-jet Trace are automatically installed as part of the installation of IAR Embedded Workbench.

If you need to install the USB driver manually, navigate to

\Program Files\IAR Systems\Embedded Workbench x.x\arm\drivers\jet \USB3\32-bit or 64-bit (depending on your system). Start the dpinst.exe application. This will install the USB driver.

The USB LED will flash twice after enumerating on the USB2 ports, and three times on USB3 ports.

For information about using multiple I-jet probes on the same host computer, see the *C-SPY® Debugging Guide for ARM*.

#### **CONNECTING THE TARGET SYSTEM**

## Power-up your I-jet Trace probe

- Connect I-jet Trace to the host computer using the USB3 micro cable or any other compatible high-quality USB3 cable.

- 2 Connect I-jet Trace to the target board using the cable that matches the target board connector (MIPI-20, MIPI-10, or Mictor-38). If a standard JTAG connector is used, you must first plug the ARM-20 to MIPI-20 adapter into the JTAG connector.

Note: No harm is done if the above order is reversed.

To prevent damage, the target GND and the USB host GND must be at the same level. When *hot-plugging*, make sure that the PC and the target board power supply are connected to the same grounded wall outlet or a common grounded desktop power strip.

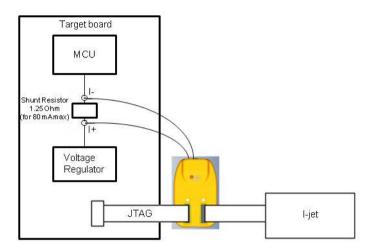

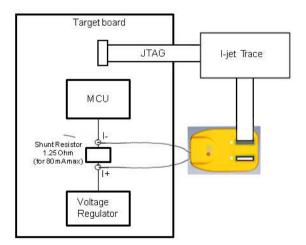

## Supplying target power from I-jet Trace

I-jet Trace can supply power to the target board only through the MIPI-20 and ARM-20 connections. The Mictor interface does not facilitate powering targets from the debug probes.

I-jet Trace CM can supply a maximum of 4.66 V at 200 mA when using USB3 ports without the need of plugging in an external 5 V DC power supply.

I-jet Trace A/R/M must use the supplied (5 V DC at 2 A) power adapter to power a target board. When it is not powering the target, I-jet Trace A/R/M does not need the external power supply as long as it is connected to the USB3 port.

## Power up your evaluation board

If you have an evaluation board that is prepared for it, you can power the board via I-jet Trace through pin 19 on the standard ARM-20 connector, or pin 11/13 on the small MIPI-20 connector. Target power of up to 400 mA can be supplied from I-jet Trace with overload protection. Most of the IAR Systems KickStart Kits contain an evaluation board that can be powered this way. Make sure that the power jumper found on most of these boards matches your setup.

**Note:** The target board will get power via I-Jet Trace once you choose the **Download** and **Debug** or **Debug without Downloading** command in C-SPY, but not before.

**Note:** The only way to use the power debugging feature is to power up your evaluation board via I-jet Trace or to use I-scope.

#### **USING TRACE**

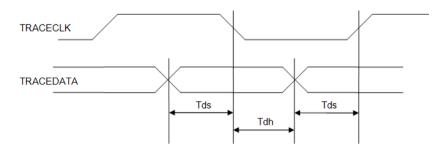

To use ETM trace, the target board must have a Cortex device with the ETM/PTM trace pins (usually named TraceCLK and TraceDxx), and these pins must be connected to the debug connector. Because on some devices, the trace pins are multiplexed, take care not to connect these pins to other logic devices on the PCB to minimize the loading and improve signal integrity.

C-SPY will initialize and enable all necessary registers on the MCU to allow the ETM port to function properly so that no special user code instrumentation is necessary. However, take care so that the running application code does not interfere (read, write, etc.) with the GPIO pins used for the ETM trace.

The TRC LED on the I-jet Trace debug probe will turn green when trace data is being collected. This usually happens after trace is enabled in C-SPY and the Run command is issued.

For more information about trace, see the C-SPY Debugging Guide.

# **UPDATING THE PROBE FIRMWARE**

For more information, see *Updating the probe firmware*, page 9.

# **Technical specifications**

Reference information about:

- The I-jet Trace package, page 40

- Model specifications, page 40

- Hardware revision history, page 42

- Connectors, page 43

- Indicators, page 45

- Adapters, page 47

- Designing target boards for ETM trace, page 51

- General PCB layout guidelines, page 51

# THE I-JET TRACE PACKAGE

The I-jet Trace package contains:

- The I-jet Trace in-circuit debugging probe

- MIPI-20 JTAG cable

- MIPI-10 JTAG cable

- USB3 A to micro-B cable

- MIPI-20 to ARM-20 adapter

- Welcome letter.

The I-jet Trace A/R/M package also contains:

• Mictor-38 adapter board attached to two 60-wire flat cables

### **MODEL SPECIFICATIONS**

These are the specifications of I-jet Trace:

USB speed 4.8 Gbps (USB 3 SuperSpeed)

480 Mbps (USB 2.0 Hi-Speed)

**USB connection** USB 3 Micro-B (USB 2.0

Micro-B-compatible)

Target connection MIPI-20 (ETM, JTAG, cJTAG, SWO, and

SWD)

MIPI-10 (JTAG and SWD)  $\,$

ARM-20 (JTAG and SWD)

Mictor-38 (I-jet Trace A/R/M only) (ETM,

JTAG, cJTAG, SWO, and SWD)

**External DC power input** 5 V DC, 2 A,  $1.3 \times 3.5$  mm

(not supplied with I-jet Trace CM)

Adapters included ADA-MIPI-20-ARM-20

**Debug interface** ETM, JTAG, cJTAG, SWO, and SWD

JTAG/SWD/cJTAG maximum clock 100 MHz

JTAG/SWD clock rise & fall time <= 2 ns

ETM maximum trace clock I-jet Trace CM: 150 MHz

**SWO protocols supported** Manchester and UART

SWO sampling frequency 200 MHz SWO maximum bandwidth 60 Mbps

ETM trace memory size I-jet Trace CM: up to 256 Mbytes

I-jet Trace A/R/M: up to 1 Gbyte

**Power supplied to target** (4.1 V-4.6 V) 400 mA max with USB 3 ports

200 mA with USB 2 ports

400 mA with ExternalDC power 600 mA (I-jet Trace A/R/M only)

Over-current protection ~420 mA with USB 3

~220 mA with USB2

~620 mA with ExternalDC power (5 V at

2 A)

Target power measurement resolution ~160 uA

**Target power measurement speed** up to 200 ksps (kilo samples per second)

JTAG/SWD/ETM voltage range 1.2 V to 5 V

Current draw from target VTref < 50 uA

**Power requirement** 3000 mW maximum (from USB or

external DC, without target)

Operating temperature 0-30 C Storage temperature 0-80 C

# I-Jet Trace A/R/M

In addition to the above model specifications, I-jet Trace A/R/M has these features:

- Support for ETMv3, ETMv4, and PTM/PFT trace and debug interfaces on any ARM Cortex-A/R/M device equipped with CoreSight

- Trace port support of up to 350 MHz double data rate (DDR) (700 Msamples/s for each trace data line) for a total of 11.2 Gbit/s throughput

- Support for streaming of trace data at up to 3.2 Gbytes/s

- Automatic alignment of parallel trace data skew on individual bits to compensate for PCB layout and signal integrity problems

- Automatic trace data and clock voltage threshold adjustments to get the most reliable trace data collection with noisy or un-terminated target boards

- 64-bit timestamp with 5 ns resolution (or CPU cycle accurate) for precise timing analysis

- No external power adapter needed when powering target boards that take less than 200 mA

#### HARDWARE REVISION HISTORY

These are the versions of I-jet Trace CM:

| Version    | Change specification                                                                     | Date       |

|------------|------------------------------------------------------------------------------------------|------------|

| Version A  | IAR internal version                                                                     | 03/24/2014 |

| Version B  | Production version                                                                       | 05/26/2014 |

| Version C  | Added 100k pull-up on nSRST                                                              | 11/26/2014 |

| Version CI | Increased voltage level on JTAG output pins for better compatibility with 5 V devices $$ | 05/15/2015 |

Table 12: I-jet Trace CM versions

These are the versions of I-jet Trace A/R/M:

| Version   | Change specification                     | Date       |

|-----------|------------------------------------------|------------|

| Version A | Production version                       | 12/15/2015 |

| Version B | No functional changes (PCB changes only) | 02/04/2016 |

Table 13: I-jet Trace A/R/M versions

Version, production date, and serial number can be found on the backside of the probe.

Note: In IAR Embedded Workbench, choose I-jet/JTAGjet>EmuDiag to open the EmuDiag dialog box where you can find both hardware and firmware versions of the plugged-in I-jet.

#### **CONNECTORS**

# **External power**

I-jet Trace has a small (1.35 mm  $\times$  3.5 mm) external power connector right next to the USB connector. It can be used whenever the host computer is unable to deliver the necessary power to I-jet Trace and to the target board. The external power supply must deliver 5 V DC at 1 A minimum for I-jet Trace CM and 2 A minimum for I-jet Trace A/R/M.

When external power is connected, almost the entire power will be taken from the external power supply, allowing more power-consuming targets (up to 600 mA) to be powered by I-jet Trace.

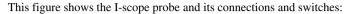

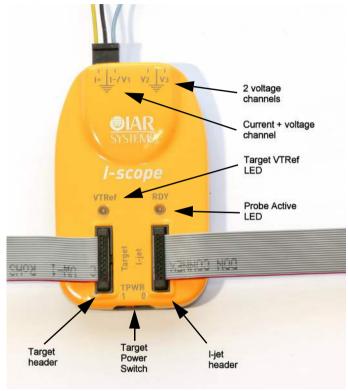

## **I-scope connector**

The I-scope connector on the side of the probe is provided for connecting the I-scope analog probe to the I-jet Trace. Unlike I-jet, I-scope cannot be connected to the same MIPI-20 connector that is used for target boards. When I-scope is connected to I-jet Trace, the Target connector on I-scope cannot be used.

#### **Expansion connector**

This 30-pin connector is reserved for future use to add more functionality and features to I-jet Trace.

#### **Target connector**

I-jet Trace CM comes with a MIPI-20 connector that allows a standard 20-pin flat cable (included) to connect to a target with a MIPI-20 male header. This target connection allows for JTAG/SWD/cJTAG debugging as well as 1-, 2-, or 4-bit ETM or SWO trace.

The MIPI-20 pinout for I-jet Trace CM is the same as for I-jet.

I-jet Trace A/R/M comes with two 60-pin flat cables that terminate in an adapter board with a Mictor-38 male connector that is designed to plug in directly into the target board.

The Mictor connector allows for JTAG/SWD/cJTAG/SWO debugging as well as for up to 16-bit wide ETM trace.

The adapter board also contains a standard MIPI-20 header for connecting to target boards without the Mictor connection.

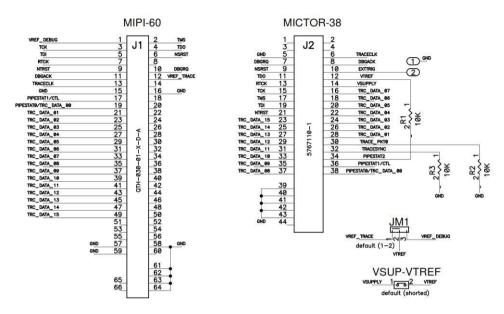

This is the Mictor-38 pinout for I-jet Trace A/R/M:

| Signal        | Pin | Pin | Signal             |

|---------------|-----|-----|--------------------|

|               | I   | 2   |                    |

|               | 3   | 4   |                    |

| GND           | 5   | 6   | TRACECLK           |

| TRIGIN        | 7   | 8   | TRIGOUT            |

| nSRST         | 9   | 10  | EXTTRIG            |

| TDO           | П   | 12  | VTREF              |

| RTCK          | 13  | 14  | VSUPPLY (not used) |

| TCK           | 15  | 16  | TRACEDATA[07]      |

| TMS           | 17  | 18  | TRACEDATA[06]      |

| TDI           | 19  | 20  | TRACEDATA[05]      |

| nTRST         | 21  | 22  | TRACEDATA[04]      |

| TRACEDATA[15] | 23  | 24  | TRACEDATA[03]      |

| TRACEDATA[14] | 25  | 26  | TRACEDATA[02]      |

| TRACEDATA[13] | 27  | 28  | TRACEDATA[01]      |

| TRACEDATA[12] | 29  | 30  |                    |

| TRACEDATA[II] | 31  | 32  |                    |

| TRACEDATA[10] | 33  | 34  |                    |

| TRACEDATA[09] | 35  | 36  | TRACECTL           |

| TRACEDATA[08] | 37  | 38  | TRACEDATA[00]      |

Table 14: The Mictor-38 pinout for I-jet Trace A/R/M

The mating connector for Mictor-38 on target board is AMP/Tyco 5767054-1.

# **INDICATORS**

I-jet Trace has four LED indicators on the top, marked TRC, TPWR, DBG, and USB. This section describes the indicators and their statuses.

# The TRC indicator

| Indicator status | Description                                                          |

|------------------|----------------------------------------------------------------------|

| Off              | No trace.                                                            |

| Green            | Collecting trace data and trace clock is present.                    |

| Red              | Trace data collection is enabled but the trace clock is not present. |

| Orange blinking  | Collecting SWO trace data.                                           |

Table 15: TRC indicator statuses

# The TPWR indicator (Target power)

| Indicator status | Description                                                 |

|------------------|-------------------------------------------------------------|

| Off              | Power to target is not provided by I-jet.                   |

| Green            | Power to target is provided by I-jet.                       |

| Yellow           | Warning. Power to target is close to the overcurrent limit. |

Table 16: TPWR indicator statuses

| Indicator status | Description                                                            |

|------------------|------------------------------------------------------------------------|

| Red              | Error. Overcurrent limit detected and power to target was switched off |

|                  | for protection.                                                        |

Table 16: TPWR indicator statuses

# The DBG indicator (JTAG/SWD/cJTAG)

| Indicator status | Description                                                     |

|------------------|-----------------------------------------------------------------|

| Off              | vTRef on JTAG header is too low.                                |

| Green            | vTRef is at or above 1.2 V.                                     |

| Green blinking   | Indicates JTAG/cJTAG/SWD communication activity from the target |

Table 17: JTAG indicator statuses

#### The USB indicator

| Indicator status | Description                                      |

|------------------|--------------------------------------------------|

| Off              | No USB power.                                    |

| Green steady     | Initial state or no transfer.                    |

| Green blinking   | USB transfers to or from I-jet Trace.            |

| Red blinking     | USB enumeration.                                 |

| Red steady       | USB did not enumerate or the hardware is broken. |

Table 18: USB indicator statuses

# **ADAPTERS**

# **ADA-MIPI20-MICTOR adapter**

The ADA-MIPI20-MICTOR adapter coverts the I-jet Trace CM standard MIPI-20 cable pinout to the high-speed Mictor 38-pin trace connector used on some target boards.

The adapter has the MIPI-20 male header on top for connecting the I-jet Trace CM MIPI-20 cable and the Mictor-style male header that straddles the edge of the PCB. This Mictor connector (AMP/Tyco 576006-1) mates with target boards with a female Mictor

$(AMP/Tyco\ 5767054-1)$  connector). These connectors are keyed to prevent incorrect insertion.

| Signal | Pin | Pin | Signal   |

|--------|-----|-----|----------|

|        | I   | 2   |          |

|        | 3   | 4   |          |

| GND    | 5   | 6   | TRACECLK |

|        | 7   | 8   |          |

| nSRST  | 9   | 10  |          |

Table 19: ADA-MIPI20-MICTOR adapter pinout

| Signal     | Pin | Pin | Signal  |

|------------|-----|-----|---------|

| TDO        | П   | 12  | VTREF   |

| RTCK*      | 13  | 14  | VSUPPLY |

| TCK        | 15  | 16  |         |

| TMS        | 17  | 18  |         |

| TDI        | 19  | 20  |         |

| $nTSRST^*$ | 21  | 22  |         |

|            | 23  | 24  | TD[3]   |

|            | 25  | 26  | TD[2]   |

|            | 27  | 28  | TD[I]   |

|            | 29  | 30  |         |

|            | 31  | 32  |         |

|            | 33  | 34  |         |

|            | 35  | 36  |         |

|            | 37  | 38  | TD[0]   |

Table 19: ADA-MIPI20-MICTOR adapter pinout

# **ADA-MICTOR-MIPI60** adapter

The ADA-MICTOR-MIPI60 adapter converts the I-jet Trace A/R/M standard Mictor-38 pinout to the MIPI-60 trace connector used on some target boards.

The adapter has the Mictor-38 female connector on top for connecting the I-jet Trace A/R/M and the MIPI-60-style male header on the bottom.

This MIPI-60 connector (Samtec QTH-030-01-F-DA) mates with target boards with a female MIPI-60 connector (Samtec QSH-030-01-F-DA). These connectors are keyed to prevent incorrect insertion.

<sup>\*</sup> The function of these pins are determined by the jumpers on the adapter.

| Signal        | Pin | Pin | Signal     |

|---------------|-----|-----|------------|

| VREF DEBUG    | I   | 2   | TMS        |

| TCK           | 3   | 4   | TDO        |

| TDI           | 5   | 6   | nSRST      |

| RTCK          | 7   | 8   |            |

| nTRST         | 9   | 10  | DBGRQ      |

| DBGACK        | 11  | 12  | VREF TRACE |

| TRACECLK      | 13  | 14  |            |

| GND           | 15  | 16  | GND        |

| TRACECTL      | 17  | 18  |            |

| TRACEDATA[00] | 19  | 20  |            |

| TRACEDATA[01] | 21  | 22  |            |

| TRACEDATA[02] | 23  | 24  |            |

| TRACEDATA[03] | 25  | 26  |            |