# ProASIC3L FPGA Fabric User's Guide

# **Table of Contents**

|   | Introduction                                                                  |      |

|---|-------------------------------------------------------------------------------|------|

|   | Contents                                                                      | 7    |

|   | Revision History                                                              | 7    |

|   | Related Information                                                           | 7    |

|   |                                                                               |      |

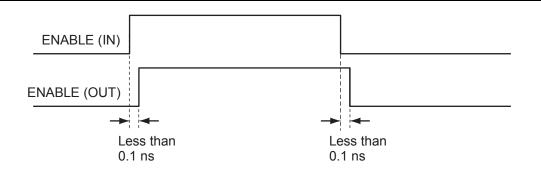

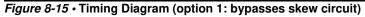

| 1 | FPGA Array Architecture in Low Power Flash Devices                            | . 9  |

|   | Device Architecture                                                           | 9    |

|   | FPGA Array Architecture Support                                               | . 10 |

|   | Device Overview                                                               | . 11 |

|   | Related Documents                                                             | . 20 |

|   | List of Changes                                                               | . 20 |

|   |                                                                               |      |

| 2 | Flash*Freeze Technology and Low Power Modes                                   | 21   |

|   | Flash*Freeze Technology and Low Power Modes                                   | . 21 |

|   | Flash Families Support the Flash*Freeze Feature                               | . 22 |

|   | Low Power Modes Overview                                                      | . 23 |

|   | Static (Idle) Mode                                                            | . 23 |

|   | Flash*Freeze Mode                                                             | . 24 |

|   | Sleep and Shutdown Modes                                                      | . 32 |

|   | Flash*Freeze Design Guide                                                     | . 34 |

|   | Conclusion                                                                    | . 42 |

|   | Related Documents                                                             | . 42 |

|   | List of Changes                                                               | . 42 |

|   |                                                                               |      |

| 3 | Global Resources in Low Power Flash Devices.                                  |      |

|   | Introduction                                                                  | . 47 |

|   | Global Architecture                                                           | . 47 |

|   | Global Resource Support in Flash-Based Devices                                | . 48 |

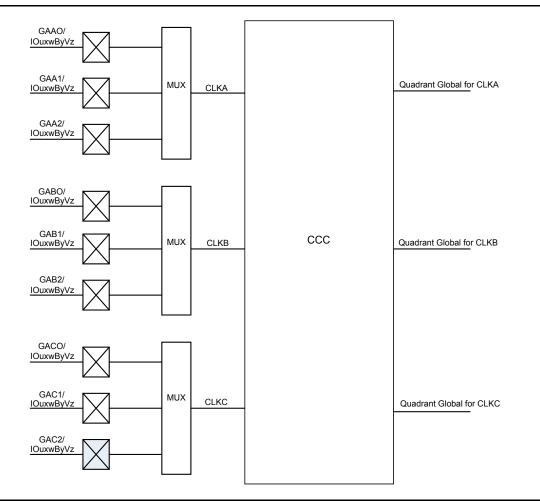

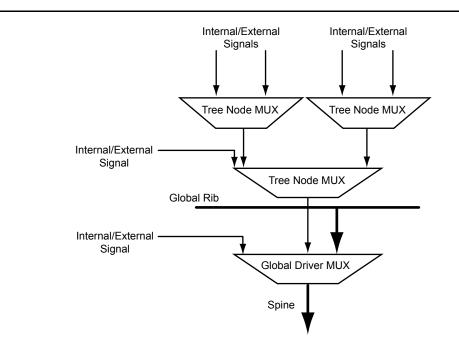

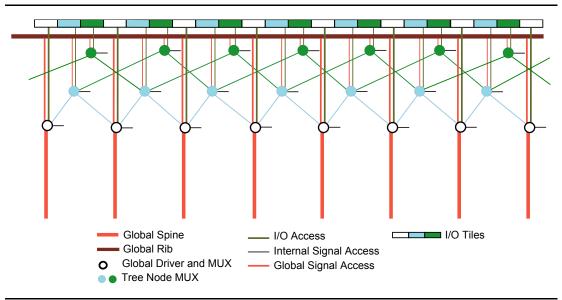

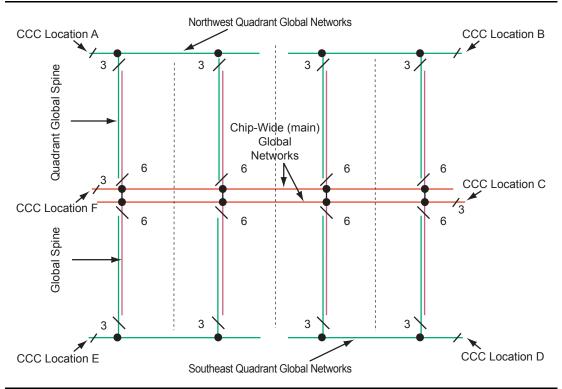

|   | VersaNet Global Network Distribution                                          | . 49 |

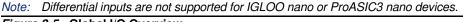

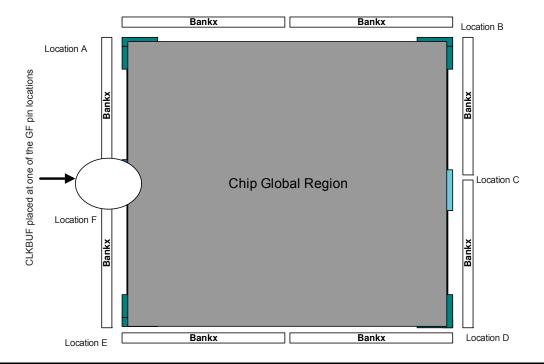

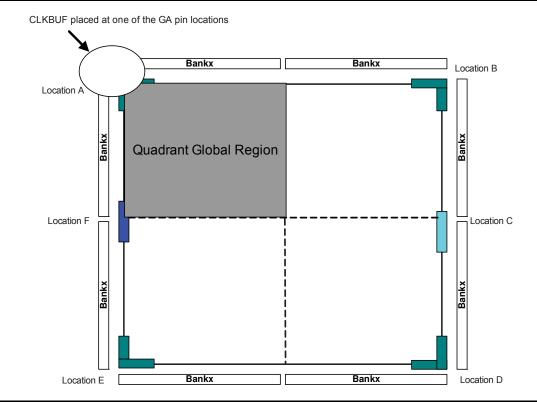

|   | Chip and Quadrant Global I/Os                                                 | . 51 |

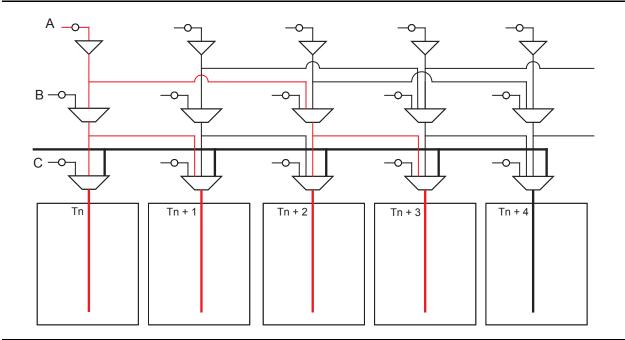

|   | Spine Architecture                                                            | . 57 |

|   | Using Clock Aggregation                                                       | . 60 |

|   | Design Recommendations                                                        | . 62 |

|   | Conclusion                                                                    | . 74 |

|   | Related Documents                                                             | . 74 |

|   | List of Changes                                                               | . 75 |

|   |                                                                               |      |

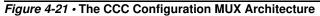

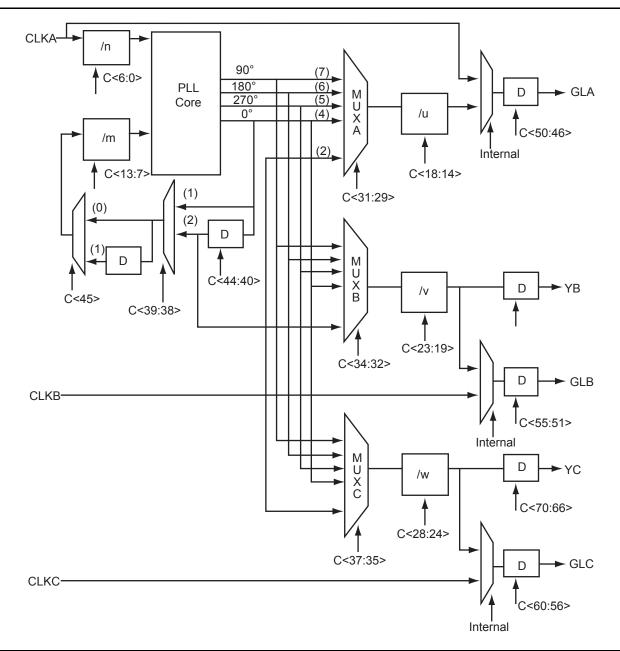

| 4 | Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs | 77   |

|   | Introduction                                                                  | . 77 |

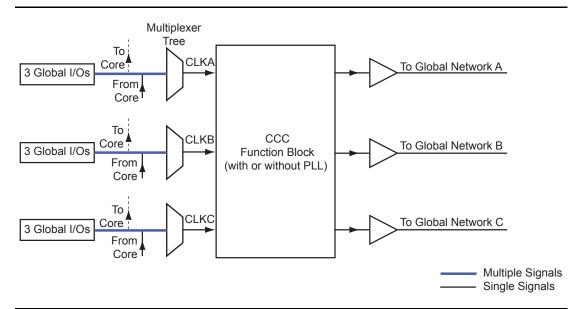

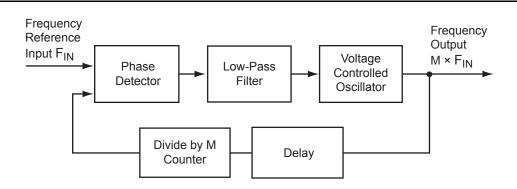

|   | Overview of Clock Conditioning Circuitry                                      | . 77 |

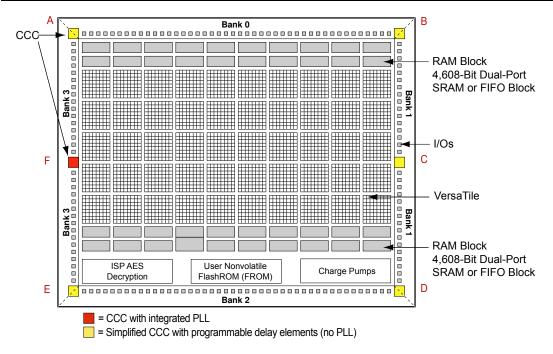

|   | CCC Support in Microsemi's Flash Devices                                      | . 79 |

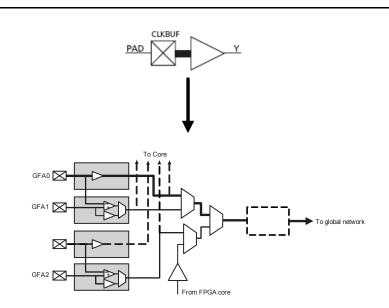

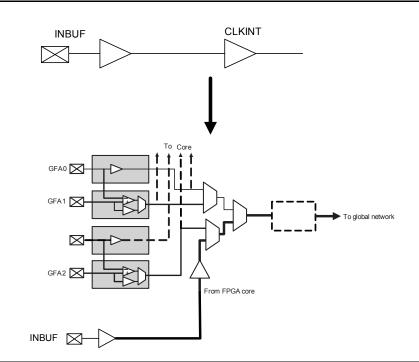

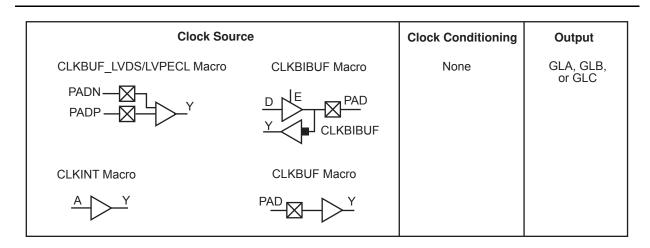

|   | Global Buffers with No Programmable Delays                                    | . 80 |

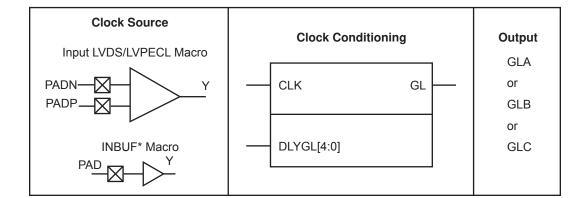

|   | Global Buffer with Programmable Delay                                         | . 80 |

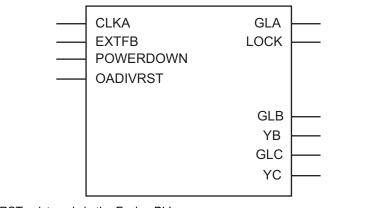

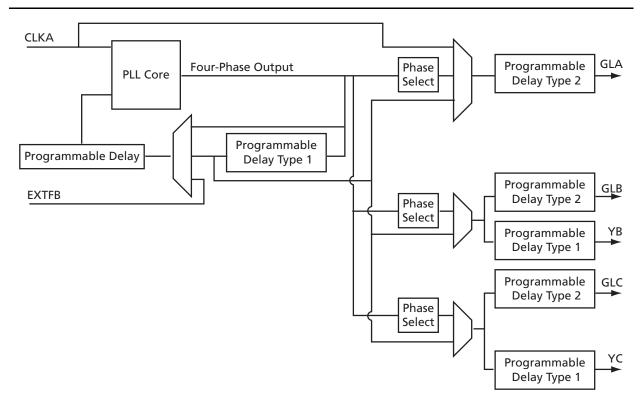

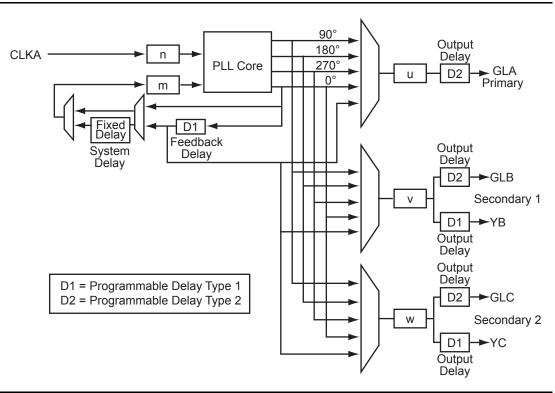

|   | Global Buffers with PLL Function                                              | . 83 |

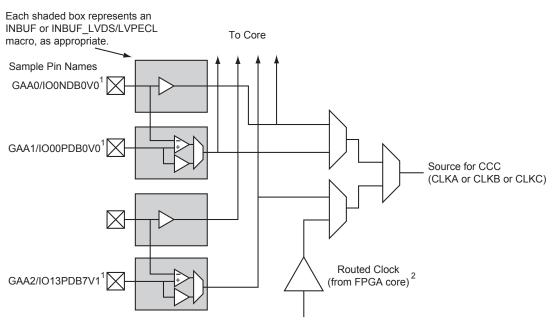

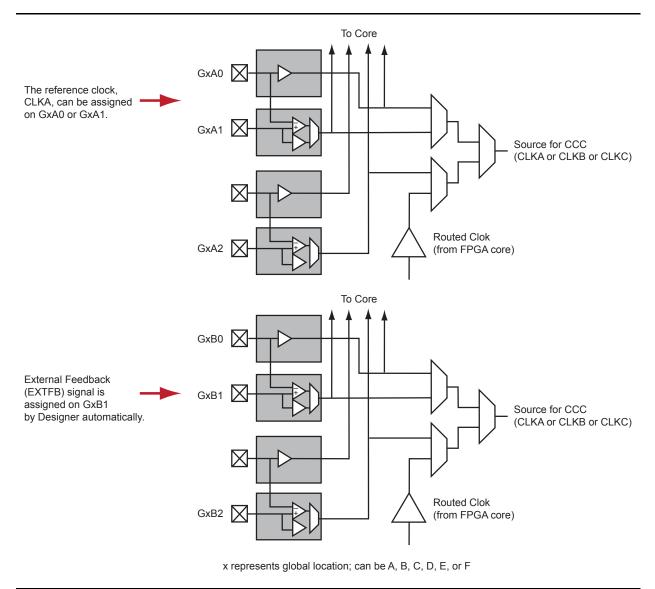

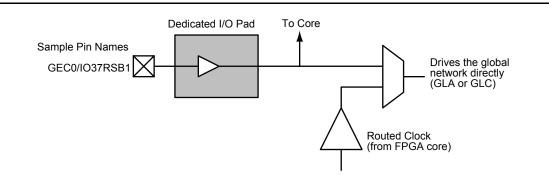

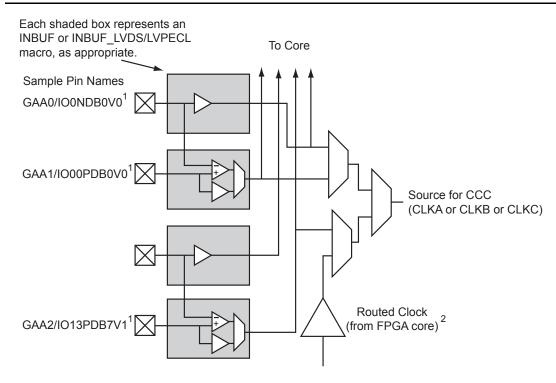

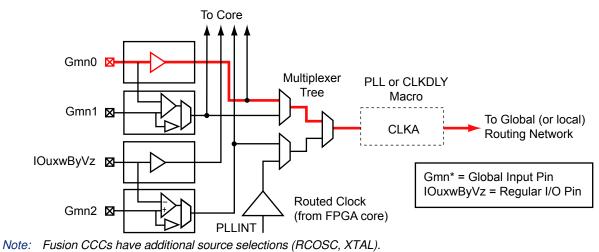

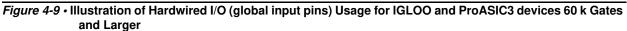

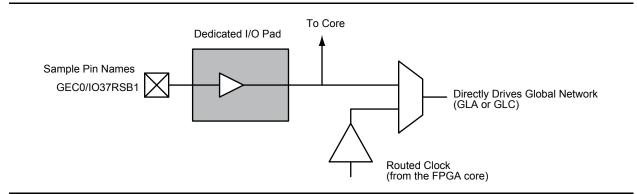

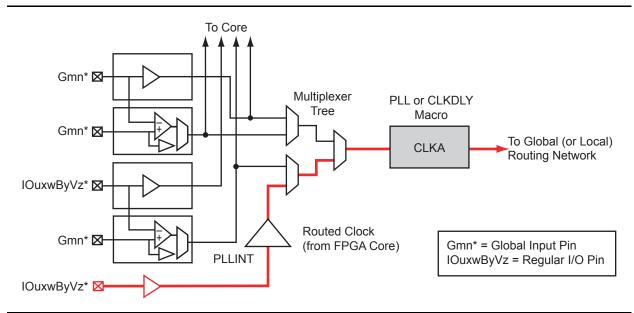

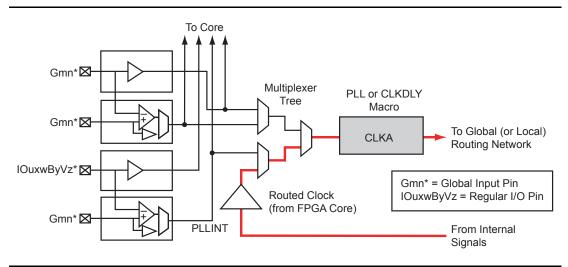

|   | Global Input Selections                                                       | . 87 |

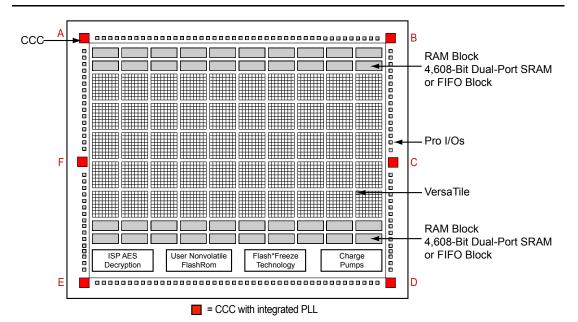

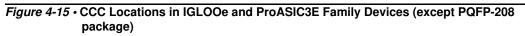

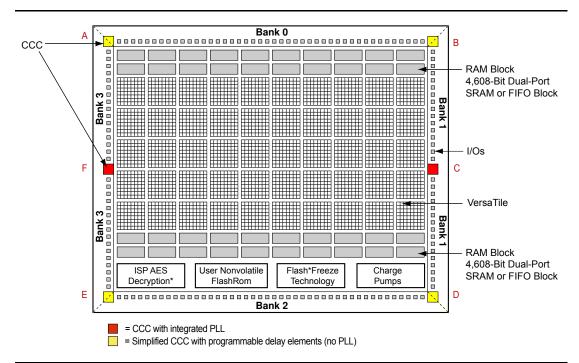

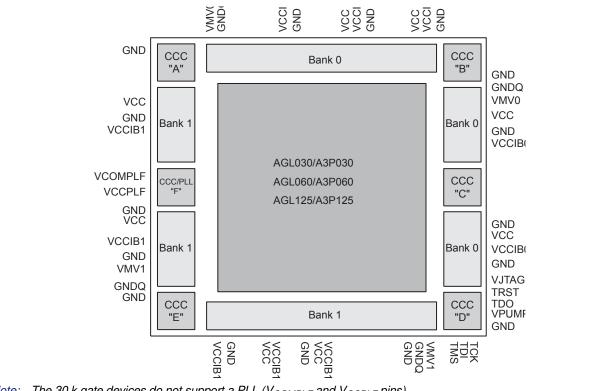

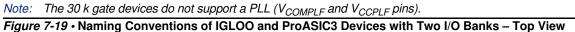

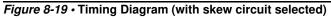

|   | Device-Specific Layout                                                   | 94  |

|---|--------------------------------------------------------------------------|-----|

|   | PLL Core Specifications                                                  | 100 |

|   | Functional Description                                                   | 101 |

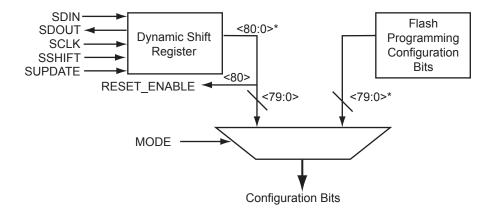

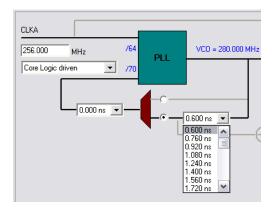

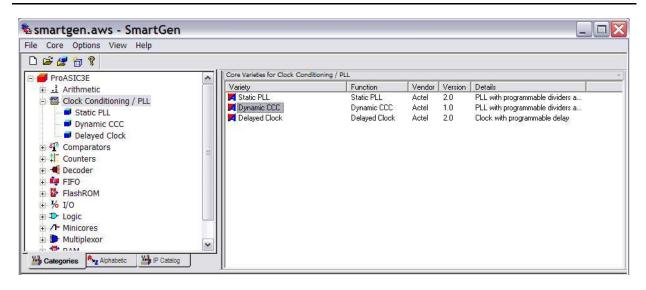

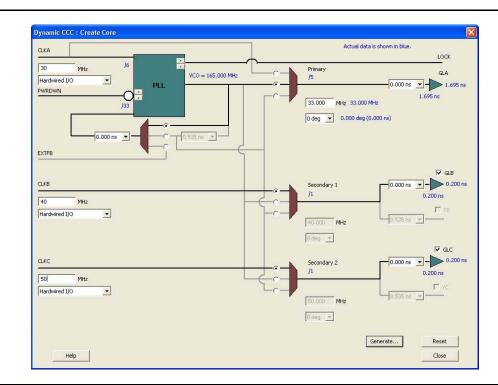

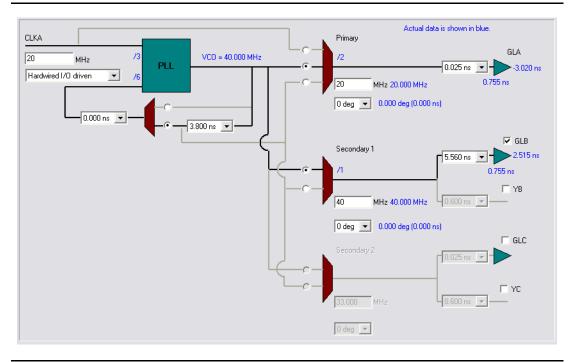

|   | Software Configuration                                                   |     |

|   | Detailed Usage Information                                               |     |

|   | Recommended Board-Level Considerations                                   |     |

|   | Conclusion                                                               |     |

|   | Related Documents                                                        |     |

|   | List of Changes                                                          | 129 |

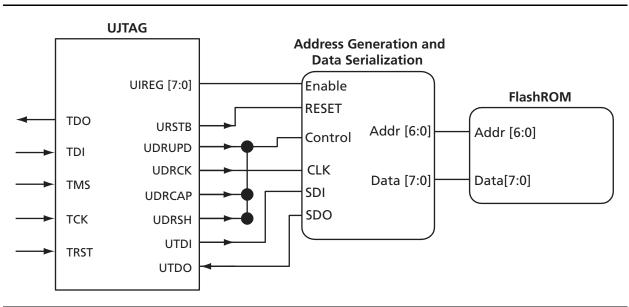

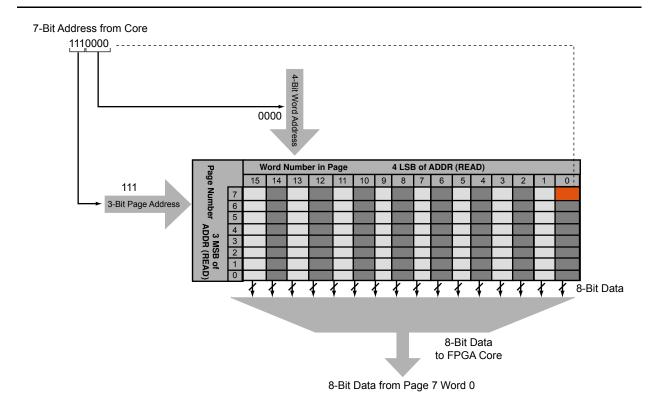

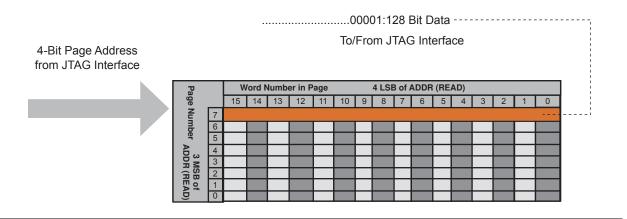

| 5 | FlashROM in Microsemi's Low Power Flash Devices                          | 133 |

|   | Introduction                                                             |     |

|   | Architecture of User Nonvolatile FlashROM                                |     |

|   | FlashROM Support in Flash-Based Devices                                  |     |

|   | FlashROM Applications                                                    |     |

|   | FlashROM Security                                                        |     |

|   | Programming and Accessing FlashROM                                       |     |

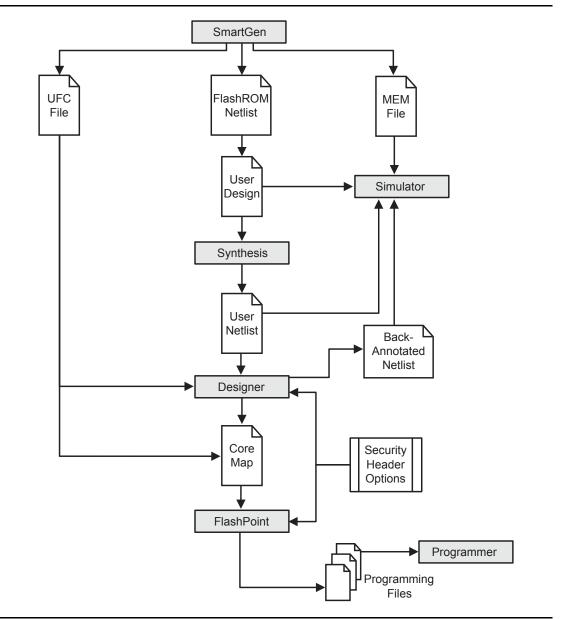

|   | FlashROM Design Flow                                                     |     |

|   | Custom Serialization Using FlashROM                                      |     |

|   | Conclusion                                                               | 146 |

|   | Related Documents                                                        | 146 |

|   | List of Changes                                                          | 146 |

|   |                                                                          |     |

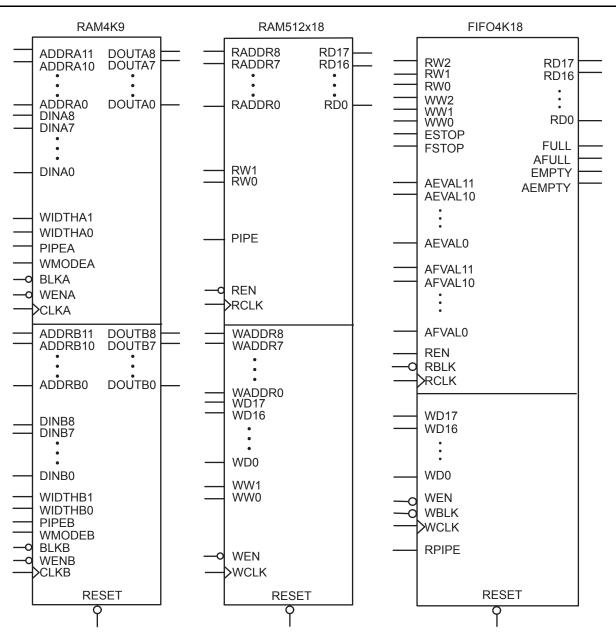

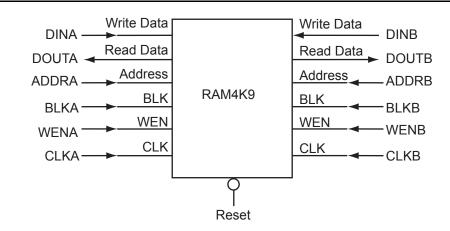

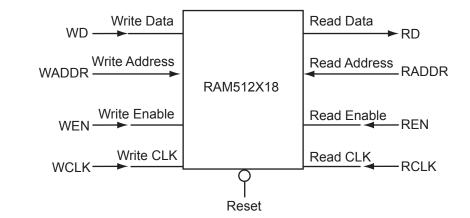

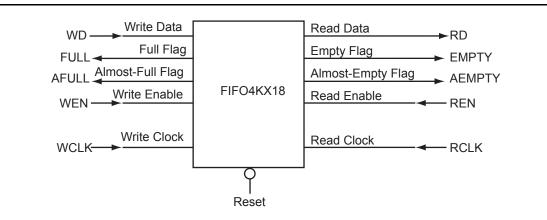

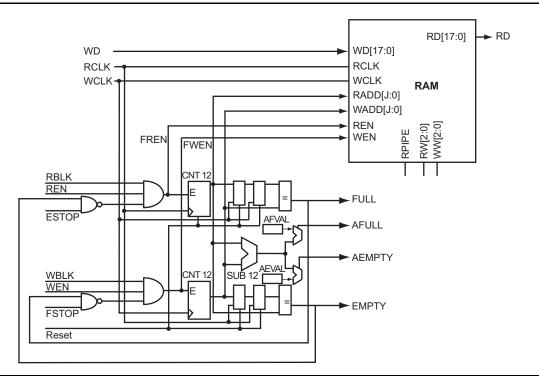

| 6 | SRAM and FIFO Memories in Microsemi's Low Power Flash Devices            |     |

|   |                                                                          |     |

|   | Device Architecture                                                      |     |

|   | SRAM/FIFO Support in Flash-Based Devices                                 |     |

|   | SRAM and FIFO Architecture                                               |     |

|   | Memory Blocks and Macros                                                 |     |

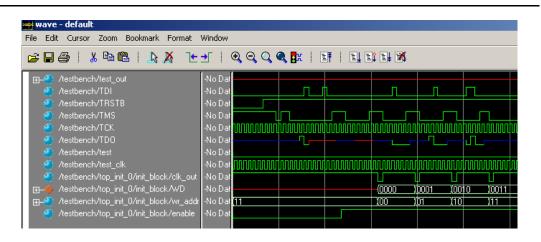

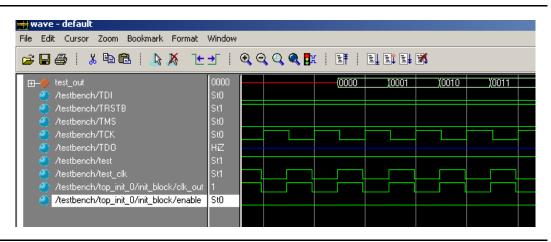

|   | Initializing the RAM/FIFO                                                |     |

|   | Software Support                                                         |     |

|   | Conclusion                                                               |     |

|   | List of Changes                                                          | 173 |

| 7 | I/O Structures in IGLOO and ProASIC3 Devices                             | 175 |

|   | Introduction                                                             | 175 |

|   | Low Power Flash Device I/O Support                                       |     |

|   | Advanced I/Os—IGLOO, ProASIC3L, and ProASIC3                             | 177 |

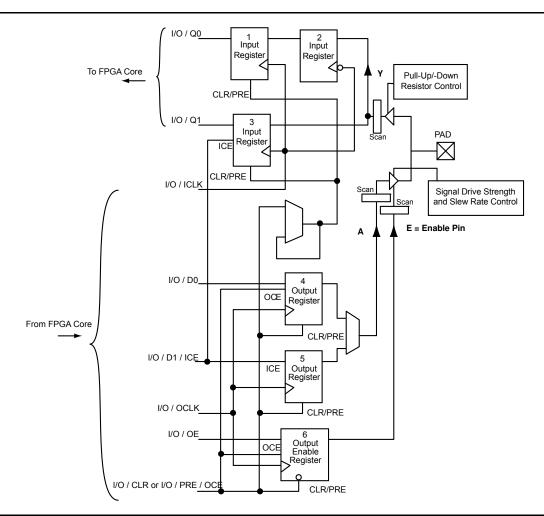

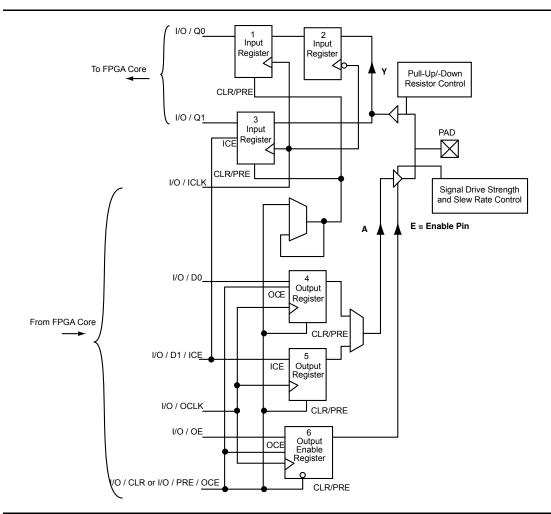

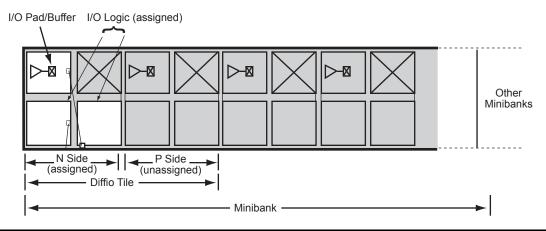

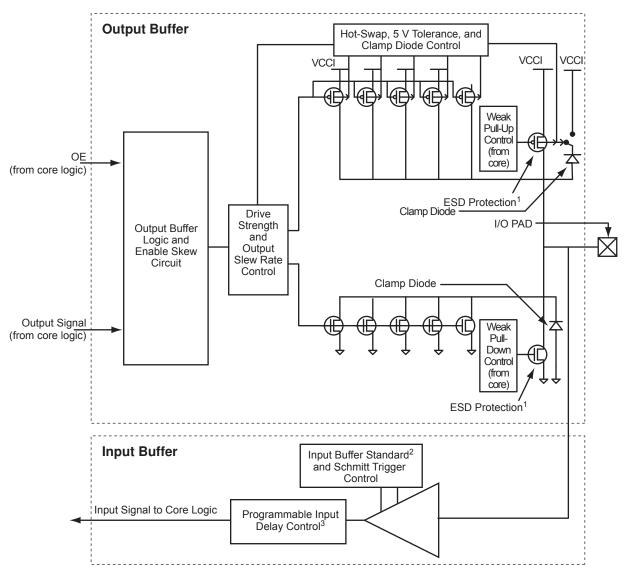

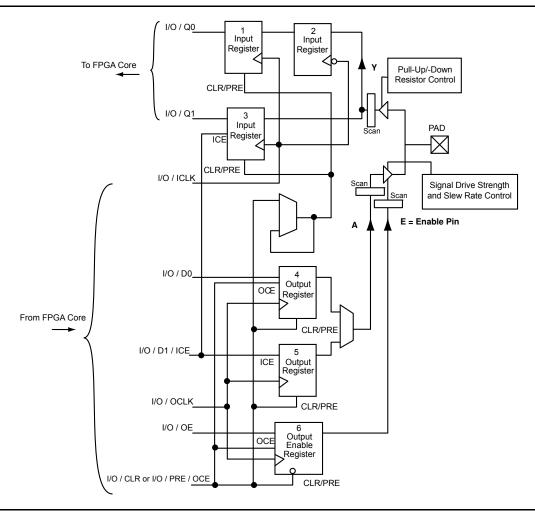

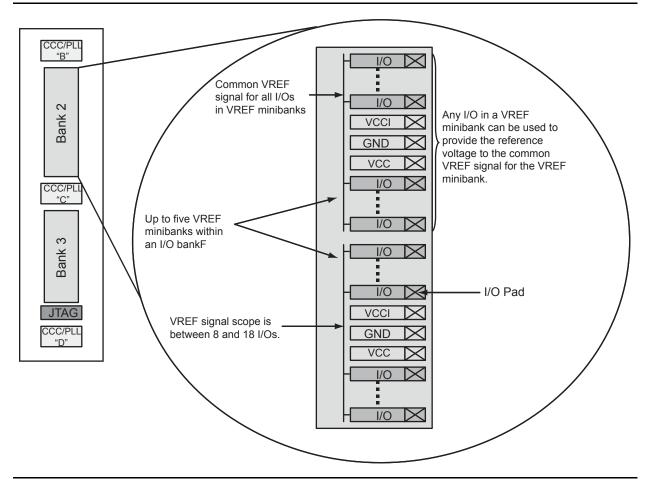

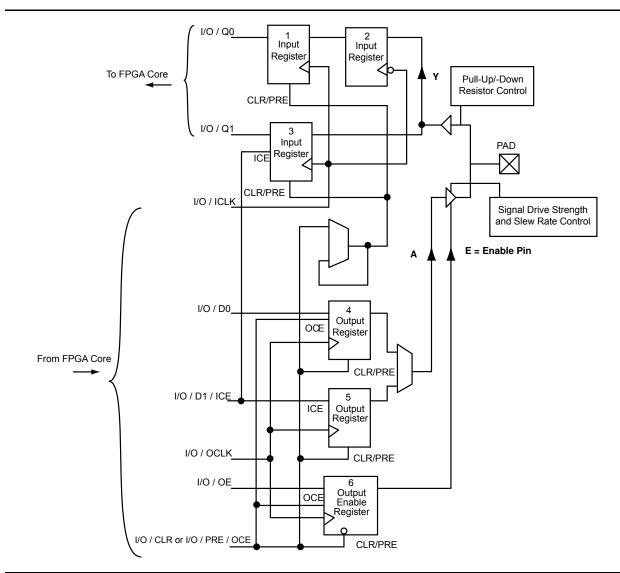

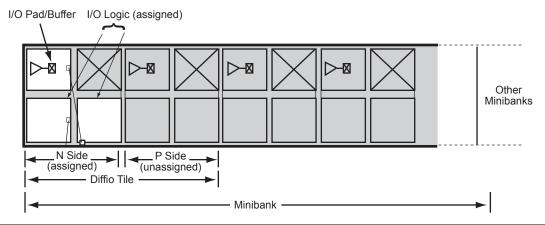

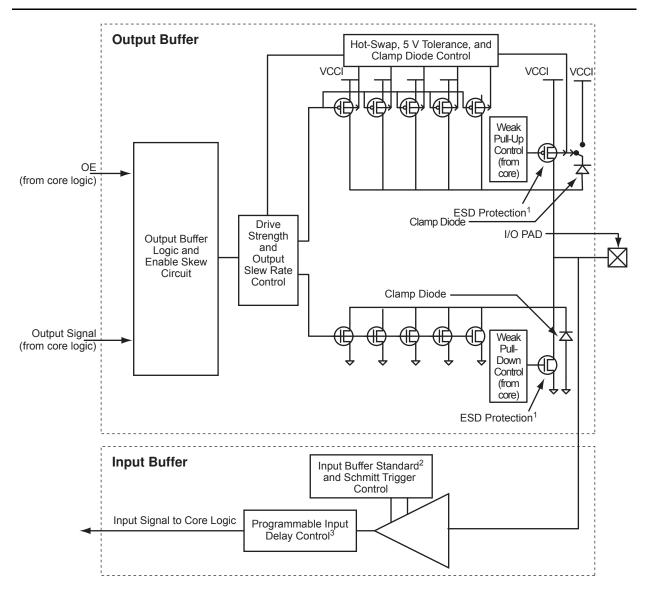

|   | I/O Architecture                                                         | 181 |

|   | I/O Standards                                                            | 184 |

|   | I/O Features                                                             | 188 |

|   | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout | 204 |

|   | I/O Software Support                                                     | 205 |

|   | User I/O Naming Convention                                               |     |

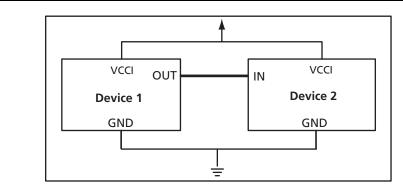

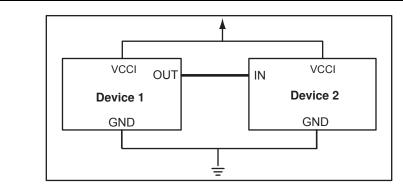

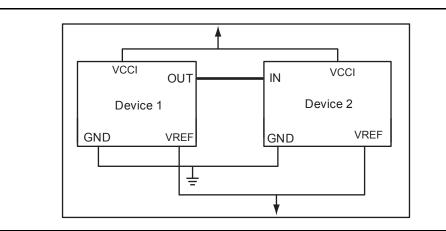

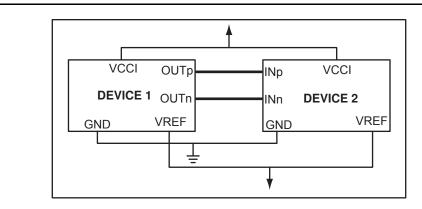

|   | Board-Level Considerations                                               |     |

|   | Conclusion                                                               |     |

|   | Related Documents                                                        |     |

|   | List of Changes                                                          | 210 |

| 8 | I/O Structures in IGLOOe and ProASIC3E Devices                           | 213 |

|    | Introduction                                                             | . 213 |

|----|--------------------------------------------------------------------------|-------|

|    | Low Power Flash Device I/O Support                                       | . 214 |

|    | Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E                               | . 215 |

|    | I/O Architecture                                                         | . 220 |

|    | I/O Standards                                                            | . 223 |

|    | I/O Features                                                             |       |

|    | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout | 241   |

|    | I/O Software Support                                                     |       |

|    | User I/O Naming Convention                                               |       |

|    | Board-Level Considerations                                               |       |

|    | Conclusion                                                               |       |

|    | Related Documents                                                        | -     |

|    | List of Changes                                                          |       |

|    |                                                                          | . 273 |

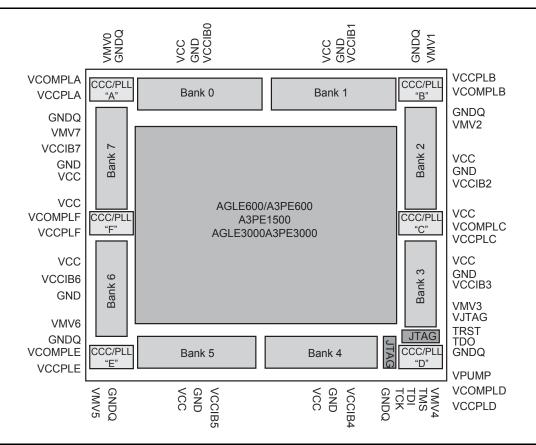

| 9  | I/O Software Control in Low Power Flash Devices                          | 251   |

|    | Flash FPGAs I/O Support                                                  |       |

|    | Software-Controlled I/O Attributes                                       |       |

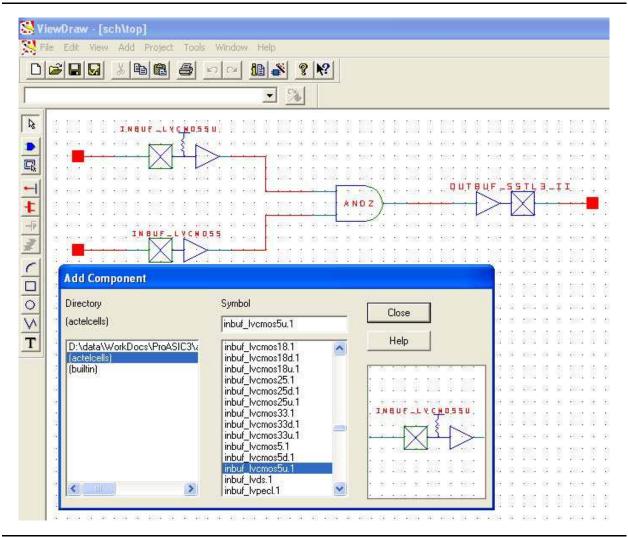

|    | Implementing I/Os in Microsemi Software                                  |       |

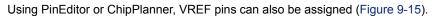

|    | Assigning Technologies and VREF to I/O Banks                             |       |

|    | Conclusion                                                               |       |

|    | Related Documents                                                        |       |

|    | List of Changes                                                          |       |

|    |                                                                          | . 270 |

| 10 | DDR for Microsemi's Low Power Flash Devices                              | 271   |

|    | Introduction                                                             |       |

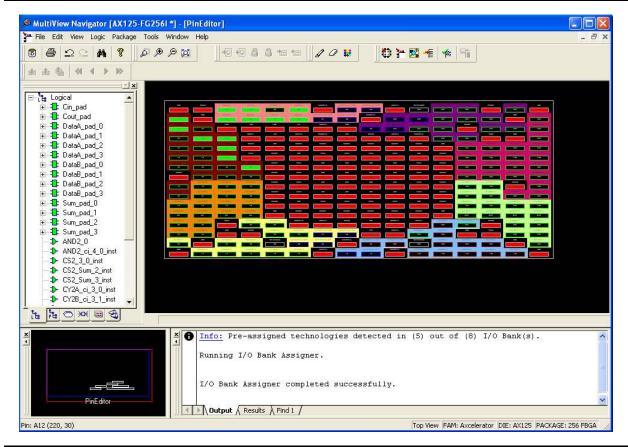

|    | Double Data Rate (DDR) Architecture                                      |       |

|    | DDR Support in Flash-Based Devices                                       |       |

|    | I/O Cell Architecture                                                    |       |

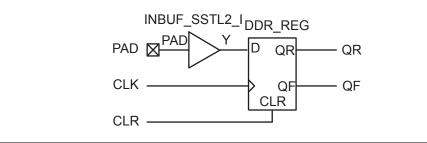

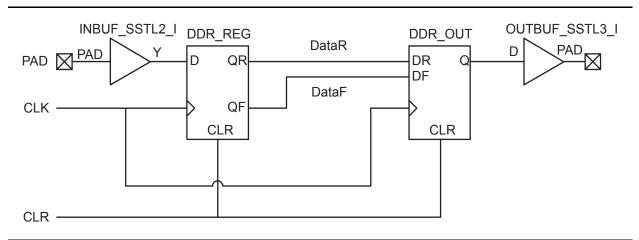

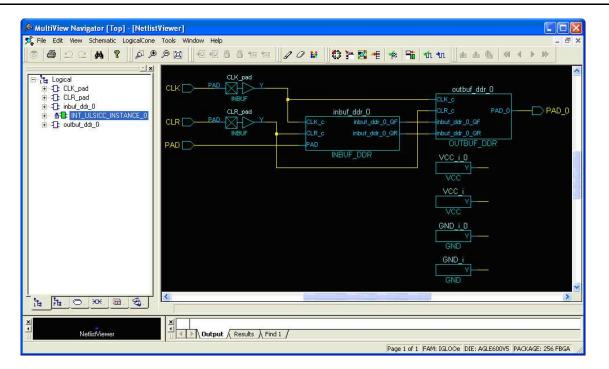

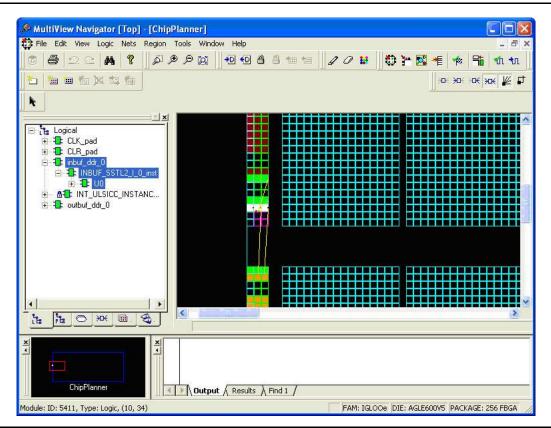

|    | Input Support for DDR                                                    |       |

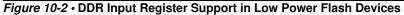

|    | Output Support for DDR                                                   |       |

|    |                                                                          |       |

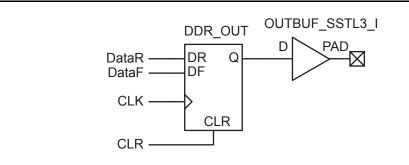

|    | Instantiating DDR Registers                                              |       |

|    | Design Example                                                           |       |

|    | Conclusion                                                               |       |

|    | List of Changes                                                          | . 285 |

| 11 | Programming Flash Devices                                                | 287   |

|    | Introduction                                                             |       |

|    |                                                                          |       |

|    | Summary of Programming Support                                           |       |

|    | Programming Support in Flash Devices                                     |       |

|    | General Flash Programming Information                                    |       |

|    | Important Programming Guidelines                                         |       |

|    | Related Documents                                                        |       |

|    | List of Changes                                                          | . 298 |

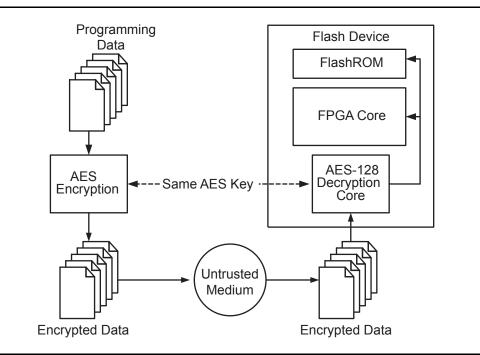

| 12 | Security in Low Power Flash Devices                                      | 301   |

| 14 | Security in Programmable Logic                                           |       |

|    | Security Support in Flash-Based Devices                                  |       |

|    | Security Support in Flash-based Devices                                  |       |

|    | •                                                                        |       |

|    | Security Features                                                        |       |

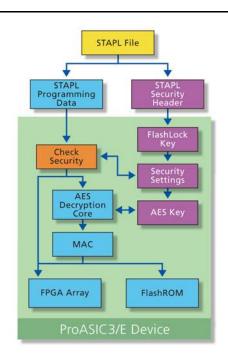

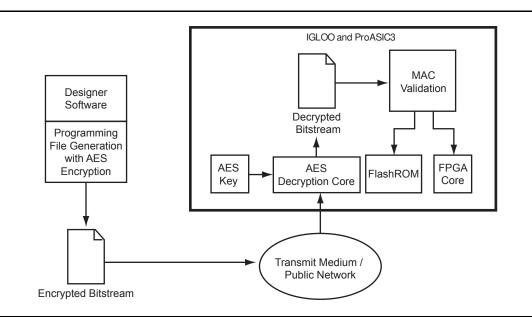

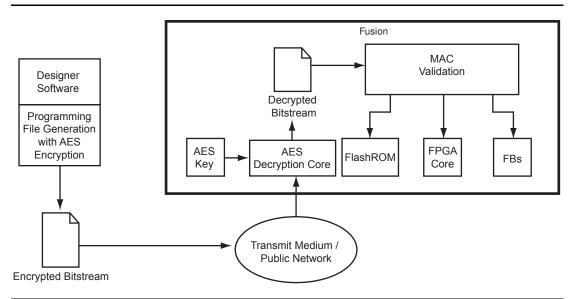

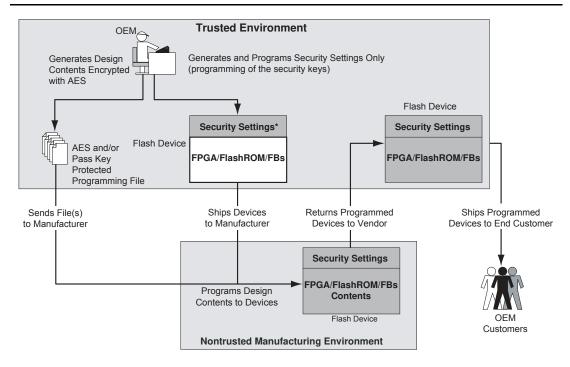

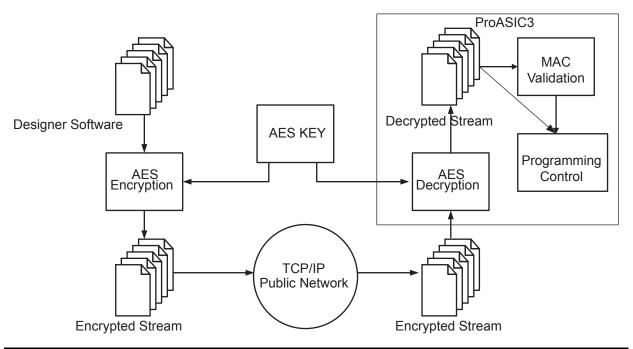

|    | Security in Action                                                       | . 308 |

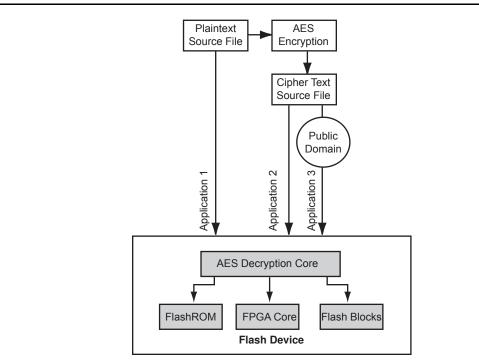

|    | FlashROM Security Use Models                                                            | . 311 |

|----|-----------------------------------------------------------------------------------------|-------|

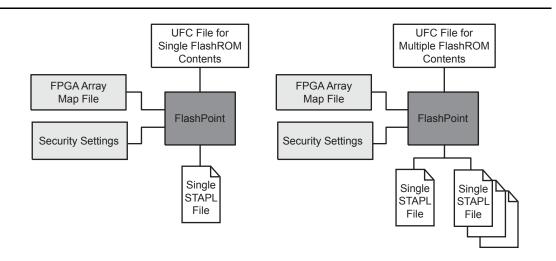

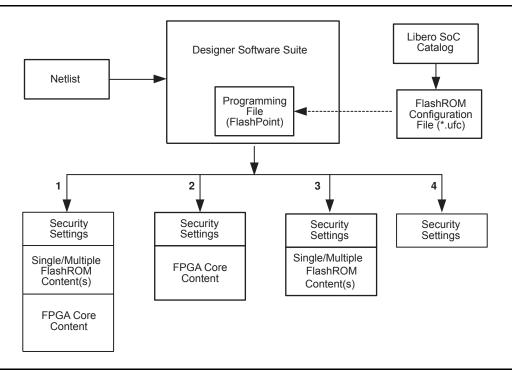

|    | Generating Programming Files                                                            | . 313 |

|    | Conclusion                                                                              | . 324 |

|    | Glossary                                                                                | . 324 |

|    | References                                                                              | . 324 |

|    | Related Documents                                                                       | . 325 |

|    | List of Changes                                                                         | . 325 |

|    |                                                                                         |       |

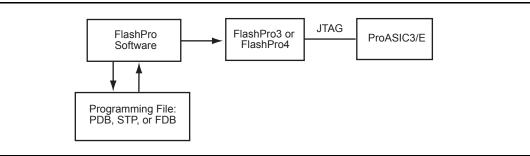

|    | In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X |       |

|    |                                                                                         |       |

|    |                                                                                         |       |

|    | ISP Support in Flash-Based Devices                                                      |       |

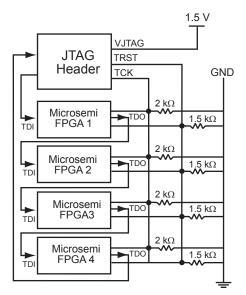

|    | Programming Voltage (VPUMP) and VJTAG                                                   |       |

|    | Nonvolatile Memory (NVM) Programming Voltage                                            |       |

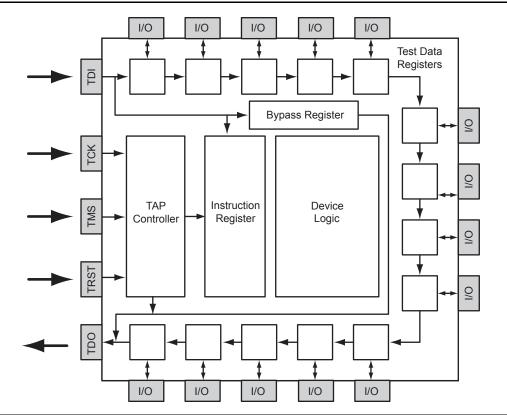

|    | IEEE 1532 (JTAG) Interface                                                              |       |

|    | Security                                                                                |       |

|    | Security in ARM-Enabled Low Power Flash Devices                                         |       |

|    | FlashROM and Programming Files                                                          |       |

|    | Programming Solution                                                                    |       |

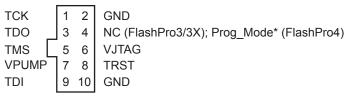

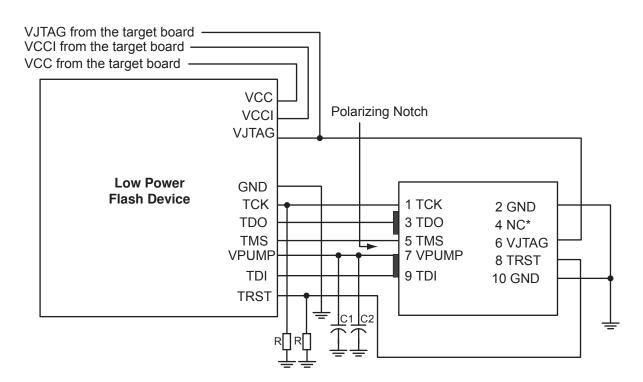

|    | ISP Programming Header Information                                                      |       |

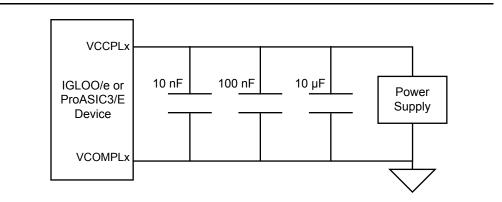

|    | Board-Level Considerations                                                              |       |

|    | Conclusion                                                                              |       |

|    | Related Documents                                                                       |       |

|    | List of Changes                                                                         | . 339 |

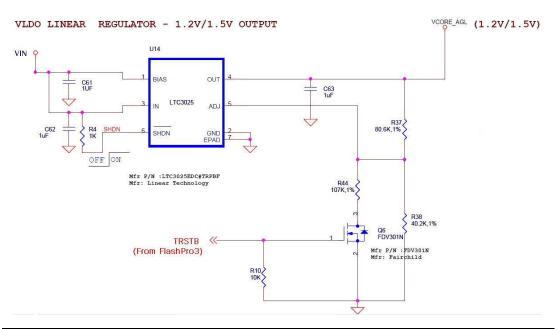

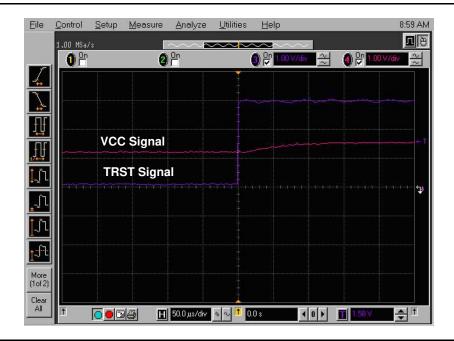

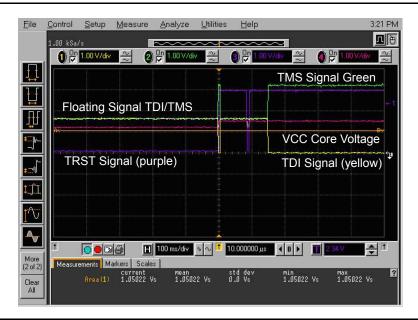

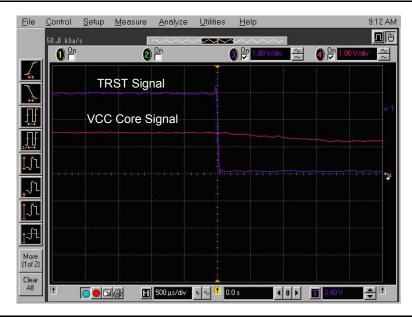

| 14 | Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming            | . 341 |

|    | Introduction                                                                            |       |

|    | Microsemi's Flash Families Support Voltage Switching Circuit                            |       |

|    |                                                                                         |       |

|    |                                                                                         |       |

|    | DirectC                                                                                 |       |

|    | Conclusion                                                                              |       |

|    | List of Changes                                                                         |       |

|    |                                                                                         |       |

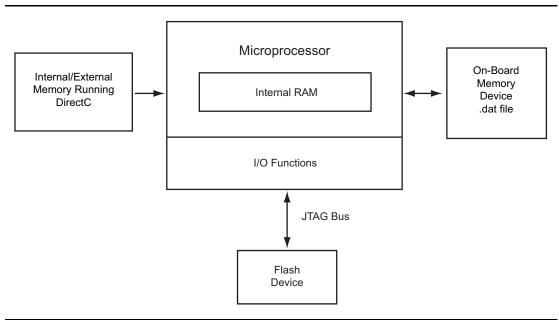

| 15 | Microprocessor Programming of Microsemi's Low Power Flash Devices                       | . 349 |

|    | Introduction                                                                            | 349   |

|    | Microprocessor Programming Support in Flash Devices                                     | . 350 |

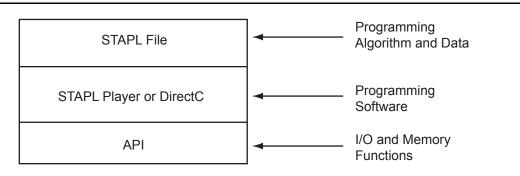

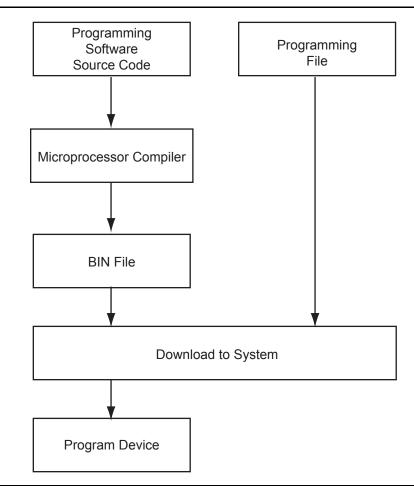

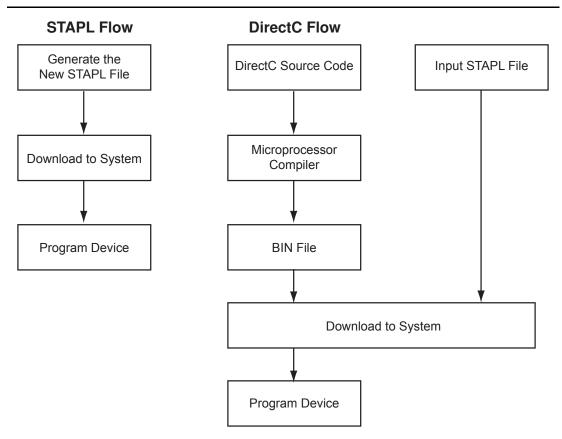

|    | Programming Algorithm                                                                   | . 351 |

|    | Implementation Overview                                                                 | . 351 |

|    | Hardware Requirement                                                                    | . 354 |

|    | Security                                                                                | . 354 |

|    | Conclusion                                                                              | . 355 |

|    | List of Changes                                                                         | . 356 |

| 16 | Boundary Scan in Low Power Flash Devices.                                               | 357   |

|    | Boundary Scan                                                                           |       |

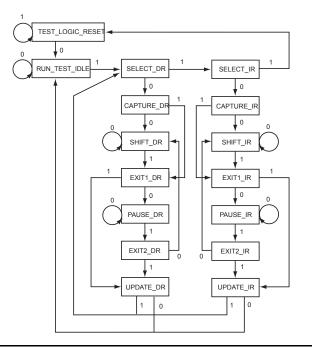

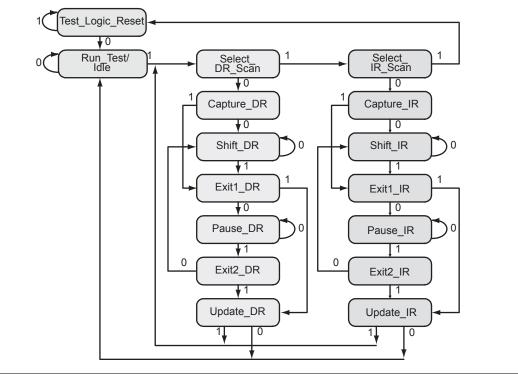

|    | TAP Controller State Machine                                                            |       |

|    |                                                                                         |       |

|    | Microsemi's Flash Devices Support the JTAG Feature                                      |       |

|    | Boundary Scan Support in Low Power Devices                                              |       |

|    |                                                                                         |       |

|    | Boundary Scan Chain                                                                                                                                                                                                                                                                                                                                       | 360<br>361                                                                                                         |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

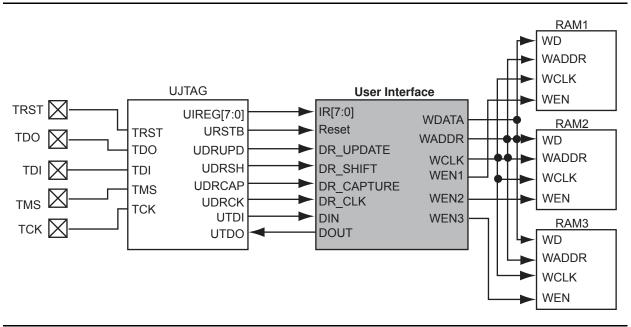

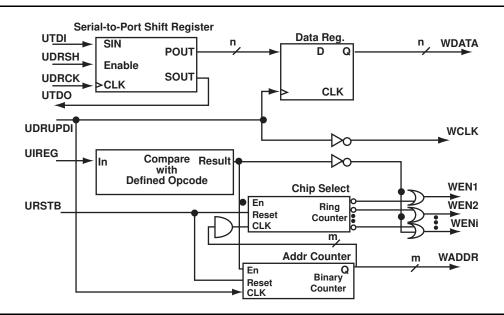

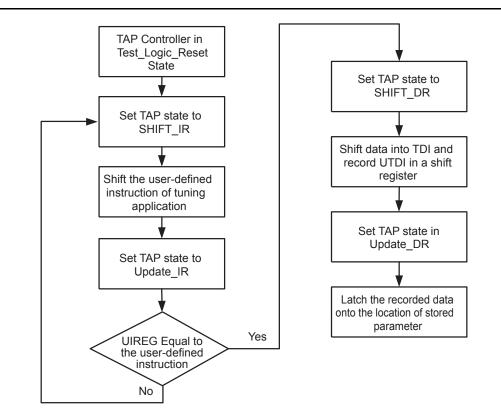

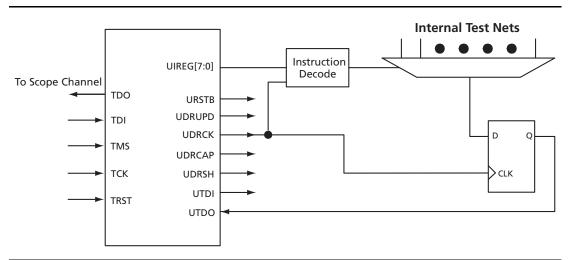

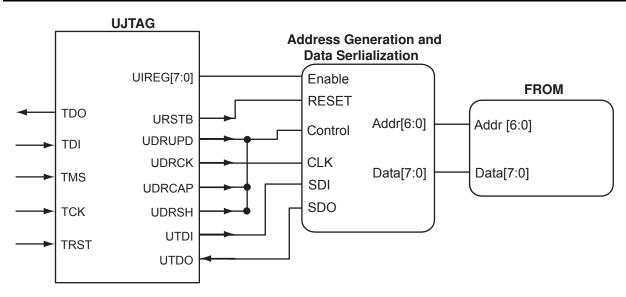

| 17 | Y UJTAG Applications in Microsemi's Low Power Flash Devices       3         Introduction       3         UJTAG Support in Flash-Based Devices       3         UJTAG Macro       3         UJTAG Operation       3         Typical UJTAG Applications       3         Conclusion       3         Related Documents       3         List of Changes       3 | 363<br>364<br>365<br>366<br>368<br>372<br>372                                                                      |

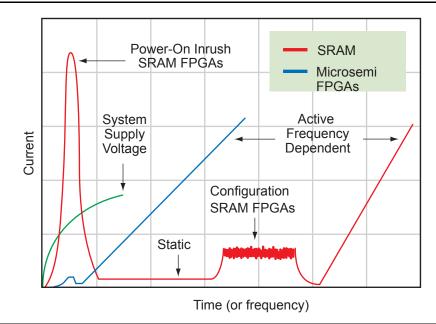

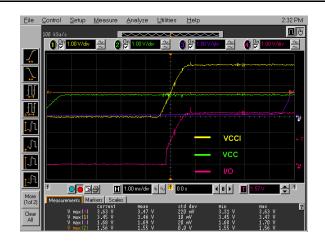

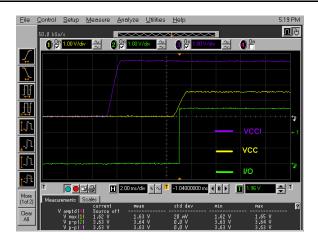

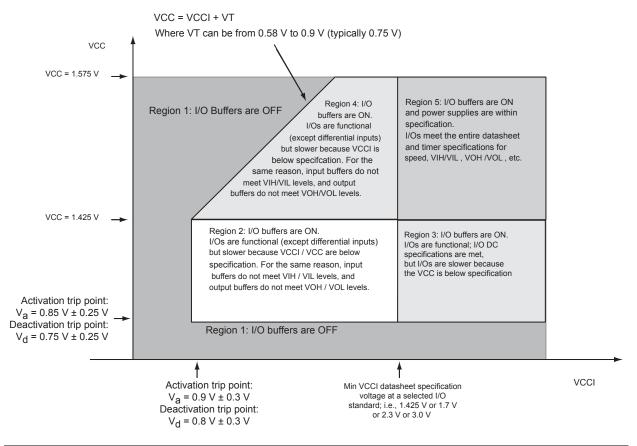

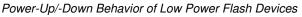

| 18 | Power-Up/-Down Behavior of Low Power Flash Devices Introduction Flash Devices Support Power-Up Behavior Power-Up/-Down Sequence and Transient Current I/O Behavior at Power-Up/-Down Cold-Sparing Hot-Swapping Conclusion Related Documents List of Changes                                                                                               | <ul> <li>373</li> <li>374</li> <li>375</li> <li>377</li> <li>382</li> <li>383</li> <li>383</li> <li>384</li> </ul> |

| A  | Summary of Changes.       3         History of Revision to Chapters       3                                                                                                                                                                                                                                                                               |                                                                                                                    |

| В  | Product Support       3         Customer Service       3         Customer Technical Support Center       5         Technical Support       5         Website       5         Contacting the Customer Technical Support Center       5         ITAR Technical Support       5         Index       3                                                        | 387<br>387<br>387<br>387<br>387<br>387<br>388                                                                      |

# Introduction

# Contents

This user's guide contains information to help designers understand and use Microsemi's ProASIC<sup>®</sup>3L devices. Each chapter addresses a specific topic. Most of these chapters apply to other Microsemi device families as well. When a feature or description applies only to a specific device family, this is made clear in the text.

# **Revision History**

The revision history for each chapter is listed at the end of the chapter. Most of these chapters were formerly included in device handbooks. Some were originally application notes or information included in device datasheets.

A "Summary of Changes" table at the end of this user's guide lists the chapters that were changed in each revision of the document, with links to the "List of Changes" sections for those chapters.

# **Related Information**

Refer to the *ProASIC3L Flash Family FPGAs* datasheet for detailed specifications, timing, and package and pin information.

The website page for ProASIC3L devices is /www.microsemi.com/soc/products/pa3l/default.aspx.

# 1 – FPGA Array Architecture in Low Power Flash Devices

# **Device Architecture**

## **Advanced Flash Switch**

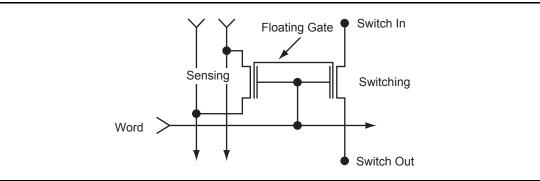

Unlike SRAM FPGAs, the low power flash devices use a live-at-power-up ISP flash switch as their programming element. Flash cells are distributed throughout the device to provide nonvolatile, reconfigurable programming to connect signal lines to the appropriate VersaTile inputs and outputs. In the flash switch, two transistors share the floating gate, which stores the programming information (Figure 1-1). One is the sensing transistor, which is only used for writing and verification of the floating gate voltage. The other is the switching transistor. The latter is used to connect or separate routing nets, or to configure VersaTile logic. It is also used to erase the floating gate. Dedicated high-performance lines are connected as required using the flash switch for fast, low-skew, global signal distribution throughout the device core. Maximum core utilization is possible for virtually any design. The use of the flash switch technology also removes the possibility of firm errors, which are increasingly common in SRAM-based FPGAs.

Figure 1-1 • Flash-Based Switch

FPGA Array Architecture in Low Power Flash Devices

# **FPGA Array Architecture Support**

The flash FPGAs listed in Table 1-1 support the architecture features described in this document.

### Table 1-1 • Flash-Based FPGAs

| Series                 | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO®                 | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|                        | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|                        | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|                        | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC <sup>®</sup> 3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|                        | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|                        | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|                        | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|                        | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|                        | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|                        | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion                 | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

*Note:* \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# **Device Overview**

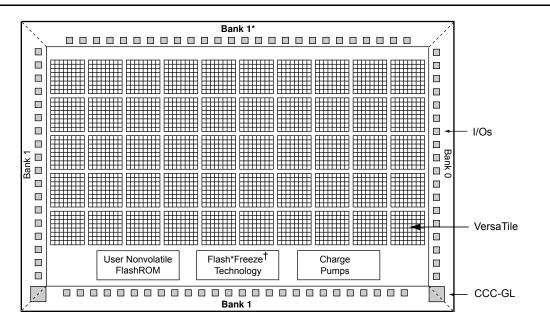

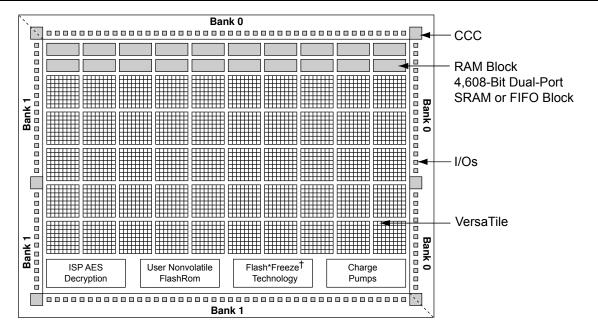

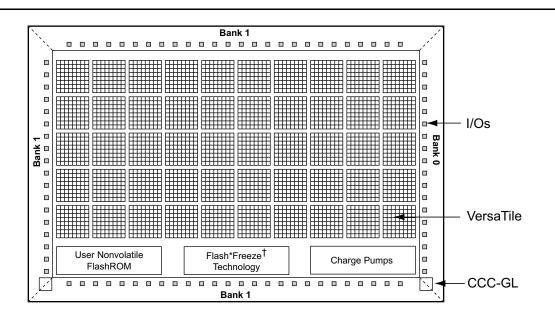

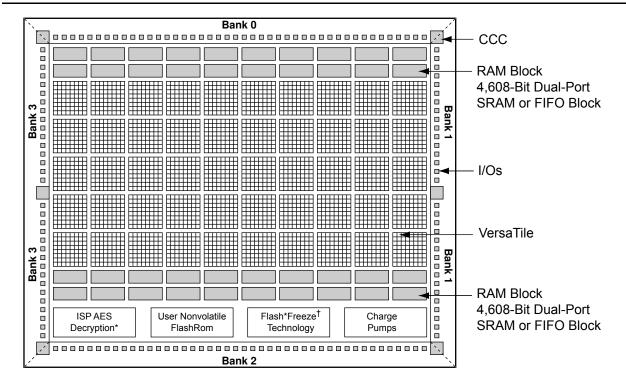

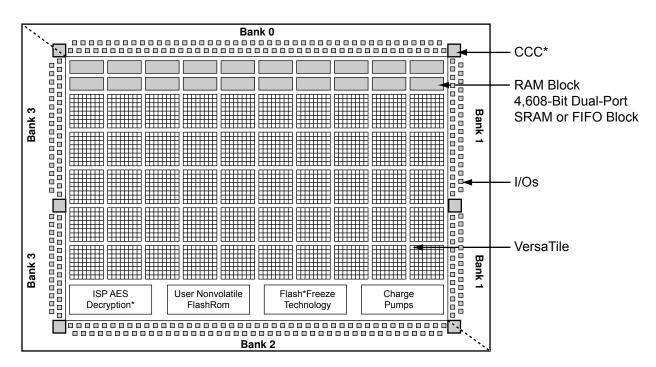

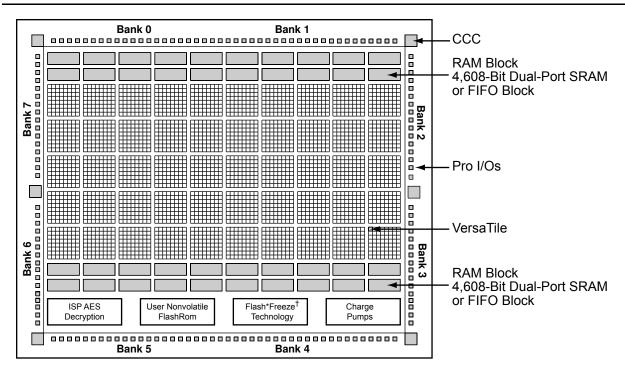

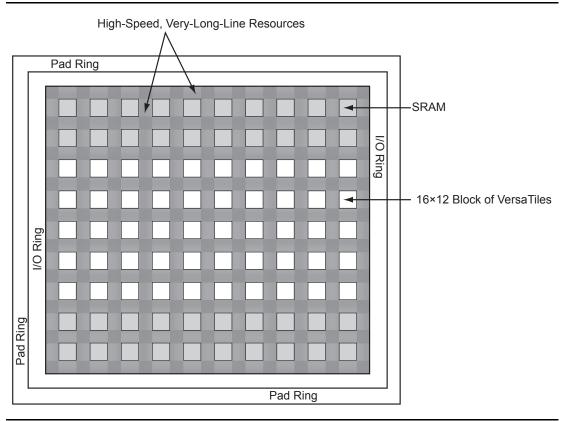

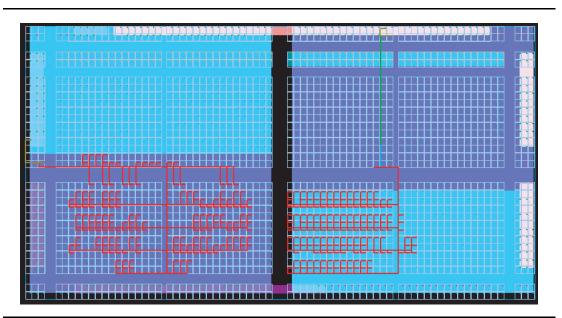

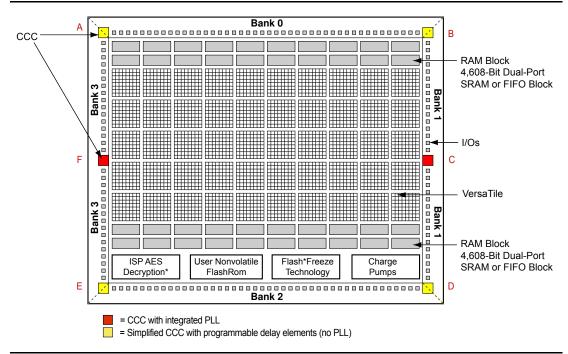

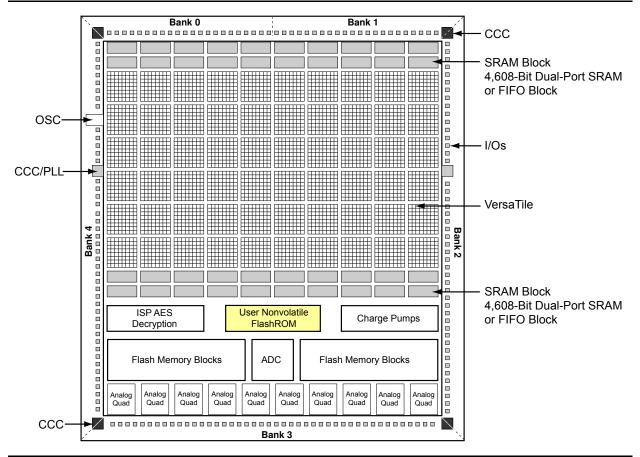

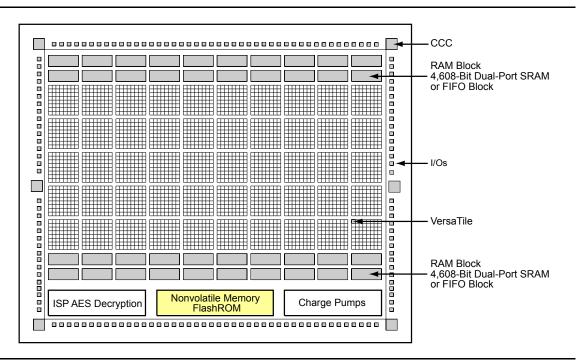

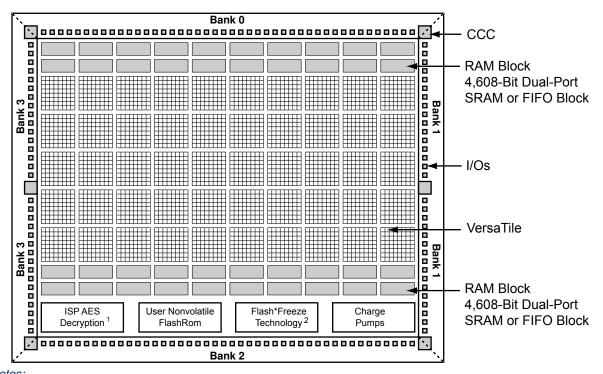

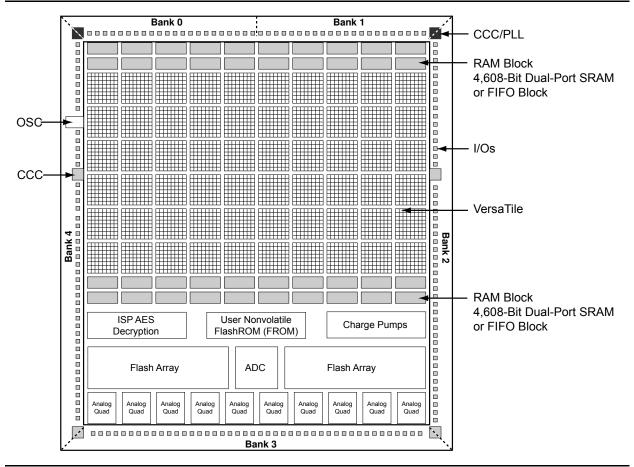

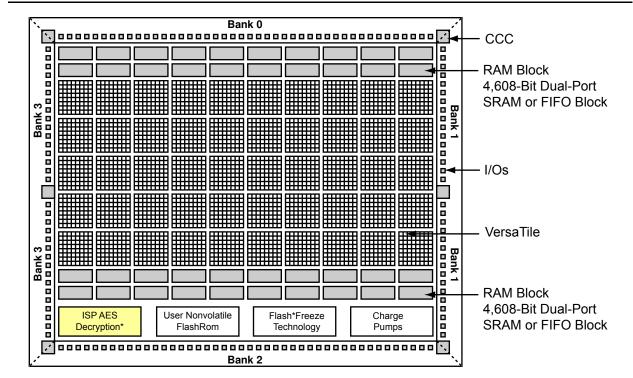

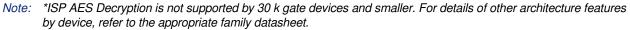

Low power flash devices consist of multiple distinct programmable architectural features (Figure 1-5 on page 13 through Figure 1-7 on page 14):

- FPGA fabric/core (VersaTiles)

- Routing and clock resources (VersaNets)

- FlashROM

- Dedicated SRAM and/or FIFO

- 30 k gate and smaller device densities do not support SRAM or FIFO.

- Automotive devices do not support FIFO operation.

- I/O structures

- Flash\*Freeze technology and low power modes

Notes: \* Bank 0 for the 30 k devices

† Flash\*Freeze mode is supported on IGLOO devices.

Figure 1-2 • IGLOO and ProASIC3 nano Device Architecture Overview with Two I/O Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices)

*Note: † Flash\*Freeze mode is supported on IGLOO devices.*

*Note: † Flash\*Freeze mode is supported on IGLOO devices.*

Figure 1-4 • IGLOO Device Architecture Overview with Three I/O Banks (AGLN015, AGLN020, A3PN015, and A3PN020)

Note: \* AGLP030 does not contain a PLL or support AES security.

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

*Note:* Flash\*Freeze technology only applies to IGLOOe devices.

Figure 1-7 · IGLOOe and ProASIC3E Device Architecture Overview (AGLE600 device is shown)

## I/O State of Newly Shipped Devices

Devices are shipped from the factory with a test design in the device. The power-on switch for VCC is OFF by default in this test design, so I/Os are tristated by default. Tristated means the I/O is not actively driven and floats. The exact value cannot be guaranteed when it is floating. Even in simulation software, a tristate value is marked as unknown. Due to process variations and shifts, tristated I/Os may float toward High or Low, depending on the particular device and leakage level.

If there is concern regarding the exact state of unused I/Os, weak pull-up/pull-down should be added to the floating I/Os so their state is controlled and stabilized.

## **Core Architecture**

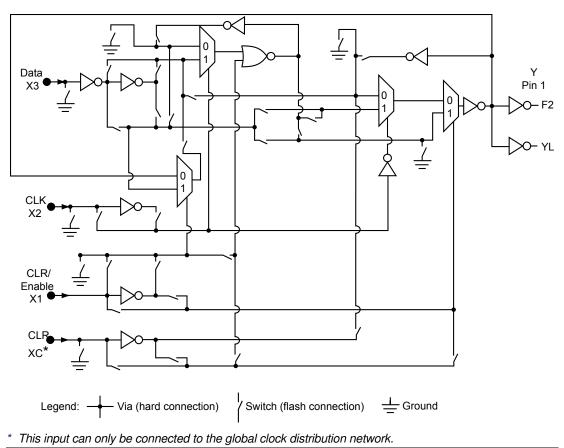

### VersaTile

The proprietary IGLOO and ProASIC3 device architectures provide granularity comparable to gate arrays. The device core consists of a sea-of-VersaTiles architecture.

As illustrated in Figure 1-8, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate flash switch connections:

- Any 3-input logic function

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a 4<sup>th</sup> input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions can be connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, SET/CLR is supported by a fourth input. The SET/CLR signal can only be routed to this fourth input over the VersaNet (global) network. However, if, in the user's design, the SET/CLR signal is not routed over the VersaNet network, a compile warning message will be given, and the intended logic function will be implemented by two VersaTiles instead of one.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-line or very-long-line resources.

Figure 1-8 • Low Power Flash Device Core VersaTile

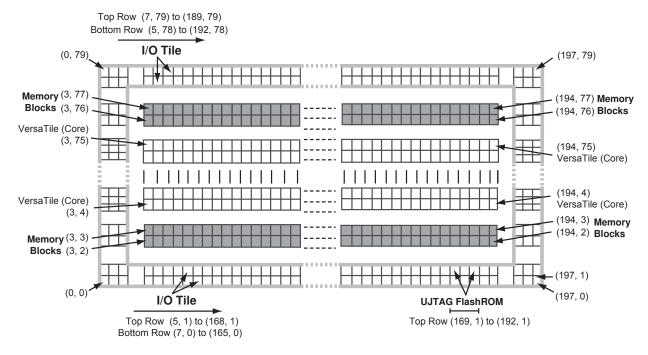

## **Array Coordinates**

During many place-and-route operations in the Microsemi Designer software tool, it is possible to set constraints that require array coordinates. Table 1-2 provides array coordinates of core cells and memory blocks for IGLOO and ProASIC3 devices. Table 1-3 provides the information for IGLOO PLUS devices. Table 1-4 on page 17 provides the information for IGLOO nano and ProASIC3 nano devices. The array coordinates are measured from the lower left (0, 0). They can be used in region constraints for specific logic groups/blocks, designated by a wildcard, and can contain core cells, memories, and I/Os.

I/O and cell coordinates are used for placement constraints. Two coordinate systems are needed because there is not a one-to-one correspondence between I/O cells and core cells. In addition, the I/O coordinate system changes depending on the die/package combination. It is not listed in Table 1-2. The Designer ChipPlanner tool provides the array coordinates of all I/O locations. I/O and cell coordinates are used for placement constraints. However, I/O placement is easier by package pin assignment.

Figure 1-9 on page 17 illustrates the array coordinates of a 600 k gate device. For more information on how to use array coordinates for region/placement constraints, see the *Designer User's Guide* or online help (available in the software) for software tools.

|          | VersaTiles                |      |   |      | Memory Rows |                        | Entire Die                 |        |            |

|----------|---------------------------|------|---|------|-------------|------------------------|----------------------------|--------|------------|

| Device   |                           | Min. |   | Max. |             | Bottom                 | Тор                        | Min.   | Max.       |

| IGLOO    | ProASIC3/<br>ProASIC3L    | x    | у | x    | у           | (x, y)                 | (x, y)                     | (x, y) | (x, y)     |

| AGL015   | A3P015                    | 3    | 2 | 34   | 13          | None                   | None                       | (0, 0) | (37, 15)   |

| AGL030   | A3P030                    | 3    | 3 | 66   | 13          | None                   | None                       | (0, 0) | (69, 15)   |

| AGL060   | A3P060                    | 3    | 2 | 66   | 25          | None                   | (3, 26)                    | (0, 0) | (69, 29)   |

| AGL125   | A3P125                    | 3    | 2 | 130  | 25          | None                   | (3, 26)                    | (0, 0) | (133, 29)  |

| AGL250   | A3P250/L                  | 3    | 2 | 130  | 49          | None                   | (3, 50)                    | (0, 0) | (133, 53)  |

| AGL400   | A3P400                    | 3    | 2 | 194  | 49          | None                   | (3, 50)                    | (0, 0) | (197, 53)  |

| AGL600   | A3P600/L                  | 3    | 4 | 194  | 75          | (3, 2)                 | (3, 76)                    | (0, 0) | (197, 79)  |

| AGL1000  | A3P1000/L                 | 3    | 4 | 258  | 99          | (3, 2)                 | (3, 100)                   | (0, 0) | (261, 103) |

| AGLE600  | A3PE600/L,<br>RT3PE600L   | 3    | 4 | 194  | 75          | (3, 2)                 | (3, 76)                    | (0, 0) | (197, 79)  |

|          | A3PE1500                  | 3    | 4 | 322  | 123         | (3, 2)                 | (3, 124)                   | (0, 0) | (325, 127) |

| AGLE3000 | A3PE3000/L,<br>RT3PE3000L | 3    | 6 | 450  | 173         | (3, 2)<br>or<br>(3, 4) | (3, 174)<br>or<br>(3, 176) | (0, 0) | (453, 179) |

### Table 1-2 · IGLOO and ProASIC3 Array Coordinates

#### *Table 1-3* • IGLOO PLUS Array Coordinates

|            |    | VersaTiles |     |     | Memor  | y Rows  | Entire Die |           |  |

|------------|----|------------|-----|-----|--------|---------|------------|-----------|--|

| Device     | Mi | Min. Max.  |     | ax. | Bottom | Тор     | Min.       | Max.      |  |

| IGLOO PLUS | x  | у          | х   | У   | (x, y) | (x, y)  | (x, y)     | (x, y)    |  |

| AGLP030    | 2  | 3          | 67  | 13  | None   | None    | (0, 0)     | (69, 15)  |  |

| AGLP060    | 2  | 2          | 67  | 25  | None   | (3, 26) | (0, 0)     | (69, 29)  |  |

| AGLP125    | 2  | 2          | 131 | 25  | None   | (3, 26) | (0, 0)     | (133, 29) |  |

|            |               | Vers      | aTiles    | Memory     | y Rows  | Entire Die |           |

|------------|---------------|-----------|-----------|------------|---------|------------|-----------|

| Device     |               | Min. Max. |           | Bottom Top |         | Min.       | Max.      |

| IGLOO nano | ProASIC3 nano | (x, y)    | (x, y)    | (x, y)     | (x, y)  | (x, y)     | (x, y)    |

| AGLN010    | A3P010        | (0, 2)    | (32, 5)   | None       | None    | (0, 0)     | (34, 5)   |

| AGLN015    | A3PN015       | (0, 2)    | (32, 9)   | None       | None    | (0, 0)     | (34, 9)   |

| AGLN020    | A3PN020       | (0, 2)    | 32, 13)   | None       | None    | (0, 0)     | (34, 13)  |

| AGLN060    | A3PN060       | (3, 2)    | (66, 25)  | None       | (3, 26) | (0, 0)     | (69, 29)  |

| AGLN125    | A3PN125       | (3, 2)    | (130, 25) | None       | (3, 26) | (0, 0)     | (133, 29) |

| AGLN250    | A3PN250       | (3, 2)    | (130, 49) | None       | (3, 50) | (0, 0)     | (133, 49) |

### Table 1-4 · IGLOO nano and ProASIC3 nano Array Coordinates

Note: The vertical I/O tile coordinates are not shown. West-side coordinates are {(0, 2) to (2, 2)} to {(0, 77) to (2, 77)}; east-side coordinates are {(195, 2) to (197, 2)} to {(195, 77) to (197, 77)}.

*Figure 1-9* • Array Coordinates for AGL600, AGLE600, A3P600, and A3PE600

## **Routing Architecture**

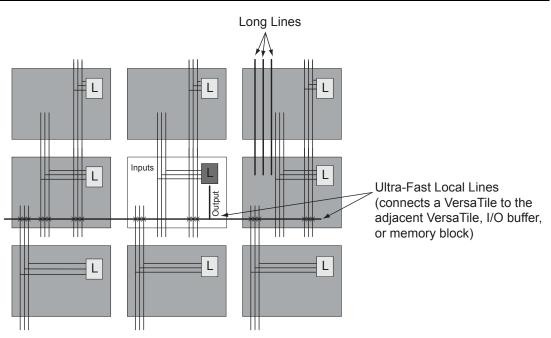

The routing structure of low power flash devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources; efficient long-line resources; high-speed, very-long-line resources; and the high-performance VersaNet networks.

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 1-10). The exception to this is that the SET/CLR input of a VersaTile configured as a D-flip-flop is driven only by the VersaTile global network.

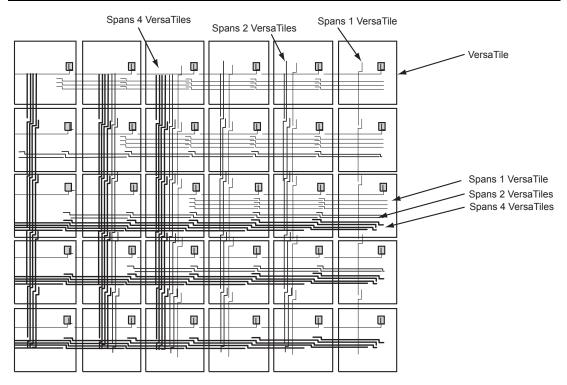

The efficient long-line resources provide routing for longer distances and higher-fanout connections. These resources vary in length (spanning one, two, or four VersaTiles), run both vertically and horizontally, and cover the entire device (Figure 1-11 on page 19). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Routing software automatically inserts active buffers to limit loading effects.

The high-speed, very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length ±12 VersaTiles in the vertical direction and length ±16 in the horizontal direction from a given core VersaTile (Figure 1-12 on page 19). Very long lines in low power flash devices have been enhanced over those in previous ProASIC families. This provides a significant performance boost for long-reach signals.

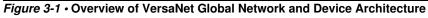

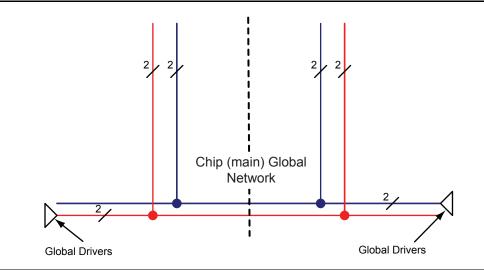

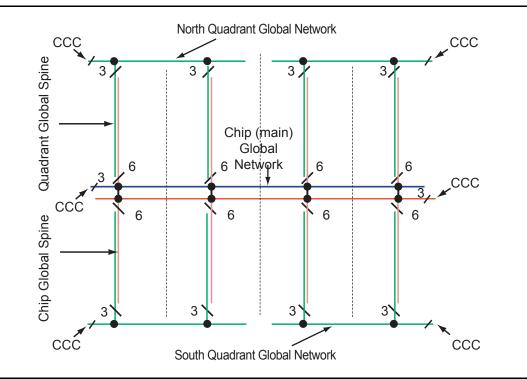

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or internal logic. These nets are typically used to distribute clocks, resets, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically, with signals accessing every input of every VersaTile. For more details on VersaNets, refer to the "Global Resources in Low Power Flash Devices" section on page 47.

Note: Input to the core cell for the D-flip-flop set and reset is only available via the VersaNet global network connection.

Figure 1-10 • Ultra-Fast Local Lines Connected to the Eight Nearest Neighbors

Figure 1-11 • Efficient Long-Line Resources

Figure 1-12 • Very-Long-Line Resources

# **Related Documents**

## **User's Guides**

Designer User's Guide

http://www.microsemi.com/soc/documents/designer\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                                                          | Page   |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|

| August 2012             | The "I/O State of Newly Shipped Devices" section is new (SAR 39542).                                                                                                                                                                                                                                                             | 14     |  |  |  |  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                        | N/A    |  |  |  |  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 1-1 • Flash-Based FPGAs.                                                                                                                                                                                                                                                |        |  |  |  |  |

|                         | Figure 1-2 • IGLOO and ProASIC3 nano Device Architecture Overview with Two I/O<br>Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices)<br>through Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device<br>Architecture Overview with Four I/O Banks (AGL600 device is shown) are new. | 11, 12 |  |  |  |  |

|                         | Table 1-4 • IGLOO nano and ProASIC3 nano Array Coordinates is new.                                                                                                                                                                                                                                                               | 17     |  |  |  |  |

| v1.3<br>(October 2008)  | The title of this document was changed from "Core Architecture of IGLOO and ProASIC3 Devices" to "FPGA Array Architecture in Low Power Flash Devices."                                                                                                                                                                           | 9      |  |  |  |  |

|                         | The "FPGA Array Architecture Support" section was revised to include new families and make the information more concise.                                                                                                                                                                                                         | 10     |  |  |  |  |

|                         | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to include Military ProASIC3/EL and RT ProASIC3 devices.                                                                                                                                                                                                            | 16     |  |  |  |  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 1-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul>                                                                                        | 10     |  |  |  |  |

| v1.1<br>(March 2008)    | Table 1-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "Device Overview" section are new.                                                                                                                                                     | 10     |  |  |  |  |

|                         | The "Device Overview" section was updated to note that 15 k devices do not support SRAM or FIFO.                                                                                                                                                                                                                                 | 11     |  |  |  |  |

|                         | Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks is new.                                                                                                                                                                                                                                                 | 13     |  |  |  |  |

|                         | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to add A3P015 and AGL015.                                                                                                                                                                                                                                           | 16     |  |  |  |  |

|                         | Table 1-3 • IGLOO PLUS Array Coordinates is new.                                                                                                                                                                                                                                                                                 | 16     |  |  |  |  |

# 2 – Flash\*Freeze Technology and Low Power Modes

## Flash\*Freeze Technology and Low Power Modes

Microsemi IGLOO,<sup>®</sup> IGLOO nano, IGLOO PLUS, ProASIC<sup>®</sup>3L, and Radiation-Tolerant (RT) ProASIC3 FPGAs with Flash\*Freeze technology are designed to meet the most demanding power and area challenges of today's portable electronics products with a reprogrammable, small-footprint, full-featured flash FPGA. These devices offer lower power consumption in static and dynamic modes, utilizing the unique Flash\*Freeze technology, than any other FPGA or CPLD.

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 devices offer various power-saving modes that enable every system to utilize modes that achieve the lowest total system power. Low Power Active capability (static idle) allows for ultra-low power consumption while the device is operational in the system by maintaining SRAM, registers, I/Os, and logic functions.

Flash\*Freeze technology provides an ultra-low power static mode (Flash\*Freeze mode) that retains all SRAM and register information with rapid recovery to Active (operating) mode. IGLOO nano and IGLOO PLUS devices have an additional feature when operating in Flash\*Freeze mode, allowing them to retain I/O states as well as SRAM and register states. This mechanism enables the user to quickly (within 1  $\mu$ s) enter and exit Flash\*Freeze mode by activating the Flash\*Freeze (FF) pin while all power supplies are kept in their original states. In addition, I/Os and clocks connected to the FPGA can still be toggled without impact on device power consumption. While in Flash\*Freeze mode, the device retains all core register states and SRAM information. This mode can be configured so that no power is consumed by the I/O banks, clocks, JTAG pins, or PLLs; and the IGLOO and IGLOO PLUS devices consume as little as 5  $\mu$ W, while IGLOO nano devices consume as little as 2  $\mu$ W. Microsemi offers a state management IP core to aid users in gating clocks and managing data before entering Flash\*Freeze mode.

This document will guide users in selecting the best low power mode for their applications, and introduces Microsemi's Flash\*Freeze management IP core.

# Flash Families Support the Flash\*Freeze Feature

The low power flash FPGAs listed in Table 2-1 support the Flash\*Freeze feature and the functions described in this document.

### Table 2-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

*Note:* \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

# Low Power Modes Overview

Table 2-2 summarizes the low power modes that achieve power consumption reduction when the FPGA or system is idle.

| Mode     |                        | VCCI | vcc | Core | Clocks | ULSICC<br>Macro                          | To Enter<br>Mode                         | To Resume<br>Operation                 | Trigger  |

|----------|------------------------|------|-----|------|--------|------------------------------------------|------------------------------------------|----------------------------------------|----------|

| Active   |                        | On   | On  | On   | On     | N/A                                      | Initiate clock                           | None                                   | -        |

| Static   | ldle                   | On   | On  | On   | Off    | N/A                                      | Stop clock                               | Initiate<br>clock                      | External |

|          | Flash*Freeze<br>type 1 | On   | On  | On   | On*    | N/A                                      | Assert FF<br>pin                         | Deassert<br>FF pin                     | External |

|          | Flash*Freeze<br>type 2 | On   | On  | On   | On*    | Used to<br>enter<br>Flash*Freeze<br>mode | Assert FF<br>pin and<br>assert<br>LSICC  | Deassert<br>FF pin                     | External |

| Sleep    |                        | On   | Off | Off  | Off    | N/A                                      | Shut down<br>VCC                         | Turn on<br>VCC supply                  | External |

| Shutdown |                        | Off  | Off | Off  | Off    | N/A                                      | Shut down<br>VCC and<br>VCCI<br>supplies | Turn on<br>VCC and<br>VCCI<br>supplies | External |

### Table 2-2 • Power Modes Summary

External clocks can be left toggling while the device is in Flash\*Freeze mode. Clocks generated by the embedded PLL will be turned off automatically.

# Static (Idle) Mode

In Static (Idle) mode, none of the clock inputs is switching, and static power is the only power consumed by the device. This mode can be achieved by switching off the incoming clocks to the FPGA, thus benefitting from reduced power consumption. In addition, I/Os draw only minimal leakage current. In this mode, embedded SRAM, I/Os, and registers retain their values so the device can enter and exit this mode just by switching the clocks on or off.

If the device-embedded PLL is used as the clock source, Static (Idle) mode can easily be entered by pulling the PLL POWERDOWN pin LOW (active Low), which will turn off the PLL.

# Flash\*Freeze Mode

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs offer an ultra-low static power mode to reduce power consumption while preserving the state of the registers, SRAM contents, and I/O states (IGLOO nano and IGLOO PLUS only) without switching off any power supplies, inputs, or input clocks.

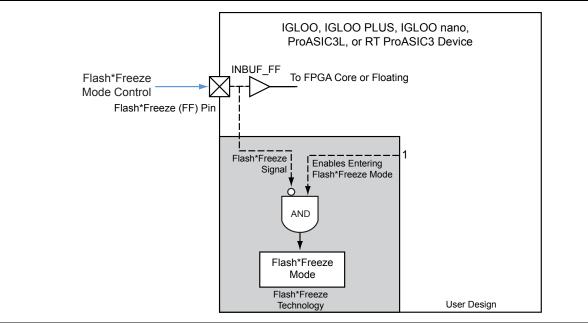

Flash\*Freeze technology enables the user to switch to Flash\*Freeze mode within 1 µs, thus simplifying low power design implementation. The Flash\*Freeze (FF) pin (active Low) is a dedicated pin used to enter or exit Flash\*Freeze mode directly; or the pin can be routed internally to the FPGA core and state management IP to allow the user's application to decide if and when it is safe to transition to this mode. If the FF pin is not used, it can be used as a regular I/O.

The FF pin has a built-in glitch filter and optional Schmitt trigger (not available for all devices) to prevent entering or exiting Flash\*Freeze mode accidentally.

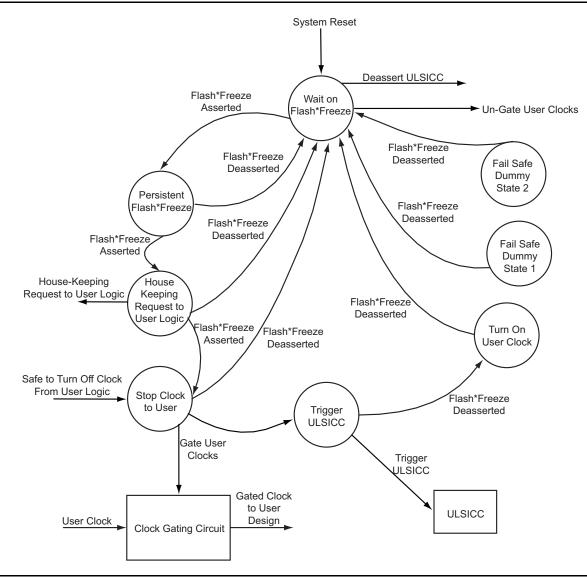

There are two ways to use Flash\*Freeze mode. In Flash\*Freeze type 1, entering and exiting the mode is exclusively controlled by the assertion and deassertion of the FF pin. This enables an external processor or human interface device to directly control Flash\*Freeze mode; however, valid data must be preserved using standard procedures (refer to the "Flash\*Freeze Mode Device Behavior" section on page 30). In Flash\*Freeze mode type 2, entering and exiting the mode is controlled by both the FF pin AND user-defined logic. Flash\*Freeze management IP may be used in type 2 mode for clock and data management while entering and exiting Flash\*Freeze mode.

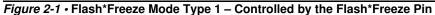

## Flash\*Freeze Type 1: Control by Dedicated Flash\*Freeze Pin

Flash\*Freeze type 1 is intended for systems where either the device will be reset upon exiting Flash\*Freeze mode, or data and clock are managed externally. The device enters Flash\*Freeze mode 1 µs after the dedicated FF pin is asserted (active Low), and returns to normal operation when the FF pin is deasserted (High) (Figure 2-1 on page 25). In this mode, FF pin assertion or deassertion is the only condition that determines entering or exiting Flash\*Freeze mode.

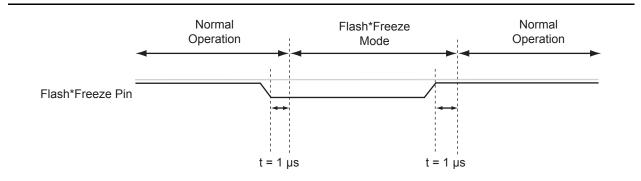

In Libero<sup>®</sup> System-on-Chip (SoC) software v8.2 and before, this mode is implemented by enabling Flash\*Freeze mode (default setting) in the Compile options of the Microsemi Designer software. To simplify usage of Flash\*Freeze mode, beginning with Libero software v8.3, an INBUF\_FF I/O macro was introduced. An INBUF\_FF I/O buffer must be used to identify the Flash\*Freeze input. Microsemi recommends switching to the new implementation.

In Libero software v8.3 and later, the user must manually instantiate the INBUF\_FF macro in the top level of the design to implement Flash\*Freeze Type 1, as shown in Figure 2-1 on page 25.

Figure 2-1 shows the concept of FF pin control in Flash\*Freeze mode type 1.

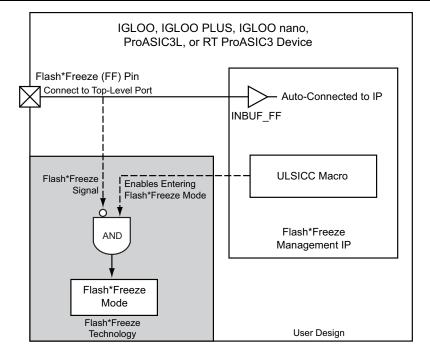

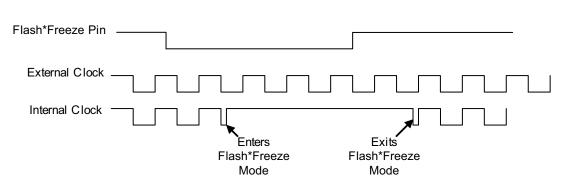

Figure 2-2 shows the timing diagram for entering and exiting Flash\*Freeze mode type 1.

Figure 2-2 • Flash\*Freeze Mode Type 1 – Timing Diagram

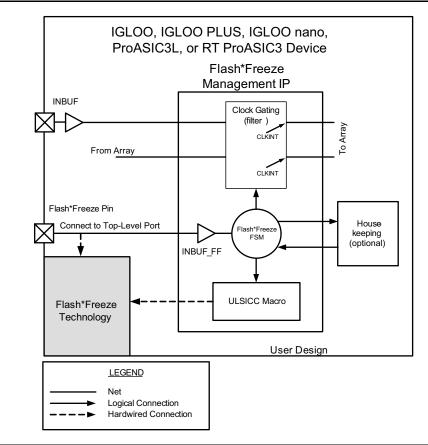

# Flash\*Freeze Type 2: Control by Dedicated Flash\*Freeze Pin and Internal Logic

The device can be made to enter Flash\*Freeze mode by activating the FF pin together with Microsemi's Flash\*Freeze management IP core (refer to the "Flash\*Freeze Management IP" section on page 36 for more information) or user-defined control logic (Figure 2-3 on page 27) within the FPGA core. This method enables the design to perform important activities before allowing the device to enter Flash\*Freeze mode, such as transitioning into a safe state, completing the processing of a critical event. Designers are encouraged to take advantage of Microsemi's Flash\*Freeze Management IP to handle clean entry and exit of Flash\*Freeze mode (described later in this document). The device will only enter Flash\*Freeze mode when the Flash\*Freeze pin is asserted (active Low) and the User Low Static I<sub>CC</sub> (ULSICC) macro input signal, called the LSICC signal, is asserted (High). One condition is not sufficient to enter Flash\*Freeze mode type 2; both the FF pin and LSICC signal must be asserted.

When Flash\*Freeze type 2 is implemented in the design, the ULSICC macro needs to be instantiated by the user. There are no functional differences in the device whether the ULSICC macro is instantiated or not, and whether the LSICC signal is asserted or deasserted. The LSICC signal is used only to control entering Flash\*Freeze mode. Figure 2-4 on page 27 shows the timing diagram for entering and exiting Flash\*Freeze mode type 2.

After exiting Flash\*Freeze mode type 2 by deasserting the Flash\*Freeze pin, the LSICC signal must be deasserted by the user design. This will prevent entering Flash\*Freeze mode by asserting the Flash\*Freeze pin only.

Refer to Table 2-3 for Flash\*Freeze (FF) pin and LSICC signal assertion and deassertion values.

| Signal                | Assertion Value | Deassertion Value |  |

|-----------------------|-----------------|-------------------|--|

| Flash*Freeze (FF) pin | Low             | High              |  |

| LSICC signal          | High            | Low               |  |

Notes:

- 1. The Flash\*Freeze (FF) pin is an active-Low signal, and LSICC is an active-High signal.

- 2. The LSICC signal is used only in Flash\*Freeze mode type 2.

*Figure 2-3* • Flash\*Freeze Mode Type 2 – Controlled by Flash\*Freeze Pin and Internal Logic (LSICC signal)

Figure 2-4 • Flash\*Freeze Mode Type 2 – Timing Diagram

Table 2-4 summarizes the Flash\*Freeze mode implementations.

| Flash*Freeze<br>Mode Type | Description                                                           | Flash*Freeze<br>Pin State | Instantiate<br>ULSICC Macro | LSICC<br>Signal   | Operating Mode    |

|---------------------------|-----------------------------------------------------------------------|---------------------------|-----------------------------|-------------------|-------------------|

|                           | Flash*Freeze mode is<br>controlled only by the<br>FF pin.             |                           | No                          | N/A               | Normal operation  |

|                           |                                                                       | Asserted                  | No                          | N/A               | Flash*Freeze mode |

|                           | Flash*Freeze mode is<br>controlled by the FF<br>pin and LSICC signal. |                           | Yes                         | Deasserted        | Normal operation  |

|                           |                                                                       | Deasserted                | Yes                         | "Don't care"      | Normal operation  |

|                           | Asserted                                                              | Yes                       | Asserted                    | Flash*Freeze mode |                   |

| Table 2-4 • Flash*Freeze Mode Usa |

|-----------------------------------|

|-----------------------------------|

Note: Refer to Table 2-3 on page 26 for Flash\*Freeze pin and LSICC signal assertion and deassertion values.

# IGLOO, ProASIC3L, and RT ProASIC3 I/O State in Flash\*Freeze Mode

In IGLOO and ProASIC3L devices, when the device enters Flash\*Freeze mode, I/Os become tristated. If the weak pull-up or pull-down feature is used, the I/Os will maintain the configured weak pull-up or pull-down status. This feature enables the design to set the I/O state to a certain level that is determined by the pull-up/-down configuration.

Table 2-5 shows the I/O pad state based on the configuration and buffer type.

Note that configuring weak pull-up or pull-down for the FF pin is not allowed. The FF pin can be configured as a Schmitt trigger input in IGLOOe, IGLOO nano, IGLOO PLUS, and ProASIC3EL devices.

#### Table 2-5 • IGLOO, ProASIC3L, and RT ProASIC3 Flash\*Freeze Mode (type 1 and type 2)—I/O Pad State

| Buffer Type                        |                  | I/O Pad Weak<br>Pull-Up/-Down | I/O Pad State in Flash*Freeze Mode |

|------------------------------------|------------------|-------------------------------|------------------------------------|

| Input/Global                       |                  | Enabled                       | Weak pull-up/pull-down*            |

|                                    |                  | Disabled                      | Tristate*                          |

| Output                             |                  | Enabled                       | Weak pull-up/pull-down             |

|                                    |                  | Disabled                      | Tristate                           |

| Bidirectional / Tristate<br>Buffer | E = 0            | Enabled                       | Weak pull-up/pull-down*            |

|                                    | (input/tristate) | Disabled                      | Tristate*                          |

|                                    | E = 1 (output)   | Enabled                       | Weak pull-up/pull-down             |

|                                    |                  | Disabled                      | Tristate                           |

\* Internal core logic driven by this input/global buffer will be tied High as long as the device is in Flash\*Freeze mode.

## IGLOO nano and IGLOO PLUS I/O State in Flash\*Freeze Mode

In IGLOO nano and IGLOO PLUS devices, users have multiple options in how to configure I/Os during Flash\*Freeze mode:

- 1. Hold the previous state

- 2. Set I/O pad to weak pull-up or pull-down

- 3. Tristate I/O pads

The I/O configuration must be configured by the user in the I/O Attribute Editor or in a PDC constraint file, and can be done on a pin-by-pin basis. The output hold feature will hold the output in the last registered state, using the I/O pad weak pull-up or pull-down resistor when the FF pin is asserted. When inputs are configured with the hold feature enabled, the FPGA core side of the input will hold the last valid state of the input pad before the device entered Flash\*Freeze mode. The input pad can be driven to any value, configured as tristate, or configured with the weak pull-up or pull-down I/O pad feature during Flash\*Freeze mode without affecting the hold state. If the weak pull-up or pull-down feature is used without the output hold feature, the input and output pads will maintain the configured weak pull-up or pull-down is defined on an output buffer or as bidirectional in output mode, and a hold state is also defined for the same pin, the pin will be configured with the predefined weak pull-up or pull-down. Any I/Os that do not use the hold state or I/O pad weak pull-up or pull-down features will be tristated during Flash\*Freeze mode and the FPGA core will be driven High by inputs. Inputs that are tristated during Flash\*Freeze mode may be left floating without any reliability concern or impact to power consumption.

Table 2-6 shows the I/O pad state based on the configuration and buffer type.

Note that configuring weak pull-up or pull-down for the FF pin is not allowed.

| Buffer Type                        |                           | Hold State | I/O Pad Weak<br>Pull-Up/-Down | I/O Pad State in<br>Flash*Freeze Mode |

|------------------------------------|---------------------------|------------|-------------------------------|---------------------------------------|

| Input                              |                           | Enabled    | Enabled                       | Weak pull-up/pull-down <sup>1</sup>   |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down <sup>2</sup>   |

|                                    |                           | Enabled    | Disabled                      | Tristate <sup>1</sup>                 |

|                                    |                           | Disabled   | Disabled                      | Tristate <sup>2</sup>                 |

| Output                             |                           | Enabled    | "Don't care"                  | Weak pull to hold state               |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down                |

|                                    |                           | Disabled   | Disabled                      | Tristate                              |

| Bidirectional / Tristate<br>Buffer | E = 0<br>(input/tristate) | Enabled    | Enabled                       | Weak pull-up/pull-down <sup>1</sup>   |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down <sup>2</sup>   |

|                                    |                           | Enabled    | Disabled                      | Tristate <sup>1</sup>                 |

|                                    |                           | Disabled   | Disabled                      | Tristate <sup>2</sup>                 |

|                                    | E = 1 (output)            | Enabled    | "Don't care"                  | Weak pull to hold state <sup>3</sup>  |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down                |

|                                    |                           | Disabled   | Disabled                      | Tristate                              |

### Table 2-6 • IGLOO nano and IGLOO PLUS Flash\*Freeze Mode (type 1 and type 2)—I/O Pad State

Notes:

- 1. Internal core logic driven by this input buffer will be set to the value this I/O had when entering Flash\*Freeze mode.

- 2. Internal core logic driven by this input buffer will be tied High as long as the device is in Flash\*Freeze mode.

- 3. For bidirectional buffers: Internal core logic driven by the input portion of the bidirectional buffer will be set to the hold state.

## Flash\*Freeze Mode Device Behavior

### Entering Flash\*Freeze Mode

- IGLOO, IGLOO nano, IGLOO PLUS, ProASCI3L, and RT ProASIC3 devices are designed and optimized to enter Flash\*Freeze mode only when power supplies are stable. If the device is being powered up while the FF pin is asserted (Flash\*Freeze mode type 1), or while both FF pin and LSICC signal are asserted (Flash\*Freeze mode type 2), the device is expected to enter Flash\*Freeze mode within 5 µs after the I/Os and FPGA core have reached their activation levels.

- If the device is already powered up when the FF pin is asserted, the device will enter Flash\*Freeze mode within 1 µs (type 1). In Flash\*Freeze mode type 2 operation, entering Flash\*Freeze mode is completed within 1 µs after both FF pin and LSICC signal are asserted. Exiting Flash\*Freeze mode is completed within 1 µs after deasserting the FF pin only.

### PLLs

- If an embedded PLL is used, entering Flash\*Freeze mode will automatically power down the PLL.

- The PLL output clocks will stop toggling within 1 µs after the assertion of the FF pin in type 1, or after both FF pin and LSICC signal are asserted in type 2. At the same time, I/Os will transition into the state specified in Table 2-6 on page 29. The user design must ensure it is safe to enter Flash\*Freeze mode.

### I/Os and Globals

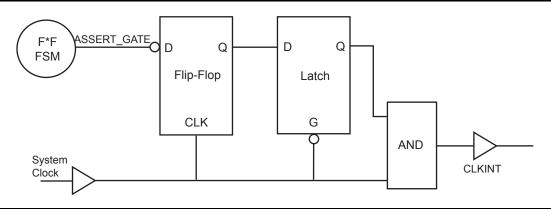

• While entering Flash\*Freeze mode, inputs, globals, and PLLs will enter their Flash\*Freeze state asynchronously to each other. As a result, clock and data glitches and narrow pulses may be generated while entering Flash\*Freeze mode, as shown in Figure 2-5.

Figure 2-5 • Narrow Clock Pulses During Flash\*Freeze Entrance and Exit

- I/O banks are not all deactivated simultaneously when entering Flash\*Freeze mode. This can cause clocks and inputs to become disabled at different times, resulting in unexpected data being captured.

- Upon entering Flash\*Freeze mode, all inputs and globals become tied High internally (except when an input hold state is used on IGLOO nano or IGLOO PLUS devices). If any of these signals are driven Low or tied Low externally, they will experience a Low to High transition internally when entering Flash\*Freeze mode.

- Upon entering type 2 Flash\*Freeze mode, ensure the LSICC signal (active High) does not deassert. This can prevent the device from entering Flash\*Freeze mode.

- Asynchronous input to output paths may experience output glitches. For example, on a direct into-out path, if the current state is '0' and the input bank turns off first, the input and then the output will transition to '1' before the output enters its Flash\*Freeze state. This can be prevented by using latches in asynchronous in-to-out paths.

- The above situations can cause glitches or invalid data to be clocked into and preserved in the device. Refer to the "Flash\*Freeze Design Guide" section on page 34 for solutions.

## During Flash\*Freeze Mode

- PLLs are turned off during Flash\*Freeze mode.

- I/O pads are configured according to Table 2-5 on page 28 and Table 2-6 on page 29.

- Inputs and input clocks to the FPGA can toggle without any impact on static power consumption, assuming weak pull-up or pull-down is not selected.

- If weak pull-up or pull-down is selected and the input is driven to the opposite direction, power dissipation will occur.

- Any toggling signals will be charging and discharging the package pin capacitance.

- IGLOO and ProASIC3L outputs will be tristated unless the I/O is configured with weak pull-up or pull-down. The output of the I/O to the FPGA core is logic High regardless of whether the I/O pin is configured with a weak pull-up or pull-down. Refer to Table 2-5 on page 28 for more information.

- IGLOO nano and IGLOO PLUS output behavior will be based on the configuration defined by the user. Refer to Table 2-6 on page 29 for a description of output behavior during Flash\*Freeze mode.

- The JTAG circuit is active; however, JTAG operations, such as JTAG commands, JTAG bypass, programming, and authentication, cannot be executed. The device must exit Flash\*Freeze mode before JTAG commands can be sent. TCK should be static to avoid extra power consumption from the JTAG state machine.

- The FF pin must be externally asserted for the device to stay in Flash\*Freeze mode.

- The FF pin is still active; i.e., the pin is used to exit Flash\*Freeze mode when deasserted.

### Exiting Flash\*Freeze Mode

### I/Os and Globals

- While exiting Flash\*Freeze mode, inputs and globals will exit their Flash\*Freeze state asynchronously to each other. As a result, clock and data glitches and narrow pulses may be generated while exiting Flash\*Freeze mode, unless clock gating schemes are used.

- I/O banks are not all activated simultaneously when exiting Flash\*Freeze mode. This can cause clocks and inputs to become enabled at different times, resulting in unexpected data being captured.

- Upon exiting Flash\*Freeze mode, inputs and globals will no longer be tied High internally (does not apply to input hold state on IGLOO nano and IGLOO PLUS). If any of these signals are driven Low or tied Low externally, they will experience a High-to-Low transition internally when exiting Flash\*Freeze mode.

- Applies only to IGLOO nano and IGLOO PLUS: Output hold state is asynchronously controlled by the signal driving the output buffer (output signal). This ensures a clean, glitch-free transition from hold state to output drive. However, any glitches on the output signal during exit from Flash\*Freeze mode may result in glitches on the output pad.

- The above situations can cause glitches or invalid data to be clocked into and preserved in the device. Refer to the "Flash\*Freeze Design Guide" on page 34 for solutions.

### PLLs

If the embedded PLL is used, the design must allow maximum acquisition time (per device datasheet) for the PLL to acquire the lock signal.

## Flash\*Freeze Pin Locations

Refer to the Pin Descriptions and Packaging chapter of specific device datasheets for information regarding Flash\*Freeze pin location on the available packages. The Flash\*Freeze pin location is independent of the device, allowing migration to larger or smaller devices while maintaining the same pin location on the board.

# Sleep and Shutdown Modes

## **Sleep Mode**

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs support Sleep mode when device functionality is not required. In Sleep mode,  $V_{CC}$  (core voltage),  $V_{JTAG}$  (JTAG DC voltage), and VPUMP (programming voltage) are grounded, resulting in the FPGA core being turned off to reduce power consumption. While the device is in Sleep mode, the rest of the system can still be operating and driving the input buffers of the device. The driven inputs do not pull up the internal power planes, and the current draw is limited to minimal leakage current.

Table 2-7 shows the power supply status in Sleep mode.

#### Table 2-7 • Sleep Mode—Power Supply Requirement for IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 Devices

| Power Supplies | Power Supply State |

|----------------|--------------------|

| VCC            | Powered off        |

| VCCI = VMV     | Powered on         |

| VJTAG          | Powered off        |

| VPUMP          | Powered off        |

Refer to the "Power-Up/-Down Behavior" section on page 33 for more information about I/O states during Sleep mode and the timing diagram for entering and exiting Sleep mode.

## Shutdown Mode

Shutdown mode is supported for all IGLOO nano and IGLOO PLUS devices as well the following IGLOO/e devices: AGL015, AGL030, AGLE600, AGLE3000, and A3PE3000L. Shutdown mode can be used by turning off all power supplies when the device function is not needed. Cold-sparing and hot-insertion features enable these devices to be powered down without turning off the entire system. When power returns, the live-at-power-up feature enables operation of the device after reaching the voltage activation point.

## Using Sleep and Shutdown Modes in the System

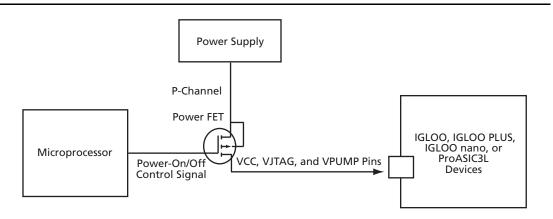

Depending on the power supply and the components used in an application, there are many ways to power on or off the power supplies connected to the device. For example, Figure 2-6 shows how a microprocessor can be used to control a power FET. Microsemi recommends that power FETs with low resistance be used to perform the switching action.

Figure 2-6 · Controlling Power-On/-Off State Using Microprocessor and Power FET

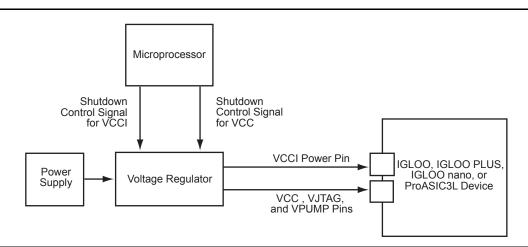

Figure 2-7 shows how a microprocessor can be used with a voltage regulator's shutdown pin to turn on or off the power supplies connected to the device.

Figure 2-7 • Controlling Power-On/-Off State Using Microprocessor and Voltage Regulator

## Power-Up/-Down Behavior

By design, all IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 I/Os are in tristate mode before device power-up. The I/Os remain tristated until the last voltage supply ( $V_{CC}$  or  $V_{CCI}$ ) is powered to its activation level. After the last supply reaches its functional level, the outputs exit the tristate mode and drive the logic at the input of the output buffer. The behavior of user I/Os is independent of the  $V_{CC}$  and  $V_{CCI}$  sequence or the state of other voltage supplies of the FPGA ( $V_{PUMP}$  and  $V_{JTAG}$ ). During power-down, device I/Os become tristated once the first power supply ( $V_{CC}$  or  $V_{CCI}$ ) drops below its deactivation voltage level. The I/O behavior during power-down is also independent of voltage supply sequencing.

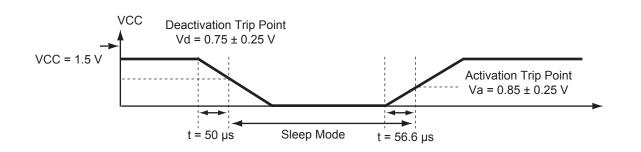

Figure 2-8 on page 34 shows a timing diagram when the V<sub>CC</sub> power supply crosses the activation and deactivation trip points in a typical application when the V<sub>CC</sub> power supply ramp-rate is 100  $\mu$ s (ramping from 0 V to 1.5 V in this example). This is the timing diagram for the FPGA entering and exiting Sleep mode, as this function is dependent on powering V<sub>CC</sub> down or up. Depending on the ramp-rate of the

power supply and board-level configurations, the user can easily calculate how long it will take for the core to become inactive or active. For more information, refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373.

Figure 2-8 • Entering and Exiting Sleep Mode, Typical Timing Diagram

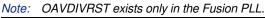

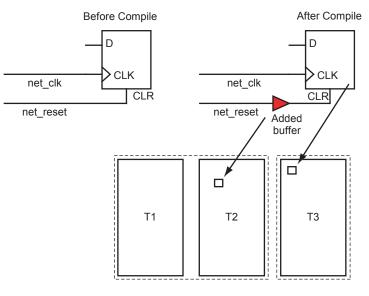

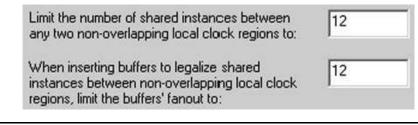

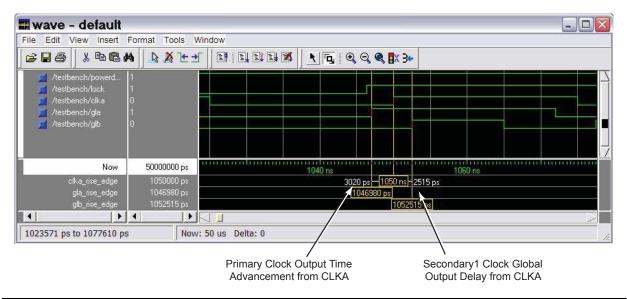

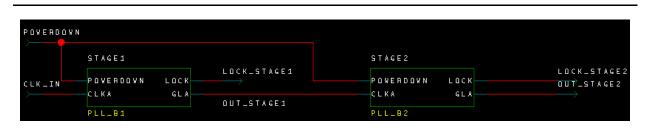

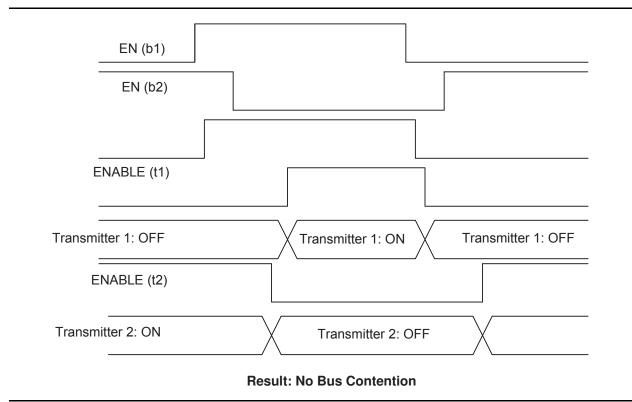

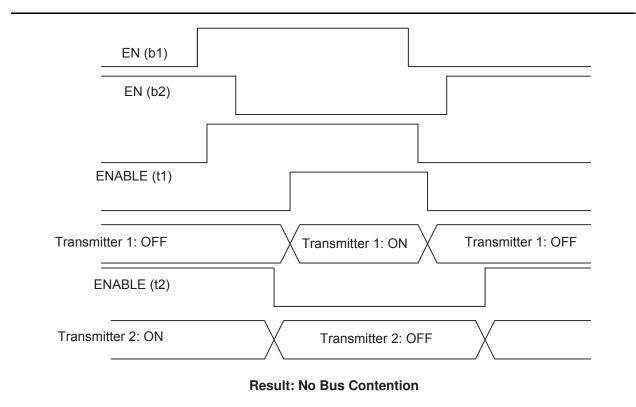

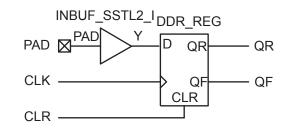

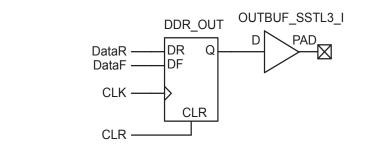

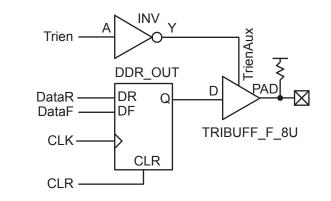

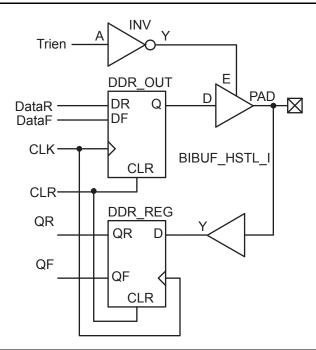

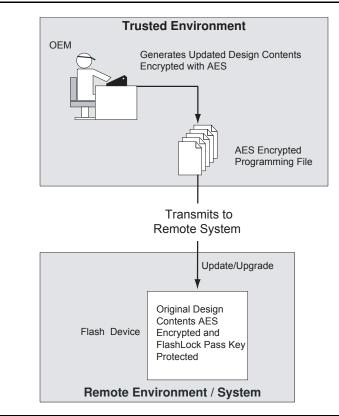

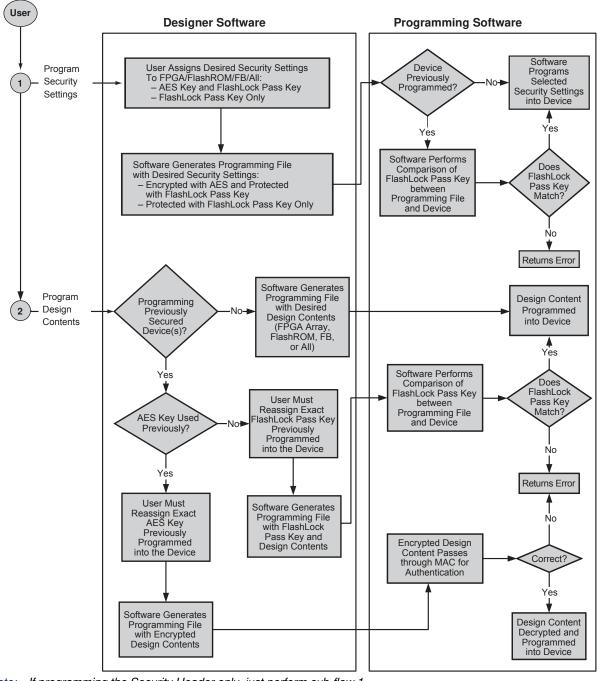

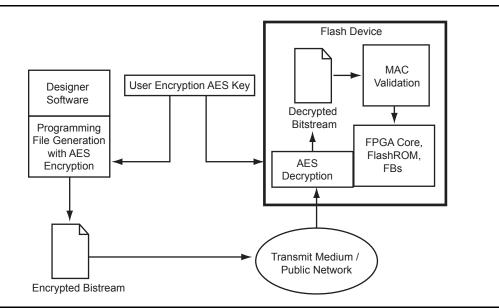

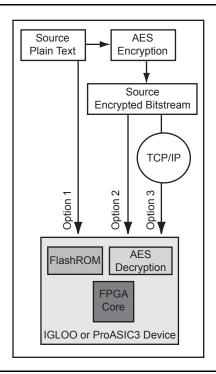

## **Context Save and Restore in Sleep or Shutdown Mode**