## PRELIMINARY

CONFIDENTIAL CYWB0224ABS, CYWB0224ABM CYWB0226ABS, CYWB0226ABM

## West Bridge™: Astoria™ USB and Mass Storage Peripheral Controller

## **Features**

- N-Xpress<sup>™</sup> NAND controller technology

- Interleave up to 16 NANDs with 8 chip enables (CE#) for x8 or x16 SLC (CYWB0224ABS) or MLC (CYWB0224ABM) NAND Flash devices

- · 4-bit error correction coding

- · Bad block management

- Static wear leveling

- · Multimedia device support

- · Up to 2 SD, SDIO, MMC, MMC+, and CE-ATA devices

- SLIM™ architecture, allowing simultaneous and independent data paths between the processor and USB, and between the USB and mass storage

- · High speed USB at 480 Mbps

- USB 2.0 compliant

- Integrated USB switch

- Integrated USB 2.0 transceiver, smart serial interface en-

- · 16 programmable endpoints

- · Flexible processor interface, which supports:

- Multiplexing and nonmultiplexing address and data interface

- SRAM interface

- Pseudo CRAM interface (Antioch interface)

- Pseudo NAND Flash interface

- SPI (slave mode) interface

- DMA slave support

- Ultra low power, 1.8V core operation

- Low power modes

- Small footprint, 6x6mm VFBGA

- Supports I2C boot and processor boot

- · Selectable clock input frequencies

- 19.2 MHz, 24 MHz, 26 MHz, and 48 MHz

## Applications

- Cellular Phones

- · Portable Media Players

- · Personal Digital Assistants

- · Portable Navigation Devices

- Digital Cameras

- POS Terminals

- · Portable Video Recorders

- Data Cards and Wireless Dongles

## **Functional Overview**

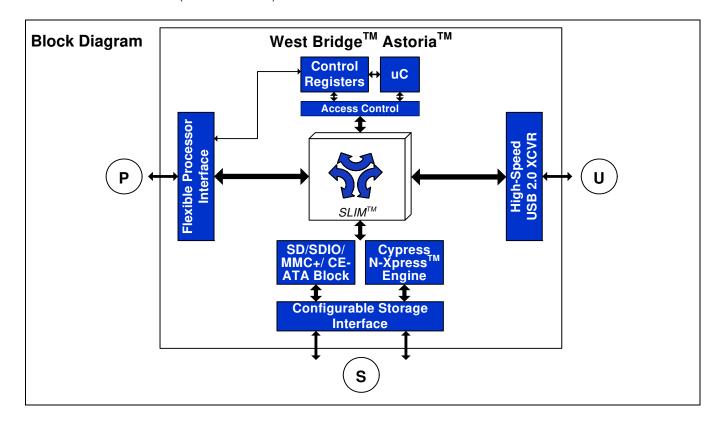

## The SLIM™ Architecture

The Simultaneous Link to Independent Multimedia (SLIM) architecture allows three different interfaces (P-port, S-port and U-port) to connect to one another independently.

With this architecture, connecting a device using Astoria to a PC through USB does not disturb any of the functions of the device. The device can still access mass storage at the same time the PC is synchronizing with the main processor.

The SLIM architecture enables new usage models in which a PC can access a mass storage device independent of the main processor, or enumerate access to both the mass storage and the main processor at the same time.

In a handset, this typically enables using the phone as a thumb drive, downloading media files to the phone while still having full functionality available on the phone, or using the same phone as a modem to connect the PC to the web.

#### 8051 Microprocessor

The 8051 microprocessor embedded in Astoria does basic transaction management for all the transactions between P-Port, S-Port, and U-Port. The 8051 does not reside in the data path; it manages the path. The data path is optimized for performance. The 8051 executes firmware that supports NAND, SD, SDIO, MMC+, and CE-ATA devices at the S-Port. For the NAND device, the 8051 firmware follows the smart media algorithm to support:

- · Physical to logical management

- · Four random bits ECC detection and correction support

- · Wear leveling

- NAND Flash bad blocks handling

## **Configuration and Status Registers**

The West Bridge Astoria device includes configuration and status registers that are accessible as memory mapped registers through the processor interface. The configuration registers allow the system to specify certain behavior of Astoria. For example, it is able to mask certain status registers from raising an interrupt. The status registers convey various status, such as the addresses of buffers for read operations.

## **Processor Interface (P-Port)**

Communication with the external processor is realized through a dedicated processor interface. This interface is configured to support different interface standards. This interface supports multiplexing and nonmultiplexing address or data bus in both synchronous and asynchronous pseudo CRAM-mapped, and nonmultiplexing address or data asynchronous SRAM-mapped memory accesses. The interface also can be configured to a pseudo NAND interface to support the processor's NAND interface. In addition, this interface can be configured to support SPI slave. Asynchronous accesses can reach a bandwidth of up

to 66.7 MBps. Synchronous accesses can be performed at 33 MHz across 16 bits for up to 66.7 MBps bandwidth.

The memory address is decoded to access any of the multiple endpoint buffers inside Astoria. These endpoints serve as buffers for data between each pair of ports, for example, between the processor port and the USB port. The processor writes and reads into these buffers via the memory interface.

Access to these buffers is controlled by either using a DMA protocol or using an interrupt to the main processor. These two modes are configurable by the external processor.

As a DMA slave, Astoria generates a DMA request signal to signify to the main processor that a specific buffer is ready to be read from or written to. The external processor monitors this signal and polls Astoria for the specific buffers ready for read or write. It then performs the appropriate read or write operations on the buffer through the processor interface. This way, the external processor only deals with the buffers to access a multitude of storage devices connected to Astoria.

In the Interrupt mode, Astoria communicates important buffer status changes to the external processor using an interrupt signal. The external processor then polls Astoria for the specific buffers ready for read or write, and it performs the appropriate read or write operations through the processor interface.

## **USB Interface (U-Port)**

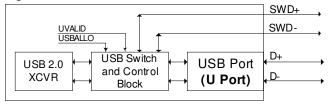

In accordance with the USB 2.0 specification, Astoria can operate in Full Speed USB mode in addition to High Speed USB. The USB interface consists of the USB transceiver. The USB interface is accessible by both the P-Port and the S-Port.

The Astoria USB interface supports programmable CONTROL/BULK/INTERRUPT/ISOCHRONOUS endpoints.

Astoria also has an integrated USB switch shown in Figure 1 that allows interfacing to an external Full Speed USB PHY.

Figure 1. U-Port With Switch and Control Block

## Mass Storage Support (S-Port)

The S-Port is configurable in six different interface modes, either simultaneously supporting an SD/SDIO/MMC+/CE-ATA port and a 8-bit SLC or MLC NAND Flash ports, supporting two SD/SDIO/MMC+/CE-ATA ports, supporting up to eight Chip Enable (CE#) for 8-bit or 16-bit SLC or MLC NAND Flash port, supporting SD/SDIO/MMC+/CE-ATA port and GPIO, supporting NAND Flash port and GPIO, and GPIO. These configurations are controlled by the 8051 firmware. The 16-bit NAND Flash interface can only be used when there is no other mass storage device connected to the S-Port.

# PRELIMINARY CONFIDENTIAL

## CYWB0224ABS, CYWB0224ABM CYWB0226ABS, CYWB0226ABM

## N-Xpress™ NAND Controller (S-Port)

Astoria, as part of its mass storage management functions, fully manages the SLC and MLC NAND Flash devices. The embedded 8051 manages the actual reading and writing of the NAND along with its required protocols. It performs standard NAND management functions such as ECC and wear leveling. The Astoria supports single bit ECC for the SLC and 4-bit ECC for MLC NAND Flash. SLC NAND Flash devices are supported by CYWB0244ABS. CYWB0244ABM supports both SLC and MLC NAND Flash devices.

## S-Port Configuration Modes

The S Port is configurable in six different interface modes.

- NAND Flash and SD/SDIO/MMC/CE-ATA interface mode

- NAND Flash interface mode

- Dual SD/SDIO/MMC/CE-ATA interface mode

- SD/SDIO/MMC/CE-ATA and GPIO interface mode

- NAND Flash and GPIO interface mode

- GPIO interface mode

#### NAND Flash Interface Mode

The NAND Flash interface mode configures the S-Port to interface with NAND Flash devices only. In this interface mode, the S-Port is configured to interface up to sixteen 8-bit SLC or MLC NAND Flash

#### NAND Port (S-Port)

Astoria, as part of its mass storage management functions, fully manages the SLC and MLC NAND Flash devices. The

embedded 8051 sets up reading and writing transaction of the NAND along with its required protocols. It performs standard NAND management functions such as ECC and wear leveling. The Astoria supports single bit ECC for the SLC and four bytes random ECC detection and correction for MLC NAND Flash.

SLC NAND Flash devices are supported by CYWB0244ABS. CYWB0244ABM supports both SLC and MLC NAND Flash devices.

## SD/SDIO/MMC+/CE-ATA Port (S-Port)

When Astoria is configured with firmware to support SD, SDIO, MMC+, and CE-ATA, this interface supports:

- The Multimedia Card System Specification, MMCA Technical Committee, Version 4.1.

- SD Memory Card Specification Part 1, Physical Layer Specification, SD Group, Version 1.10, October 15, 2004.

- SD Memory Card Specification Part 1, Physical Layer Specification, SD Group, Version 2.0, May 9, 2006.

- SD Specifications Part E1 SDIO Specification, Version 1.10, August 18, 2004.

- CE-ATA Specification CE-ATA Digital Protocol, CE-ATA Committee, Version 1.1, September, 2005.

West Bridge Astoria provides support for 1-bit and 4-bit SD and SDIO cards, 1-bit, 4-bit and 8-bit MMC, MMC+ cards, and CE-ATA drive. For the SD, SDIO, MMC/MMC Plus, and CE-ATA, this block supports one card for one physical bus interface.

Astoria supports SD commands including the multisector program command that are handled by the API.

## **Pin Assignments**

## Table 1. Astoria Pin Assignments

|        |                             |   |                                  |   |              | P | in Name                     |   |             |      |                                                             |                 |  |  |  |

|--------|-----------------------------|---|----------------------------------|---|--------------|---|-----------------------------|---|-------------|------|-------------------------------------------------------------|-----------------|--|--|--|

| P-Port | PCRAM Non<br>Multiplexing   | Ю | PCRAM<br>Multiplexing<br>(ADM)   | Ю | SRAM         | Ю | PNAND                       | Ю | SPI         | Ю    | Pin De-<br>scription                                        | Power<br>Domain |  |  |  |

|        | CLK (pull low in Asyn mode) | ı | CLK (pull-low in<br>Async mode)  | ı | Ext pull low | I | Ext pull low                | 1 | SCK         | ı    | Clock                                                       |                 |  |  |  |

|        | CE#                         | I | CE#                              | I | CE#          | I | CE#                         | I | SS#         | ı    | Chip<br>Enable/PNA<br>ND Chip<br>Select/SPI<br>Slave Select |                 |  |  |  |

|        | A0                          | I | Ext pull-up                      | I | A0           | I | CLE                         | I | Ext pull-up | I    | Addr. Bus<br>0/PNAND<br>Command<br>Latch                    |                 |  |  |  |

|        | A1                          | I | Ext pull-up                      | I | A1           | I | RB#                         | 0 | Ext pull-up | I    | Addr. Bus<br>1/PNAND<br>Ready_Buy                           | PVDDQ           |  |  |  |

|        | A[3:2]                      | I | A[2] = 1<br>A[3] = don't<br>care | I | A[3:2]       | I | A[3:2] = 00                 | I | A[3:2] = 10 | I    | Addr. Bus<br>[3:2]                                          |                 |  |  |  |

|        | A4                          | I | Ext pull-up                      | I | A4           | I | WP#                         | I | Ext pull-up | ı    | Addr. Bus<br>4/PNAND<br>Write<br>Protect                    |                 |  |  |  |

|        | A5                          | Ι | SCL                              | Ю | A5           | I | SCL                         | Ю | SCL         | Ю    | Addr. Bus<br>5/I2C clock                                    | VGND            |  |  |  |

|        | A6                          | I | SDA                              | Ю | A6           | I | SDA                         | Ю | SDA         | Ю    | Addr. Bus<br>6/I2C data                                     |                 |  |  |  |

|        | A7                          | I | Ext pull-up                      | I | A7           | I | A7 => 1:SBD<br>A7 => 0: LBD | I | Ext pull-up | I    | Addr. Bus 7                                                 |                 |  |  |  |

|        | DQ[0]                       | Ю | AD[0]                            | Ю | DQ[0]        | Ю | IO[0]                       | Ю | SDI         | 1    | SPI<br>Input/Data<br>Bus 0                                  |                 |  |  |  |

|        | DQ[1]                       | Ю | AD[1]                            | Ю | DQ[1]        | Ю | IO[1]                       | Ю | SDO         | 0    | SPI<br>Output/Data<br>Bus 1                                 |                 |  |  |  |

|        | DQ[15:2]                    | Ю | AD[15:2]                         | Ю | DQ[15:2]     | Ю | IO[15:2]                    | Ю | Ext pull-up | I    | Data Bus                                                    |                 |  |  |  |

|        | ADV#                        | I | ADV#                             | I |              | I | ALE                         | I | Ext pull-up | 1    | Address<br>Valid                                            |                 |  |  |  |

|        | OE#                         | I | OE#                              | I | OE#          | I | RE#                         | I | Ext pull-up | I    | Output<br>Enable                                            |                 |  |  |  |

|        | WE#                         | I | WE#                              | I | WE#          | I | WE#                         | I | Ext pull-up | I    | Write<br>Enable                                             |                 |  |  |  |

|        | INT#                        | 0 | INT#                             | 0 | INT#         | 0 | INT#                        | 0 | SINT#       | 0    | Interrupt<br>Request                                        |                 |  |  |  |

| DRQ &  | DRQ#                        | 0 | DRQ#                             | 0 | DRQ#         | 0 | DRQ#                        | 0 | N/C         | 0    | DMA<br>Request                                              | GVDDQ<br>VGND   |  |  |  |

| 9      | DACK#                       | I | DACK#                            | I | DACK#        | I | DACK#                       | I | Ext pull-up | I    | DMA<br>Acknowl-<br>edgement                                 | Valvid          |  |  |  |

|        | D+                          |   |                                  |   |              |   |                             |   |             |      | USB D+                                                      |                 |  |  |  |

| t      | D-                          |   |                                  |   |              |   |                             |   |             | IO/Z | USB D-                                                      |                 |  |  |  |

| U-Port | SWD+                        |   |                                  |   |              |   |                             |   |             | IO/Z | USB Switch<br>DP                                            | UVDDQ<br>UVSSQ  |  |  |  |

|        | SWD-                        |   |                                  |   |              |   |                             |   |             | IO/Z | USB Switch<br>DM                                            |                 |  |  |  |

|        |                             |   |                                  |   |              |   |                             |   |             | I    |                                                             |                 |  |  |  |

Table 1. Astoria Pin Assignments (continued)

|        | SDIO & NAND Configuration                   | Ю            | NAND only<br>Configuration            | Ю   | Double SDIO Configuration    | Ю       | NAND & GPIO<br>Configuration                 | Ю       | SDIO & GPIO<br>Configuration  | Ю                    | GPIO only<br>Configuration | Ю                       |                                                                                |                     |

|--------|---------------------------------------------|--------------|---------------------------------------|-----|------------------------------|---------|----------------------------------------------|---------|-------------------------------|----------------------|----------------------------|-------------------------|--------------------------------------------------------------------------------|---------------------|

|        | SD_D[7:0]                                   | Ю            | NAND_IO[15:8]<br>or PD[7:0]<br>(GPIO) | Ю   | SD_D[7:0]                    | Ю       | NAND_IO[15:8]<br>or<br>PD[7:0] (GPIO)        | Ю       | SD_D[7:0]                     | Ю                    | PD[7:0] (GPIO)             | Ю                       | SD Data<br>bus/NAND<br>Upper IO<br>bus                                         | SSVD                |

|        | SD_CLK                                      | 0            | NAND_CE8#or<br>NAND_R/B4#             | 0   | SD_CLK                       | 0       | PC-7 (GPIO) or<br>NAND_CE8# or<br>NAND_R/B4# | 10 0 1  | SD_CLK                        |                      | PC-7 (GPIO)                | Ю                       | SD Clock,<br>NAND CE8#<br>or NAND<br>R/B4#                                     |                     |

|        | SD_CMD                                      | Ю            | NAND_CE7#or<br>NAND_R/B3#             | 0 - | SD_CMD                       | Ю       | PC-3 (GPIO) or<br>NAND_CE7# or<br>NAND_R/B3# | 00-     | SD_CMD                        | Ю                    | PC-3 (GPIO)                | Ю                       | SD<br>Command,<br>NAND CE7#<br>or NAND<br>R/B4#                                |                     |

|        | SD_POW                                      | 0            | NAND_CE6#                             | 0   | SD_POW                       |         | PC-6 (GPIO) or<br>NAND_CE6#                  | 10      | SD_POW                        |                      | PC-6 (GPIO)                | Ю                       | SD Power<br>Control/NA<br>ND CE6#                                              |                     |

| S-Port | SD_WP                                       | I            | NAND_CE5#                             | 0   | SD_WP                        | I       | PC-5 (GPIO) or<br>NAND_CE5#                  | Ю       | SD_WP                         | I                    | N/C                        | I                       | GPIO (SD<br>Write<br>Protection<br>Microswitch<br>) or NAND<br>CE5#            |                     |

|        | NAND_IO[7:0]                                | Ю            | NAND_IO[7:0]                          | Ю   | SD2_D[7:0]                   | Ю       | NAND_IO[7:0]                                 | 0       | PB[7:0] (GPIO)                | 10                   | PB[7:0] (GPIO)             | Ю                       | NAND<br>Lower IO<br>bus                                                        |                     |

|        | NAND_CLE                                    | 0            | NAND_CLE                              | 0   | SD2_CLK                      | 0       | NAND_CLE                                     | 0       | PA-6 (GPIO)                   | 0                    | PA-6 (GPIO)                | 0                       | CMD Latch<br>Enable                                                            | SNVD-<br>DQ<br>VGND |

|        | NAND_ALE                                    | 0            | NAND_ALE                              | 0   | SD2_CMD                      | Ю       | NAND_ALE                                     | 0       | PA-7 (GPIO)                   | Ю                    | PA-7 (GPIO)                | Ю                       | Address<br>Latch<br>Enable                                                     |                     |

|        | NAND_CE#                                    | 0            | NAND_CE#                              | 0   | SD2_POW                      | 0       | NAND_CE#                                     | 0       | PC-0 (GPIO)                   | Ю                    | PC-0 (GPIO)                | Ю                       | Chip Enable                                                                    |                     |

|        | NAND_RE#                                    | 0            | NAND_RE#                              | 0   | N/C                          | 0       | NAND_RE#                                     | 0       | N/C                           | 0                    | N/C                        | 0                       | Read<br>Enable                                                                 |                     |

|        | NAND_WE#                                    | 0            | NAND_WE#                              | 0   | N/C                          | 0       | NAND_WE#                                     | 0       | N/C                           | 0                    | N/C                        | 0                       | Write<br>Enable                                                                |                     |

|        | NAND_WP#                                    | 0            | NAND_WP#                              | 0   | PA-5 (GPIO)                  | Ю       | NAND_WP#                                     | Ι       | PA-5 (GPIO)                   | Ю                    | PA-5 (GPIO)                | Ю                       | Write<br>Protect                                                               |                     |

|        | NAND_R/B#                                   | ı            | NAND_R/B#                             | ı   | N/C                          | Ι       | NAND_R/B#                                    | Ι       | N/C                           | I                    | N/C                        | I                       | Ready/Busy                                                                     |                     |

|        | NAND_CE2#                                   | 0            | NAND_CE2#                             | 0   | SD2_WP                       | 0       | NAND_CE2#                                    | 0       | PC-2 (GPIO)                   | Ю                    | PC-2 (GPIO)                | Ю                       | Chip Enable<br>2                                                               |                     |

|        | RESETOUT /<br>NAND_R/B2#                    | O            | NAND_R/B2#                            | _   | RESETOUT                     | 0       | RESETOUT or<br>NAND_R/B2#                    | 0       | RESETOUT                      | 0                    | RESETOUT                   | 0                       | RESET<br>OUT or<br>NAND<br>Busy/Ready                                          | 01/000              |

| Other  | PC-4<br>(GPIO[0]) /<br>SD_CD /<br>NAND_CE4# | 10<br>1<br>0 | NAND_CE4#                             | 0   | PC-4 (GPIO[0])<br>/<br>SD_CD | IO<br>I | PC-4 (GPIO[0])<br>or<br>NAND_CE4#            | 10<br>0 | PC-4 (GPIO[0])<br>or<br>SD_CD | IO<br>I              | PC-4 (GPIO[0])             | Ю                       | General<br>Input/Output<br>0 or<br>SD/MMC<br>Card<br>Detection or<br>NAND CE4# |                     |

| ō      | PC-5<br>(GPIO[1]) /                         | 10<br>0      | NAND_CE3#                             | 0   | PC-5 (GPIO[1])               | Ю       | PC-5 (GPIO[1])<br>or                         | Ю       | PC-5 (GPIO[1])                | Ю                    | PC-5 (GPIO[1])             | Ю                       | General<br>Input/Output                                                        |                     |

|        | NAND_CE3#                                   |              |                                       |     | SD2_CD                       | I       | NAND_CE3#                                    | 0       |                               |                      |                            |                         | 1,<br>NAND<br>CE3#, or<br>SD2_CD                                               |                     |

|        | RESET#                                      |              |                                       |     |                              |         |                                              |         |                               |                      |                            | _                       | RESET                                                                          | ]                   |

|        | WAKEUP                                      |              |                                       |     |                              |         |                                              |         |                               |                      |                            | _                       | Wake Up<br>Signal                                                              |                     |

| Conf   | XTALSLC[1:0]                                |              |                                       |     |                              |         |                                              |         |                               |                      | I                          | Clock Select<br>0 and 1 | GVDDQ                                                                          |                     |

| ပိ     | TEST[2:0]                                   |              |                                       |     |                              |         |                                              |         |                               |                      | I                          | Test Config-<br>uration | VGND                                                                           |                     |

| Clock  | XTALIN                                      |              |                                       |     |                              |         |                                              |         | _                             | Crystal/Cloc<br>k IN | XVDDQ                      |                         |                                                                                |                     |

| ਠੱ     | XTALOUT                                     |              |                                       |     |                              |         |                                              |         |                               | 0                    | Crystal Out                | VGND                    |                                                                                |                     |

## Table 1. Astoria Pin Assignments (continued)

|       | PVDDQ  | Power | Processor<br>I/F VDD |

|-------|--------|-------|----------------------|

|       | SNVDDQ | Power | NAND VDD             |

|       | UVDDQ  | Power | USB VDD              |

|       | SSVDDQ | Power | SDIO VDD             |

| Power | GVDDQ  | Power | Misc IO<br>VDD       |

|       | AVDDQ  | Power | Analog VDD           |

|       | XVDDQ  | Power | Crystal VDD          |

|       | VDD    | Power | Core VDD             |

|       | VDD33  | Power | Independen<br>t 3.3V |

|       | UVSSQ  | Power | USB GND              |

|       | AVSSQ  | Power | Analog GND           |

|       | VGND   | Power | Core GND             |

## **Ordering Information**

| Ordering Code    | Package Type        | NAND Flash Support                            | Available Clock Input Frequencies (MHz) |  |  |

|------------------|---------------------|-----------------------------------------------|-----------------------------------------|--|--|

| CYWB0224ABS-BVXI | 100 VFBGA – Pb-Free | Support SLC NAND Flash only                   | 19.2, 24, 26, 48                        |  |  |

| CYWB0224ABM-BVXI | 100 VFBGA – Pb-Free | Support SLC and MLC NAND Flash                | 19.2, 24, 26, 48                        |  |  |

| CYWB0226ABS-BVXI | 100 VFBGA – Pb-Free | Support SLC NAND Flash and USB switch         | 19.2, 24, 26, 48                        |  |  |

| CYWB0226ABM-BVXI | 100 VFBGA – Pb-Free | Support SLC and MLC NAND Flash and USB switch | 19.2, 24, 26, 48                        |  |  |

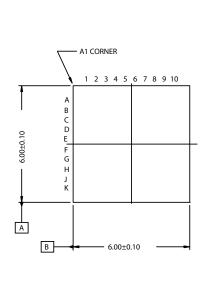

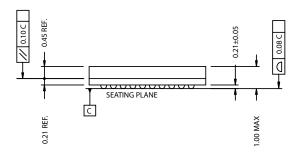

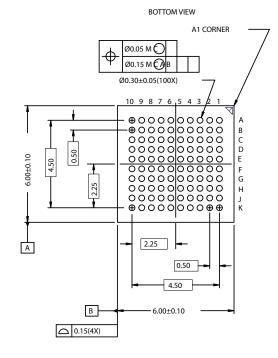

## **Package Diagram**

Figure 2. 100 VFBGA (6 x 6 x 1.0 MM) BZ100A

TOP VIEW

REFERENCE JEDEC MO-195C PKG. WEIGHT: TBD (NEW PKG.)

51-85209-\*B

© Cypress Semiconductor Corporation, 2007-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

West Bridge, Astoria, Antioch, and SLIM are trademarks of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.