### **General Description**

The MAX20326 is a dual-channel, precision, open-drain, communication-line accelerator. It provides the acceleration from a low-to-high transition necessary to allow faster data transfer in a highly capacitive, multidrop node system.

The MAX20326 is optimized for the I<sup>2</sup>C bus, as well as 1-Wire<sup>®</sup> bus, where a high-speed, open-drain operation is often required with a highly capacitive load.

This device is available in a 4-pin 0.5mm pitch 1.25mm x 1.25mm flip-chip QFN package and operates over the -40°C to +85°C extended temperature range.

### **Applications**

- I<sup>2</sup>C

- MDIO

- 1-Wire Bus

### **Benefits and Features**

- Reliable Communication

- Wide Operating Input Voltage: +1.4V to +5.5V

- Precision Accelerator Trigger Threshold: 0.5V ±50mV

- · Fast Charge Up to 1000pF Load

- · Low EMI: Controlled Acceleration Slope

- Space Saving

- 4-Pin (0.5mm Pitch 1.25mm x 1.25mm Flip-Chip QFN)

- · Integrated Precision Pullup

Ordering Information appears at end of data sheet.

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

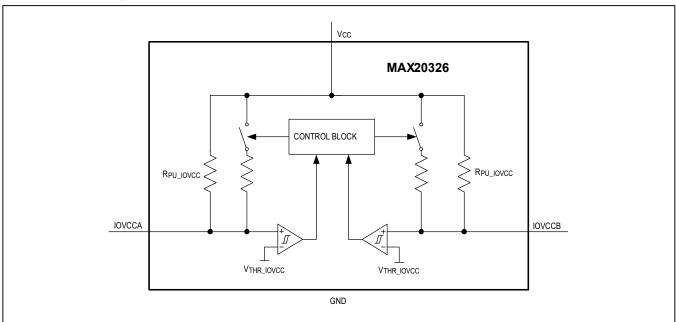

## **Functional Diagram**

## **Absolute Maximum Ratings**

| (All voltages referenced to GND.)                     | Operating Temperature Range40°C to +85°C |

|-------------------------------------------------------|------------------------------------------|

| V <sub>CC</sub> 0.5V to +6V                           | Junction Temperature+150°C               |

| IOVCCA, IOVCCB0.5V to V <sub>CC</sub> + 0.5V          | Storage Temperature Range65°C to +150°C  |

| Continuous Current Into Any Terminal±100mA            | Soldering Temperature (reflow)+260°C     |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                          |

| FC QFN (derate 5.15mW/°C above +70°C)412mW            |                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 4 FC QFN

| PACKAGE CODE                           | F41A1F+1  |  |  |

|----------------------------------------|-----------|--|--|

| Outline Number                         | 21-100188 |  |  |

| Land Pattern Number                    | 90-100054 |  |  |

| Thermal Resistance, Four-Layer Board:  |           |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 194°C/W   |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 84°C/W    |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

www.maximintegrated.com Maxim Integrated | 2

### **Electrical Characteristics**

$(V_{CC} = 1.4V \text{ to } 5.5V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = 1.8V, T_A = +25^{\circ}\text{C})$  (Notes 1, 2)

| PARAMETER                                         | SYMBOL                  | CONDITIONS                                                                           | MIN   | TYP | MAX  | UNITS |  |

|---------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------|-------|-----|------|-------|--|

| SUPPLY OPERATION                                  | •                       |                                                                                      |       |     |      |       |  |

| Operating Voltage                                 | V <sub>CC</sub>         |                                                                                      | 1.4   |     | 5.5  | V     |  |

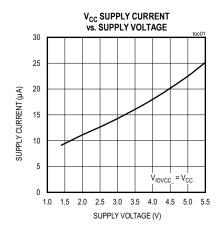

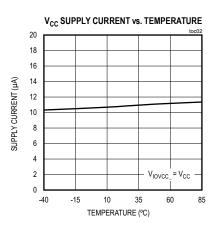

| Supply Current                                    | I <sub>Q_VCC</sub>      | V <sub>IOVCCA</sub> = V <sub>IOVCCB</sub> = V <sub>CC</sub> , V <sub>CC</sub> ≤ 1.8V | 11 18 |     | 18   |       |  |

|                                                   |                         | $V_{IOVCCA} = V_{IOVCCB} = V_{CC}, V_{CC} \le 5.5V$                                  | 45    |     |      | μA    |  |

| Supply Shutdown Threshold                         | V <sub>TH_VCC</sub>     | V <sub>CC</sub> rising                                                               |       | 0.7 | 1.1  | V     |  |

| Supply Shutdown Threshold<br>Hysteresis           | V <sub>TH_HY_VCC</sub>  |                                                                                      |       | 40  |      | mV    |  |

| I/O LOGIC LEVELS                                  |                         |                                                                                      |       |     |      |       |  |

| Resistive Static Pullup                           | R <sub>PU_IOVCC</sub>   |                                                                                      | 1.98  | 2.2 | 2.42 | kΩ    |  |

| IOVCC_Accelerator Rising<br>Trigger Threshold     | V <sub>THR_IOVCC</sub>  |                                                                                      | 0.45  | 0.5 | 0.55 | V     |  |

| IOVCC_Accelerator Falling<br>Threshold Hysteresis | V <sub>THH</sub> _IOVCC |                                                                                      |       | 19  |      | mV    |  |

| Minimum IOVCC_Low<br>Pulse Duration               | tLOW_REARM              |                                                                                      | 125   |     |      | ns    |  |

| ACCELERATOR                                       |                         |                                                                                      |       |     |      |       |  |

| Accelerator Pulse Duration                        | t <sub>ACC_ON</sub>     | V <sub>CC</sub> ≥ 1.6V                                                               | 120   |     | 200  | ns    |  |

|                                                   |                         | V <sub>CC</sub> ≥ 1.4V                                                               | 120   |     | 250  |       |  |

| Accelerator Static Source Impedance (Note 3)      | R <sub>ACC_STAT</sub>   | $R_{LOAD}$ = 25Ω, accelerator driven with internal clock waveform                    |       | 22  |      | Ω     |  |

| CAPACITANCE                                       |                         |                                                                                      |       |     |      |       |  |

| IOVCC_ Capacitance                                | C <sub>IOVCC</sub>      |                                                                                      |       | 13  |      | pF    |  |

| ESD PROTECTION                                    |                         |                                                                                      |       |     |      |       |  |

| Human Body Model                                  |                         | All pins                                                                             |       | ±2  |      | kV    |  |

Note 1: All devices are 100% production tested at  $T_A$  = +25°C. Specifications over the operating temperature range are guaranteed

Note 2: After V<sub>CC</sub> reaches V<sub>TH\_VCC</sub>, at least 3ms is needed in order to guarantee all min/max values.

Note 3: The impedance exhibited by the accelerator when driving a capacitive load varies and transiently differs from the static one.

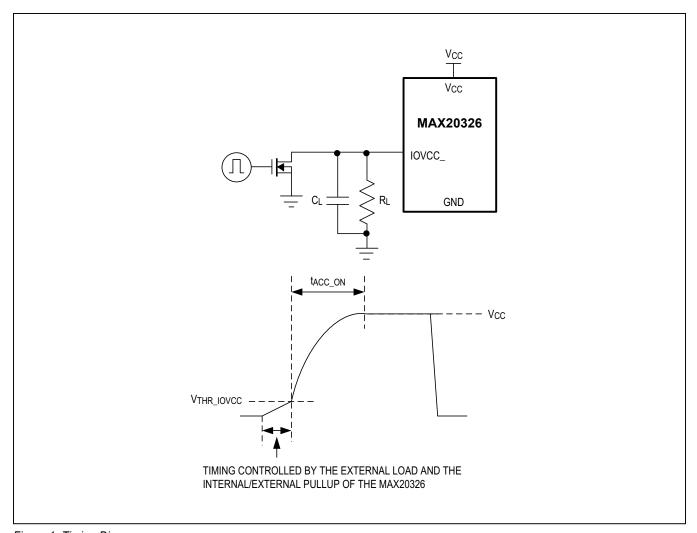

Figure 1. Timing Diagram

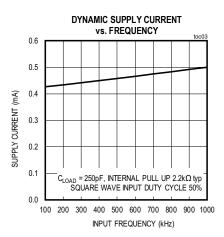

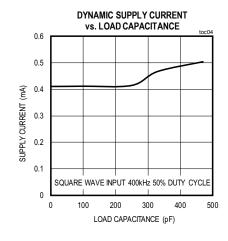

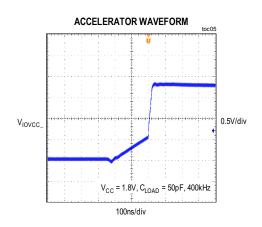

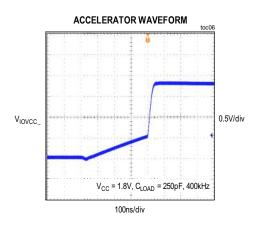

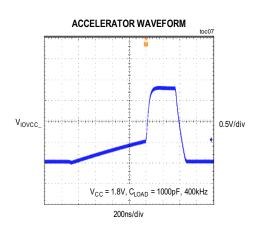

# **Typical Operating Characteristics**

( $V_{CC}$  = 1.8V,  $T_A$  = +25°C, unless otherwise noted.)

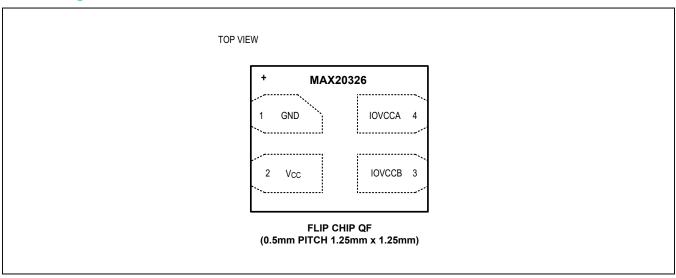

# **Pin Configuration**

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                   |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| 1   | GND             | Ground                                                                                                                     |

| 2   | V <sub>CC</sub> | $V_{CC}$ Supply Input. Bypass $V_{CC}$ with a ceramic capacitor 0.1 $\mu$ F or greater as close as possible to the device. |

| 3   | IOVCCB          | Input/Output Channel B. Reference to V <sub>CC</sub> .                                                                     |

| 4   | IOVCCA          | Input/Output Channel A. Reference to V <sub>CC</sub> .                                                                     |

www.maximintegrated.com Maxim Integrated | 6

### **Detailed Description**

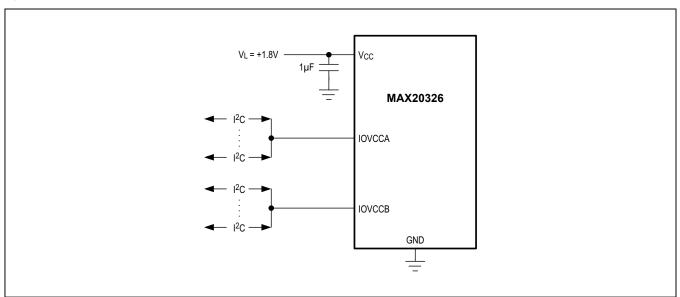

The MAX20326 is a precision input/output accelerator. The MAX20326 provides the precision pullup resistance to the IOVCC\_ line. When the IOVCC\_ transitions from logic-low to logic-high, the slope-adjusted accelerator kicks in to optimize the turn-on time to cope with various load capacitance. The device is optimized for an open-drain and high-speed operation, such as I<sup>2</sup>C bus, MDIO bus, or 1-wire bus. The device features a precision ±10% accurate internal pullup on each IOVCC\_ line.

### **High-Speed Operation**

The MAX20326 assists the system with meeting the requirements of high-speed, open-drain operation. The maximum data rate is at least 1MHz for open-drain operation, with the total bus capacitance up to 1000pF. The maximum operating frequency is limited by the load capacitance, the internal/external pullup used on the IOVCC\_line, accelerator pulse duration, and the minimum IOVCC low-pulse duration.

## **Typical Application Circuit**

# **Ordering Information**

| PART          | INTERNAL PULLUP | TOP MARK | TEMP RANGE     | PIN-PACKAGE |

|---------------|-----------------|----------|----------------|-------------|

| MAX20326EFS+T | 2.2kΩ           | AA       | -40°C TO +85°C | 4 FC QFN    |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

# **Chip Information**

PROCESS: BICMOS

T = Tape and reel.

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 12/17         | Initial release | _                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.