### **General Description**

The MAX9742 stereo Class D audio power amplifier delivers up to 2 x 16W into  $4\Omega$  loads. The MAX9742 features high-power efficiency (92% with  $8\Omega$  loads), eliminating the need for a bulky heatsink and conserving power. The MAX9742 operates from a 20V to 40V single supply or a ±10V to ±20V dual supply. Features include fully differential inputs, comprehensive click-and-pop suppression, low-power shutdown mode, and an externally adjustable gain. Short-circuit and thermal-overload protection prevent the device from being damaged during a fault condition.

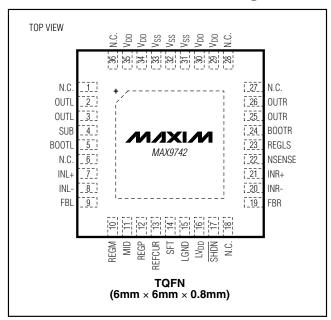

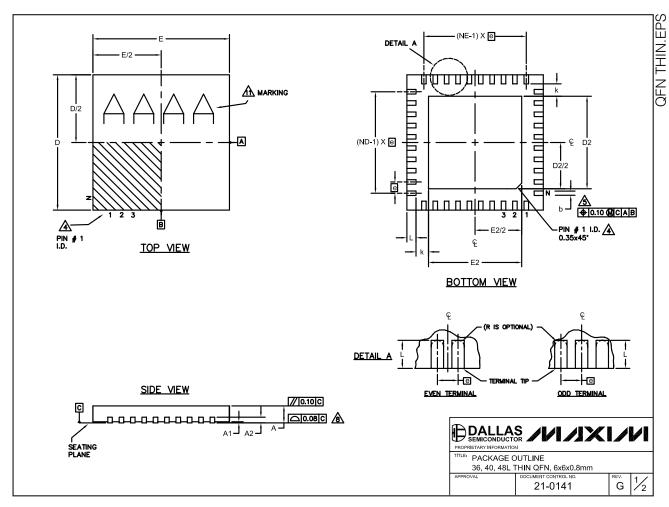

The MAX9742 is available in a thermally efficient 36-pin TQFN (6mm x 6mm x 0.8mm) package and is specified over the -40°C to +85°C extended temperature range.

### **Applications**

CRT TVs

Flat-Panel Display TVs

Audio Docking Stations

Multimedia Monitors

#### **Features**

- ♦ 2 x 16W Output Power (R<sub>L</sub> =  $4\Omega$ , THD+N = 10%)

- ♦ High Efficiency: Up to 92% with R<sub>L</sub> = 8Ω

- ♦ Mute and Shutdown Modes

- **♦ Differential Inputs Suppress Common-Mode Noise**

- ♦ Adjustable Gain

- ♦ Integrated Click-and-Pop Suppression

- ♦ Low 0.06% THD+N at 3.5W,  $R_L = 8\Omega$

- ♦ Output Short-Circuit and Thermal Protection

- ♦ Available in Space-Saving, 6mm x 6mm, 36-Pin TQFN Package

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE | PKG<br>CODE |

|-------------|----------------|-------------|-------------|

| MAX9742ETX+ | -40°C to +85°C | 36 TQFN-EP* | T3666-3     |

<sup>+</sup>Denotes lead-free package.

Pin Configuration located at end of data sheet.

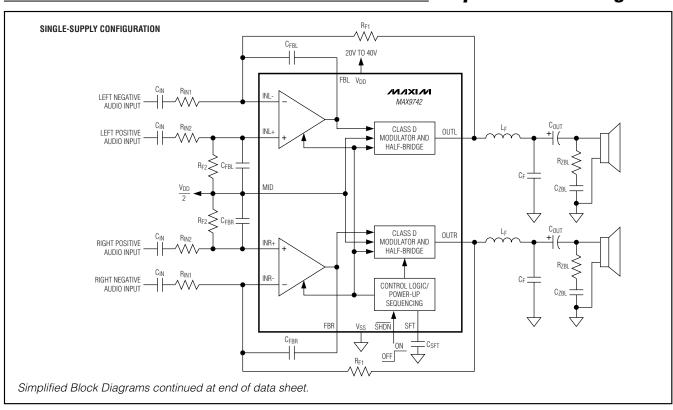

### Simplified Block Diagrams

MIXIM

Maxim Integrated Products

<sup>\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to V <sub>SS</sub> , NSENSEMID, LGND, LV <sub>DD</sub> , REGM, REGP, OUTR, | 0.3V to +45V           | Сс  |

|--------------------------------------------------------------------------------------------|------------------------|-----|

| OUTL to V <sub>SS</sub>                                                                    | 0.3V to +45V           |     |

| MID, LGND, LVDD, REGM, REGP, OUTR,                                                         |                        |     |

| OUTL to V <sub>DD</sub>                                                                    | 45V to +0.3V           |     |

| REGLS to V <sub>SS</sub>                                                                   | 0.3V to +12V           | Ju  |

| MID to REGP, REGM(VREGM - 0.3V)                                                            | to (VREGP + 0.3V)      |     |

| REGP to REGM                                                                               | 0.3V to +12V           |     |

| LV <sub>DD</sub> to LGND                                                                   | 0.3V to +6V            |     |

| SHDN to LGND                                                                               | 0.3V to +4V            |     |

| SFT to LGND                                                                                | 0.3V to +6V            | Ju  |

| FB_, IN_+, IN, REFCUR to REGP,                                                             |                        | Op  |

| REGM(V <sub>REGM</sub> - 0.3V)                                                             | to $(V_{REGP} + 0.3V)$ | Ma  |

| BOOTR to OUTR                                                                              | 0.3V to +12V           | Sto |

| BOOTL to OUTL                                                                              | 0.3V to +12V           | Le  |

| OUTR, OUTL Shorted to LGND                                                                 | Continuous             |     |

|                                                                                            |                        |     |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) (Note 1)<br>Single-Layer Board: |      |

|---------------------------------------------------------------------------------------|------|

| 36-Pin TQFN (derate 26.3mW/°C above +70°C)2.                                          | 11W  |

| Multilayer Board:                                                                     |      |

| 36-Pin TQFN (derate 35.7mW/°C above +70°C)2.                                          | 86W  |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )                             |      |

| Single-Layer Board:                                                                   |      |

| 36-Pin TQFN38°                                                                        | 'C/W |

| Multilayer Board:                                                                     |      |

| 36-Pin TQFN28°                                                                        | 'C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )1.4°                            | 'C/W |

| Operating Temperature Range40°C to +8                                                 | 35°C |

| Maximum Junction Temperature+15                                                       | 50°C |

| Storage Temperature Range65°C to +15                                                  | 50°C |

| Lead Temperature (soldering, 10s)+30                                                  |      |

|                                                                                       |      |

Note 1: Actual power capabilities are dependent on PCB layout. See the Thermal Considerations section.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS—Single-Supply, Single-Ended Output**

$(V_{DD} = 24V, V_{SS} = V_{SUB} = LGND = 0V, V_{\overline{SHDN}} = 3.3V, V_{MID} = 12V, C_{VDD} = 660\mu\text{F}, C_{MID1} = 10\mu\text{F}, C_{MID2} = 10\mu\text{F}, R1 = R2 = R3 = 10k\Omega, C_{SFT} = 0.47\mu\text{F}, C_{OUT} = 1000\mu\text{F}, C_{FB\_1} = 150p\text{F}, C_{FB\_2} = 10p\text{F}, C_{BOOT} = 0.1\mu\text{F}, C_{REGP} = C_{REGM} = 1\mu\text{F}, R_{IN\_} = 30.1k\Omega, R_{F1A} = 121k\Omega, R_{F1B} = 562k\Omega, R_{F2} = 681k\Omega, R_{REF} = 68k\Omega, R_{L} = \infty, T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}\text{C}. ) \text{ (Note 2)}$

| PARAMETER                                   | SYMBOL          | CONDITIONS                                                          | MIN | TYP  | MAX | UNITS |

|---------------------------------------------|-----------------|---------------------------------------------------------------------|-----|------|-----|-------|

| Supply Voltage Range                        | V <sub>DD</sub> | (Note 3)                                                            |     |      | 40  | V     |

| Supply Current                              | I <sub>DD</sub> | No load, output filter removed                                      |     | 15   |     | mA    |

| Mute Mode Supply Current                    |                 | No load, V <sub>SFT</sub> = 0V (outputs not switching)              |     | 8    |     | mA    |

| Shutdown Current                            |                 | No load, VSHDN = 0V                                                 |     | 0.8  | 1.3 | mA    |

| Switching Frequency                         | fsw             |                                                                     |     | 300  |     | kHz   |

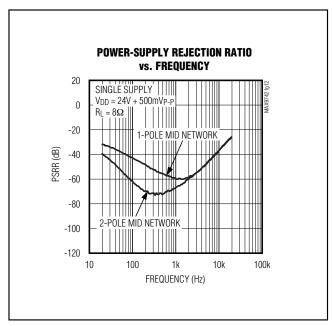

| Power-Supply Rejection Ratio (Note 4)       | PSRR            | V <sub>DD</sub> = 24V + 500mV <sub>P-P</sub> , f = 1kHz             |     | 68   |     | dB    |

| Crosstalk<br>(Notes 5 and 6)                |                 | L to R, R to L, $R_L = 8\Omega$ , $P_{OUT} = 1W$ , $f = 1kHz$       |     | -78  |     | dB    |

|                                             |                 | $R_L = 8\Omega$ , $f_{IN} = 1$ kHz, $T$ HD+ $N = 10$ %              |     | 9.5  |     |       |

| Continuous Output Power (Notes 5, 6, and 7) | Роит            | $R_L = 8\Omega$ , $f_{IN} = 1kHz$ , $THD+N = 10\%$ , $V_{DD} = 35V$ |     | 20.5 |     | W     |

|                                             |                 | $R_L = 4\Omega$ , $f_{ N} = 1$ kHz, $THD+N = 10\%$                  |     | 16   |     |       |

| Efficiency (Notes 5, 6, and 7)              |                 | $R_L = 8\Omega$ , $P_{OUT} = 9.5W$ , $THD+N = 10\%$                 |     | 92   |     | %     |

### **ELECTRICAL CHARACTERISTICS—Single-Supply, Single-Ended Output (continued)**

$(V_{DD} = 24V, V_{SS} = V_{SUB} = LGND = 0V, V_{\overline{SHDN}} = 3.3V, V_{MID} = 12V, C_{VDD} = 660\mu\text{F}, C_{MID1} = 10\mu\text{F}, C_{MID2} = 10\mu\text{F}, R1 = R2 = R3 = 10k\Omega, C_{SFT} = 0.47\mu\text{F}, C_{OUT} = 1000\mu\text{F}, C_{FB\_1} = 150p\text{F}, C_{FB\_2} = 10p\text{F}, C_{BOOT} = 0.1\mu\text{F}, C_{REGP} = C_{REGM} = 1\mu\text{F}, R_{IN\_} = 30.1k\Omega, R_{F1A} = 121k\Omega, R_{F1B} = 562k\Omega, R_{F2} = 681k\Omega, R_{REF} = 68k\Omega, R_{L} = \infty, T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}\text{C}. ) \text{ (Note 2)}$

| PARAMETER                                 | SYMBOL               | CONDITIONS                                              |                                    | MIN | TYP  | MAX | UNITS    |

|-------------------------------------------|----------------------|---------------------------------------------------------|------------------------------------|-----|------|-----|----------|

| Total Harmonic Distortion Plus            | TUD . N              | $f_{IN} = 1kHz$ ,<br>BW = 22Hz to 22kHz                 | $R_L = 8\Omega$ , $P_{OUT} = 3.5W$ |     | 0.06 |     | . %      |

| Noise                                     | THD+N                | (Notes 5, 6, and 7)                                     | $R_L = 4\Omega$ , $P_{OUT} = 5W$   |     | 0.08 |     | %        |

|                                           | ONID                 | $P_{OUT} = 9.5W$ , $R_L = 8\Omega$ ,                    | Unweighted                         |     | 88   |     | <u>.</u> |

| Signal-to-Noise Ratio                     | SNR                  | BW = 22Hz to 22kHz<br>(Notes 5 and 6)                   | A-weighted                         |     | 93   |     | dB       |

| Half-Bridge Switch<br>On-Resistance       | R <sub>DS</sub> (ON) |                                                         |                                    |     | 0.4  | 0.7 | Ω        |

| Switch Rise and Fall Times                |                      | No load (Note 4)                                        |                                    |     | 50   |     | ns       |

| IN_ Input Bias Current                    |                      |                                                         |                                    |     |      | +1  | μΑ       |

| MID Input Bias Current                    | I <sub>MID</sub>     | V <sub>DD</sub> = 24V, no load                          |                                    |     |      | 50  | μΑ       |

| Shutdown-to-Full Operation                | tson                 |                                                         |                                    |     | 68   |     | ms       |

| Power-On to Full Operation                | tpU                  | V <sub>SHDN</sub> = 3.3V                                |                                    |     | 1.5  |     | S        |

| Thermal-Overload Threshold<br>Temperature | T <sub>SH</sub>      | Junction temperature                                    | Junction temperature               |     | 150  |     | °C       |

| Short-Circuit Output Current              | Isc                  | OUT_ shorted to V <sub>DD</sub> or V                    | /ss                                | 2.9 | 4.5  |     | Α        |

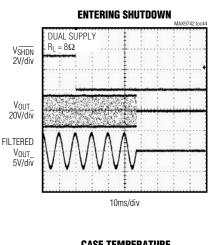

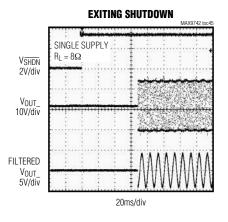

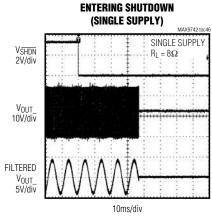

| Click-and-Pop                             | KCP                  | Peak voltage, 32-samples                                | Into shutdown                      |     | -38  |     | dBV      |

| Click-aliu-rop                            | KCb                  | per second, A-weighted (Notes 4 and 8)  Out of shutdown |                                    |     | -40  |     | иву      |

| DIGITAL INPUTS (SHDN) (Not                | e 9)                 |                                                         |                                    |     |      |     |          |

| Logic-Input Low Voltage                   | V <sub>IL</sub>      |                                                         |                                    |     |      | 0.4 | V        |

| Logic-Input High Voltage                  | VIH                  |                                                         |                                    | 2.4 |      |     | V        |

| Input Leakage Current                     |                      |                                                         |                                    | -1  |      | +1  | μΑ       |

### **ELECTRICAL CHARACTERISTICS—Dual Supplies**

$(V_{DD}=15V, V_{SS}=V_{SUB}=-15V, V_{\overline{SHDN}}=3.3V, V_{MID}=LGND=0V, C_{VDD}=C_{VSS}=1000\mu F, C_{BYP}=1\mu F, C_{SFT}=0.22\mu F, C_{FB\_1}=150 \mu F, C_{FB\_2}=10 \mu F, C_{BOOT}=0.1 \mu F, C_{REGP}=C_{REGM}=1 \mu F, R_{IN\_}=30.1 k\Omega, R_{F1A}=121 k\Omega, R_{F1B}=562 k\Omega, R_{F2}=681 k\Omega, R_{REF}=68 k\Omega, R_{L}=\infty, T_{A}=T_{MIN} \ to T_{MAX}, unless otherwise noted. Typical values are at T_{A}=+25 ^{\circ}C.) \ (Note 2)$

| PARAMETER                            | SYMBOL          | CONDITIONS                                             | MIN | TYP | MAX | UNITS |

|--------------------------------------|-----------------|--------------------------------------------------------|-----|-----|-----|-------|

| Positive Supply Voltage Range        | V <sub>DD</sub> | (Note 3)                                               | 10  |     | 20  | V     |

| Negative Supply Voltage<br>Range     | V <sub>SS</sub> | (Note 3)                                               | -20 |     | -10 | V     |

| Positive Supply Mute Mode<br>Current |                 | No load, VSFT = 0V (outputs not switching)             |     | 8   | 11  | mA    |

| Negative Supply Mute Mode<br>Current |                 | No load, V <sub>SFT</sub> = 0V (outputs not switching) | -12 | -8  |     | mA    |

### **ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)**

$(V_{DD}=15V,V_{SS}=V_{SUB}=-15V,V_{\overline{SHDN}}=3.3V,V_{MID}=LGND=0V,C_{VDD}=C_{VSS}=1000\mu\text{F},C_{BYP}=1\mu\text{F},C_{SFT}=0.22\mu\text{F},C_{FB}\_1=150p\text{F},C_{FB}\_2=10p\text{F},C_{BOOT}=0.1\mu\text{F},C_{REGP}=C_{REGM}=1\mu\text{F},R_{IN}\_=30.1k\Omega,R_{F1A}=121k\Omega,R_{F1B}=562k\Omega,R_{F2}=681k\Omega,R_{REF}=68k\Omega,R_{L}=\infty,T_{A}=T_{MIN}\text{ to }T_{MAX},\text{ unless otherwise noted. Typical values are at }T_{A}=+25^{\circ}\text{C.})$  (Note 2)

| PARAMETER                           | SYMBOL          | CONDITIONS                                                             |                                                               |                                           | MIN | TYP   | MAX | UNITS   |  |

|-------------------------------------|-----------------|------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|-----|-------|-----|---------|--|

| Positive Supply Current             | I <sub>DD</sub> | No load, output filter removed                                         |                                                               |                                           |     | 23    | 36  | mA      |  |

| Negative Supply Current             | I <sub>SS</sub> | No load, output filte                                                  | No load, output filter removed                                |                                           | -36 | -23   |     | mA      |  |

| Positive Supply Shutdown<br>Current |                 | No load, $\sqrt{SHDN} = 0$                                             | )V                                                            |                                           |     | 0.001 | 1   | μA      |  |

| Negative Supply Shutdown<br>Current |                 | No load, VSHDN = 0                                                     | )V                                                            |                                           | -1  | -0.03 |     | μA      |  |

| Output Offset Voltage               |                 | Output referred, affortolerances (Note 4)                              |                                                               | by R <sub>IN</sub> _ and R <sub>F</sub> _ |     | 5     | 30  | mV      |  |

| IN_ Input Bias Current              |                 |                                                                        |                                                               |                                           | -1  |       | +1  | μΑ      |  |

|                                     |                 | $V_{DD} = 10V \text{ to } 20V$                                         |                                                               |                                           |     | 97    |     |         |  |

| Power-Supply Rejection Ratio        | PSRR            | Vss = -10V to -20V                                                     |                                                               |                                           |     | 100   |     | al D    |  |

| (Note 4)                            | PORR            | $V_{DD} = 15V + 500m^{\circ}$                                          | V <sub>P-P</sub> , f                                          | = 1kHz                                    |     | 67    |     | dB      |  |

|                                     |                 | $V_{SS} = -15V + 500 \text{mV}_{P-P}, f = 1 \text{kHz}$                |                                                               |                                           |     | 64    |     | 1       |  |

| Crosstalk<br>(Notes 5 and 6)        |                 | L to R, R to L, $R_L =$                                                | L to R, R to L, $R_L = 8\Omega$ , $P_{OUT} = 1W$ , $f = 1kHz$ |                                           |     | -61   |     | dB      |  |

|                                     |                 |                                                                        | R <sub>L</sub> =                                              | 8Ω                                        |     | 14    |     |         |  |

| Continuous Output Power             | Pout            | f <sub>IN</sub> = 1kHz,<br>THD+N = 10%                                 |                                                               | 21                                        |     | W     |     |         |  |

|                                     |                 | (Notes 5, 6, and 7) $R_L = 4\Omega$ , $V_{DD} = 12V$ , $V_{SS} = -12V$ |                                                               | 9.5                                       |     |       |     |         |  |

| Efficiency<br>(Notes 5, 6, and 7)   |                 | $R_L = 8\Omega$ , $P_{OUT} = 15$                                       | 5W, TH                                                        | ID+N = 10%                                |     | 93    |     | %       |  |

| Total Harmonic Distortion           |                 | f <sub>IN</sub> = 1kHz,                                                |                                                               | $R_L = 8\Omega$ , $P_{OUT} = 5W$          |     | 0.06  |     |         |  |

| Plus Noise                          | THD+N           | BW = 22Hz to 22kH<br>(Notes 5, 6, and 7)                               | łZ                                                            | $R_L = 4\Omega$ , $P_{OUT} = 10W$         |     | 0.08  |     | %       |  |

|                                     |                 | P <sub>OUT</sub> = 14W,                                                |                                                               | Unweighted                                |     | 89    |     |         |  |

| <u> </u>                            |                 | $R_L = 8\Omega$ , BW = 22H<br>22kHz (Notes 5 and                       |                                                               | A-weighted                                |     | 94    |     | dB      |  |

| Shutdown-to-Full Operation          | tson            |                                                                        |                                                               |                                           | 68  |       | ms  |         |  |

| Short-Circuit Output Current        | Isc             | OUT_ shorted to V <sub>DD</sub> or V <sub>SS</sub>                     |                                                               | 2.9                                       | 4.5 |       | Α   |         |  |

| Click and Dan                       | IZ :            | Peak voltage, 32-sai                                                   |                                                               | Into shutdown                             |     | -36   |     | المال ا |  |

| Click-and-Pop                       | KCP             | per second, A-weigl<br>(Notes 4 and 8)                                 | niea                                                          | Out of shutdown                           |     | -36   |     | dBV     |  |

NIXIN

### **ELECTRICAL CHARACTERISTICS—Single-Supply, BTL Configuration**

$(V_{DD} = 24V, V_{SS} = V_{SUB} = LGND = 0V, V_{\overline{SHDN}} = 3.3V, V_{MID} = 12V, C_{VDD} = 660\mu F, C_{MID1} = 10\mu F, C_{MID2} = 10\mu F, R1 = R2 = R3 = 10kΩ, C_{SFT} = 0.47\mu F, C_{OUT} = 1000\mu F, C_{FB}_1 = 150p F, C_{FB}_2 = 10p F, C_{BOOT} = 0.1\mu F, C_{REGP} = C_{REGM} = 1\mu F, R_{IN}_ = 30.1kΩ, R_{F1A} = 121kΩ, R_{F1B} = 562kΩ, R_{F2} = 681kΩ, R_{REF} = 68kΩ, R_{L} = ∞, T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                     | SYMBOL | CONDIT                                                                                       | MIN TY                                                               | P MAX | UNITS |     |

|---------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------|-------|-----|

| Output Offset Voltage                                         |        | (Note 4)                                                                                     | 7                                                                    | 7     | mV    |     |

| Power-Supply Rejection Ratio                                  | PSRR   | V <sub>DD</sub> = 20V to 40V                                                                 | / <sub>DD</sub> = 20V to 40V                                         |       |       | dB  |

| (Note 4)                                                      | FORR   | $V_{DD} = 24V + 500mV_{P-P}, f =$                                                            | : 1kHz                                                               | 7     | 7     | αь  |

| Continuous Output Power                                       | Pout   | $R_L = 8\Omega$ , $f_{IN} = 1$ kHz, THD+ (Notes 6, 10, and 11)                               | N = 10%,                                                             | 3     | 2     | W   |

| Efficiency                                                    |        | $R_L = 8\Omega$ , $P_{OUT} = 10W$ , THE (Notes 5 and 6)                                      | $R_L = 8\Omega$ , $P_{OUT} = 10W$ , $THD+N = 10\%$ , (Notes 5 and 6) |       | 3     | %   |

| Total Harmonic Distortion Plus<br>Noise (Notes 6, 10, and 11) | THD+N  | $f_{IN}$ = 1kHz, BW = 22Hz to 22kHz,<br>R <sub>L</sub> = 8 $\Omega$ , P <sub>OUT</sub> = 10W |                                                                      | 0.0   | 08    | %   |

|                                                               |        | $P_{OUT} = 32W, R_L = 8\Omega,$                                                              | Unweighted                                                           | 9     | 0     |     |

| Signal-to-Noise Ratio                                         | SNR    | BW = 22Hz to 22kHz<br>(Notes 6, 10, and 11)                                                  | A-weighted                                                           | 9     | 6     | dB  |

| Shutdown-to-Full Operation                                    | tson   | <u> </u>                                                                                     |                                                                      | 6     | 8     | ms  |

| Click-and-Pon                                                 | KCP    | Peak voltage, 32-samples per second, A-weighted                                              | Into shutdown                                                        | -4    | .7    | dBV |

| Click-and-Pop                                                 | NOP    | (Notes 4, 11, and 12)                                                                        | Out of shutdown                                                      | -3    | 2     | GDV |

- Note 2: All devices are 100% production tested at +25°C. All temperature limits are guaranteed by design.

- **Note 3:** Supply pumping may occur at high output powers with low audio frequencies. Use proper supply bypassing to prevent the device from entering overvoltage protection due to supply pumping. See the *Supply Pumping Effects* and the *Supply Undervoltage and Overvoltage Protection* sections.

- Note 4: Amplifier inputs AC-coupled to ground.

- Note 5: For  $R_L = 4\Omega$ ,  $L_F = 22\mu H$  and  $C_F = 0.68\mu F$ . For  $R_L = 6\Omega$ ,  $L_F = 33\mu H$  and  $C_F = 0.47\mu F$ . For  $R_L = 8\Omega$ ,  $L_F = 47\mu H$  and  $C_F = 0.33\mu F$ .

- **Note 6:** Testing performed with four-layer PCB.

- Note 7: Both channels driven in phase.

- Note 8: Testing performed with an 8Ω resistor connected between LC filter output and ground. Mode transitions are controlled by SHDN. K<sub>CP</sub> level is calculated as 20log[(peak voltage during mode transition, no input signal) / 1V<sub>RMS</sub>].

- Note 9: Digital input specifications apply to both single-supply and dual-supply operation.

- Note 10: Channels driven 180° out-of-phase. Load connected between LC filter outputs.

- **Note 11:**  $L_F = 22\mu H$  and  $C_F = 0.68\mu F$ .

- Note 12: Testing performed with an 8Ω resistor connected between LC filter outputs. Mode transitions are controlled by SHDN. KCP level is calculated as 20log[(peak voltage during mode transition, no input signal) / 1V<sub>RMS</sub>].

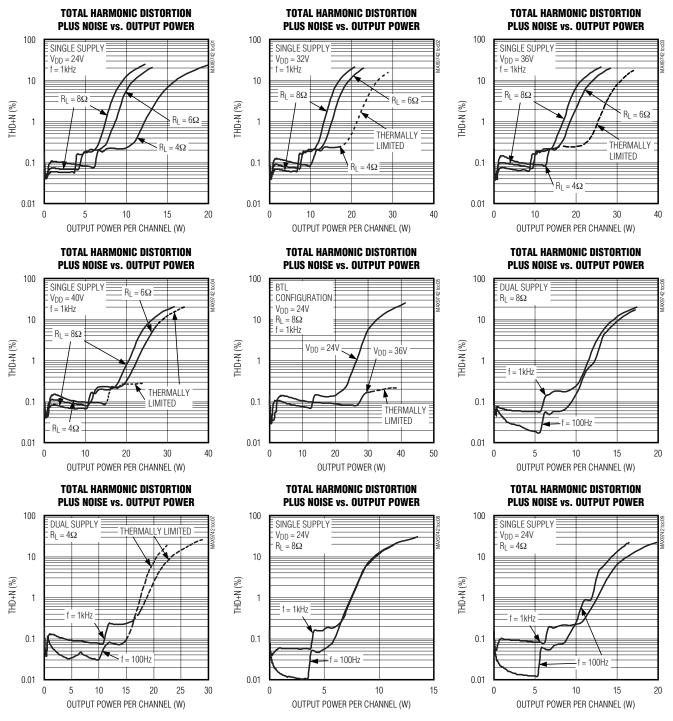

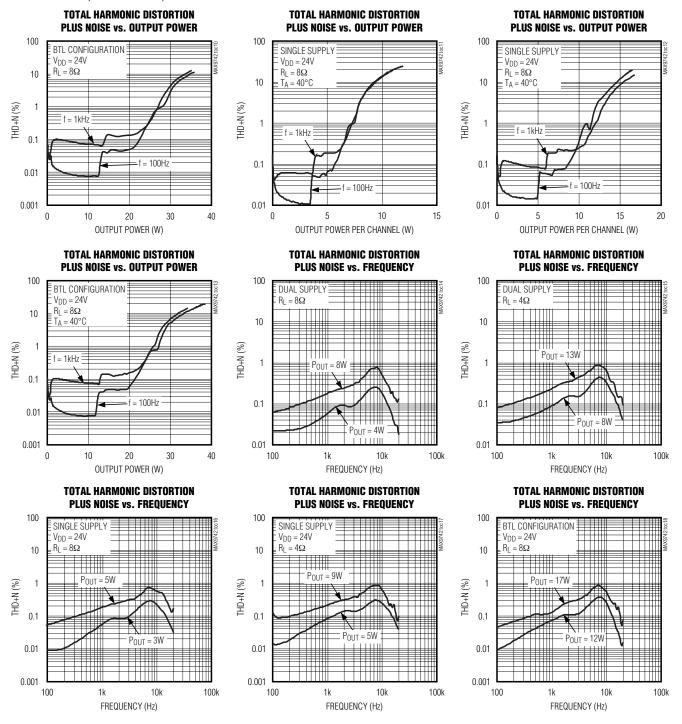

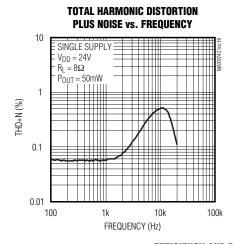

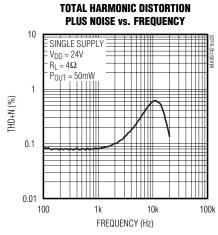

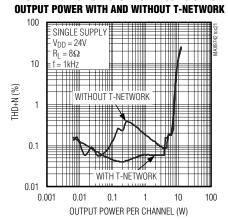

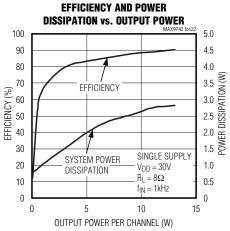

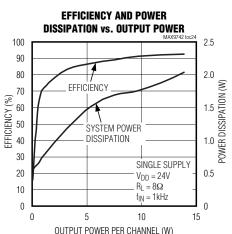

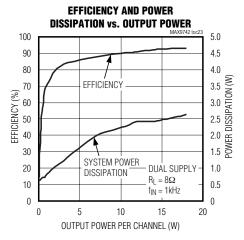

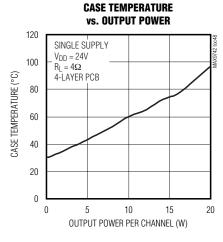

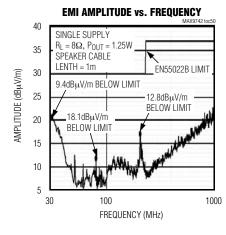

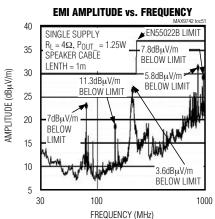

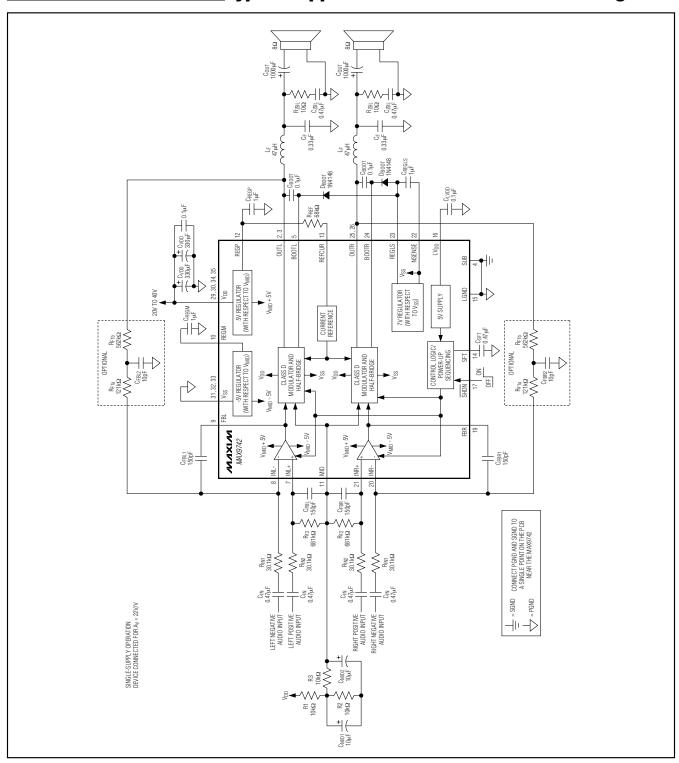

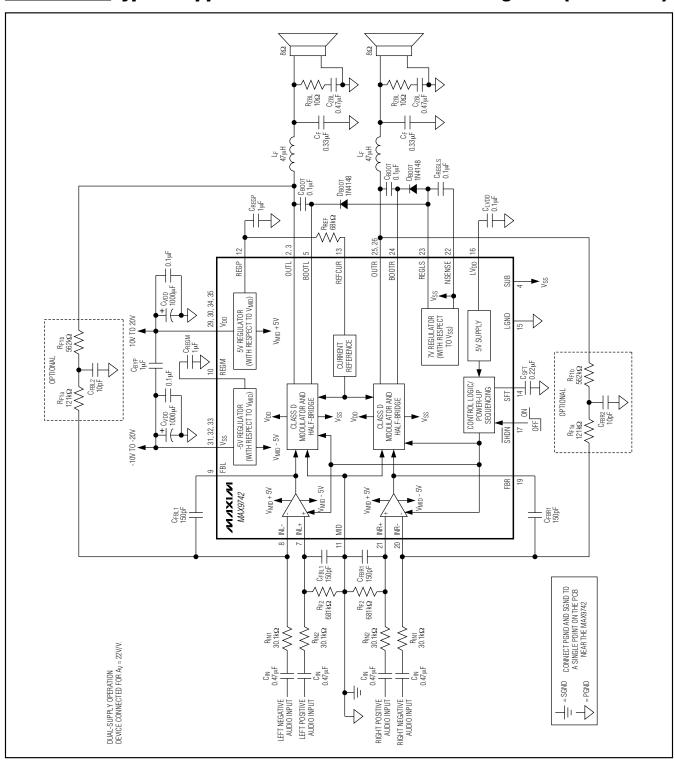

### **Typical Operating Characteristics**

(24V single-supply mode,  $\pm 15$ V dual-supply mode, both channels driven in phase, THD+N measurement bandwidth = 22Hz to 22kHz,  $T_A = +25$ °C, unless otherwise noted. See Figure 1 for test circuits, see *Typical Application Circuits/Functional Diagrams* for test circuit component values.)

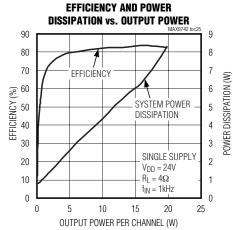

### Typical Operating Characteristics (continued)

(24V single-supply mode,  $\pm$ 15V dual-supply mode, both channels driven in phase, THD+N measurement bandwidth = 22Hz to 22kHz,  $T_A = +25^{\circ}$ C, unless otherwise noted. See Figure 1 for test circuits, see *Typical Application Circuits/Functional Diagrams* for test circuit component values.)

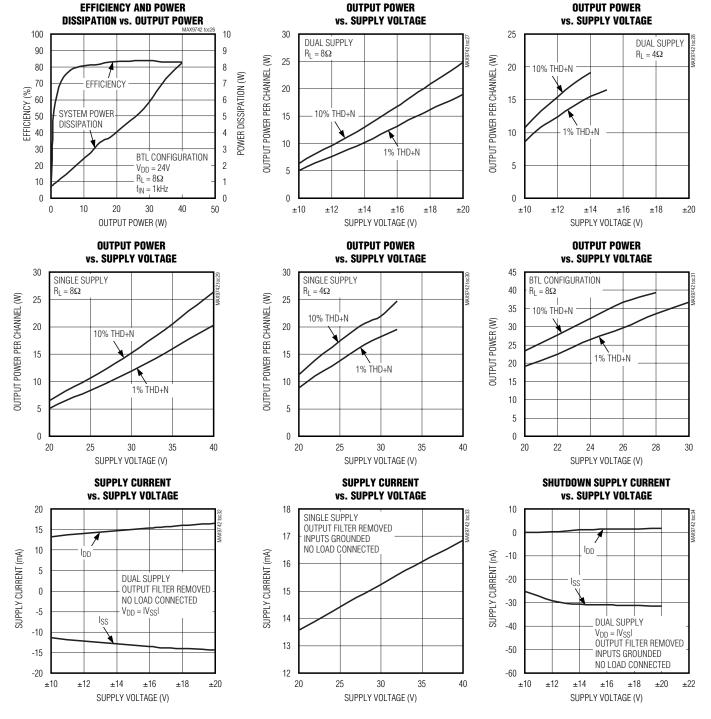

### Typical Operating Characteristics (continued)

(24V single-supply mode,  $\pm$ 15V dual-supply mode, both channels driven in phase, THD+N measurement bandwidth = 22Hz to 22kHz,  $T_A = +25^{\circ}$ C, unless otherwise noted. See Figure 1 for test circuits, see *Typical Application Circuits/Functional Diagrams* for test circuit component values.)

TOTAL HARMONIC DISTORTION PLUS NOISE vs.

### Typical Operating Characteristics (continued)

(24V single-supply mode,  $\pm 15$ V dual-supply mode, both channels driven in phase, THD+N measurement bandwidth = 22Hz to 22kHz,  $T_A = +25$ °C, unless otherwise noted. See Figure 1 for test circuits, see *Typical Application Circuits/Functional Diagrams* for test circuit component values.)

### Typical Operating Characteristics (continued)

(24V single-supply mode,  $\pm$ 15V dual-supply mode, both channels driven in phase, THD+N measurement bandwidth = 22Hz to 22kHz,  $T_A = +25^{\circ}$ C, unless otherwise noted. See Figure 1 for test circuits, see *Typical Application Circuits/Functional Diagrams* for test circuit component values.)

### Typical Operating Characteristics (continued)

(24V single-supply mode,  $\pm 15$ V dual-supply mode, both channels driven in phase, THD+N measurement bandwidth = 22Hz to 22kHz,  $T_A = +25$ °C, unless otherwise noted. See Figure 1 for test circuits, see *Typical Application Circuits/Functional Diagrams* for test circuit component values.)

### **Pin Description**

| PIN                     | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 18,<br>27, 28, 36 | N.C.             | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2, 3                    | OUTL             | Left Speaker Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4                       | SUB              | Device Substrate. Connect SUB to VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5                       | BOOTL            | Left-Channel Bootstrap Capacitor Terminal. Connect a 0.1µF capacitor between BOOTL and OUTL.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7                       | INL+             | Left-Channel Positive Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8                       | INL-             | Left-Channel Negative Input. Connect an external feedback capacitor between INL- and FBL. See the Feedback Capacitor (CFB_) section.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9                       | FBL              | Left-Channel Feedback Capacitor Terminal. Connect an external feedback capacitor between FBL and INL See the <i>Feedback Capacitor (CFB_)</i> section.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10                      | REGM             | -5V Internal Regulator Output. Regulator output voltage is with respect to MID. Bypass REGM with a 1μF capacitor to signal ground plane (SGND). See the <i>Supply Bypassing/Layout</i> section.                                                                                                                                                                                                                                                                                                                                                           |

| 11                      | MID              | Midsupply Bias Voltage Input. The MID input biases the internal preamplifiers to the average value of the V <sub>DD</sub> and V <sub>SS</sub> supply inputs. For dual-supply operation, connect to the signal ground plane (SGND). For single-supply operation, apply a voltage to MID equal to 0.5 x V <sub>DD</sub> through an external resistive voltage-divider and decoupling network (see the <i>Setting V<sub>MID</sub></i> section). See the <i>Typical Application Circuits/Functional Diagrams</i> and <i>Supply Bypassing/Layout</i> sections. |

| 12                      | REGP             | 5V Internal Regulator Output. Regulator output voltage is with respect to MID. Bypass REGP with a 1µF capacitor to the signal ground plane (SGND). See the <i>Supply Bypassing/Layout</i> section.                                                                                                                                                                                                                                                                                                                                                        |

| 13                      | REFCUR           | Reference Current Resistor Terminal. Connect an external resistor from REFCUR to REGP to set the switching frequency and output short-circuit current-limit value. Use resistor values greater than or equal to $58k\Omega$ and less than or equal to $75k\Omega$ . See the Setting the Switching Frequency and Output Current Limit (RREF) section.                                                                                                                                                                                                      |

| 14                      | SFT              | Soft-Start Capacitor Terminal/Mute Input. Connect a 0.22µF capacitor between SFT and PGND to utilize the soft-start power-up sequence. Drive SFT low to mute the outputs.                                                                                                                                                                                                                                                                                                                                                                                 |

| 15                      | LGND             | Logic Ground. Connect LGND to signal ground (SGND) and power ground (PGND) planes. See the<br>Supply Bypassing/Layout section.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16                      | LV <sub>DD</sub> | Internal 5V Logic Supply. Bypass LVDD to LGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17                      | SHDN             | Active-Low Shutdown Input. Drive SHDN high for normal operation. Drive SHDN low to place the device into shutdown mode.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19                      | FBR              | Right-Channel Feedback Capacitor Terminal. Connect an external feedback capacitor between FBR and INR See the <i>Feedback Capacitor (CFB_)</i> section.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 20                      | INR-             | Right-Channel Negative Input. Connect an external feedback capacitor between INR- and FBR. See the Feedback Capacitor (CFB_) section.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21                      | INR+             | Right-Channel Positive Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22                      | NSENSE           | Negative Supply Sense Input. NSENSE is internally connected to V <sub>SS</sub> . Connect a 1µF bypass capacitor between NSENSE and REGLS.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23                      | REGLS            | 7V Internal Regulator Output. REGLS output voltage is with respect to V <sub>SS</sub> . Bypass REGLS with a 1μF capacitor to NSENSE.                                                                                                                                                                                                                                                                                                                                                                                                                      |

### **Pin Description (continued)**

| PIN               | NAME            | FUNCTION                                                                                                                                                                                                             |

|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24                | BOOTR           | Right-Channel Bootstrap Capacitor. Connect a 0.1µF capacitor between BOOTR and OUTR.                                                                                                                                 |

| 25, 26            | OUTR            | Right Speaker Output                                                                                                                                                                                                 |

| 29, 30,<br>34, 35 | $V_{DD}$        | Positive Power-Supply Input. Bypass V <sub>DD</sub> to LGND with a 0.1µF plus additional bulk capacitance. See the <i>Supply Pumping Effects</i> section.                                                            |

| 31, 32, 33        | V <sub>SS</sub> | Negative Power-Supply Input. For dual-supply operation, connect to negative power-supply voltage and bypass Vss to LGND with a 0.1µF plus additional bulk capacitance. For single-supply operation, connect to LGND. |

| EP                | EP              | Exposed Paddle. EP is internally connected to device substrate. Connect EP to V <sub>SS</sub> through a large section of copper to maximize power dissipation.                                                       |

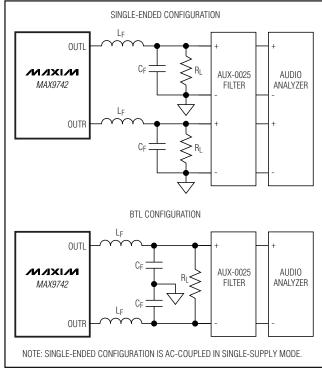

#### **Test Circuits**

Figure 1. Test Circuits for Single-Ended and BTL Configurations

### Detailed Description

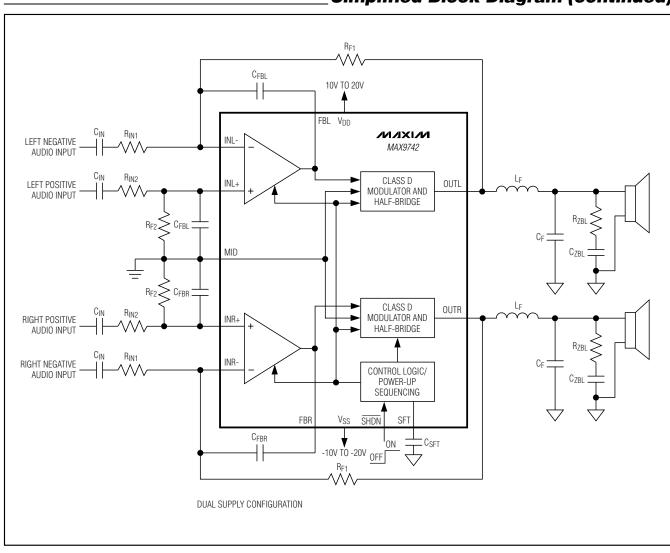

The MAX9742 is a two-channel, single-ended Class D stereo amplifier capable of providing 16W of output power on each channel into  $4\Omega$  loads in single- or dual-supply operation. The amplifier can also provide 32W of output power in a mono bridge-tied-load (BTL) configuration. The device offers Class AB audio performance with Class D efficiency.

The differential input architecture reduces commonmode noise pickup. The device can also be configured for single-ended input signals.

The connection of external feedback components allows custom gain settings.

#### **Class D Operation and Efficiency**

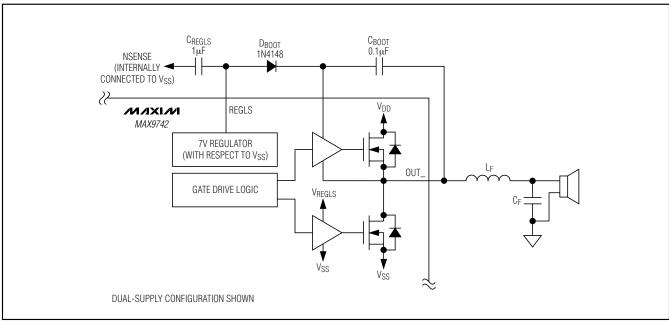

Class D amplifiers are switch-mode devices capable of significantly higher power efficiencies in comparison to linear amplifiers. The output stage of the MAX9742 consists of a half-bridge speaker driver (see Figure 2). The high efficiency of a Class D amplifier is attributed to the region of operation of the output stage transistors. In a Class D amplifier, the output transistors act as current-steering switches by switching the output between VDD and VSS (ground for single-supply operation). Any power loss associated with the Class D output stage is mostly due to the I²R loss of the MOSFET on-resistance and quiescent current overhead. The theoretical best

efficiency of a linear amplifier is 78%; however, that efficiency is only exhibited at peak output powers. Under normal operating levels (typical music reproduction levels), efficiency falls below 30%, whereas the MAX9742 still exhibits 80% efficiency under the same conditions.

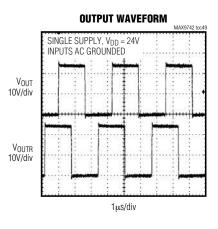

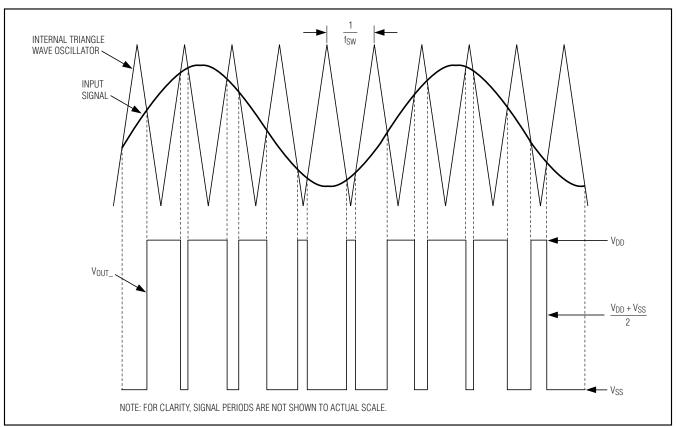

Since the output transistors switch the output to either VDD or VSS (ground for single-supply operation), the resulting output of a Class D amplifier is a high-frequency square wave. This square wave is pulse-width-modulated by the audio input signal. In the MAX9742, the pulse-width modulation (PWM) is accomplished by comparing the input audio signal to an internally generated triangle wave oscillator. The resulting duty cycle of

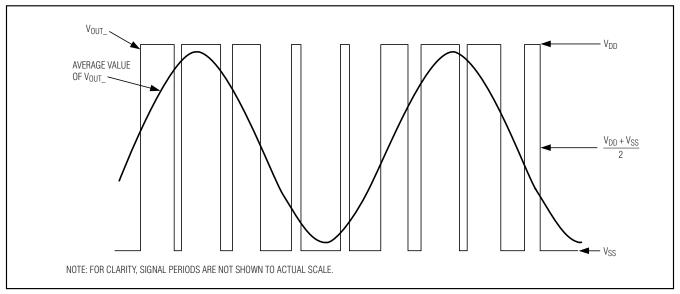

the square wave is proportional to the level of the input signal. When the input signal is at 0V, the duty cycle of the MAX9742 output is equal to 50%. To extract the amplified audio signal from this PWM waveform, the output of the MAX9742 is fed to an external LC lowpass filter (see the Single-Ended LC Output Filter Design (LF and CF) section). The LC filter works as an averaging circuit for the PWM output voltage waveform. The resulting averaged output voltage is equal to the amplified audio signal. Figure 3a illustrates the resulting PWM output waveform due to the varying input signal level, and Figure 3b shows the recovered amplified input signal after filtering.

Figure 2. Simplified Block Diagram of the MAX9742 Output Stage

Figure 3a. MAX9742 Output with an Applied Input Signal

Figure 3b. MAX9742 Output with Resulting Output After Filtering

#### Shutdown Mode

The MAX9742 features a low-power shutdown mode that reduces quiescent current consumption to less than 0.5mA in single-supply mode and less than 1 $\mu$ A in dual-supply mode. Drive SHDN low to place the device into shutdown mode. Connect SHDN to a logic-high for normal operation.

The maximum voltage that may be applied to the SHDN input is 4V (see the Absolute Maximum Ratings section). If the SHDN input must be controlled by a 5V logic signal, limit the maximum voltage that can be applied to the SHDN input to 4V through an external resistive divider.

#### Click-and-Pop Suppression

The MAX9742 features comprehensive click-and-pop suppression that minimizes audible transients on startup and shutdown. While in shutdown, the half-bridge output transistor switches are turned off, causing each output to go high impedance. During startup, or powerup, the input amplifiers are muted and an internal loop sets the modulator bias voltages to the correct levels, minimizing audible clicks and pops when the output half-bridge is enabled. The value of the soft-start capacitor, CSFT, affects the click-and-pop performance and startup time of the MAX9742 (see the Soft-Start Capacitor (CSFT) section). To maximize click-and-pop suppression when powering up an audio system, drive SHDN or SFT (see the Mute Function section) to 0V until the rest of the circuitry in the system has had enough time to stabilize. This ensures the MAX9742 is the last device to be activated in the system and prevents transients caused by circuitry preceding the MAX9742 from being amplified at the outputs.

#### **Mute Function**

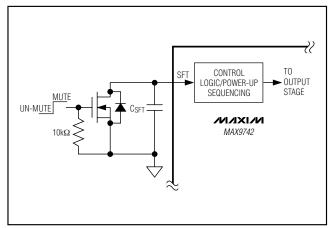

The MAX9742 features a clickless/popless mute mode. When the device is muted, the outputs stop switching, muting the speaker. The mute function only affects the output stage and does not shutdown the device. To mute the MAX9742, drive SFT to ground. Figure 4 shows how an external transistor (MOSFET or BJT) can be used to easily mute the MAX9742.

#### **Thermal-Overload Protection**

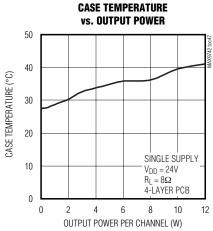

Thermal-overload protection limits total power dissipation in the MAX9742. When the junction temperature exceeds approximately +160°C, the thermal protection circuitry disables the amplifier output stage. The amplifiers are enabled once the junction temperature cools by approximately 15°C. This results in a pulsing output under continuous thermal-overload conditions.

#### Supply Undervoltage and Overvoltage Protection

The MAX9742 features an undervoltage protection function that prevents the device from operating if  $V_{DD}$  is less than +7V with respect to  $V_{MID}$  input or if  $V_{SS}$  is greater than -7V with respect to  $V_{MID}$ . This feature prevents improper operation when insufficient supply voltages are present. Once the supply voltage exceeds the undervoltage threshold, the MAX9742 is turned on and the amplifiers are powered, provided that  $\overline{SHDN}$  is high and the outputs are unmuted.

The MAX9742 also features an overvoltage protection function that prevents the device from operating if the potential difference between V<sub>DD</sub> and V<sub>SS</sub> exceeds +46V. This feature prevents the MAX9742 from damaging itself due to excessive supply pumping effects (see the *Supply Pumping Effects* section). The device returns to normal operation once the potential difference between V<sub>DD</sub> and V<sub>SS</sub> drops below +46V.

### Applications Information

#### **Output Dynamic Range**

Dynamic range is the difference between the noise floor of the system and the output level at 10% THD+N. It is essential that a system's dynamic range be known before setting the maximum output gain. Output clipping occurs if the output signal is greater than the dynamic range of the system.

Use the THD+N vs. Output Power graph in *Typical Operating Characteristics* to identify the system's dynamic range. Given the system's supply voltage, find the output power that causes 10% THD+N for a given load. Use the following equation to determine the peak-

Figure 4. MAX9742 Mute Circuit

to-peak output voltage that causes 10% THD+N for a given load.

$$V_{OUT\_P-P} = 2\sqrt{2(P_{OUT\_10\%} \times R_L)} (V)$$

where P<sub>OUT\_10%</sub> is the output power that causes 10% THD+N, R<sub>L</sub> is the load resistance, and V<sub>OUT\_P-P</sub> is the peak-to-peak output voltage. Determine the voltage gain (A<sub>V</sub>) necessary to attain this output voltage based on the maximum peak-to-peak input voltage (V<sub>IN\_P-P</sub>):

$$A_{V} = \frac{V_{OUT\_P-P}}{V_{IN\ P-P}} (V/V)$$

Set the closed-loop voltage gain of the MAX9742 less than or equal to Ay to prevent clipping of the output, unless audible clipping is acceptable for the application.

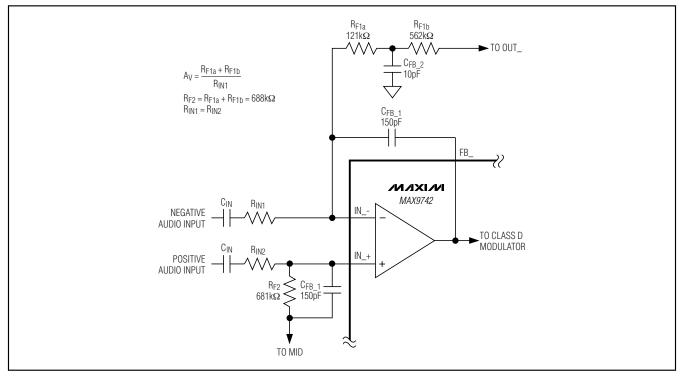

#### **Input Amplifier**

The external feedback networks of the MAX9742 input amplifiers allow custom gain settings while maximizing dynamic range. The input amplifiers also accommodate a variety of standard amplifier configurations including differential input, single-ended input, and summing amplifiers. Due to the output current limitations of the internal input amplifiers, always select feedback resistors (RF1, see the *Typical Application Circuits/Functional Diagrams*) with values greater than or equal to  $400k\Omega$ . To preserve gain accuracy, avoid using feedback resistors with values greater than  $1M\Omega$ . For proper operation, limit common-mode input voltages to  $\pm 3V$ .

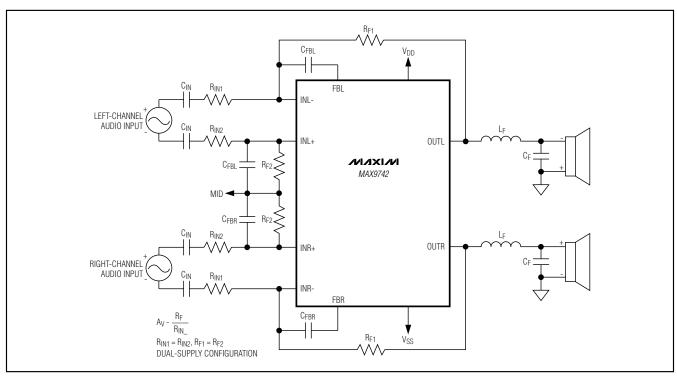

#### **Differential Input Configuration**

The Typical Application Circuits/Functional Diagrams show each channel of the MAX9742 configured as differential input amplifiers. A differential input offers improved noise immunity over a single-ended input. In systems that include high-speed digital circuitry, high-frequency noise can couple into the amplifier's input traces. The signals appear at the amplifier's input accommon-mode noise. A differential input amplifier amplifies the difference of the two inputs, and signals common to both inputs are subtracted out. When configured for differential inputs, the voltage gain of the MAX9742 is set by:

$$A_V = \frac{R_{F1}}{R_{IN1}} (V/V)$$

where A<sub>V</sub> is the desired voltage gain in V/V.  $R_{IN1}$  should be equal to  $R_{IN2}$ , and  $R_{F1}$  should be equal to  $R_{F2}$ .

When using the differential input configuration, the common-mode rejection ratio (CMRR) is primarily limited by the external resistor tolerances. Ideally, to achieve the highest possible CMRR, the resistors should be perfectly matched and the following condition should be met:

$$\frac{R_{F1}}{R_{IN1}} = \frac{R_{F2}}{R_{IN2}}$$

To ensure the MAX9742 input amplifiers operate as fully differential integrators, connect a capacitor between IN\_+ and MID whose value is equal to C<sub>F</sub> (see the *Feedback Capacitor (CFB\_)* section).

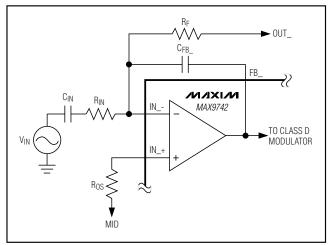

#### Single-Ended Input

Each channel of the MAX9742 can be configured as a single-ended input amplifier by connecting IN\_+ to MID (through an external resistor, Ros) and driving IN\_- with the input source (see Figure 5). In this configuration, the MAX9742 is configured as a single-ended amplifier whose voltage gain is equal to:

$$A_V = - \frac{R_F}{R_{IN}} (V/V)$$

where A<sub>V</sub> is the desired voltage gain in V/V.

To minimize output offset voltages due to input bias currents, connect a resistor, Ros, (see Figure 5) between IN $_+$  and MID. Select the value of Ros so that the DC resistances looking out of inputs of the amplifier (IN $_+$  and IN $_-$ ) are equal. For example, when using the dual-supply configuration with a DC-coupled input source, the value of Ros should be equal to RFIIRIN.

Figure 5. Single-Ended Input Configuration

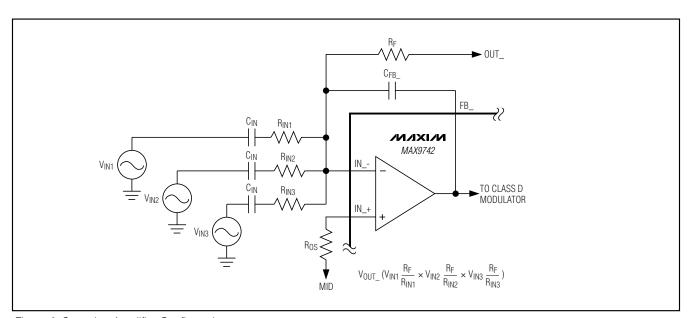

#### **Summing Configuration (Audio Mixer)**

Figure 6 shows the MAX9742 configured as a summing amplifier, which allows multiple audio sources to be linearly mixed together. Using this configuration, the output of the MAX9742 is equal to the weighted sum of the input signals:

$$V_{OUT_{-}} = - (V_{IN1} \frac{R_F}{R_{IN1}} + V_{IN2} \frac{R_F}{R_{IN2}} + V_{IN3} \frac{R_F}{R_{IN3}})$$

As shown in the above equation, the weighting or amount of gain applied to each input signal source is determined by the ratio of RF and the respective input resistor (R $_{\rm IN1}$ , R $_{\rm IN2}$ , R $_{\rm IN3}$ ) connected to each signal source. Select RF and R $_{\rm IN}$ \_ so that the dynamic range of the MAX9742 is not exceeded when the input signals are at their maximum values and in phase with each other (see the *Output Dynamic Range* section).

To minimize output offset voltages due to input bias currents, connect a resistor, ROS, (see Figure 6) between IN\_+ and MID. Select the value of ROS such that the DC resistances looking out of inputs of the amplifier (IN\_+ and IN\_-) are equal. For example, when using the dual-supply configuration with a DC-coupled input source, the value of ROS should be equal to RFIRIN1IIRIN2II IIRINn.

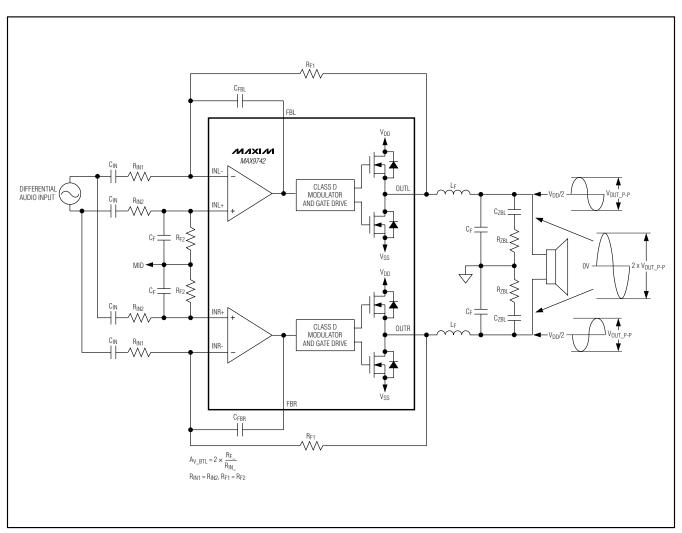

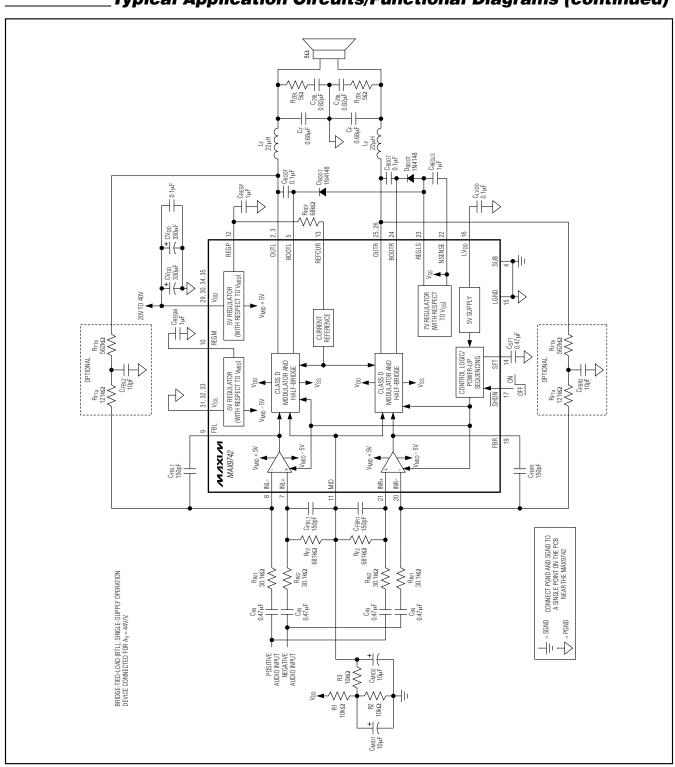

#### Mono Bridge-Tied-Load (BTL) Configuration

The MAX9742 also accommodates a mono bridge-tied-load (BTL) configuration that can be used in single-supply and dual-supply applications. In the BTL configuration, the speaker load is driven differentially by connecting the half-bridge outputs as a full H-bridge driver. To drive the speaker differentially, the inputs of both channels must be driven by the same audio signal with one channel 180° out-of-phase with the other channel. Figure 7 shows the connections required for BTL operation.

The advantages of BTL operation include reduced component count due to the elimination of the output-coupling capacitors when using single-supply operation, a 6dB increase in gain due to the load being driven differentially, increased output power into a single load, and the minimization of the supply-pumping since each half bridge is driven 180° out-of-phase (see the *Supply Pumping Effects* section). For single-supply applications, the output-coupling capacitors are not needed for BTL operation since the DC voltage present at each half-bridge output is equal in value and applies to each side of the load. This means no DC voltage appears across the load, and therefore, no DC current flows into the speaker.

Figure 6. Summing Amplifier Configuration

Since each half-bridge output stage is only capable of driving loads as small as  $4\Omega$  and each half-bridge sees half of the differential load resistance when configured for BTL, only use the BTL configuration with loads greater than or equal to  $8\Omega.$  The MAX9742 may be thermally limited when using the BTL configuration with high supply voltages due to the decreased load resistance seen by each half bridge. For optimum performance, the PCB should be thermally optimized to achieve the continuous output powers required for the application (see the *Thermal Considerations* section).

#### **Component Selection**

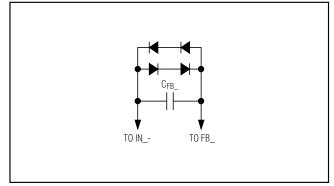

#### Feedback Capacitor (CFB )

To maximize dynamic range, an external feedback capacitor (CFB\_) is needed to generate an error signal for the Class D modulator. The feedback capacitor configures the input amplifier stage as an integrator whose output is equal to an error signal consisting of the sum of the integrated input audio and PWM output signals. The integrator provides a noise-shaping function for the closed-loop response of the amplifier.

Figure 7. Input Signal Source and Load Connections for BTL Operation

To guarantee stability and minimize distortion, select the external feedback resistor (RF\_) and capacitor (CFB) so that the following conditions are met:

$$R_F \times C_{FB} \ge \frac{21.5}{f_{SW}}$$

and  $R_F > 400k\Omega$

where f<sub>SW</sub> is the output switching frequency determined by R<sub>REF</sub> (see the *Setting the Switching Frequency and Output Current Limit (R<sub>REF</sub>)* section).

#### Setting the Switching Frequency and Output Current Limit (RREF)

Resistor R<sub>REF</sub> determines the output switching frequency (fsw) and the output short-circuit current-limit value (I<sub>SC</sub>). Set fsw and I<sub>SC</sub> with the following equations:

$$f_{SW} = \frac{1}{3.3\mu s \times \frac{68k\Omega}{R_{REF}}} (Hz)$$

$$I_{SC} = 3.6A \times \frac{68k\Omega}{R_{REF}} (A)$$

For example, selecting a  $68k\Omega$  resistor for RREF results in a switching frequency of 303kHz and an output short-circuit current limit of 4.5A.

To prevent damage to the MAX9742 during output short-circuit conditions and to utilize its full output power capabilities, use resistor values greater than or equal to  $58k\Omega$  and less than or equal to  $75k\Omega$  for RREF.

#### Input-Coupling Capacitor

The AC-coupling capacitors ( $C_{IN}$ ) and input resistors ( $R_{IN}$ ) form highpass filters that remove any DC bias from an input signal (see the *Typical Application Circuits/Functional Diagrams*).  $C_{IN}$  prevents any DC components from the input-signal source from appearing at the amplifier outputs. The -3dB point of the highpass filter, assuming zero source impedance due to the input signal source, is given by:

$$f_{-3dB} = \frac{1}{2\pi \times R_{IN} \times C_{IN}}$$

(Hz)

Choose C<sub>IN</sub> so that f<sub>-3dB</sub> is well below the lowest frequency of interest. Setting f<sub>-3dB</sub> too high affects the amplifier's low-frequency response. Use capacitors with low-voltage coefficient dielectrics. Aluminum electrolytic, tantalum, or

film dielectric capacitors are good choices for AC-coupling capacitors. Capacitors with high-voltage coefficients, such as ceramics (non-COG dielectrics), can result in increased distortion at low frequencies.

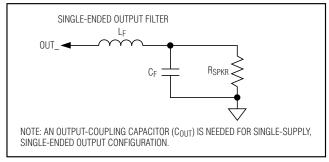

#### Single-Ended LC Output Filter Design (LF and CF)

An LC output filter is needed to extract the amplified audio signal from the PWM output (see Figure 8). The LC circuit forms an LCR lowpass filter (neglecting voice coil inductance) with the impedance of the speaker. To provide a maximally flat-frequency response, the LCR filter should be designed to have a Butterworth response and should be optimized for a specific speaker load. Table 1 provides some recommended standard LF and CF component values for  $4\Omega$ ,  $6\Omega$ , and  $8\Omega$  speaker loads. The component values given in Table 1 provide an approximate -3dB cutoff frequency (fC) of 40kHz. The following paragraph provides information on calculating filter component values for cutoff frequencies other than 40kHz and speaker loads not listed in Table 1.

The LCR filter has the following 2nd order transfer function:

$$H(s) = \frac{\frac{1}{L_F \times C_F}}{s^2 + \frac{1}{R_{SPKR} \times C_F} s + \frac{1}{L_F \times C_F}}$$

where LF is the value of the filter inductor, CF is the value of the filter capacitor, and RSPKR is the DC resistance of the speaker. The voice coil inductance of the speaker has been neglected to simplify filter calculations (see the *Zobel Network* section). The above transfer function is presented in the general 2nd order transfer function format given below:

$$H(s) = \frac{\omega_n^2}{s^2 + 2 \times \zeta \times \omega_n \times s + \omega_n^2}$$

where  $w_{n}$  is the natural frequency in radians/s and  $\zeta$  is the damping ratio of the 2nd order system. For an ideal Butterworth response,  $\zeta$  is equal to 0.707 and  $\omega_{C}$  is equal to the -3dB cutoff frequency,  $\omega_{C}.$  Using the above transfer functions and converting to Hertz, the -3dB cutoff frequency of the filter is:

$$f_C = \frac{1}{2 \times \pi \times \sqrt{L_F \times C_F}} (Hz)$$

NIXIN

Using the transfer functions and the equation for  $f_C$ , the following expressions for  $L_F$  and  $C_F$  can be derived:

$$C_{F} = \frac{1}{4 \times \pi \times f_{C} \times R_{SPKR} \times \xi} (F)$$

$$L_{F} = \frac{1}{4 \times \pi^{2} \times f_{C}^{2} \times C_{F}} (H)$$

Since the frequency response of the output filter is dependent on the speaker resistance, it is best to optimize the LC filter for a particular load resistance. To calculate the component values of the LC filter for a given speaker load resistance, first select an appropriate cutoff frequency for the filter. The cutoff frequency should be high enough so that upper audio frequency band attenuation is kept to a minimum while providing sufficient attenuation at the switching frequency (fsw) of the MAX9742. Once the cutoff frequency is determined, calculate C<sub>F</sub> using the DC resistance of the speaker (RSPKR) and a damping ratio (ξ) equal to 0.707. Finally, calculate L<sub>F</sub> using the resulting C<sub>F</sub> value.

When selecting  $C_F$ , use capacitors with DC voltage ratings greater than  $V_{DD}$ .

When selecting LF, it is important to take into account the DC resistance, current capabilities, and upper frequency limitations of the inductor. Choosing an inductor with minimum DC resistance minimizes I<sup>2</sup>R losses due to the filter inductor and therefore preserves power efficiency. The inductor current rating should be greater than the maximum peak output current to prevent the inductor from going into saturation. Output inductor saturation introduces nonlinearities into the output signal and therefore increases distortion. The

Table 1. Recommended LC Filter Component Values for Various Speaker Loads (f<sub>C</sub> = 40kHz)

| DC RESISTANCE OF SPEAKER ( $\Omega$ ) | L <sub>F</sub> (µH) | C <sub>F</sub> (µF) |

|---------------------------------------|---------------------|---------------------|

| 4                                     | 22                  | 0.68                |

| 6                                     | 33                  | 0.47                |

| 8                                     | 47                  | 0.33                |

upper frequency limit of the inductor should also be taken into account. The load connected to the output of the half-bridge (LC filter and speaker) should remain inductive at the switching frequency of the MAX9742. If not, a significant amount of high-frequency energy is dissipated in the resistive load, therefore, increasing the supply current to excessive levels. To prevent this from occurring, select an output inductor whose self-resonant frequency is substantially higher than the switching frequency of the MAX9742.

To minimize possible EMI radiation, place the LC filter near the MAX9742 on the PCB.

Table 2 provides some suggested inductor manufacturers.

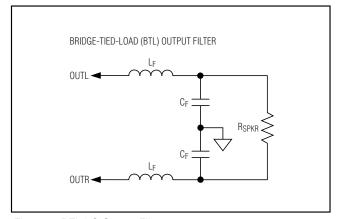

#### BTL LC Output Filter Design

When using the BTL configuration, optimize the output filter for fully differential operation (see Figure 9 and Table 3). Follow the design criteria provided for the singleended filter except use half the value of the BTL resistance for the output filter calculations. This is because each half-bridge output sees half of the BTL resistance. For example, with a BTL resistance of  $8\Omega$  the ideal filter component values are  $C_F = 0.7 \mu F$  and  $L_F = 22.5 \mu H$  for a maximally flat differential filter response with an approximate cutoff frequency of 40kHz. Rounding to the nearest standard component values yields CF = 0.68µF and LF = 22uH. Also connect ground-terminated Zobel networks on each side of the speaker load (see the Zobel Network section). Ground terminating the Zobel networks prevents excessive peaking in the common-mode frequency response of the filter.

Figure 8. Single-Ended LC Output Filter

Table 2. Suggested Inductor Manufacturers

| MODEL    | MANUFACTURER | DIMENSIONS                | WEBSITE               |

|----------|--------------|---------------------------|-----------------------|

| DO3340P  | Coilcraft    | 12.95mm x 9.4mm x 11.43mm | www.coilcraft.com     |

| CDRH127  | Sumida       | 12.3mm x 12.3mm x 8mm     | www.sumida.com        |

| 11RHBP   | Toko         | 11mm x 11mm x 13.75mm     | www.tokoam.com        |

| SLF12575 | TDK          | 12.5mm x 12.5mm x 7.5mm   | www.component.tdk.com |

To maximize the performance of the differential output filter and minimize EMI radiation, keep the ground connections of the CF capacitors close together on the PCB and place the filter near the MAX9742.

The component ratings for C<sub>F</sub> and L<sub>F</sub> follow the same requirements mentioned in the *Single-Ended LC Output Filter Design (L<sub>F</sub> and C<sub>F</sub>)* section.

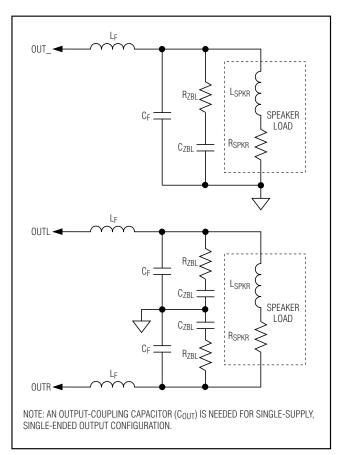

#### Zobel Network

For speaker loads that have appreciable amounts of voice coil inductance (> 33µH), peaking in the frequency response of the output may occur near the cutoff frequency of the LC filter, which may cause the device to go into current limit at high output powers. This peaking is due to the resonant circuit formed by the LC output filter and complex impedance of the speaker. To nullify the peaking in the frequency response, connect a Zobel network (series RC circuit) in parallel with the speaker load as shown in Figure 10. The Zobel circuit reduces the peaking by dampening the reactive behavior of the speaker. For the single-ended output configuration, use the following equations to calculate the component values for the Zobel network:

$$R_{ZBL} = 1.2 \times R_{SPKR} (\Omega)$$

$$C_{ZBL} = \frac{1}{2\pi \times R_{SPKR} \times f_C} (F)$$

where  $R_{ZBL}$  is the value of the Zobel resistor,  $C_{ZBL}$  is the value of the Zobel capacitor,  $R_{SPKR}$  is the DC resistance of the speaker, and  $f_{C}$  is the cutoff frequency of

Figure 9. BTL LC Output Filter

the LC filter. For the BTL configuration, use half of the BTL resistance for the Zobel network calculations. Connect a ground-terminated Zobel network on each side of the BTL resistance to prevent excessive peaking in the common-mode response of the output filter. For most applications, RZBL should have a minimum power rating of 1/4W or greater. CZBL should have a voltage rating greater than or equal to VDD.

Table 3. Recommended Differential LC Filter Component Values for an  $8\Omega$  BTL Speaker Load ( $f_C = 40 \text{kHz}$ )

| DC Resistance of Speaker (Ω) | L <sub>F</sub> (µH) | C <sub>F</sub> (µF) |  |

|------------------------------|---------------------|---------------------|--|

| 8                            | 22                  | 0.68                |  |

Figure 10. Zobel Network Connections for High-Inductance Speakers

#### Bootstrap Diode (DBOOT)

To provide sufficient gate drive voltage to the high-side transistor of the half-bridge output stage, an external diode (DBOOT) and capacitor (CBOOT) are needed for the internal bootstrapping circuitry (see Figure 2). To maintain high power efficiencies and maximum output power at low audio frequencies, use fast-recovery switching diodes for DBOOT. Silicon diodes equivalent to 1N914, BAS16, or 1N4148 work well.

#### Capacitor (CBOOT)

For most applications, use a C<sub>BOOT</sub> capacitor  $\geq$  0.1 $\mu$ F and  $\leq$  0.22 $\mu$ F. For proper operation, use capacitors with low ESR and voltage ratings greater than 7V for C<sub>BOOT</sub>.

## Output-Coupling Capacitors (COUT, Single-Ended, Single-Supply Operation)

The MAX9742 requires output-coupling capacitors for single-supply operation. Since the MAX9742 outputs switch between VDD and ground in single-supply operation, there is a DC component equal to 0.5 x VDD present at the outputs. The output-coupling capacitor blocks this DC component, preventing DC current from flowing into the load. The output capacitor and the load resistance of the speaker form a highpass filter. The -3dB point of the highpass filter can be approximated by:

$$f_{-3dB} = \frac{1}{2\pi \times R_{SPKR} \times C_{OUT}}$$

(Hz)

where f<sub>-3dB</sub> is the -3dB cutoff frequency of the filter, RSPKR is the DC resistance of the speaker, and C<sub>OUT</sub> is the value of the output-coupling capacitor. As with the input capacitor, choose C<sub>OUT</sub> such that f<sub>-3dB</sub> is well below the lowest frequency of interest. Setting f<sub>-3dB</sub> too high affects the amplifier's low-frequency response. Select capacitors with low ESR to minimize power losses. Since the output-coupling capacitor has a large amplitude AC current (resulting average output current due to the LC filter) flowing through it at high output powers, it is important to select an output-coupling

capacitor that has an appropriate ripple current rating. To prevent damage to the output-coupling capacitor, use the following equation to calculate the required RMS ripple current rating for COUT:

$$I_{RMS\_RIPPLE} = \frac{V_{DD}}{2.83 \times R_{SPKR}} (A)$$

where IRMS\_RIPPLE is the minimum required RMS ripple current rating for COUT and RSPKR is the DC resistance of the speaker. The ripple current ratings of capacitors are frequency dependent, so be sure to select a capacitor based on its ripple current rating within the audio frequency range.

Select output-coupling capacitors with DC voltage ratings greater than V<sub>DD</sub>.

In single-supply operation with single-ended outputs, the leakage current of  $C_{OUT}$  can affect the startup time of the MAX9742. To minimize startup time delays due to  $C_{OUT}$ , use capacitors with leakage current ratings less than 1 $\mu$ A for  $C_{OUT}$ . See the *Startup Time Considerations* section for more information on optimizing the startup time of the MAX9742.

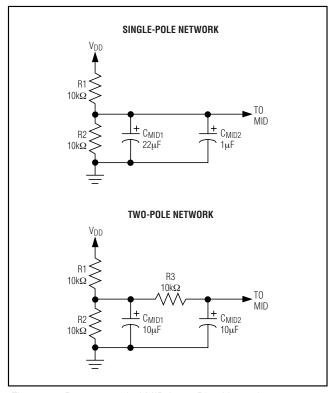

#### Setting V<sub>MID</sub>

The voltage present at the MID input biases the internal amplifiers and should be set to the average value of VDD and VSS for maximum dynamic range. For dual-supply operation, connect MID to ground. For single-supply operation, set MID to 0.5 x VDD through an external resistive divider. To minimize power dissipation while providing enough input bias current for the MID input, select divider-resistors with values greater than or equal to  $10k\Omega$  and less than or equal to  $20k\Omega$ . Connect a decoupling network between MID and the SGND plane (see the <code>Supply Bypassing/Layout</code> section) to provide a sufficient low- and high-frequency AC ground for the internal amplifiers. Figure 11 shows the recommended decoupling networks for bypassing the MID input.

#### Multiple-Pole MID Network vs. Single-Pole VMID Network for Increased PSRR Performance (Single-Supply Operation)

A multiple-pole MID network improves PSRR performance over a single-pole network. Since the input amplifiers of the MAX9742 are biased at V<sub>MID</sub>, any noise coupled into the MID input using the MID bias network supply appears at the outputs of the MAX9742. Increasing the number of poles in the MID network provides further attenuation of low-frequency noise at the MID input, and therefore, improving the AC PSRR performance of the MAX9742. Figure 11 shows the recommended single-pole and two-pole MID input bias networks. Figure 12 illustrates the differences of the MAX9742's low-frequency AC PSRR performance with the single-pole and two-pole networks shown in Figure 11.

Figure 11. Recommended MID Input Bias Networks

#### Soft-Start Capacitor (CSFT)

The soft-start capacitor determines the timing for the soft-start power-up sequencing that minimizes audible clicks-and-pops during power-up/power-down transitions and when entering/exiting shutdown mode. Connect a capacitor between SFT and ground for proper operation. For optimum performance, this capacitor should equal 0.22µF. Using capacitor values much smaller than these values degrade click-and-pop performance and values much greater lengthen startup time.

#### Startup Time Considerations

At the beginning of the soft-start sequence, the MAX9742 ensures  $V_{\text{OUT}}$  is approximately equal to  $V_{\text{MID}}$  before continuing the soft-start sequence. For single-supply operation with single-ended outputs, the output-coupling capacitors ( $C_{\text{OUT}}$ ) are first gradually charged up to  $V_{\text{MID}}$  before continuing soft-start sequencing. This gradual charging up of  $C_{\text{OUT}}$  minimizes audible transients that may appear across the

Figure 12. Comparison of MAX9742 AC PSRR with Single-Pole and Two-Pole MID Networks

speaker loads during mode transitions. After  $C_{OUT}$  is charged up to  $V_{MID}$ , the MAX9742 concludes the soft-start sequence by precharging  $C_{REGLS}$ ,  $C_{BOOT}$ , and  $C_{IN}$ . Once the soft-start sequence is complete, the MAX9742 begins normal operation.

For dual-supply operation, the startup time of the MAX9742 is primarily dependent on the value of CSFT since it controls the rate of the soft-start sequencing.

In single-supply operation, the overall startup time is affected by the values of  $C_{MID1}$ ,  $C_{MID2}$ ,  $C_{SFT}$ ,  $C_{OUT}$  (single-ended outputs) and the value of the resistors used to bias the MID input. This is because soft-start power-up sequencing is dependent on the charging-up of the MID input bias network and the charging rate of  $C_{OUT}$ . As with dual-supply operation, the startup time is also affected by the value of  $C_{SFT}$  since it controls the rate of the soft-start sequencing. Using the component values shown in Figure 11 and a  $C_{SFT}$  capacitor value of  $0.22\mu F$  yields a typical single-supply power-up time of 1.5s.

For single-supply operation with single-ended outputs, the leakage current of  $C_{OUT}$  can also affect the startup time of the MAX9742. To minimize startup time delays due to  $C_{OUT}$ , use capacitors with leakage current ratings less than  $1\mu A$  for  $C_{OUT}$ .

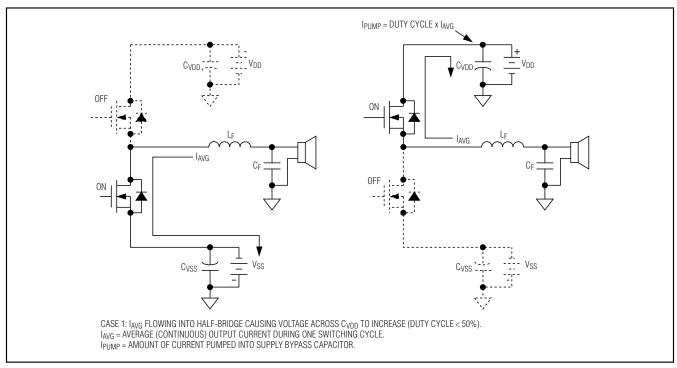

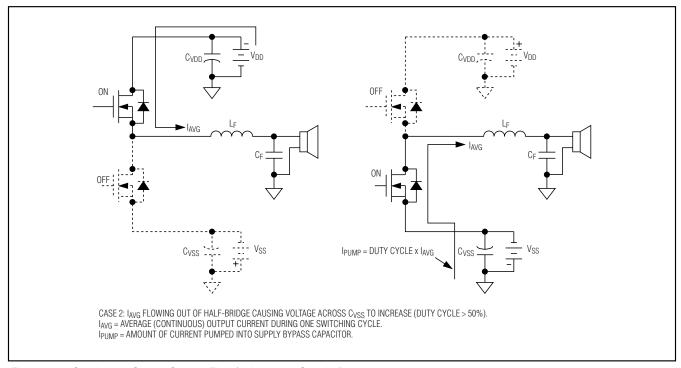

#### Supply Pumping Effects

When using the MAX9742 in the single-ended output configuration, the power-supply voltages (VDD and Vss) may increase if the supplies cannot sink current. This "supply pumping" is primarily due to the inductive loading of the LC filter and the voice coil inductance of the speaker. The inductive load connected to the output of the device prevents the output current from changing instantaneously. When the MAX9742 drives this inductive load, a continuous current flows at the output whose value is equal to the running average of the output switching currents, or in other words, the amplified audio signal. This averaged current continues to flow during both switching cycles of the half-bridge, which means that some of the current is pumped back towards the opposite power supply. If the respective supply cannot sink this current, it flows into supply bypass capacitor causing the voltage across the capacitor to increase.