### 11.3Gbps, Low-Power, AC-Coupled Laser Driver

### **General Description**

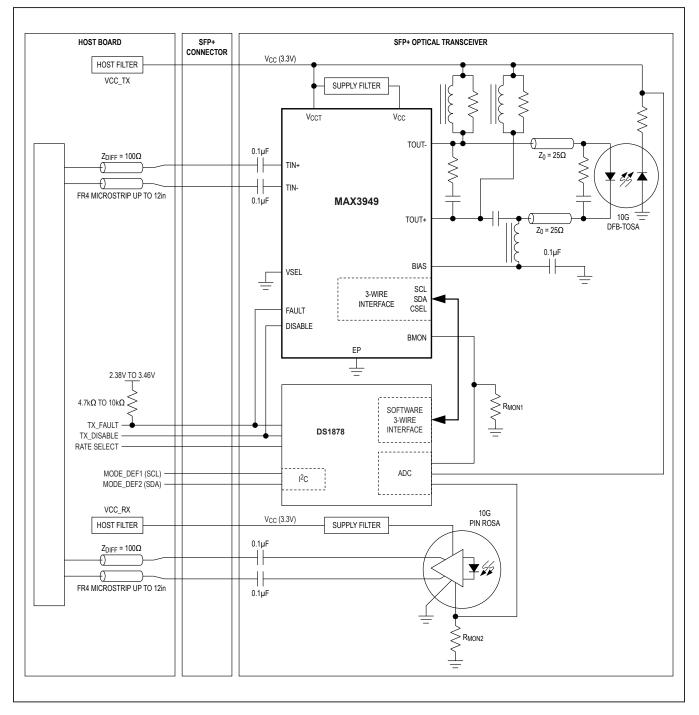

The MAX3949 is a 3.3V, multirate, low-power laser diode driver designed for Ethernet, Fibre Channel, and SONET transmission systems at data rates up to 11.3Gbps. This device is optimized to drive a differential transmitter optical subassembly (TOSA) with a  $25\Omega$  flex circuit. The unique design of the output stage enables use of unmatched TOSAs.

The device receives differential AC-coupled signals with on-chip termination. It can deliver laser modulation currents of up to 85mA at an edge speed of 22ps (20% to 80%) into a 5 $\Omega$  external differential load. The device is designed to have a high-bandwidth differential signal path with on-chip back termination resistors integrated into its outputs. An input equalization block can be activated to compensate for SFP+ host connector losses. The integrated bias circuit provides programmable laser bias currents up to 105mA. Both the laser bias current generator and the laser modulator can be disabled from a single pin.

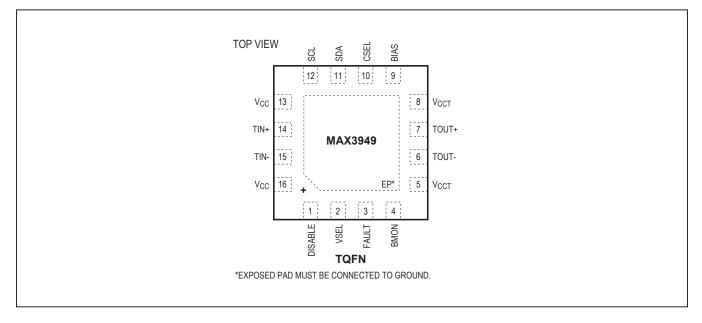

The use of a 3-wire digital interface reduces the pin count while permitting adjustment of input equalization, polarity, output deemphasis, and modulation and bias currents without the need for external components. The device is available in a 3mm x 3mm, 16-pin TQFN package, and is specified for the -40°C to +95°C extended temperature range.

### **Benefits and Features**

- Low Power Consumption

- Saves Board Space

- Small 3mm x 3mm Package

- Flexibility

- Programmable Modulation Current Up to  $85mA (5\Omega \text{ Load})$

- Programmable Bias Current Up to 105mA

- Programmable Input Equalization and Output Deemphasis

- Safety

- Supports SFF-8431 SFP+ MSA and SFF-8472 Digital Diagnostic

- Integrated Eye Safety Features with Maskable Faults

- Bias Current Monitor

### Applications

- 10GBASE-LR SFP+ Optical Transceivers

- 10GBASE-LRM SFP+ Optical Transceivers

- OC192-SR SFP+ SDH/SONET Transceivers

Ordering Information appears at end of data sheet.

### **Absolute Maximum Ratings**

| V <sub>CC</sub> , V <sub>CCT</sub> 0.3V to +4.0V                   | Voltage Range at BIAS0.4V to 2.5V                     |

|--------------------------------------------------------------------|-------------------------------------------------------|

| V <sub>CC</sub> - V <sub>CCT</sub>   < 0.5V                        | Current into TOUT+ and TOUT+150mA                     |

| Voltage Range at TIN+, TIN-, DISABLE,                              | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| SDA, SCL, CSEL, VSEL, FAULT, and BMON0.3V to V <sub>CC</sub>       | TQFN (derate 20.8mW/°C above +70°C)1666.7mW           |

| Voltage Range at                                                   | Storage Temperature Range55°C to +150°C               |

| TOUT-, TOUT+(V <sub>CCT</sub> - 1.3V) to (V <sub>CCT</sub> + 1.3V) | Die Attach Temperature+400°C                          |

| Current Range into TIN+ and TIN20mA to +20mA                       | Lead Temperature (soldering, 10s)+300°C               |

| Current Range into BIAS0mA to +120mA                               | Soldering Temperature (reflow)+260°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| PACKAGE TYPE: 16-PIN TQFN             |         |  |  |  |

|---------------------------------------|---------|--|--|--|

| Package Code                          | T1633+5 |  |  |  |

| Outline Number                        | 21-0136 |  |  |  |

| Land Pattern Number                   | 90-0032 |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD  |         |  |  |  |

| Junction to Ambient ( $\theta_{JA}$ ) | 48°C/W  |  |  |  |

| Junction to Case ( $\theta_{JC}$ )    | 10°C/W  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

### **Electrical Characteristics**

| PARAMETER                             | SYMBOL                             | CONDITIONS                                                                                            | MIN  | TYP  | MAX  | UNITS            |  |

|---------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------------------|--|

| POWER SUPPLY                          |                                    | ·                                                                                                     |      |      |      |                  |  |

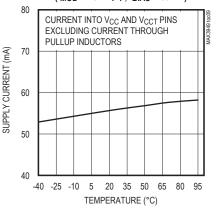

| Power-Supply Current                  | I <sub>CC</sub>                    | Excludes output current through the external pullup inductors (Note 2)                                |      | 55   | 70   | mA               |  |

| Power-Supply Voltage                  | V <sub>CCT</sub> , V <sub>CC</sub> |                                                                                                       | 2.95 |      | 3.63 | V                |  |

| POWER-ON RESET                        |                                    | ·                                                                                                     |      |      |      |                  |  |

| V <sub>CC</sub> for Enable High       |                                    |                                                                                                       |      | 2.55 | 2.75 | V                |  |

| V <sub>CC</sub> for Enable Low        |                                    |                                                                                                       | 2.3  | 2.45 |      | V                |  |

| DATA INPUT SPECIFICATION              |                                    |                                                                                                       |      |      |      |                  |  |

| Input Data Rate                       |                                    |                                                                                                       | 1    | 10.3 | 11.3 | Gbps             |  |

|                                       |                                    | Launch amplitude into FR4 transmission<br>line ≤ 12in,<br>SET_TXEQ[1:0] = 01b,<br>SET_TXEQ[1:0] = 11b | 0.2  |      | 0.8  |                  |  |

| Differential Input Voltage            | V <sub>IN</sub>                    | SET_TXEQ[1:0] = 01b,<br>SET_TXEQ[1:0] = 11b,<br>outside of optimized range                            | 0.15 |      | 1.0  | V <sub>P-P</sub> |  |

|                                       |                                    | SET_TXEQ[1:0] = 00b                                                                                   | 0.15 |      | 1.0  |                  |  |

| Common-Mode Input Voltage             | V <sub>CM</sub>                    |                                                                                                       |      | 2.15 |      | V                |  |

| Differential Input Resistance         | R <sub>IN</sub>                    |                                                                                                       | 75   | 100  | 125  | Ω                |  |

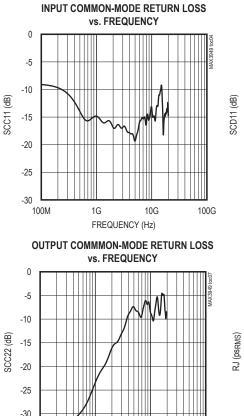

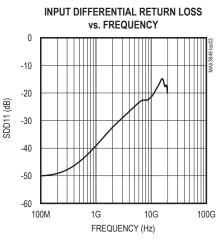

|                                       | SCD11                              | 0.1GHz ≤ f ≤ 11.3GHz                                                                                  |      | -30  |      |                  |  |

| Differential Input S-Parameters       | SDD11                              | f≤4.1GHz                                                                                              |      | -19  |      | - dB             |  |

| (Note 3)                              | 30011                              | 4.1GHz ≤ f ≤ 11.3GHz                                                                                  |      | -16  |      |                  |  |

|                                       | SCC11                              | $1$ GHz $\leq$ f $\leq$ 11.3GHz, Z <sub>CM_SOURCE</sub> = $25\Omega$                                  |      | -13  |      |                  |  |

| BIAS CURRENT GENERATOR (              | Figure 3)                          |                                                                                                       |      |      |      |                  |  |

| Maximum BIAS DAC Current              | IBIASMAX                           | Current into BIAS pin                                                                                 | 85   | 105  |      | mA               |  |

| Minimum BIAS DAC Current              | IBIASMIN                           | Current into BIAS pin                                                                                 |      |      | 5    | mA               |  |

| BIAS-Off Current                      | IBIAS-OFF                          |                                                                                                       |      |      | 0.1  | mA               |  |

| BIAS DAC LSB Size                     |                                    |                                                                                                       |      | 200  |      | μA               |  |

| BIAS DAC Integral Nonlinearity        | INL                                | $5mA \le I_{BIAS} \le 85mA$                                                                           |      | ±0.5 |      | %FS              |  |

| BIAS DAC Differential<br>Nonlinearity | DNL                                | Guaranteed monotonic at 8-bit resolution,<br>SET_IBIAS[8:1]                                           |      | ±0.5 |      | LSB              |  |

| BIAS Current DAC Stability            |                                    | $5mA \le I_{BIAS} \le 85mA$ , $V_{BIAS} = 1.5V$<br>(Notes 4, 5)                                       |      | 1    | 4    | %                |  |

| BIAS Compliance Voltage               |                                    |                                                                                                       | 0.9  | 1.5  | 2.1  | V                |  |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

### **Electrical Characteristics (continued)**

| PARAMETER                                                     | SYMBOL                                                                                   | CONDITIONS                                                                                             | MIN                  | TYP  | MAX                  | UNITS             |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|-------------------|

| BMON Current Gain                                             | G <sub>BMON</sub>                                                                        | G <sub>BMON</sub> = I <sub>BMON</sub> /I <sub>BIAS</sub> , external resistor<br>to GND defines voltage | 8.5                  | 9.6  | 11.8                 | mA/A              |

| BMON Current Gain Stability                                   | BMON Current Gain Stability $5mA \le I_{BIAS} \le 85mA, V_{BIAS} = 1.5V$<br>(Notes 4, 5) |                                                                                                        |                      | 1.5  | 5                    | %                 |

| Compliance Voltage at BMON                                    |                                                                                          |                                                                                                        | 0                    |      | 1.8                  | V                 |

| LASER MODULATOR (Note 6)                                      | 1                                                                                        |                                                                                                        |                      |      |                      |                   |

| Maximum Laser Modulation<br>Current                           | LD <sub>MODMAX</sub>                                                                     | Current into TOUT+ pin, 5Ω laser load, 6.25% deemphasis                                                | 85                   |      |                      | mA <sub>P-P</sub> |

| Minimum Laser Modulation<br>Current                           | LD <sub>MODMIN</sub>                                                                     | Current into TOUT+ pin, 5Ω laser load,<br>6.25% deemphasis                                             |                      |      | 10                   | mA <sub>P-P</sub> |

| Modulation-Off Laser Current                                  | LD <sub>MOD-</sub><br>OFF                                                                | Current into TOUT+ pin                                                                                 |                      |      | 0.1                  | mA                |

| Modulation DAC Full-Scale<br>Current                          | I <sub>MOD-FS</sub>                                                                      |                                                                                                        | 99.7                 | 130  |                      | mA                |

| Modulation DAC LSB Size                                       |                                                                                          |                                                                                                        |                      | 247  |                      | μA                |

| Modulation DAC Integral<br>Nonlinearity                       | INL                                                                                      |                                                                                                        |                      | ±1   |                      | %FS               |

| Modulation DAC Differential<br>Nonlinearity                   |                                                                                          |                                                                                                        |                      | ±0.5 |                      | LSB               |

| TOUT- and TOUT+<br>Instantaneous Output<br>Compliance Voltage | Instantaneous Output With external inductive pullup to V <sub>CCT</sub>                  |                                                                                                        | V <sub>CCT</sub> - 1 |      | V <sub>CCT</sub> + 1 | V                 |

| Modulation Output Termination                                 | R <sub>OUT</sub>                                                                         |                                                                                                        | 19                   | 25   | 31                   | Ω                 |

| Modulation Current DAC Stability                              |                                                                                          | 10mA ≤ LD <sub>MOD</sub> ≤ 85mA,<br>V <sub>BIAS</sub> = 1.5V (Notes 5, 6)                              |                      | 1.5  | 4                    | %                 |

| Modulation Current Rise/Fall<br>Time                          | t <sub>R</sub> , t <sub>F</sub>                                                          | 20% to 80%, 10mA ≤ LD <sub>MOD</sub> ≤ 85mA<br>(Note 4)                                                |                      | 22   | 36                   | ps                |

|                                                               |                                                                                          | 10mA ≤ LD <sub>MOD</sub> ≤ 85mA, 8.5Gbps with<br>K28.5 pattern                                         |                      | 4    |                      |                   |

| Deterministic Jitter (Note 4)                                 | DJ                                                                                       | 10mA ≤ LD <sub>MOD</sub> ≤ 85mA, 10.3125Gbps<br>(Note 7)                                               |                      | 6    | 12                   | psp-p             |

|                                                               |                                                                                          | 10mA ≤ LD <sub>MOD</sub> ≤ 85mA, 11.3Gbps<br>(Note 7)                                                  |                      | 8    | 13                   |                   |

| Random Jitter                                                 | RJ                                                                                       | 10mA ≤ LD <sub>MOD</sub> ≤ 85mA (Note 4)                                                               |                      | 0.19 | 0.55                 | ps <sub>RMS</sub> |

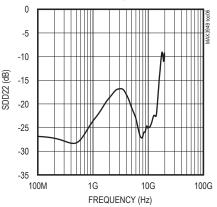

|                                                               | 80000                                                                                    | $0.1GHz \le f \le 4.1GHz$ ,<br>$Z_{CM}SOURCE = 12.5\Omega$                                             |                      | -10  |                      |                   |

| Differential S-Parameters (Note 3)                            | SCC22                                                                                    | 4.1GHz < f ≤ 11.3GHz,<br>Z <sub>CM_SOURCE</sub> = 12.5Ω                                                |                      | -5   |                      | dB                |

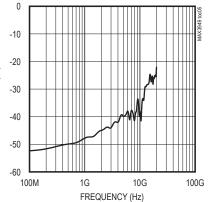

| (                                                             | SDD22                                                                                    | 0.1GHz < f ≤ 11.3GHz,<br>ZDIFF_SOURCE = 50Ω                                                            |                      | -13  |                      |                   |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

### **Electrical Characteristics (continued)**

| PARAMETER                         | SYMBOL               | CONDITIONS                                                                                                                                                                          | MIN                        | TYP | MAX                        | UNITS |

|-----------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| SAFETY FEATURES                   |                      | ·                                                                                                                                                                                   |                            |     |                            |       |

| Threshold Voltage at BIAS         |                      | Fault never occurs for $V_{BIAS} \ge 0.55V$ , fault always occurs for $V_{BIAS} < 0.35V$                                                                                            | 0.35                       |     | 0.55                       | V     |

| Threshold Voltage at TOUT+        |                      | Fault never occurs for V <sub>TOUT+</sub> ≥ V <sub>CCT</sub><br>- 1.45, fault always occurs for V <sub>TOUT+</sub> <<br>V <sub>CCT</sub> - 1.88                                     | V <sub>CCT</sub> -<br>1.88 |     | V <sub>CCT</sub> -<br>1.45 | V     |

| Threshold Voltage at TOUT-        |                      | Fault never occurs for V <sub>TOUT</sub> ≥ V <sub>CCT</sub> -<br>1.45V, fault always occurs for V <sub>TOUT</sub> <<br>V <sub>CCT</sub> - 1.88V                                     | V <sub>CCT</sub> -<br>1.88 |     | V <sub>CCT</sub> -<br>1.45 | V     |

| Threshold Voltage at $V_{CCT}$    |                      | Fault never occurs for $V_{CCT} \ge V_{CC} - 0.27V$ , fault always occurs for $V_{CCT} < V_{CC} - 0.6V$                                                                             | V <sub>CC</sub> -<br>0.6   |     | V <sub>CC</sub> -<br>0.27  | V     |

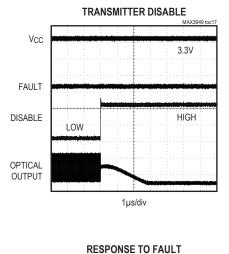

| TIMING REQUIREMENTS (Notes        | s 4, 6)              |                                                                                                                                                                                     |                            |     |                            |       |

| Initialization Time               | t <sub>INIT</sub>    | $I_{BIAS}$ = 25mA, LD <sub>MOD</sub> = 65mA, bias and<br>modulation DAC are both 0h, time from<br>TX_EN = high to I <sub>BIAS</sub> and LD <sub>MOD</sub> at 90%<br>of steady state |                            | 12  |                            | μs    |

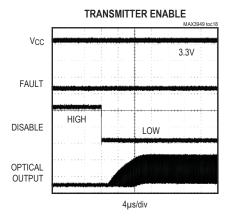

| DISABLE Assert Time               | tOFF                 | Time from rising edge of DISABLE input<br>signal to I <sub>BIAS</sub> and LD <sub>MOD</sub> at 10% of<br>steady state (Note 4)                                                      |                            | 3   |                            | μs    |

| DISABLE Negate Time               | ton                  | Time from falling edge of DISABLE to ${\sf I}_{BIAS}$ and ${\sf LD}_{MOD}$ at 90% of steady state (Note 4)                                                                          |                            | 12  |                            | μs    |

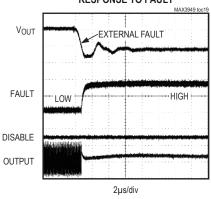

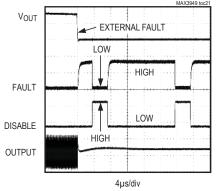

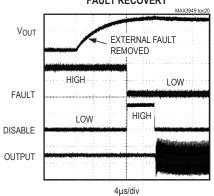

| FAULT Reset Time                  | <sup>t</sup> RECOVER | Time from negation of latched fault using DISABLE to $\rm I_{BIAS}$ and $\rm LD_{MOD}$ at 90% of steady state                                                                       |                            |     |                            | μs    |

| FAULT Assert Time                 | <sup>t</sup> FAULT   | Time from fault to FAULT = high,<br>C <sub>FAULT</sub> ≤ 20pF, R <sub>FAULT</sub> = 4.7kΩ                                                                                           |                            | 0.7 | 3                          | μs    |

| DISABLE to Reset Time             |                      | Time DISABLE must be held high to reset fault                                                                                                                                       | 4                          |     |                            | μs    |

| DIGITAL I/O SPECIFICATIONS (      | SDA, SCL, CS         | EL, FAULT, DISABLE)                                                                                                                                                                 |                            |     |                            |       |

| Input High Voltage                | VIH                  |                                                                                                                                                                                     | 1.8                        |     | V <sub>CC</sub>            | V     |

| Input Low Voltage V <sub>IL</sub> |                      |                                                                                                                                                                                     | 0                          |     | 0.8                        | V     |

| Input Hysteresis                  | V <sub>HYST</sub>    |                                                                                                                                                                                     |                            | 80  |                            | mV    |

| Input Capacitance                 | C <sub>IN</sub>      |                                                                                                                                                                                     |                            |     | 5                          | pF    |

| DISABLE Input Resistance          | R <sub>PULL</sub>    | Internal pullup resistor                                                                                                                                                            | 4.7                        | 7.5 | 10                         | kΩ    |

| Input Leakage Current             | I <sub>IH</sub>      | Input connected to V <sub>CC</sub>                                                                                                                                                  |                            |     | 10                         | μA    |

| (DISABLE)                         | IIL                  | Input connected to GND                                                                                                                                                              |                            | 440 | 775                        | μΛ    |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

### **Electrical Characteristics (continued)**

| PARAMETER                                      | SYMBOL           | CONDITIONS                                                              | MIN                         | TYP                      | MAX                         | UNITS |  |

|------------------------------------------------|------------------|-------------------------------------------------------------------------|-----------------------------|--------------------------|-----------------------------|-------|--|

| lanut La skana Oumant                          | IIH              | Input connected to V <sub>CC</sub>                                      | -2                          |                          | +2                          |       |  |

| Input Leakage Current<br>(SDA)                 | IIL              | Input connected to GND, internal pullup is $75k\Omega$ typical          | 35                          |                          | 75                          | μA    |  |

| Input Leakage Current                          | ЦН               | Input connected to $V_{CC},$ internal pulldown is $75 k\Omega$ typical  | 35                          |                          | 75                          |       |  |

| (SCL, CSEL)                                    | IIL              | Input connected to GND                                                  | -2                          |                          | +2                          | μA    |  |

| Output High Voltage<br>(SDA, FAULT)            | V <sub>OH</sub>  | External pullup is (4.7k $\Omega$ to 10k $\Omega$ ) to V <sub>CC</sub>  | V <sub>CC</sub> - 0.1       |                          |                             | V     |  |

| Output Low Voltage<br>(SDA, FAULT)             | V <sub>OL</sub>  | External pullup is (4.7k $\Omega$ to 10k $\Omega$ ) to V <sub>CC</sub>  |                             |                          | 0.4                         | V     |  |

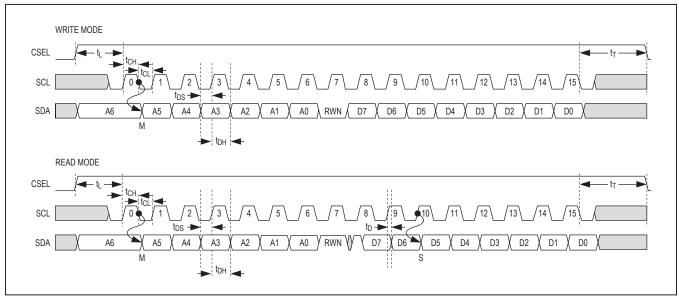

| 3-WIRE DIGITAL INTERFACE TIM                   | ING CHARA        | CTERISTICS (Figure 5)                                                   |                             |                          |                             |       |  |

| SCL Clock Frequency                            | fSCL             |                                                                         |                             | 400                      | 1000                        | kHz   |  |

| SCL Pulse-Width High                           | t <sub>CH</sub>  |                                                                         | 500                         |                          |                             | ns    |  |

| SCL Pulse-Width Low                            | t <sub>CL</sub>  |                                                                         | 500                         |                          |                             | ns    |  |

| SDA Setup Time                                 | t <sub>DS</sub>  |                                                                         |                             | 100                      |                             | ns    |  |

| SDA Hold Time                                  | t <sub>DH</sub>  |                                                                         |                             | 100                      |                             | ns    |  |

| SCL Rise to SDA Propagation<br>Time            | t <sub>D</sub>   |                                                                         |                             | 5                        |                             | ns    |  |

| CSEL Pulse-Width Low                           | t <sub>CSW</sub> |                                                                         | 500                         |                          |                             | ns    |  |

| CSEL Leading Time Before the<br>First SCL Edge | tL               |                                                                         |                             | 500                      |                             | ns    |  |

| CSEL Trailing Time After the Last SCL Edge     | tT               |                                                                         |                             | 500                      |                             | ns    |  |

| SDA, SCL Load                                  | CB               | Total bus capacitance on one line with $4.7 k\Omega$ pullup to $V_{CC}$ |                             |                          | 20                          | pF    |  |

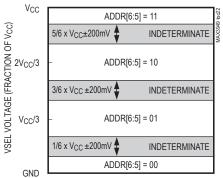

| VSEL FOUR-LEVEL DIGITAL INF                    | UT (Table 2)     |                                                                         |                             |                          |                             |       |  |

| Input Voltage High                             |                  | 3-wire address, ADDR[6:5] = 11b                                         | 5/6V <sub>CC</sub><br>+ 0.2 |                          | V <sub>CC</sub>             | V     |  |

| Input Voltage Mid-High                         |                  | 3-wire address, ADDR[6:5] = 10b                                         | 3/6V <sub>CC</sub><br>+ 0.2 | 2/3 x<br>V <sub>CC</sub> | 5/6V <sub>CC</sub><br>- 0.2 | V     |  |

| Input Voltage Mid-Low                          |                  | 3-wire address, ADDR[6:5] = 01b                                         | 1/6V <sub>CC</sub><br>+ 0.2 | 1/3 x<br>V <sub>CC</sub> | 3/6V <sub>CC</sub><br>- 0.2 | V     |  |

| Input Voltage Low                              |                  | 3-wire address, ADDR[6:5] = 00b                                         | 0                           |                          | 1/6V <sub>CC</sub><br>- 0.2 | V     |  |

### **Electrical Characteristics (continued)**

$(V_{CC} = V_{CCT} = 2.95V$  to 3.63V,  $T_A = -40^{\circ}C$  to +95°C; typical values are at  $V_{CC} = V_{CCT} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $I_{BIAS} = 60$ mA, LD<sub>MOD</sub> = 40mA, and 14Ω single-ended electrical output load, unless otherwise noted. See AC Test Setup for electrical setup.) (Note 1)

- **Note 1:** Specifications at  $T_A = -40^{\circ}C$  and  $+95^{\circ}C$  are guaranteed by design and characterization.

- Note 2: BIAS is connected to 1.9V. TOUT- and TOUT+ are connected to V<sub>CCT</sub> through pullup inductors.

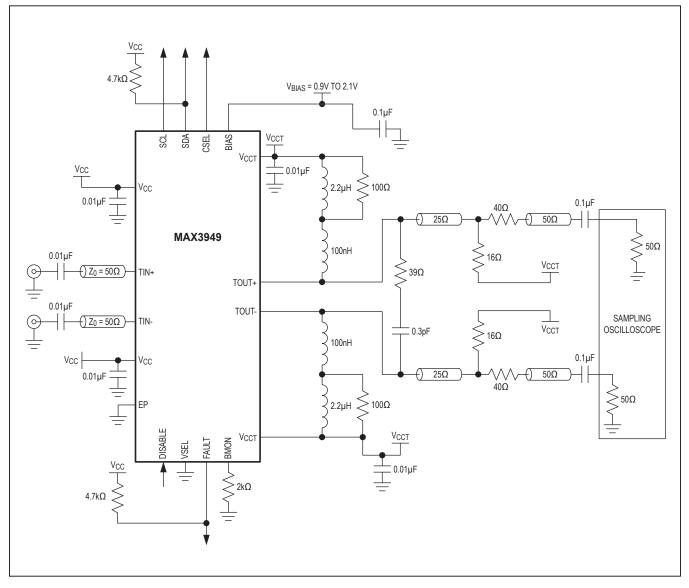

- Note 3: Measured with Agilent 8720ES + ATN-U112A and series RC (39Ω and 0.3pF) between TOUT+ and TOUT- (AC Test Setup).

- Note 4: Guaranteed by design and characterization.

- Note 5: Stability is defined as [(I<sub>MEASURED</sub>) (I<sub>REFERENCE</sub>)]/(I<sub>REFERENCE</sub>) over the listed current/temperature range and V<sub>CCT</sub> = V<sub>CC</sub> = V<sub>CCREF</sub> ±5%, V<sub>CCREF</sub> = 3.3V. Reference current measured at V<sub>CCREF</sub> and T<sub>REF</sub> = +25°C.

Note 6: LD<sub>MOD</sub> = I<sub>MOD</sub> x (1 DE) x 50/(50 + R), where LD<sub>MOD</sub> is the effective laser modulation current, I<sub>MOD</sub> is the modulation

- DAC current, DE is the deemphasis percentage, and R is the differential laser load resistance. Example: For R $\Omega$  = 5 and DE = 6.25%,  $LD_{MOD}$  = 0.852 x I<sub>MOD</sub>. Note 7: Equivalent 2<sup>23</sup> - 1 PRBS pattern = 2<sup>7</sup> - 1 PRBS + 72 zeros + 2<sup>7</sup> - 1 PRBS + 72 ones.

### AC Test Setup

11.3Gbps, Low-Power, AC-Coupled Laser Driver

### **Typical Operating Characteristics**

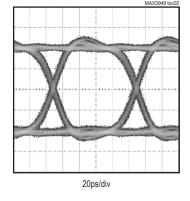

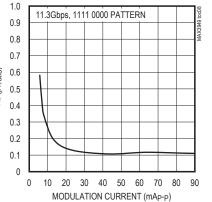

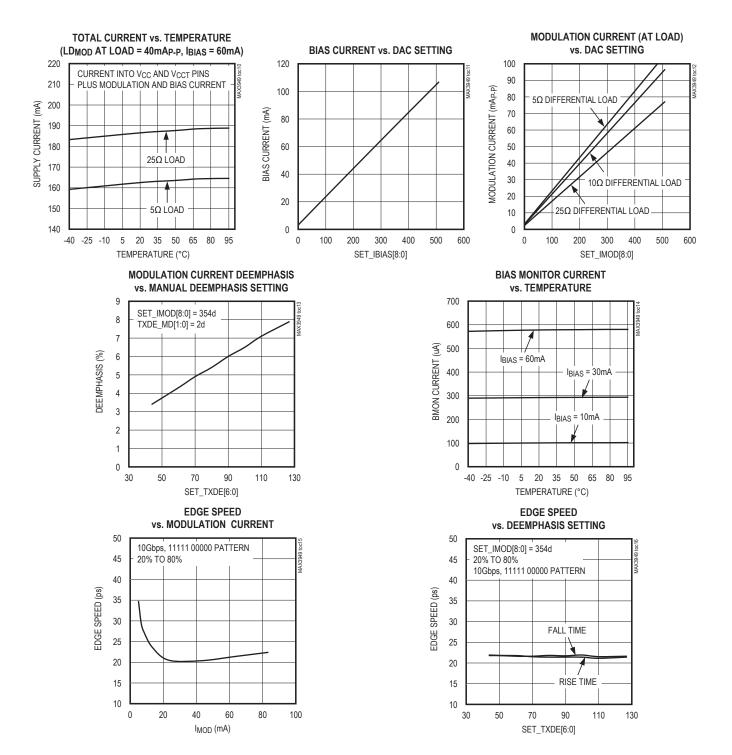

(Typical values are at  $V_{CC} = V_{CCT} = 3.3V$ ,  $T_A = +25^{\circ}C$ , data pattern =  $2^7 - 1$  PRBS + 72 zeros +  $2^7 - 1$  PRBS (inverted) + 72 ones, unless otherwise noted.)

10.3Gbps OPTICAL EYE DIAGRAM

16ps/div

100G

10G

10Gbps ELECTRICAL EYE DIAGRAM

INPUT DIFFERENTIAL TO COMMON-MODE RETURN LOSS vs. FREQUENCY

RANDOM JITTER vs. MODULATION CURRENT (AT LOAD)

OUTPUT DIFFERENTIAL RETURN LOSS vs. FREQUENCY

SUPPLY CURRENT vs. TEMPERATURE (IMOD = 40mAp-p, IBIAS = 60mA)

1G

FREQUENCY (Hz)

-35

100M

### **Typical Operating Characteristics (continued)**

(Typical values are at  $V_{CC} = V_{CCT} = 3.3V$ ,  $T_A = +25^{\circ}C$ , data pattern =  $2^7 - 1$  PRBS + 72 zeros +  $2^7 - 1$  PRBS (inverted) + 72 ones, unless otherwise noted.)

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

### **Typical Operating Characteristics (continued)**

(Typical values are at  $V_{CC} = V_{CCT} = 3.3V$ ,  $T_A = +25^{\circ}C$ , data pattern =  $2^7 - 1$  PRBS + 72 zeros +  $2^7 - 1$  PRBS (inverted) + 72 ones, unless otherwise noted.)

#### MAX3949 3-WIRE ADDRESS vs. VSEL VOLTAGE

#### FAULT RECOVERY

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

## **Pin Configuration**

## **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                             | EQUIVALENT CIRCUIT |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1   | DISABLE | Disable Input, CMOS. Set to logic-low for normal operation. Logic-high or open disables both the modulation current and the bias current. Internally pulled up by a $7.5k\Omega$ resistor to $V_{CC}$ .                                                              | DISABLE            |

| 2   | VSEL    | 4-Level Input for SPI Device Address Detection. Connecting to V <sub>CC</sub> sets ADDR[6:5] to 11b, connecting to V <sub>CC</sub> x 2/3 sets ADDR[6:5] to 10b, connecting to V <sub>CC</sub> /3 sets ADDR[6:5] to 01b, and connecting to GND sets ADDR[6:5] to 00b. | VSEL               |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

## **Pin Description (continued)**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                       | EQUIVALENT CIRCUIT                 |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 3   | FAULT            | Fault Output, Open Drain. Logic-high indicates a fault condition has been detected. It remains high even after the fault condition has been removed. A logic-low occurs when the fault condition has been removed and the fault latch has been cleared by toggling DISABLE. FAULT should be pulled up to $V_{CC}$ by a 4.7k $\Omega$ to 10k $\Omega$ resistor. | SS- CLAMP                          |

| 4   | BMON             | Analog Laser Bias Current Monitor Output. Current out of<br>this pin develops a ground-referenced voltage across an<br>external resistor that is proportional to the BIAS pin current.<br>The current sourced by this pin is typically 1/104 the BIAS<br>pin current.                                                                                          | R<br>S<br>BMON                     |

| 5,8 | V <sub>CCT</sub> | Power Supply. Provides supply voltage to the output block.                                                                                                                                                                                                                                                                                                     | _                                  |

| 6   | TOUT-            | Inverting Laser Diode Modulation Current Output. Internally pulled up by a $25\Omega$ resistor to V <sub>CCT</sub> .                                                                                                                                                                                                                                           | V <sub>CCT</sub><br>TOUT-<br>TOUT+ |

| 7   | TOUT+            | Noninverting Laser Diode Modulation Current Output. Internally pulled up by a $25\Omega$ resistor to V <sub>CCT</sub> .                                                                                                                                                                                                                                        |                                    |

## **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                      | EQUIVALENT CIRCUIT |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 9   | BIAS | Combined Current Return Path and Laser BIAS Current<br>Output                                                                                                                                                                 | UCCT<br>BIAS       |

| 10  | CSEL | Chip-Select CMOS Input. Setting CSEL to logic-high starts a 3-wire command cycle. Setting CSEL to logic-low ends the cycle and resets the control state machine. Internally pulled down to GND by a $75k\Omega$ resistor.     |                    |

| 11  | SDA  | Serial Data Bidirectional CMOS Input. Also an open-drain output. This pin has a 75k $\Omega$ internal pullup, but requires an external 4.7k $\Omega$ to 10k $\Omega$ pullup resistor to V <sub>CC</sub> for proper operation. | SDA                |

| 12  | SCL  | Serial-Clock CMOS Input. This pin has an internal 75k $\Omega$ pulldown resistor to GND.                                                                                                                                      | SCL                |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

## **Pin Description (continued)**

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                           | EQUIVALENT CIRCUIT |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 13, 16 | V <sub>CC</sub> | Power Supply. Provides supply voltage to core analog and digital circuitry.                                                                                                                                                        | —                  |

| 14     | TIN+            | Noninverting Data Input. Input with internal 50Ω termination.                                                                                                                                                                      |                    |

| 15     | TIN-            | Inverting Data Input. Input with internal $50\Omega$ termination.                                                                                                                                                                  |                    |

| _      | EP              | Exposed Pad (Ground). This is the only electrical connection to ground on the MAX3949 and must be soldered to the circuit board ground for proper thermal and electrical performance (see the <i>Exposed-Pad Package</i> section). | _                  |

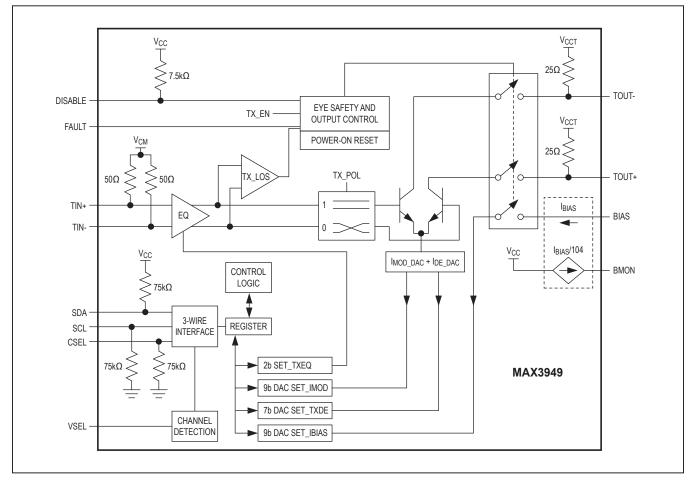

### **Functional Diagram**

### **Detailed Description**

The MAX3949 SFP+/QSFP+ laser driver is designed to drive  $5\Omega$  to  $10\Omega$  TOSAs from 1Gbps to 11.3Gbps. It contains an input buffer with programmable equalization, bias and modulation current DACs, an output driver with adjustable deemphasis, power-on-reset circuitry, bias current monitor, programmable 3-wire address, and eye safety circuitry with maskable fault monitors. A 3-wire digital interface is used to control these functions.

#### Input Buffer with Programmable Equalization

The input is internally biased and terminated with  $50\Omega$  to a common-mode voltage. The first amplifier stage features a programmable equalizer for high-frequency losses including a SFP+/QSFP+ host connector. Equalization is controlled by the <u>SET\_TXEQ</u> register (<u>Table 1</u>). The TX\_POL bit in the <u>TXCTRL</u> register controls the polarity of TOUT- and TOUT+ vs. TIN+ and TIN-. A status indicator bit (<u>TXSTAT1</u> bit 5) monitors the presence of an AC input signal.

# Table 1. Input Equalization ControlRegister Settings

| SET_TX | EQ[1:0] | BOOST AT 5.16GHz (dB) |

|--------|---------|-----------------------|

| 0      | 0       | 1                     |

| 0      | 1       | 3                     |

| 1      | 1       | 5.5                   |

#### Bias Current DAC

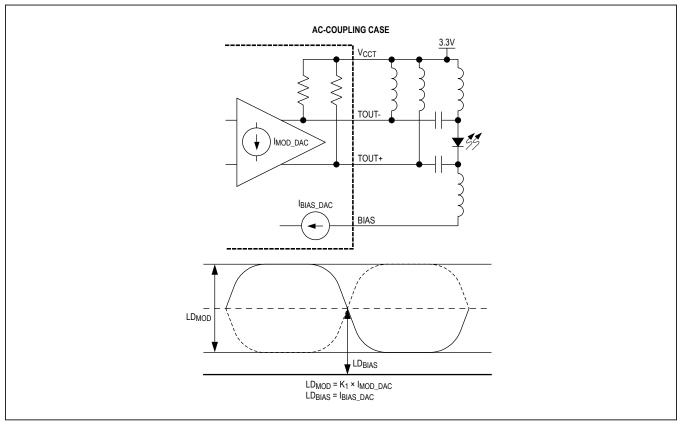

The bias current from the device is optimized to provide up to 105mA of bias current into a laser diode with 200 $\mu$ A resolution (Figure 1). The bias DAC current is controlled through the 3-wire digital interface using the SET\_IBIAS[8:0], IBIASMAX[7:0], and BIASINC[4:0] bits.

For laser operation, the laser bias current can be set using the 9-bit <u>SET\_IBIAS</u> DAC register. The upper 8 bits are set by the <u>SET\_IBIAS[8:1]</u> register, commonly used during the initialization procedure after power-on reset (POR). The LSB (bit 0) of <u>SET\_IBIAS</u> (<u>BIASINC[7]</u>) is initialized to zero after POR and can be updated using

Figure 1. AC-Coupling Case

the <u>BIASINC</u> register. The <u>IBIASMAX</u> register limits the maximum <u>SET\_IBIAS[8:1]</u> DAC code.

After initialization the value of the <u>SET\_IBIAS</u> DAC register should be updated using the <u>BIASINC</u> register to optimize cycle time and enhance laser safety. The <u>BIASINC</u> register is an 8-bit register. The first 5 bits of <u>BIASINC</u> contain the increment information in two's complement format. Increment values range from -16 to +15 LSBs. If the updated value of <u>SET\_IBIAS[8:1]</u> exceeds IBIASMAX[7:0], the IBIASERR warning flag is set and <u>SET\_IBIAS[8:1]</u> is set to <u>IBIASMAX[7:0]</u>.

#### **Modulation Current DAC**

The modulation current from the MAX3949 is optimized to provide up to 85mA of modulation current into a 5 $\Omega$  laser load with 210µA resolution. The modulation current is controlled through the 3-wire digital interface using the <u>SET\_IMOD[8:1]</u>, <u>IMODMAX[7:0]</u>, <u>MODINC[7:0]</u>, and <u>SET\_TXDE</u> registers.

For laser operation, the laser modulation current can be set using the 9-bit <u>SET\_IMOD</u> DAC. The upper 8 bits are programmed through the <u>SET\_IMOD</u>[8:1] register, commonly used during the initialization procedure after POR. The LSB (bit 0) of <u>SET\_IMOD</u> <u>MODINC</u>[7])is initialized to zero after POR and can be updated using the <u>MODINC</u> register. The <u>IMODMAX</u> register limits the maximum <u>SET\_IMOD</u>[8:1] DAC code.

After initialization the value of the <u>SET\_IMOD</u> DAC register should be updated using the <u>MODINC[4:0]</u> bits to optimize cycle time and enhance laser safety. The <u>MODINC</u> register is an 8-bit register. The first 5 bits of <u>MODINC</u> contain the increment information in two's complement format. Increment values range from -16 to +15 LSBs. If the updated value of <u>SET\_IMOD[8:1]</u> exceeds <u>IMODMAX[7:0]</u>, the IMODERR warning flag is set and <u>SET\_IMOD[8:1]</u> is set to IMODMAX[7:0].

Effective modulation current seen by the laser is actually the combination of the DAC current generated by the <u>SET\_IMOD[8:0]</u> register ( $I_{MOD}$ ), deemphasis setting (DE), and differential laser load (R). It is calculated by the following formula:

$LD_{MOD} = I_{MOD} \times 50 \times (1 - DE)/(50 + R)$

#### **Output Driver**

This device is optimized to drive a differential TOSA with a  $25\Omega$  flex circuit. The unique design of the output stage

enables DC-coupling to unmatched TOSAs with laser diode impedances ranging from  $5\Omega$  to  $10\Omega$ . The output stage also features programmable deemphasis that can be set as a percentage of the modulation current. The deemphasis function is controlled by the <u>TXCTRL[4:3]</u> and the <u>SET\_TXDE</u> registers.

#### Power-On Reset (POR)

Power-on reset ensures that the laser is off until the supply voltage has reached a specified threshold (2.75V). After power-on reset, TX\_EN is 0 and bias current and modulation current DACs default to small codes. In the case of a POR, all registers are reset to their default values.

#### **BMON Function**

The current out of the BMON pin is typically 1/104th the value of the current into the BIAS pin. The total resistance to ground at BMON sets the voltage.

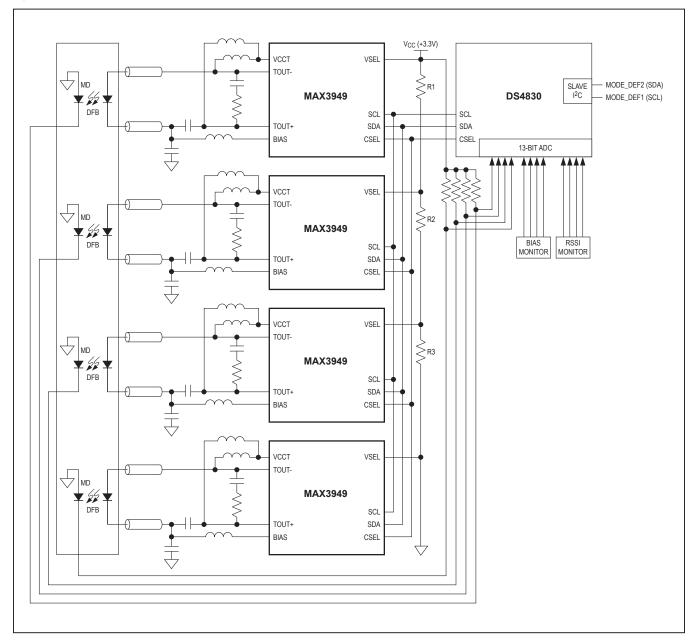

#### **VSEL** Function

The VSEL pin is an analog input that sets the 3-wire address for the MAX3949. The pin can be set to either  $V_{CC}$ ,  $V_{CC}$  x 2/3,  $V_{CC}$ /3, or to GND (<u>Table 2</u>). This allows up to four MAX3949s to be operated on a single 3-wire bus, each with their own address.

### Table 2. 3-Wire Address Selection

| VSEL                  | ADDR[6:5] |

|-----------------------|-----------|

| V <sub>CC</sub>       | 11b       |

| V <sub>CC</sub> x 2/3 | 10b       |

| V <sub>CC</sub> /3    | 01b       |

| GND                   | 00b       |

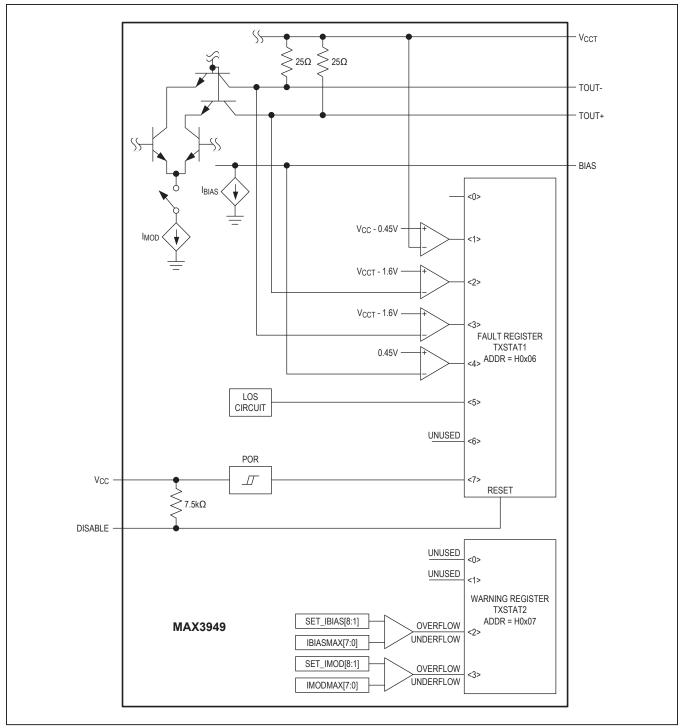

### Eye Safety and Output Control Circuitry

The safety and output control circuitry includes the disable pin (DISABLE) and enable bit (TX\_EN), along with a FAULT indicator and fault detectors (Figure 2). A fault condition triggers the FAULT pin to go high and a corresponding bit is set in the <u>TXSTAT1</u> register. The MAX3949 has two types of faults: hard faults and soft faults. Hard faults are maskable, trigger the FAULT pin (transitions high), disable the outputs and are stored in the <u>TXSTAT1</u> register. Soft faults serve as warnings, do not disable the outputs, and are stored in the TXSTAT2 register.

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

Figure 2. Eye Safety Circuitry

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

The FAULT pin is a latched output that can be cleared by toggling the DISABLE pin. Toggling the DISABLE pin also clears the <u>TXSTAT1</u> and <u>TXSTAT2</u> registers. A single-point

failure can be a short to V<sub>CC</sub> or GND. Table 3 shows the circuit response to various single-point failures.

### Table 3. Circuit Response to Single-Point Failure

| PIN    | NAME             | SHORT TO V <sub>CC</sub>                                          | SHORT TO GND                                              | OPEN                                                         |  |

|--------|------------------|-------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|--|

| 1      | DISABLE          | Disabled                                                          | Normal (Note 1). Can only be disabled by other means.     | Disabled                                                     |  |

| 2      | VSEL             | Normal (Note 2)                                                   | Normal (Note 2)                                           | Normal (Note 2)                                              |  |

| 3      | FAULT            | Normal (Note 2)                                                   | Normal (Note 1)                                           | Normal (Note 2)                                              |  |

| 4      | BMON             | Normal (Note 2)                                                   | Normal (Note 2)                                           | Normal (Note 2)                                              |  |

| 5, 8   | V <sub>CCT</sub> | Normal                                                            | Disabled—Fault (external supply shorted) (Note 3)         | Redundant path (Note 4)                                      |  |

| 6      | TOUT-            | Laser modulation current is reduced                               | Disabled (hard fault)                                     | Laser modulation current is reduced or disabled (hard fault) |  |

| 7      | TOUT+            | Laser modulation current is<br>reduced or off                     | Disabled (hard fault)                                     | Laser modulation current is reduced or disabled (hard fault) |  |

| 9      | BIAS             | I <sub>BIAS</sub> is on, but not delivered to the laser; no fault | Disabled (hard fault)                                     | Disabled (hard fault)                                        |  |

| 10     | CSEL             | Normal (Note 2)                                                   | Normal (Note 2)                                           | Normal (Note 2)                                              |  |

| 11     | SDA              | Normal (Note 2)                                                   | Normal (Note 2)                                           | Normal (Note 2)                                              |  |

| 12     | SCL              | Normal (Note 2)                                                   | Normal (Note 2)                                           | Normal (Note 2)                                              |  |

| 13, 16 | V <sub>CC</sub>  | Normal                                                            | Disabled—Hard fault<br>(external supply shorted) (Note 3) | Redundant path (Note 4)                                      |  |

| 14     | TIN+             | Disabled (hard fault)                                             | Disabled (hard fault)                                     | Normal (Note 2) or disabled (hard fault)                     |  |

| 15     | TIN-             | Disabled (hard fault)                                             | Disabled (hard fault)                                     | Normal (Note 2) or disabled (hard fault)                     |  |

Note 1: Normal operation—Does not affect the laser power.

Note 2: Pin functionality might be affected, which could affect laser power/performance.

Note 3: Supply-shorted current is assumed to be primarily on the circuit board (outside this device) and the main supply is collapsed by the short.

Note 4: Normal in functionality, but performance could be affected.

Warning: Shorted to V<sub>CC</sub> or shorted to ground on some pins can violate the Absolute Maximum Ratings.

#### **3-Wire Interface**

The MAX3949 implements a proprietary 3-wire digital interface. An external controller generates the clock. The 3-wire interface consists of an SDA bidirectional data line, a SCL clock signal input, and a CSEL chip-select input (active high). The external master initiates a data transfer by asserting the CSEL pin. The master starts to generate a clock signal after the CSEL pin has been set to a logic-high. All data transfers are most significant bit (MSB) first.

#### Protocol

Each operation consists of 16-bit transfers (15-bit address/data, 1-bit RWN). The bus master generates 16 clock cycles to SCL. All operations transfer 8 bits to the MAX3949. The RWN bit determines if the cycle is read or write (Table 5).

#### **Register Addresses**

The MAX3949 contains 13 registers available for programming. Table 6 shows the registers and addresses.

#### Write Mode (RWN = 0)

The master generates 16 clock cycles at SCL in total. The master outputs a total of 16 bits (MSB first) to the SDA line at the falling edge of the clock. The master closes the

# Table 4. Broadcast Mode RegisterInitialization Sequence

| ADDRESS | NAME      |

|---------|-----------|

| H0x0F   | FMSK      |

| H0x10   | SET_TXDE  |

| H0x11   | SET_TXEQ  |

| H0x0A   | IMODMAX   |

| H0x0B   | IBIASMAX  |

| H0x08   | SET_IBIAS |

| H0x09   | SET_IMOD  |

| H0x05   | TXCTRL    |

transmission by setting CSEL to 0.  $\underline{\mbox{Figure 3}}$  shows the interface timing.

#### Read Mode (RWN = 1)

The master generates 16 clock cycles at SCL in total. The master outputs a total of 8 bits (MSB first) to the SDA line at the falling edge of the clock. The SDA line is released after the RWN bit has been transmitted. The slave outputs 8 bits of data (MSB first) at the rising edge of the clock. The master closes the transmission by setting CSEL to 0. Figure 3 shows the interface timing.

#### Mode Control

Normal mode allows read-only instruction for all registers. Only the <u>MODINC</u> and <u>BIASINC</u> registers can be updated during normal mode. Doing so speeds up the laser control update through the 3-wire interface by a factor of two. The normal mode is the default mode.

Setup mode allows the master to write unrestricted data into any register except the status (TXSTAT1, TXSTAT2) registers. To enter the setup mode, the <u>MODECTRL</u> register (address = H0x0F) must be set to 12h. After the <u>MODECTRL</u> register has been set to 12h, the next operation is unrestricted. The setup mode is automatically exited after the operation is finished. This sequence must be repeated if further unrestricted settings are necessary.

Broadcast mode allows for faster configuration of multiple MAX3949 ICs by causing the address selection bits (ADDR[6:5]) to be ignored so all MAX3949s on the bus can be written to simultaneously.

A block write in broadcast mode can start at any of the addresses in <u>Table 4</u>. The block write is achieved by holding the CSEL pin high to lengthen the SPI cycle. The register address increments automatically through the sequence listed in <u>Table 4</u> and wraps from <u>TXCTRL</u> to <u>FMSK</u>. The block write ends once the CSEL pin is asserted low.

### Table 5. Digital Communication Word Structure

|    |           |    |    |    |    |   | В   | ΙТ |   |   |      |        |   |   |   |

|----|-----------|----|----|----|----|---|-----|----|---|---|------|--------|---|---|---|

| 15 | 14        | 13 | 12 | 11 | 10 | 9 | 8   | 7  | 6 | 5 | 4    | 3      | 2 | 1 | 0 |

|    | ADDR[6:0] |    |    |    |    |   | RWN |    |   |   | DATA | A[7:0] |   |   |   |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

| ADDRESS | NAME      | FUNCTION                                      |

|---------|-----------|-----------------------------------------------|

| H0x05   | TXCTRL    | Transmitter Control Register                  |

| H0x06   | TXSTAT1   | Transmitter Status Register 1                 |

| H0x07   | TXSTAT2   | Transmitter Status Register 2                 |

| H0x08   | SET_IBIAS | Bias Current Setting Register                 |

| H0x09   | SET_IMOD  | Modulation Current Setting Register           |

| H0x0A   | IMODMAX   | Maximum Modulation Current Setting Register   |

| H0x0B   | IBIASMAX  | Maximum Bias Current Setting Register         |

| H0x0C   | MODINC    | Modulation Current Increment Setting Register |

| H0x0D   | BIASINC   | Bias Current Increment Setting Register       |

| H0x0E   | MODECTRL  | Mode Control Register                         |

| H0x0F   | FMSK      | Fault Mask Register                           |

| H0x10   | SET_TXDE  | Transmitter Deemphasis Control Register       |

| H0x11   | SET_TXEQ  | Transmitter Equalization Control Register     |

### **Table 6. Register Descriptions and Addresses**

Figure 3. Timing for 3-Wire Digital Interface

### **Register Descriptions**

### Transmitter Control Register (TXCTRL), Address: H0x05

| Bit        | D7       | D6       | D5       | D4         | D3         | D2      | D1     | D0    |

|------------|----------|----------|----------|------------|------------|---------|--------|-------|

| Bit Name   | RESERVED | RESERVED | RESERVED | TXDE_MD[1] | TXDE_MD[0] | SOFTRES | TX_POL | TX_EN |

| Read/Write | R/W      | R/W      | R/W      | R/W        | R/W        | R/W     | R/W    | R/W   |

| POR State  | 0        | 0        | 0        | 0          | 0          | 0       | 1      | 0     |

The TXCTRL register sets the device's operation.

| BIT    | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                                                     |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:5] | RESERVED | Reserved Bits. The default state for these bits is 0 and they must be kept 0 when the register is accessed for a write operation.                                                                                                                                                                               |

| D[4:3] | TXDE_MD  | Controls the mode of the transmit output deemphasis circuitry.<br>00 = Deemphasis is fixed at 6% of the modulation amplitude<br>01 = Deemphasis is fixed at 3% of the modulation amplitude<br>10 = Deemphasis is programmed by SET_TXDE register setting (3% to 9%)<br>11 = Deemphasis is at its maximum of ~9% |

| D2     | SOFTRES  | Resets all registers to their default values (TXCTRL[1:0] must be = 10b during the write to SOFTRES for the registers to be set to their default values).<br>0 = Normal operation<br>1 = Reset                                                                                                                  |

| D1     | TX_POL   | Controls the polarity of the transmit signal path.<br>0 = Inverse<br>1 = Normal operation                                                                                                                                                                                                                       |

| D0     | TX_EN    | Enables or disables the transmit circuitry.<br>0 = Disabled<br>1 = Enabled                                                                                                                                                                                                                                      |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

| Bit             | D7<br>(STICKY) | D6<br>(STICKY) | D5<br>(STICKY) | D4<br>(STICKY) | D3<br>(STICKY) | D2<br>(STICKY) | D1<br>(STICKY) | D0<br>(STICKY) |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Bit Name        | FST[7]         | FST[6]         | FST[5]         | FST[4]         | FST[3]         | FST[2]         | FST[1]         | FST[0]         |

| Read/Write      | R              | R              | R              | R              | R              | R              | R              | R              |

| POR State       | 1              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |

| Reset Upon Read | Yes            |

#### Transmitter Status Register 1 (TXSTAT1), Address: H0x06

The TXSTAT1 register is a device status register.

| BIT | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | FST[7] | When the V <sub>CC</sub> supply voltage is below 2.3V, the POR circuitry reports a FAULT and <b>communication to the SPI cannot be performed</b> . Once the V <sub>CC</sub> supply voltage is above 2.75V, the POR resets all registers to their default values and the FAULT latch is cleared. |

| D6  | FST[6] | Reserved.                                                                                                                                                                                                                                                                                       |

| D5  | FST[5] | Indicates low or no AC signal at the inputs, a hard fault is reported unless masked.                                                                                                                                                                                                            |

| D4  | FST[4] | Indicates BIAS open or shorted to GND condition, threshold = 0.45V.                                                                                                                                                                                                                             |

| D3  | FST[3] | Indicates TOUT- open or shorted to GND condition, threshold = $V_{CCT}$ - 1.6V, a hard fault is reported unless masked.                                                                                                                                                                         |

| D2  | FST[2] | Indicates TOUT+ open or shorted to GND condition, threshold = $V_{CCT}$ - 1.6V, a hard fault is reported unless masked.                                                                                                                                                                         |

| D1  | FST[1] | Indicates $V_{CCT}$ open or shorted to GND conditions, threshold ( $V_{CCT}$ ) = $V_{CC}$ - 0.45V, a hard fault is reported unless masked.                                                                                                                                                      |

| D0  | FST[0] | Copy of a FAULT signal.                                                                                                                                                                                                                                                                         |

### Transmitter Status Register 2 (TXSTAT2), Address: H0x07

| Bit             | D7 | D6 | D5 | D4 | D3<br>(STICKY) | D2<br>(STICKY) | D1 | D0 |

|-----------------|----|----|----|----|----------------|----------------|----|----|

| Bit Name        | Х  | Х  | Х  | Х  | IMODERR        | IBIASERR       | Х  | Х  |

| Read/Write      | Х  | Х  | Х  | Х  | R              | R              | Х  | Х  |

| POR State       | Х  | Х  | Х  | Х  | 0              | 0              | Х  | Х  |

| Reset Upon Read | Х  | Х  | Х  | Х  | Yes            | Yes            | Х  | Х  |

The TXSTAT2 register is a device status register.

| BIT | NAME     | DESCRIPTION                                                                                                                                                                                                                                              |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D3  | IMODERR  | Modulation current overflow (on increment) or underflow (on decrement) error.<br>Overflow occurs if result > IMODMAX. In overflow condition, SET_IMOD[8:1] = IMODMAX[7:0].<br>Underflow occurs if result < 0. In underflow condition, SET_IMOD[8:0] = 0. |

| D2  | IBIASERR | Bias current overflow (on increment) or underflow (on decrement) error.<br>Overflow occurs if result > IBIASMAX. In overflow condition, SET_IBIAS[8:1] = IBIASMAX[7:0].<br>Underflow occurs if result < 0. In underflow condition, SET_IBIAS[8:0] = 0.   |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

| Blas Current Sett | ing Registe  |              | (S), Addres  | S: HUXU8     |              |              |              |              |

|-------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Bit               | D7           | D6           | D5           | D4           | D3           | D2           | D1           | D0           |

| Bit Name          | SET_IBIAS[8] | SET_IBIAS[7] | SET_IBIAS[6] | SET_IBIAS[5] | SET_IBIAS[4] | SET_IBIAS[3] | SET_IBIAS[2] | SET_IBIAS[1] |

| Read/Write        | R/W          |

| POR State         | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 1            |

### Bias Current Setting Register (SET\_IBIAS), Address: H0x08

The SET\_BIAS register sets the laser bias current DAC.

| BIT    | NAME           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |

|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | SET_IBIAS[8:1] | The bias current DAC is controlled by a total of 9 bits. The SET_IBIAS[8:1] bits are used to set the bias current with even denominations from 0 to 510 bits. The LSB (SET_IBIAS[0]) bit is controlled by the BIASINC register and is used to set the odd denominations in the SET_IBIAS[8:0]. Any direct write to SET_IBIAS[8:1] resets the LSB. |

### Modulation Current Setting Register (SET\_IMOD), Address: H0x09

| Bit        | D7          | D6          | D5          | D4          | D3          | D2          | D1          | D0          |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Bit Name   | SET_IMOD[8] | SET_IMOD[7] | SET_IMOD[6] | SET_IMOD[5] | SET_IMOD[4] | SET_IMOD[3] | SET_IMOD[2] | SET_IMOD[1] |

| Read/Write | R/W         |

| POR State  | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 0           |

The SET\_IMOD register sets the laser modulation current DAC.

| BIT    | NAME          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |

|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | SET_IMOD[8:1] | The mod current DAC is controlled by a total of 9 bits. The SET_IMOD[8:1] bits are used to set the modulation current with even denominations from 0 to 510 bits. The LSB (SET_IMOD[0]) bit is controlled by the MODINC register and is used to set the odd denominations in the SET_IMOD[8:0]. Any direct write to SET_IMOD[8:1] resets the LSB. |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

#### Maximum Modulation Current Setting Register (IMODMAX), Address: H0x0A

| Bit        | D7         | D6         | D5         | D4         | D3         | D2         | D1         | D0         |

|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Bit Name   | IMODMAX[7] | IMODMAX[6] | IMODMAX[5] | IMODMAX[4] | IMODMAX[3] | IMODMAX[2] | IMODMAX[1] | IMODMAX[0] |

| Read/Write | R/W        |

| POR State  | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          |

The IMODMAX register sets the upper limit of modulation current.

| BIT    | NAME         | DESCRIPTION                                                                                                                                                 |

|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | IMODMAX[7:0] | The IMODMAX register is an 8-bit register that can be used to limit the maximum modulation current. IMODMAX[7:0] is continuously compared to SET_IMOD[8:1]. |

#### Maximum Bias Current Setting Register (IBIASMAX), Address: H0x0B

| Bit        | D7          | D6          | D5          | D4          | D3          | D2          | D1          | D0          |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Bit Name   | IBIASMAX[7] | IBIASMAX[6] | IBIASMAX[5] | IBIASMAX[4] | IBIASMAX[3] | IBIASMAX[2] | IBIASMAX[1] | IBIASMAX[0] |

| Read/Write | R/W         |

| POR State  | 0           | 0           | 1           | 0           | 0           | 0           | 0           | 0           |

The IBIASMAX register sets the upper limit of bias current.

| BIT    | NAME          | DESCRIPTION                                                                                                                                              |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | IBIASMAX[7:0] | The IBIASMAX register is an 8-bit register that can be used to limit the maximum bias current. IBIASMAX[7:0] is continuously compared to SET_IBIAS[8:1]. |

#### Modulation Current Increment Setting Register (MODINC), Address: H0x0C

| Bit        | D7          | D6 | D5 | D4        | D3        | D2        | D1        | D0        |

|------------|-------------|----|----|-----------|-----------|-----------|-----------|-----------|

| Bit Name   | SET_IMOD[0] | Х  | Х  | MODINC[4] | MODINC[3] | MODINC[2] | MODINC[1] | MODINC[0] |

| Read/Write | R           | Х  | Х  | R/W       | R/W       | R/W       | R/W       | R/W       |

| POR State  | 0           | Х  | Х  | 0         | 0         | 0         | 0         | 0         |

The MODINC register increments/decrements the SET\_IMOD register.

| BIT    | NAME        | DESCRIPTION                                                                                                                                                                   |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7     | SET_IMOD[0] | LSB of SET_IMOD register                                                                                                                                                      |

| D[4:0] | MODINC      | This string of bits is used to increment or decrement the modulation current. When written to, the SET_IMOD[8:0] bits are updated. MODINC[4:0] are a two's complement string. |

## 11.3Gbps, Low-Power, AC-Coupled Laser Driver

|            |              | 0 0 | ``` | •          |            |            |            |            |

|------------|--------------|-----|-----|------------|------------|------------|------------|------------|

| Bit        | D7           | D6  | D5  | D4         | D3         | D2         | D1         | D0         |

| Bit Name   | SET_IBIAS[0] | Х   | Х   | BIASINC[4] | BIASINC[3] | BIASINC[2] | BIASINC[1] | BIASINC[0] |

| Read/Write | R            | Х   | Х   | R/W        | R/W        | R/W        | R/W        | R/W        |

| POR State  | 0            | Х   | Х   | 0          | 0          | 0          | 0          | 0          |

#### Bias Current Increment Setting Register (BIASINC), Address: H0x0D

The BIASINC register increments/decrements the SET\_IBIAS register.

| BIT    | NAME         | DESCRIPTION                                                                                                                                                                     |

|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7     | SET_IBIAS[0] | LSB of SET_IBIAS register.                                                                                                                                                      |

| D[4:0] | BIASINC      | This string of bits is used to increment or decrement the modulation current. When written to, the SET_IBIAS[8:0] bits are updated. BIASINC[4:0] are a two's complement string. |

### Mode Control Register (MODECTRL), Address: H0x0E

| Bit             | D7          | D6          | D5          | D4          | D3          | D2          | D1          | D0          |

|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Bit Name        | MODECTRL[7] | MODECTRL[6] | MODECTRL[5] | MODECTRL[4] | MODECTRL[3] | MODECTRL[2] | MODECTRL[1] | MODECTRL[0] |

| Read/Write      | R/W         |

| POR State       | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| Reset Upon Read | Yes*        |

\*All three modes reset back to 0h on the next 3-wire access.

The MODECTRL register set the operational mode of the 3-wire control for the MAX3949.