## National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

## LM4549B

# AC '97 Rev 2.1 Multi-Channel Audio Codec with Sample Rate Conversion and National 3D Sound

## **General Description**

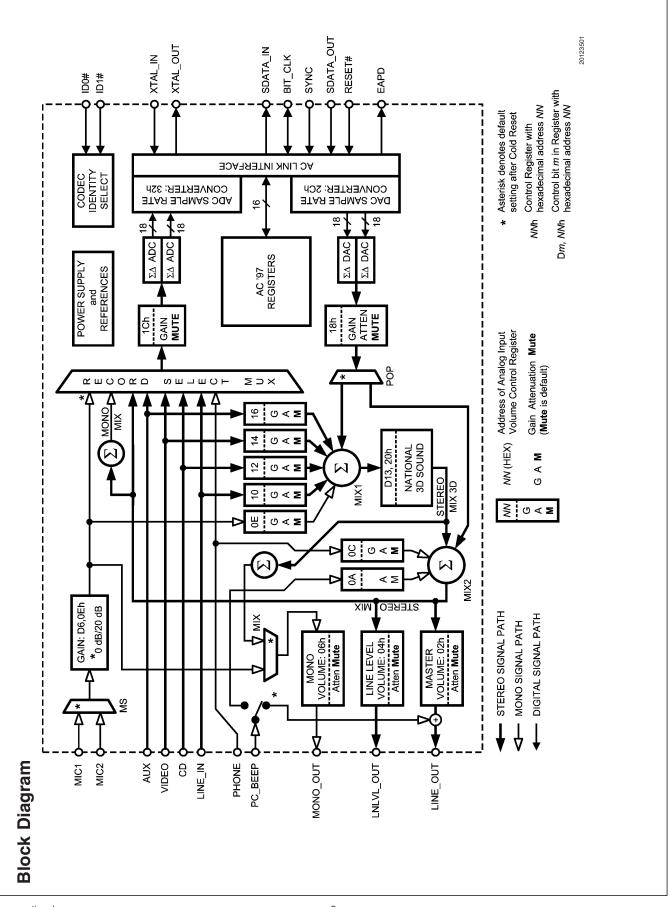

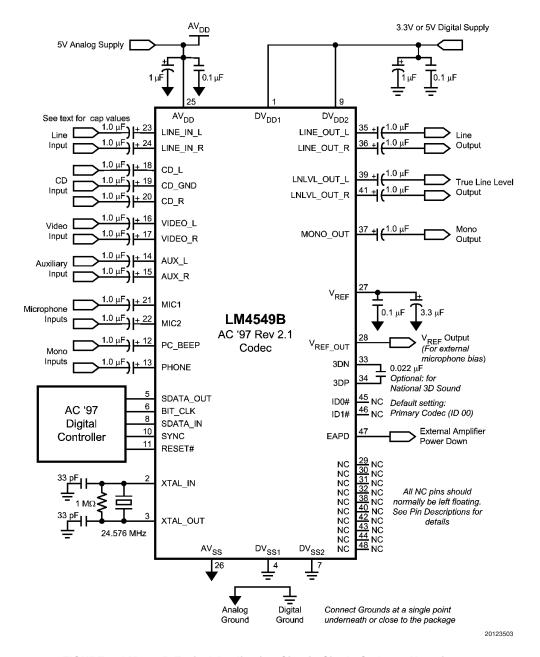

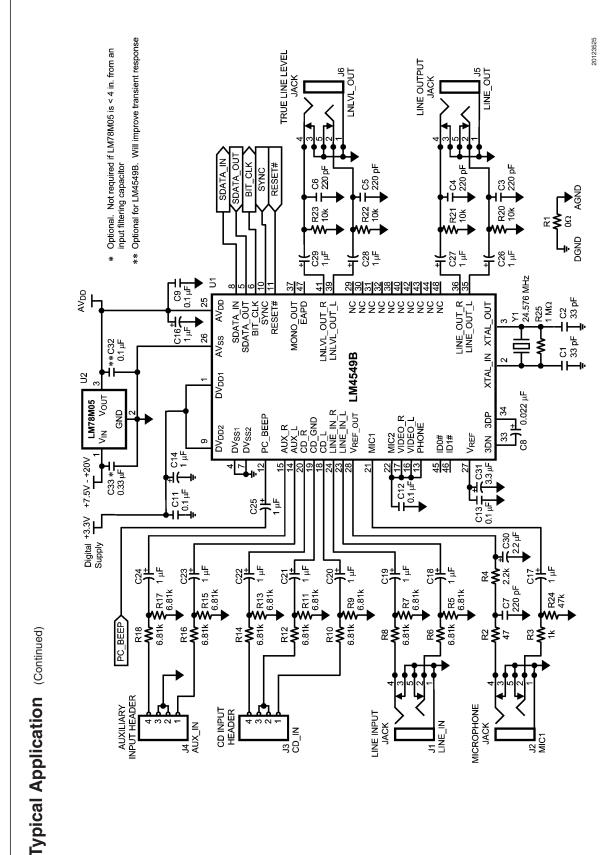

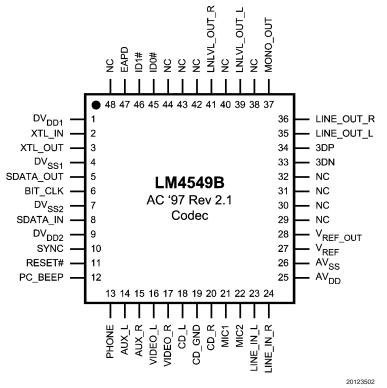

The LM4549B is an audio codec for PC systems which is fully PC99 compliant and performs the analog intensive functions of the AC '97 Rev 2.1 architecture. Using 18-bit Sigma-Delta ADCs and DACs, the LM4549B provides 90 dB of Dynamic Range.

The LM4549B was designed specifically to provide a high quality audio path and provide all analog functionality in a PC audio system. It features full duplex stereo ADCs and DACs and analog mixers with access to 4 stereo and 4 mono inputs. Each mixer input has separate gain, attenuation and mute control and the mixers drive 1 mono and 2 stereo outputs, each with attenuation and mute control. The LM4549B supports National's 3D Sound stereo enhancement and a comprehensive sample rate conversion capability. The sample rate for the ADCs and DACs can be programmed separately with a resolution of 1 Hz to convert any rate in the range 4 kHz - 48 kHz. Sample timing from the ADCs and sample request timing for the DACs are completely deterministic to ease task scheduling and application software development. These features together with an extended temperature range also make the LM4549B suitable for non-PC codec applications.

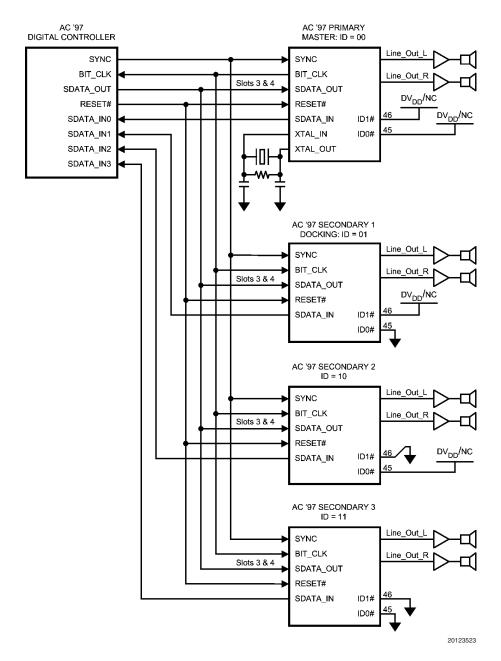

The LM4549B features the ability to connect several codecs together using the Extended AC Link configuration of one dedicated serial data signal to the Controller per codec. LM4549B systems support up to 8 simultaneous channels of streaming data on Input Frames (Codec to Controller) while Output Frames (Controller to Codec) carry 2 streams to multiple codecs. The LM4549B may also be used in systems with the National LM4550B to support up to 6 simultaneous channels of streaming data on Output Frames.

The AC '97 architecture separates the analog and digital functions of the PC audio system allowing both for system design flexibility and increased performance.

## **Key Specifications**

■ Analog Mixer Dynamic Range

DAC Dynamic Range

By dB (typ)

ADC Dynamic Range

ADC Dynamic Range

By dB (typ)

OdB (typ)

#### **Features**

- AC '97 Rev 2.1 compliant

- High quality Sample Rate Conversion from 4 kHz to 48 kHz in 1 Hz increments

- Multiple codec support

- True Line Level Output with separate gain control

- National's 3D Sound stereo enhancement circuitry

- Advanced power management support

- External Amplifier Power Down (EAPD) control

- PC-Beep passthrough to Line Out during Initialization or Cold Reset

- Digital 3.3V and 5V supply options

- Extended Temperature: -40°C ≤ T<sub>A</sub> ≤ 85°C

## **Applications**

- Desktop PC audio systems on PCI cards, AMR cards, or with motherboard chips sets featuring AC Link

- Portable PC systems as on MDC cards, or with a chipset or accelerator featuring AC Link

- General and Multi-channel audio frequency systems

- Automotive Telematics

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 6.0V

Storage Temperature -65°C to +150°C

Input Voltage -0.3V to V<sub>DD</sub> +0.3V

ESD Susceptibility (Note 2) 2000V

pin 3 750V

ESD Susceptibility (Note 3) 200V

pin 3 100V

Junction Temperature 150°C

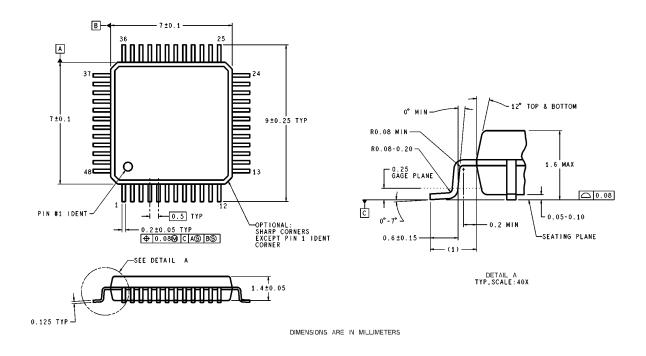

$\begin{array}{c} \text{Soldering Information} \\ \text{LQFP Package} \\ \text{Vapor Phase (60 sec.)} \\ \text{Infrared (15 sec.)} \\ \theta_{\text{JA}} \left( \text{typ} \right) - \text{VBH48A} \end{array} \qquad \begin{array}{c} 215^{\circ}\text{C} \\ 220^{\circ}\text{C} \\ 74^{\circ}\text{C/W} \end{array}$

## **Operating Ratings**

Temperature Range

$$\begin{split} T_{\text{MIN}} \leq T_{\text{A}} \leq T_{\text{MAX}} \text{ (Note 4)} & -40\,^{\circ}\text{C} \leq T_{\text{A}} \leq 85\,^{\circ}\text{C} \\ \text{Analog Supply Range} & 4.2\text{V} \leq \text{AV}_{\text{DD}} \leq 5.5\text{V} \\ \text{Digital Supply Range} & 3.0\text{V} \leq \text{DV}_{\text{DD}} \leq 5.5\text{V} \end{split}$$

**Electrical Characteristics** (Notes 1, 5) The following specifications apply for  $AV_{DD} = 5V$ ,  $DV_{DD} = 3.3V$ , Fs = 48 kHz, single codec configuration, (primary mode) unless otherwise noted. Limits apply for  $T_A = 25$ °C. The reference for 0 dB is 1 Vrms unless otherwise specified.

| Symbol           | Parameter                             | Conditions                                                         | LM4      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |  |  |

|------------------|---------------------------------------|--------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

|                  |                                       |                                                                    | Typical  | Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |  |  |

|                  |                                       |                                                                    | (Note 6) | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |  |  |

| AV <sub>DD</sub> | Analog Supply Range                   |                                                                    |          | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V (min)  |  |  |

|                  |                                       |                                                                    |          | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V (max)  |  |  |

| $DV_DD$          | Digital Supply Range                  |                                                                    |          | 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V (min)  |  |  |

|                  |                                       |                                                                    |          | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V (max)  |  |  |

| D                | Digital Quiescent Power Supply        | $DV_{DD} = 5 V$                                                    | 34       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mA       |  |  |

| $D_IDD$          | Current                               | $DV_{DD} = 3.3 \text{ V}$                                          | 19       | Cal   Limit   Chimits   Cal   Chimits   Cal   Chimits   Cal   C | mA       |  |  |

| A <sub>IDD</sub> | Analog Quiescent Power Supply Current | AV <sub>DD</sub> = 5.5 V                                           | 53       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mA       |  |  |

| I <sub>DSD</sub> | Digital Shutdown Current              | PR543210 = 111111                                                  | 19       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | μΑ       |  |  |

| I <sub>ASD</sub> | Analog Shutdown Current               | PR543210 = 111111                                                  | 70       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | μΑ       |  |  |

| $V_{REF}$        | Reference Voltage                     | No pullup resistor                                                 | 2.16     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V        |  |  |

| PSRR             | Power Supply Rejection Ratio          |                                                                    | 40       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB       |  |  |

| Analog Loop      | othrough Mode (Note 8)                |                                                                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |  |  |

|                  | Dynamic Range (Note 9)                | CD Input to Line Output, -60 dB Input THD+N                        | 97       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | dB (min  |  |  |

| THD              | Total Harmonic Distortion             | $V_O = -3 \text{ dB}, f = 1 \text{ kHz}, R_L = 10 \text{ k}\Omega$ | 0.013    | 0.02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | % (max)  |  |  |

| Analog Inpu      | t Section                             |                                                                    |          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |  |  |

| V <sub>IN</sub>  | Line Input Voltage                    | LINE_IN, AUX, CD, VIDEO, PC_BEEP, PHONE                            | 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Vrms     |  |  |

| V <sub>IN</sub>  | Mic Input with 20 dB Gain             |                                                                    | 0.1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Vrms     |  |  |

| V <sub>IN</sub>  | Mic Input with 0 dB Gain              |                                                                    | 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Vrms     |  |  |

| Xtalk            | Crosstalk                             | CD Left to Right                                                   | -95      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB       |  |  |

| Z <sub>IN</sub>  | Input Impedance(Note 9)               | All Analog Inputs                                                  | 40       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | kΩ (min) |  |  |

| C <sub>IN</sub>  | Input Capacitance(Note 9)             |                                                                    | 3.7      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | pF       |  |  |

|                  | Interchannel Gain Mismatch            | CD Left to Right                                                   | 0.1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB       |  |  |

| Record Gair      | Amplifier - ADC                       |                                                                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |  |  |

| A <sub>S</sub>   | Step Size                             | 0 dB to 22.5 dB                                                    | 1.5      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB       |  |  |

| A <sub>M</sub>   | Mute Attenuation (Note 9)             |                                                                    | 86       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB       |  |  |

| Mixer Section    | on                                    |                                                                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |  |  |

| A <sub>S</sub>   | Step Size                             | +12 dB to -34.5 dB                                                 | 1.5      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB       |  |  |

| A <sub>M</sub>   | Mute Attenuation                      |                                                                    | 86       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB       |  |  |

**Electrical Characteristics** (Notes 1, 5) The following specifications apply for  $AV_{DD} = 5V$ ,  $DV_{DD} = 3.3V$ , Fs = 48 kHz, single codec configuration, (primary mode) unless otherwise noted. Limits apply for  $T_A = 25$ °C. The reference for 0 dB is 1 Vrms unless otherwise specified. (Continued)

| Symbol              | Parameter                               | Conditions                                          | LM4                 | Units<br>(Limits)          |         |

|---------------------|-----------------------------------------|-----------------------------------------------------|---------------------|----------------------------|---------|

|                     |                                         |                                                     | Typical<br>(Note 6) | Limit<br>(Note 7)          |         |

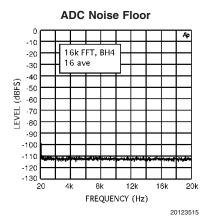

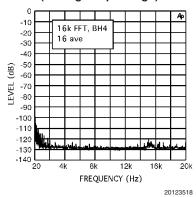

| Analog to Di        | igital Converters                       |                                                     |                     |                            |         |

|                     | Resolution                              |                                                     | 18                  |                            | Bits    |

|                     | Dynamic Range (Note 9)                  | -60 dB Input THD+N, A-Weighted                      | 90                  | 86                         | dB (mir |

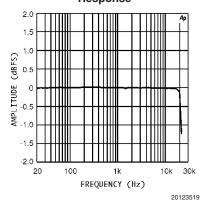

|                     | Frequency Response                      | -1 dB Bandwidth                                     | 20                  |                            | kHz     |

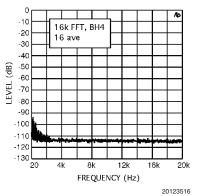

| Digital to An       | nalog Converters                        |                                                     |                     |                            |         |

|                     | Resolution                              |                                                     | 18                  |                            | Bits    |

|                     | Dynamic Range (Note 9)                  | -60 dB Input THD+N, A-Weighted                      | 89                  | 82                         | dB (mir |

| THD                 | Total Harmonic Distortion               | $V_{IN}$ = -3 dB, f = 1 kHz, $R_L$ = 10 k $\Omega$  | 0.01                |                            | %       |

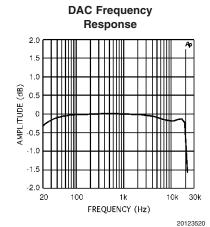

|                     | Frequency Response                      |                                                     | 20 - 21 k           |                            | Hz      |

|                     | Group Delay (Note 9)                    | Sample Frequency = 48 kHz                           | 0.36                | 1                          | ms (ma  |

|                     | Out of Band Energy (Note 10)            |                                                     | -40                 |                            | dB      |

|                     | Stop Band Rejection                     |                                                     | 70                  |                            | dB      |

| D <sub>T</sub>      | Discrete Tones                          |                                                     | -96                 |                            | dB      |

| Analog Outp         | out Section                             |                                                     |                     |                            |         |

| A <sub>S</sub>      | Step Size                               | 0 dB to -46.5 dB                                    | 1.5                 |                            | dB      |

| A <sub>M</sub>      | Mute Attenuation                        |                                                     | 86                  |                            | dB      |

| Z <sub>OUT</sub>    | Output Impedance (Note 9)               | All Analog Outputs                                  | 220                 |                            | Ω       |

| Digital I/O (N      | Note 9)                                 |                                                     |                     |                            |         |

| V <sub>IH</sub>     | High level input voltage                |                                                     |                     | 0.65 x<br>DV <sub>DD</sub> | V (min  |

| V <sub>IL</sub>     | Low level input voltage                 |                                                     |                     | 0.35 x<br>DV <sub>DD</sub> | V (max  |

| V <sub>OH</sub>     | High level output voltage               | I <sub>O</sub> = -2.5 mA.                           |                     | 0.90 x<br>DV <sub>DD</sub> | V (min  |

| V <sub>OL</sub>     | Low level output voltage                | I <sub>O</sub> = 2.5 mA.                            |                     | 0.10 x<br>DV <sub>DD</sub> | V (max  |

| IL                  | Input Leakage Current                   | AC Link inputs                                      |                     | ±10                        | μA      |

| I <sub>L</sub>      | Tri state Leakage Current               | High impedance AC Link outputs                      |                     | ±10                        | μA      |

| C <sub>IN</sub>     | AC-Link I/O capacitance(Note 9)         | SDout, BitClk, SDin, Sync, Reset# only              | 4                   | 7.5                        | pF (max |

| I <sub>DR</sub>     | Output drive current                    | AC Link outputs                                     | 5                   |                            | mA      |

| Digital Timin       | ng Specifications (Note 9)              |                                                     |                     |                            | _       |

| F <sub>BC</sub>     | BIT_CLK frequency                       |                                                     | 12.288              |                            | MHz     |

| T <sub>BCP</sub>    | BIT_CLK period                          |                                                     | 81.4                |                            | ns      |

| T <sub>CH</sub>     | BIT_CLK high                            | Variation of BIT_CLK duty cycle from 50%            |                     | ±20                        | % (max  |